Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48MHz                                                          |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART, USB                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 21x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f343-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 17.5.3.Slave Receiver Mode                                            | 201 |

|-----------------------------------------------------------------------|-----|

| 17.5.4.Slave Transmitter Mode                                         |     |

| 17.6.SMBus Status Decoding                                            |     |

| 18.UART0                                                              |     |

| 18.1.Enhanced Baud Rate Generation                                    |     |

| 18.2.Operational Modes                                                |     |

| 18.2.1.8-Bit UART                                                     |     |

| 18.2.2.9-Bit UART                                                     |     |

| 18.3.Multiprocessor Communications                                    |     |

| 19. UART1 (C8051F340/1/4/5/8/A/B/C Only)                              |     |

| 19.1.Baud Rate Generator                                              |     |

| 19.2.Data Format                                                      |     |

| 19.3.Configuration and Operation                                      |     |

| 19.3.1.Data Transmission                                              |     |

| 19.3.2.Data Reception                                                 |     |

| 19.3.3.Multiprocessor Communications                                  |     |

| 20. Enhanced Serial Peripheral Interface (SPI0)                       |     |

| 20.1.Signal Descriptions                                              |     |

| 20.1.1.Master Out, Slave In (MOSI)                                    | 223 |

| 20.1.2.Master In, Slave Out (MISO)                                    |     |

| 20.1.3.Serial Clock (SCK)                                             |     |

| 20.1.4.Slave Select (NSS)                                             |     |

| 20.2.SPI0 Master Mode Operation                                       |     |

| 20.3.SPI0 Slave Mode Operation                                        |     |

| 20.4.SPI0 Interrupt Sources                                           |     |

| 20.5.Serial Clock Timing                                              |     |

| 20.6.SPI Special Function Registers                                   |     |

| 21. Timers                                                            |     |

| 21.1.Timer 0 and Timer 1                                              |     |

| 21.1.1.Mode 0: 13-bit Counter/Timer                                   |     |

| 21.1.2.Mode 1: 16-bit Counter/Timer                                   |     |

| 21.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload                   |     |

| 21.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)                |     |

| 21.2.Timer 2                                                          |     |

| 21.2.1.16-bit Timer with Auto-Reload                                  |     |

| 21.2.2.8-bit Timers with Auto-Reload                                  |     |

| 21.2.3. Timer 2 Capture Modes: USB Start-of-Frame or LFO Falling Edge |     |

| 21.3.Timer 3                                                          |     |

| 21.3.1.16-bit Timer with Auto-Reload                                  | 249 |

| 21.3.2.8-bit Timers with Auto-Reload                                  |     |

| 21.3.3.USB Start-of-Frame Capture                                     |     |

| 22. Programmable Counter Array (PCA0)                                 |     |

| 22.1.PCA Counter/Timer                                                | 256 |

| 22.2.Capture/Compare Modules                                          |     |

| 22.2.1.Edge-triggered Capture Mode                                    | 258 |

| SFR Definition 22.6. PCA0CPLn: PCA Capture Module Low Byte       | 269 |

|------------------------------------------------------------------|-----|

| SFR Definition 22.7. PCA0CPHn: PCA Capture Module High Byte      | 270 |

| C2 Register Definition 23.1. C2ADD: C2 Address                   | 271 |

| C2 Register Definition 23.2. DEVICEID: C2 Device ID              | 271 |

| C2 Register Definition 23.3. REVID: C2 Revision ID               | 272 |

| C2 Register Definition 23.4. FPCTL: C2 Flash Programming Control | 272 |

| C2 Register Definition 23.5. FPDAT: C2 Flash Programming Data    | 272 |

## 1. System Overview

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 48 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Universal Serial Bus (USB) Function Controller with eight flexible endpoint pipes, integrated transceiver, and 1 kB FIFO RAM

- Supply Voltage Regulator

- True 10-bit 200 ksps differential / single-ended ADC with analog multiplexer

- On-chip Voltage Reference and Temperature Sensor

- On-chip Voltage Comparators (2)

- Precision internal calibrated 12 MHz internal oscillator and 4x clock multiplier

- Internal low-frequency oscillator for additional power savings

- Up to 64 kB of on-chip Flash memory

- Up to 4352 Bytes of on-chip RAM (256 + 4 kB)

- External Memory Interface (EMIF) available on 48-pin versions.

- SMBus/I2C, up to 2 UARTs, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Missing Clock Detector

- Up to 40 Port I/O (5 V tolerant)

With on-chip Power-On Reset, V<sub>DD</sub> monitor, Voltage Regulator, Watchdog Timer, and clock oscillator, C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 2.7–5.25 V operation over the industrial temperature range (-40 to +85 °C). For voltages above 3.6 V, the on-chip Voltage Regulator must be used. A minimum of 3.0 V is required for USB communication. The Port I/O and RST pins are tolerant of input signals up to 5 V. C8051F340/1/2/3/ 4/5/6/7/8/9/A/B/C/D devices are available in 48-pin TQFP, 32-pin LQFP, or 32-pin QFN packages. See Table 1.1, "Product Selection Guide," on page 18 for feature and package choices.

## 5.4. Programmable Window Detector

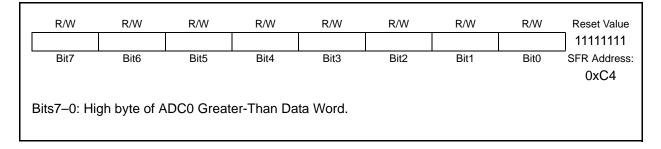

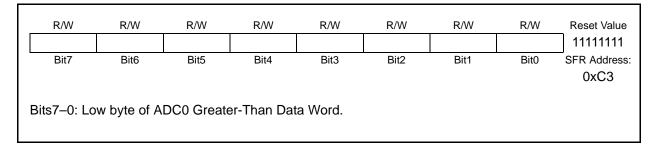

The ADC Programmable Window Detector continuously compares the ADC0 conversion results to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

The Window Detector registers must be written with the same format (left/right justified, signed/unsigned) as that of the current ADC configuration (left/right justified, single-ended/differential).

## SFR Definition 5.7. ADC0GTH: ADC0 Greater-Than Data High Byte

## SFR Definition 5.8. ADC0GTL: ADC0 Greater-Than Data Low Byte

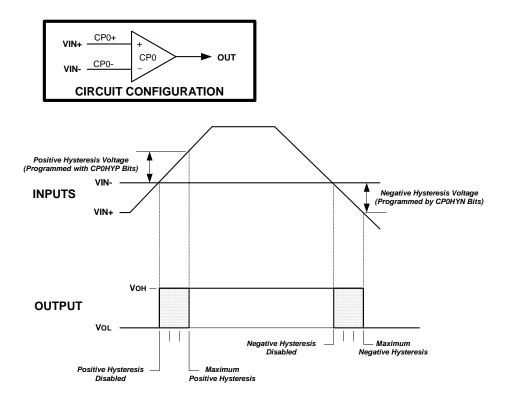

Figure 7.2. Comparator Hysteresis Plot

Comparator hysteresis is programmed using Bits3-0 in the Comparator Control Register CPTnCN (shown in SFR Definition 7.1 and SFR Definition 7.4). The amount of negative hysteresis voltage is determined by the settings of the CPnHYN bits. As shown in Figure 7.2, various levels of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPnHYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see **Section "9.3. Interrupt Handler" on page 88**.) The CPnFIF flag is set to '1' upon a Comparator falling-edge, and the CPnRIF flag is set to '1' upon the Comparator rising-edge. Once set, these bits remain set until cleared by software. The output state of the Comparator can be obtained at any time by reading the CPnOUT bit. The Comparator is enabled by setting the CPnEN bit to '1', and is disabled by clearing this bit to '0'.

### Table 9.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| -        |      | Description                       | Page |  |  |

|----------|------|-----------------------------------|------|--|--|

| P1MDIN   | 0xF2 | Port 1 Input Mode Configuration   | 152  |  |  |

| P1MDOUT  | 0xA5 | Port 1 Output Mode Configuration  | 152  |  |  |

| P1SKIP   | 0xD5 | Port 1 Skip                       | 153  |  |  |

| P2       | 0xA0 | Port 2 Latch                      | 153  |  |  |

| P2MDIN   | 0xF3 | Port 2 Input Mode Configuration   | 153  |  |  |

| P2MDOUT  | 0xA6 | Port 2 Output Mode Configuration  | 154  |  |  |

| P2SKIP   | 0xD6 | Port 2 Skip                       | 154  |  |  |

| P3       | 0xB0 | Port 3 Latch                      | 155  |  |  |

| P3MDIN   | 0xF4 | Port 3 Input Mode Configuration   | 155  |  |  |

| P3MDOUT  | 0xA7 | Port 3 Output Mode Configuration  | 155  |  |  |

| P3SKIP   | 0xDF | Port 3Skip                        | 156  |  |  |

| P4       | 0xC7 | Port 4 Latch                      | 156  |  |  |

| P4MDIN   | 0xF5 | Port 4 Input Mode Configuration   | 157  |  |  |

| P4MDOUT  | 0xAE | Port 4 Output Mode Configuration  | 157  |  |  |

| PCA0CN   | 0xD8 | PCA Control                       | 266  |  |  |

| PCA0CPH0 | 0xFC | PCA Capture 0 High                | 270  |  |  |

| PCA0CPH1 | 0xEA | PCA Capture 1 High                | 270  |  |  |

| PCA0CPH2 | 0xEC | PCA Capture 2 High                | 270  |  |  |

| PCA0CPH3 | 0xEE | PCA Capture 3High                 | 270  |  |  |

| PCA0CPH4 | 0xFE | PCA Capture 4 High                | 270  |  |  |

| PCA0CPL0 | 0xFB | PCA Capture 0 Low                 | 269  |  |  |

| PCA0CPL1 | 0xE9 | PCA Capture 1 Low                 | 269  |  |  |

| PCA0CPL2 | 0xEB | PCA Capture 2 Low                 | 269  |  |  |

| PCA0CPL3 | 0xED | PCA Capture 3 Low                 | 269  |  |  |

| PCA0CPL4 | 0xFD | PCA Capture 4 Low                 | 269  |  |  |

| PCA0CPM0 | 0xDA | PCA Module 0 Mode Register        | 268  |  |  |

| PCA0CPM1 | 0xDB | PCA Module 1 Mode Register        | 268  |  |  |

| PCA0CPM2 | 0xDC | PCA Module 2 Mode Register        | 268  |  |  |

| PCA0CPM3 | 0xDD | PCA Module 3 Mode Register        | 268  |  |  |

| PCA0CPM4 | 0xDE | PCA Module 4 Mode Register        | 268  |  |  |

| PCA0H    | 0xFA | PCA Counter High                  | 269  |  |  |

| PCA0L    | 0xF9 | PCA Counter Low                   | 269  |  |  |

| PCA0MD   | 0xD9 | PCA Mode                          | 267  |  |  |

| PCON     | 0x87 | Power Control                     | 98   |  |  |

| PFE0CN   | 0xAF | Prefetch Engine Control           | 99   |  |  |

| PSCTL    | 0x8F | Program Store R/W Control         | 112  |  |  |

| PSW      | 0xD0 | Program Status Word               | 87   |  |  |

| REF0CN   | 0xD1 | Voltage Reference Control         | 58   |  |  |

| REG0CN   | 0xC9 | Voltage Regulator Control         | 72   |  |  |

| RSTSRC   | 0xEF | Reset Source Configuration/Status | 105  |  |  |

| SBCON1   | 0xAC | UART1 Baud Rate Generator Control | 220  |  |  |

| SBRLH1   | 0xB5 | UART1 Baud Rate Generator High    | 221  |  |  |

| SBRLL1   | 0xB4 | UART1 Baud Rate Generator Low     | 221  |  |  |

| SBUF1    | 0xD3 | UART1 Data Buffer                 | 220  |  |  |

| SCON1    | 0xD2 | UART1 Control                     | 218  |  |  |

## SFR Definition 9.6. B: B Register

|   | R/W                                                                                                        | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W         | Reset Value  |  |  |  |  |

|---|------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------------|--------------|--|--|--|--|

|   | B.7                                                                                                        | B.6  | B.5  | B.4  | B.3  | B.2  | B.1  | B.0         | 00000000     |  |  |  |  |

|   | Bit7                                                                                                       | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0        | SFR Address: |  |  |  |  |

|   |                                                                                                            |      |      |      |      |      | (bit | addressable | ) 0xF0       |  |  |  |  |

| B | Bits7–0: B: B Register.<br>This register serves as a second accumulator for certain arithmetic operations. |      |      |      |      |      |      |             |              |  |  |  |  |

## 9.3. Interrupt Handler

The CIP-51 includes an extended interrupt system supporting multiple interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE-EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

### 9.3.1. MCU Interrupt Sources and Vectors

The MCU supports multiple interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 9.4 on page 90. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### 9.3.2. External Interrupts

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (**Section "21.1. Timer 0 and Timer 1" on page 235**) select level or edge sensitive. The following table lists the possible configurations.

| Interrupt Source               | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|--------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                          | 0x0000              | Тор               | None                                                                       | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(INT0) | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow               | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(INT1) | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow               | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                          | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                | Ν              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow               | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                           | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                | N              | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                           | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Y                | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| USB0                           | 0x0043              | 8                 | Special                                                                    | Ν                | Ν              | EUSB0<br>(EIE1.1)  | PUSB0<br>(EIP1.1)   |

| ADC0 Window<br>Compare         | 0x004B              | 9                 | ADOWINT<br>(ADC0CN.3)                                                      | Y                | Ν              | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| ADC0 Conversion<br>Complete    | 0x0053              | 10                | AD0INT (ADC0CN.5)                                                          | Y                | Ν              | EADC0<br>(EIE1.3)  | PADC0<br>(EIP1.3)   |

| Programmable Counter<br>Array  | 0x005B              | 11                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                           | Y                | N              | EPCA0<br>(EIE1.4)  | PPCA0<br>(EIP1.4)   |

| Comparator0                    | 0x0063              | 12                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | Ν                | Ν              | ECP0<br>(EIE1.5)   | PCP0<br>(EIP1.5)    |

| Comparator1                    | 0x006B              | 13                | CP1FIF (CPT1CN.4)<br>CP1RIF (CPT1CN.5)                                     | Ν                | Ν              | ECP1<br>(EIE1.6)   | PCP1<br>(EIP1.6)    |

| Timer 3 Overflow               | 0x0073              | 14                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | Ν                | N              | ET3<br>(EIE1.7)    | PT3<br>(EIP1.7)     |

| VBUS Level                     | 0x007B              | 15                | N/A                                                                        | N/A              | N/A            | EVBUS<br>(EIE2.0)  | PVBUS<br>(EIP2.0)   |

| UART1                          | 0x0083              | 16                | RI1 (SCON1.0)<br>TI1 (SCON1.1)                                             | Ν                | Ν              | ES1<br>(EIE2.1)    | PS1<br>(EIP2.1)     |

Table 9.4. Interrupt Summary

### 9.3.5. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

## 12. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operation is not required. Code execution is stalled during a Flash write/erase operation. Refer to Table 12.1 for complete Flash memory electrical characteristics.

## 12.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Labs or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see **Section "23. C2 Interface" on page 271**.

To ensure the integrity of Flash contents, it is strongly recommended that the  $V_{DD}$  monitor be left enabled in any system which writes or erases Flash memory from code. It is also crucial to ensure that the FLRT bit in register FLSCL be set to '1' if a clock speed higher than 25 MHz is being used for the device.

### 12.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 12.2.

### 12.1.2. Flash Erase Procedure

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, Flash write operations must be enabled by: (1) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY); and (2) Setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory). The PSWE bit remains set until cleared by software.

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. A byte location to be programmed must be erased before a new value is written. The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- Step 1. Disable interrupts (recommended).

- Step 2. Write the first key code to FLKEY: 0xA5.

- Step 3. Write the second key code to FLKEY: 0xF1.

- Step 4. Set the PSEE bit (register PSCTL).

- Step 5. Set the PSWE bit (register PSCTL).

- Step 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- Step 7. Clear the PSWE bit (register PSCTL).

- Step 8. Clear the PSEE bit (register PSCTI).

#### 12.1.3. Flash Write Procedure

Bytes in Flash memory can be written one byte at a time, or in groups of two. The FLBWE bit in register PFE0CN (SFR Definition 10.1) controls whether a single byte or a block of two bytes is written to Flash during a write operation. When FLBWE is cleared to '0', the Flash will be written one byte at a time. When FLBWE is set to '1', the Flash will be written in two-byte blocks. Block writes are performed in the same amount of time as single-byte writes, which can save time when storing large amounts of data to Flash memory.During a single-byte write to Flash, bytes are written individually, and a Flash write will be performed after each MOVX write instruction. The recommended procedure for writing Flash in single bytes is:

- Step 1. Disable interrupts.

- Step 2. Clear the FLBWE bit (register PFE0CN) to select single-byte write mode.

- Step 3. Set the PSWE bit (register PSCTL).

- Step 4. Clear the PSEE bit (register PSCTL).

- Step 5. Write the first key code to FLKEY: 0xA5.

- Step 6. Write the second key code to FLKEY: 0xF1.

- Step 7. Using the MOVX instruction, write a single data byte to the desired location within the 512-byte sector.

- Step 8. Clear the PSWE bit.

- Step 9. Re-enable interrupts.

Steps 5-7 must be repeated for each byte to be written.

For block Flash writes, the Flash write procedure is only performed after the last byte of each block is written with the MOVX write instruction. A Flash write block is two bytes long, from even addresses to odd addresses. Writes must be performed sequentially (i.e. addresses ending in 0b and 1b must be written in order). The Flash write will be performed following the MOVX write that targets the address ending in 1b. If a byte in the block does not need to be updated in Flash, it should be written to 0xFF. The recommended procedure for writing Flash in blocks is:

- Step 1. Disable interrupts.

- Step 2. Set the FLBWE bit (register PFE0CN) to select block write mode.

- Step 3. Set the PSWE bit (register PSCTL).

- Step 4. Clear the PSEE bit (register PSCTL).

- Step 5. Write the first key code to FLKEY: 0xA5.

- Step 6. Write the second key code to FLKEY: 0xF1.

- Step 7. Using the MOVX instruction, write the first data byte to the even block location (ending in 0b).

- Step 8. Write the first key code to FLKEY: 0xA5.

- Step 9. Write the second key code to FLKEY: 0xF1.

- Step 10. Using the MOVX instruction, write the second data byte to the odd block location (ending in 1b).

- Step 11. Clear the PSWE bit.

- Step 12. Re-enable interrupts.

Steps 5–10 must be repeated for each block to be written.

## **13.3.** Configuring the External Memory Interface

Configuring the External Memory Interface consists of five steps:

- 1. Configure the Output Modes of the associated port pins as either push-pull or open-drain (push-pull is most common), and skip the associated pins in the crossbar.

- 2. Configure Port latches to "park" the EMIF pins in a dormant state (usually by setting them to logic '1').

- 3. Select Multiplexed mode or Non-multiplexed mode.

- 4. Select the memory mode (on-chip only, split mode without bank select, split mode with bank select, or off-chip only).

- 5. Set up timing to interface with off-chip memory or peripherals.

Each of these five steps is explained in detail in the following sections. The Port selection, Multiplexed mode selection, and Mode bits are located in the EMI0CF register shown in SFR Definition 13.2.

#### 13.4. Port Configuration

The External Memory Interface appears on Ports 4, 3, 2, and 1 when it is used for off-chip memory access. When the EMIF is used, the Crossbar should be configured to skip over the control lines P1.7 (WR), P1.6 ( $\overline{RD}$ ), and if multiplexed mode is selected P1.3 (ALE) using the P1SKIP register. For more information about configuring the Crossbar, see Section "Figure 15.1. Port I/O Functional Block Diagram (Port 0 through Port 3)" on page 142.

The External Memory Interface claims the associated Port pins for memory operations ONLY during the execution of an off-chip MOVX instruction. Once the MOVX instruction has completed, control of the Port pins reverts to the Port latches or to the Crossbar settings for those pins. See Section "15. Port Input/ Output" on page 142 for more information about the Crossbar and Port operation and configuration. The Port latches should be explicitly configured to 'park' the External Memory Interface pins in a dormant state, most commonly by setting them to a logic 1.

During the execution of the MOVX instruction, the External Memory Interface will explicitly disable the drivers on all Port pins that are acting as Inputs (Data[7:0] during a READ operation, for example). The Output mode of the Port pins (whether the pin is configured as Open-Drain or Push-Pull) is unaffected by the External Memory Interface operation, and remains controlled by the PnMDOUT registers. In most cases, the output modes of all EMIF pins should be configured for push-pull mode.

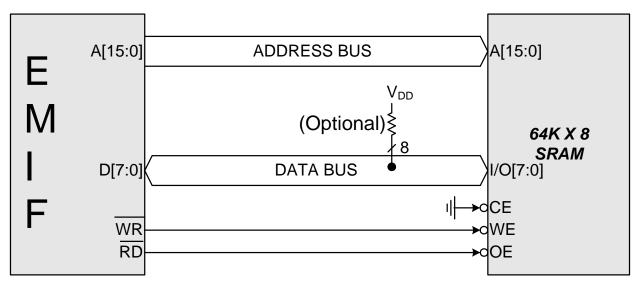

#### 13.5.2. Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Non-multiplexed Configuration is shown in Figure 13.3. See **Section "13.7.1. Non-multiplexed Mode" on page 124** for more information about Non-multiplexed operation.

Figure 13.3. Non-multiplexed Configuration Example

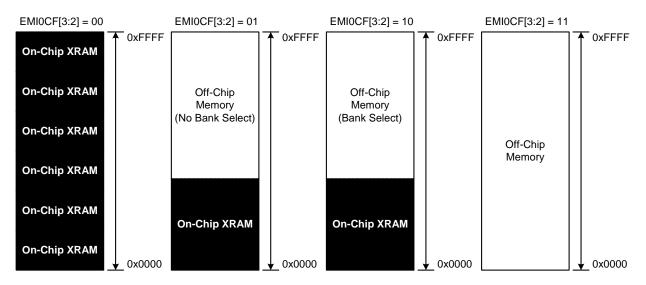

## 13.6. Memory Mode Selection

The external data memory space can be configured in one of four modes, shown in Figure 13.4, based on the EMIF Mode bits in the EMIOCF register (SFR Definition 13.2). These modes are summarized below. More information about the different modes can be found in **Section "13.7. Timing" on page 122**.

Figure 13.4. EMIF Operating Modes

| SFR Definition 14.4 | . OSCXCN: External | <b>Oscillator Control</b> |

|---------------------|--------------------|---------------------------|

|---------------------|--------------------|---------------------------|

|                   |             | R/W                                            | R/W          | R             | R/W                     | R/W   | R/W        | Reset Value |

|-------------------|-------------|------------------------------------------------|--------------|---------------|-------------------------|-------|------------|-------------|

| XTLVLD            | XOSCM       | D2 XOSCMD1                                     | XOSCMD0      | -             | XFCN2                   | XFCN1 | XFCN0      | 00000000    |

| Bit7              | Bit6        | Bit5                                           | Bit4         | Bit3          | Bit2                    | Bit1  | Bit0       | SFR Address |

|                   |             |                                                |              |               |                         |       |            | 0xB1        |

| Bit7:             |             | Crystal Occillat                               | or Valid Ela | a             |                         |       |            |             |

| DILT.             |             | Crystal Oscillat<br>Ily when XOSCI             |              | ıy.           |                         |       |            |             |

|                   |             | l Oscillator is ur                             |              | t vet stable. |                         |       |            |             |

|                   |             | l Oscillator is ru                             |              |               |                         |       |            |             |

| Bits6-4:          | •           | 02–0: External (                               | -            |               |                         |       |            |             |

|                   | 00x: Exte   | ernal Oscillator o                             | circuit off. |               |                         |       |            |             |

|                   | 010: Exte   | ernal CMOS Clo                                 | ck Mode.     |               |                         |       |            |             |

|                   |             | ernal CMOS Clo                                 |              | th divide by  | v 2 stage.              |       |            |             |

|                   |             | Oscillator Mode                                |              |               |                         |       |            |             |

|                   | •           | acitor Oscillator                              |              |               |                         |       |            |             |

|                   |             | stal Oscillator M                              |              |               |                         |       |            |             |

| D:+2.             |             | tal Oscillator M                               |              |               | age.                    |       |            |             |

| Bit3:<br>Bits2–0: |             | ED. Read = 0, <sup>v</sup><br>D: External Osci |              |               | ol Rite                 |       |            |             |

| DIISZ-U.          |             | See table belov                                | •            | iency Contr   | OI DIIS.                |       |            |             |

|                   |             |                                                |              |               |                         |       |            |             |

|                   |             | Crystal (XOSC                                  | ,            |               | CMD = 10x)              |       | CMD = 10   | <)          |

|                   | 000         | f ≤ 32 kł                                      |              | f ≤ 25        |                         |       | tor = 0.87 |             |

|                   | 001         | 32 kHz < f ≤                                   |              |               | f ≤ 50 kHz              |       | ctor = 2.6 |             |

|                   | 010         | 84 kHz < f ≤ 2                                 |              |               | ≤ 100 kHz               |       | ctor = 7.7 |             |

|                   | 011         | 225 kHz < f ≤                                  |              |               | f ≤ 200 kHz             |       | ctor = 22  |             |

|                   | 100         | 590 kHz < f ≤                                  |              |               | f ≤ 400 kHz             |       | ctor = 65  |             |

|                   | 101         | 1.5 MHz < f ≤                                  |              |               | f ≤ 800 kHz             |       | tor = 180  |             |

|                   | 110         | 4 MHz < f ≤ 1                                  |              |               | f ≤ 1.6 MHz             |       | ctor = 664 |             |

|                   | 111         | 10 MHz < f ≤                                   | 30 MHz       | 1.6 MHz <     | $f \le 3.2 \text{ MHz}$ | K Fac | tor = 1590 |             |

| CRYSTA            | L MODE (    | Circuit from Fig                               | ure 14.1, O  | ption 1; XO   | SCMD = 11               | x)    |            |             |

|                   | •           | KFCN value to r                                |              | •             |                         | ,     |            |             |

|                   |             |                                                |              |               |                         |       |            |             |

| RC MOD            | •           | from Figure 14.                                | •            |               | •                       |       |            |             |

|                   |             | KFCN value to r                                | •            | ency range    | :                       |       |            |             |

|                   |             | 10 <sup>3</sup> ) / (R x C), w                 |              |               |                         |       |            |             |

|                   |             | ency of clock in                               |              |               |                         |       |            |             |

|                   | •           | citor value in pF                              |              |               |                         |       |            |             |

|                   | K = Pull-   | up resistor value                              | e in κΩ      |               |                         |       |            |             |

|                   | (Circuit fr | om Figure 14.1,                                | Ontion 2. V  | ( <u>)</u>    | 10v)                    |       |            |             |

|                   |             | K Factor (KF) fo                               |              |               |                         |       |            |             |

|                   |             | C x V <sub>DD</sub> ), where                   |              | aon neque     | ity uconeu.             |       |            |             |

|                   | -           | ency of clock in                               |              |               |                         |       |            |             |

|                   | •           | citor value the >                              |              | ηpF           |                         |       |            |             |

|                   |             | ower Supply on                                 |              |               |                         |       |            |             |

|                   |             |                                                |              |               |                         |       |            |             |

| R/W   | R/W                                           | R/W                      | R/W              | R/W            | R/W       | R/W   | R/W   | Reset Value  |  |  |  |  |

|-------|-----------------------------------------------|--------------------------|------------------|----------------|-----------|-------|-------|--------------|--|--|--|--|

| CP1AE |                                               | CPOAE                    | CP0E             | SYSCKE         | SMB0E     | SPIOE | URTOE | 00000000     |  |  |  |  |

| Bit7  | Bit6                                          | Bit5                     | Bit4             | Bit3           | Bit2      | Bit1  | Bit0  | SFR Address: |  |  |  |  |

| DIL7  | DILO                                          | БЦЭ                      | DIL4             | BIIS           | DILZ      | DILI  | DILU  | OxE1         |  |  |  |  |

|       |                                               |                          |                  |                |           |       |       | UXEI         |  |  |  |  |

| Bit7: | CP1AE: Comparator1 Asynchronous Output Enable |                          |                  |                |           |       |       |              |  |  |  |  |

| Ditr. | 0: Asynchroi                                  | •                        |                  | •              |           |       |       |              |  |  |  |  |

|       | 1: Asynchro                                   |                          |                  |                |           |       |       |              |  |  |  |  |

| Bit6: | CP1E: Com                                     |                          |                  | •              |           |       |       |              |  |  |  |  |

|       | 0: CP1 unav                                   |                          | •                |                |           |       |       |              |  |  |  |  |

|       | 1: CP1 route                                  | ed to Port pi            | n.               |                |           |       |       |              |  |  |  |  |

| Bit5: | CP0AE: Cor                                    | nparator0 <sup>•</sup> A | synchrono        | us Output E    | nable     |       |       |              |  |  |  |  |

|       | 0: Asynchro                                   | nous CP0 u               | navailable       | at Port pin.   |           |       |       |              |  |  |  |  |

|       | 1: Asynchro                                   | nous CP0 re              | outed to Po      | ort pin.       |           |       |       |              |  |  |  |  |

| Bit4: | CP0E: Com                                     | parator0 Ou              | tput Enable      | e              |           |       |       |              |  |  |  |  |

|       | 0: CP0 unav                                   |                          |                  |                |           |       |       |              |  |  |  |  |

|       | 1: CP0 route                                  |                          |                  |                |           |       |       |              |  |  |  |  |

| Bit3: | SYSCKE: /S                                    |                          | •                |                |           |       |       |              |  |  |  |  |

|       | 0: /SYSCLK                                    |                          |                  |                |           |       |       |              |  |  |  |  |

|       | 1: /SYSCLK                                    |                          |                  | oin.           |           |       |       |              |  |  |  |  |

| Bit2: | SMB0E: SM                                     |                          |                  |                |           |       |       |              |  |  |  |  |

|       | 0: SMBus I/                                   |                          | •                | ins.           |           |       |       |              |  |  |  |  |

| DIM   | 1: SMBus I/                                   |                          | Port pins.       |                |           |       |       |              |  |  |  |  |

| Bit1: | SPI0E: SPI                                    |                          | • D = = • = := = |                |           |       |       |              |  |  |  |  |

|       | 0: SPI I/O ur                                 |                          | •                |                |           |       |       |              |  |  |  |  |

| Dit0. | 1: SPI I/O ro                                 |                          | •                |                |           |       |       |              |  |  |  |  |

| Bit0: | URT0E: UAI<br>0: UART0 I/                     |                          | •                |                |           |       |       |              |  |  |  |  |

|       | 1: UARTO T                                    |                          |                  |                | nd P0 5   |       |       |              |  |  |  |  |

|       | 1. UAILIO I.                                  | λυ, πλυ ΙΟ <b>ι</b>      |                  | . pins r 0.4 a | nu r 0.J. |       |       |              |  |  |  |  |

|       |                                               |                          |                  |                |           |       |       |              |  |  |  |  |

## SFR Definition 15.1. XBR0: Port I/O Crossbar Register 0

## Table 15.1. Port I/O DC Electrical Characteristics

#### $V_{DD}$ = 2.7 to 3.6 V, -40 to +85 °C unless otherwise specified

| Parameters            | Conditions                                   | Min                   | Тур                   | Max | Units |

|-----------------------|----------------------------------------------|-----------------------|-----------------------|-----|-------|

|                       | I <sub>OH</sub> = –3 mA, Port I/O push-pull  | V <sub>DD</sub> – 0.7 |                       |     |       |

| Output High Voltage   | $I_{OH} = -10 \ \mu A$ , Port I/O push-pull  | V <sub>DD</sub> – 0.1 |                       |     | V     |

|                       | I <sub>OH</sub> = –10 mA, Port I/O push-pull |                       | V <sub>DD</sub> – 0.8 |     |       |

|                       | I <sub>OL</sub> = 8.5 mA                     |                       |                       | 0.6 |       |

| Output Low Voltage    | I <sub>OL</sub> = 10 μA                      |                       |                       | 0.1 | V     |

|                       | I <sub>OL</sub> = 25 mA                      |                       | 1.0                   |     |       |

| Input High Voltage    |                                              | 2.0                   |                       |     | V     |

| Input Low Voltage     |                                              |                       |                       | 0.8 | V     |

| Input Leakage Current | Weak Pull-up Off                             |                       |                       | ±1  | μA    |

| Input Leakage Cullent | Weak Pull-up On, V <sub>IN</sub> = 0 V       |                       | 25                    | 50  | μΑ    |

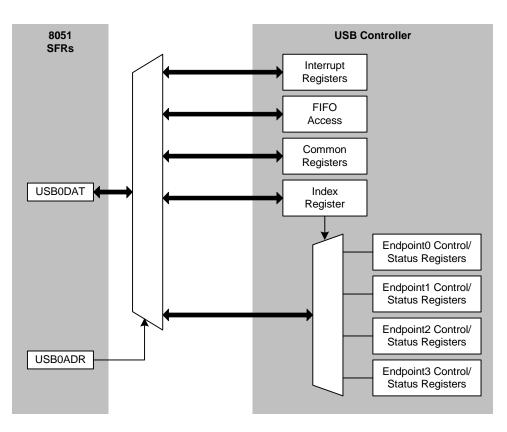

by reads/writes of the USB0DAT register. See Figure 16.2.

Endpoint control/status registers are accessed by first writing the USB register INDEX with the target endpoint number. Once the target endpoint number is written to the INDEX register, the control/status registers associated with the target endpoint may be accessed. See the "Indexed Registers" section of Table 16.2 for a list of endpoint control/status registers.

Important Note: The USB clock must be active when accessing USB registers.

Figure 16.2. USB0 Register Access Scheme

### USB Register Definition 16.8. POWER: USB0 Power

| R/W   | R/W                             | R/W          | R/W           | R/W           | R/W             | R            | R/W           | Reset Value        |

|-------|---------------------------------|--------------|---------------|---------------|-----------------|--------------|---------------|--------------------|

| ISOUD | -                               | -            | USBINH        | USBRST        | RESUME          | SUSMD        | SUSEN         | 00010000           |

| Bit7  | Bit6                            | Bit5         | Bit4          | Bit3          | Bit2            | Bit1         | Bit0          | USB Addres<br>0x01 |

| Bit7: | ISOUD: ISO                      | •            |               |               |                 |              |               |                    |

|       | This bit affect                 |              |               |               |                 |              |               |                    |

|       | 0: When soft                    | ware write   | s INPRDY =    | : '1', USB0 \ | vill send the   | packet wh    | en the next   | IN token is        |

|       | received.<br>1: When soft       | ware write   | s INPRDY -    | - '1' USB0 y  | will wait for a | a SOE toke   | n hefore se   | anding the         |

|       | packet. If an                   |              |               |               |                 |              |               |                    |

|       | ,<br>packet.                    |              |               |               | ,               |              |               | 0                  |

|       | Unused. Rea                     |              | Vrite = don't | care.         |                 |              |               |                    |

| Bit4: | USBINH: US                      |              |               |               |                 |              |               | react (coo         |

|       | This bit is se<br>Bit3: RESET   |              |               |               |                 |              |               |                    |

|       | complete. So                    | ,            |               |               |                 |              |               | 1201101113         |

|       | 0: USB0 ena                     |              |               |               |                 |              |               |                    |

|       | 1: USB0 inhi                    |              |               | ignored.      |                 |              |               |                    |

| Bit3: | USBRST: Re                      |              |               |               |                 |              | 1.26 1.1.     |                    |

|       | Writing '1' to status inform    |              | ces an asynd  | chronous U    | SBU reset. H    | ceading this | s bit provide | es dus rese        |

|       | Read:                           |              |               |               |                 |              |               |                    |

|       | 0: Reset sigr                   | naling is no | ot present or | n the bus.    |                 |              |               |                    |

|       | 1: Reset sigr                   |              |               | bus.          |                 |              |               |                    |

| Bit2: | RESUME: F                       |              |               |               |                 |              |               |                    |

|       | Software car<br>a '1' to this b |              |               |               |                 |              |               |                    |

|       | naling on the                   |              |               |               |                 |              |               |                    |

|       | 10 ms to15 r                    |              |               |               |                 |              |               |                    |

|       | SUSMD, wh                       |              |               | SUME = '0'.   |                 |              |               |                    |

| Bit1: | SUSMD: Su                       |              |               |               |                 |              |               |                    |

|       | Set to '1' by ware writes I     |              |               |               |                 |              |               |                    |

|       | detection of                    |              | ``            | •             | wallcup) of     |              | owner reg     |                    |

|       | 0: USB0 not                     |              | • •           |               |                 |              |               |                    |

|       | 1: USB0 in s                    |              |               |               |                 |              |               |                    |

| Bit0: | SUSEN: Sus                      |              |               |               |                 | alama Barra  |               |                    |

|       | 0: Suspend of 1: Suspend of     |              |               |               |                 |              |               | nd signalin        |

|       | 1. Suspend (                    |              |               |               |                 |              | 2013 303081   |                    |

#### 17.3.2. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 17.3.3. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMB0CF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 17.3.4. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50 µs, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods. If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. Note that a clock source is required for free timeout detection, even in a slave-only implementation.

### 17.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

SMBus interrupts are generated for each data byte or slave address that is transferred. When transmitting, this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data, this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. See **Section "17.5. SMBus Transfer Modes" on page 198** for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in **Section "17.4.2. SMB0CN Control Register" on page 195**; Table 17.4 provides a quick SMB0CN decoding reference.

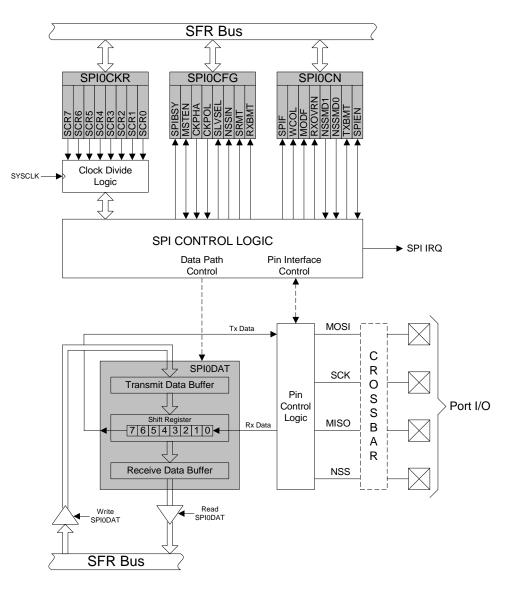

## 20. Enhanced Serial Peripheral Interface (SPI0)

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

Figure 20.1. SPI Block Diagram

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W                              | R/W        | R/W  | R/W     | R/W  | R/W  | R/W  | Reset Value |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------|------|---------|------|------|------|-------------|--|--|--|--|

| SCR7                                                                                                                                                                                                                                                                                                                                                                                                                                        | SCR6                             | SCR5       | SCR4 | SCR3    | SCR2 | SCR1 | SCR0 | 0000000     |  |  |  |  |

| Bit7                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit6                             | Bit5       | Bit4 | Bit3    | Bit2 | Bit1 | Bit0 | _           |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | SFR Address: 0xA2                |            |      |         |      |      |      |             |  |  |  |  |

| Bits 7–0: SCR7–SCR0: SPI0 Clock Rate.<br>These bits determine the frequency of the SCK output when the SPI0 module is configured<br>for master mode operation. The SCK clock frequency is a divided version of the system<br>clock, and is given in the following equation, where SYSCLK is the system clock frequency<br>and SPI0CKR is the 8-bit value held in the SPI0CKR register.<br>$f_{SCK} = \frac{SYSCLK}{2 \times (SPI0CKR + 1)}$ |                                  |            |      |         |      |      |      |             |  |  |  |  |

| fo                                                                                                                                                                                                                                                                                                                                                                                                                                          | or 0 <= SPI                      | 0CKR <= 2  | 55   |         |      |      |      |             |  |  |  |  |

| Example: If                                                                                                                                                                                                                                                                                                                                                                                                                                 | SYSCLK =                         | 2 MHz 200  |      | - 0×04  |      |      |      |             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3130LK =                         |            |      | = 0x04, |      |      |      |             |  |  |  |  |

| $f_{SCK} =$<br>$f_{SCK} = 2$                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{2000000}{2 \times (4+1)}$ | <u>)</u> ) |      |         |      |      |      |             |  |  |  |  |

## SFR Definition 20.3. SPI0CKR: SPI0 Clock Rate

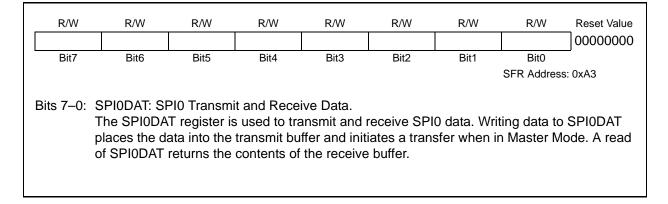

## SFR Definition 20.4. SPI0DAT: SPI0 Data

Rev. 1.3