Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 48MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 21x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 32-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f343-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### List of Figures

| 1. System Overview                                                            |    |

|-------------------------------------------------------------------------------|----|

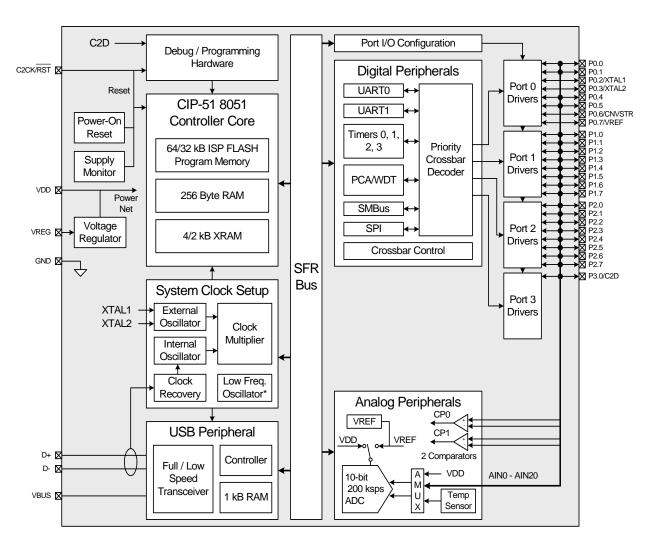

| Figure 1.1. C8051F340/1/4/5 Block Diagram                                     | 19 |

| Figure 1.2. C8051F342/3/6/7 Block Diagram                                     | 20 |

| Figure 1.3. C8051F348/C Block Diagram                                         |    |

| Figure 1.4. C8051F349/D Block Diagram                                         |    |

| Figure 1.5. C8051F34A/B Block Diagram                                         | 23 |

| 4. Pinout and Package Definitions                                             |    |

| Figure 4.1. TQFP-48 Pinout Diagram (Top View)                                 | 31 |

| Figure 4.2. TQFP-48 Package Diagram                                           |    |

| Figure 4.3. TQFP-48 Recommended PCB Land Pattern                              |    |

| Figure 4.4. LQFP-32 Pinout Diagram (Top View)                                 |    |

| Figure 4.5. LQFP-32 Package Diagram                                           |    |

| Figure 4.6. LQFP-32 Recommended PCB Land Pattern                              | 36 |

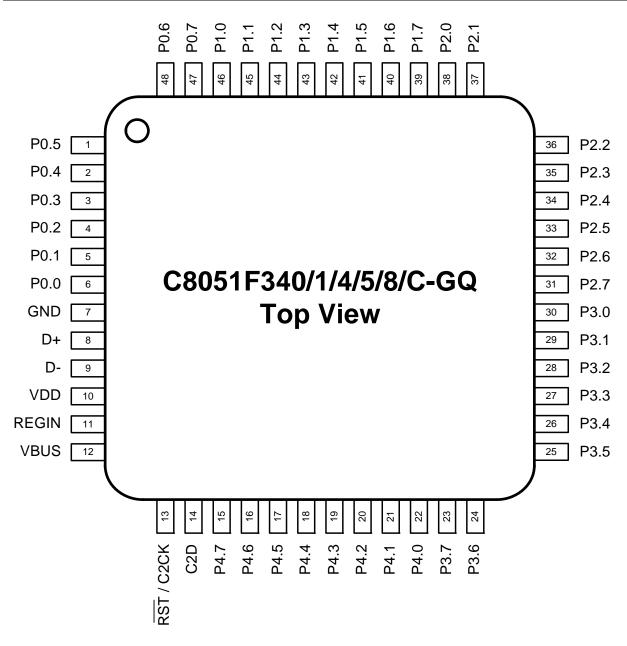

| Figure 4.7. QFN-32 Pinout Diagram (Top View)                                  |    |

| 5. 10-Bit ADC (ADC0, C8051F340/1/2/3/4/5/6/7/A/B Only)                        |    |

| Figure 5.1. ADC0 Functional Block Diagram                                     | 41 |

| Figure 5.2. Temperature Sensor Transfer Function                              | 43 |

| Figure 5.3. Temperature Sensor Error with 1-Point Calibration (VREF = 2.40 V) | 44 |

| Figure 5.4. 10-Bit ADC Track and Conversion Example Timing                    | 46 |

| Figure 5.5. ADC0 Equivalent Input Circuits                                    | 47 |

| Figure 5.6. ADC Window Compare Example: Right-Justified Single-Ended Data     | 54 |

| Figure 5.7. ADC Window Compare Example: Left-Justified Single-Ended Data      | 54 |

| Figure 5.8. ADC Window Compare Example: Right-Justified Differential Data     | 55 |

| Figure 5.9. ADC Window Compare Example: Left-Justified Differential Data      | 55 |

| 6. Voltage Reference (C8051F340/1/2/3/4/5/6/7/A/B Only)                       |    |

| Figure 6.1. Voltage Reference Functional Block Diagram                        | 57 |

| 7. Comparators                                                                |    |

| Figure 7.1. Comparator Functional Block Diagram                               | 60 |

| Figure 7.2. Comparator Hysteresis Plot                                        |    |

| 8. Voltage Regulator (REG0)                                                   |    |

| Figure 8.1. REG0 Configuration: USB Bus-Powered                               |    |

| Figure 8.2. REG0 Configuration: USB Self-Powered                              | 70 |

| Figure 8.3. REG0 Configuration: USB Self-Powered, Regulator Disabled          | 71 |

| Figure 8.4. REG0 Configuration: No USB Connection                             | 71 |

| 9. CIP-51 Microcontroller                                                     |    |

| Figure 9.1. CIP-51 Block Diagram                                              | 73 |

| Figure 9.2. On-Chip Memory Map for 64 kB Devices                              |    |

| Figure 9.3. On-Chip Memory Map for 32 kB Devices                              | 80 |

| 11. Reset Sources                                                             |    |

| Figure 11.1. Reset Sources 1                                                  |    |

| Figure 11.2. Power-On and VDD Monitor Reset Timing 1                          | 01 |

Figure 1.5. C8051F34A/B Block Diagram

Figure 4.1. TQFP-48 Pinout Diagram (Top View)

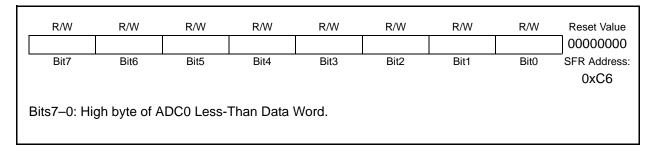

#### SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte

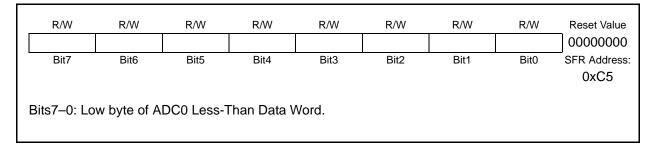

### SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte

| SFR Definition 9.11. EIE2: Extended Interrupt Enable 2 |

|--------------------------------------------------------|

|--------------------------------------------------------|

| R/W                        | R/W                                                                                                                                       | R/W                                                                                             | R/W                                                                        | R/W                                | R/W       | R/W  | R/W   | Reset Value  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------|-----------|------|-------|--------------|

| -                          | -                                                                                                                                         | -                                                                                               | -                                                                          | -                                  | -         | ES1  | EVBUS | 00000000     |

| Bit7                       | Bit6                                                                                                                                      | Bit5                                                                                            | Bit4                                                                       | Bit3                               | Bit2      | Bit1 | Bit0  | SFR Address: |

|                            |                                                                                                                                           |                                                                                                 |                                                                            |                                    |           |      |       | 0xE7         |

| Bits7–2:<br>Bit1:<br>Bit0: | UNUSED. R<br>ES1: Enable<br>This bit sets<br>0: Disable U<br>1: Enable U<br>EVBUS: Ena<br>This bit sets<br>0: Disable al<br>1: Enable int | UART1 Int<br>the maskin<br>ART1 intern<br>ART1 intern<br>able VBUS<br>the maskin<br>I VBUS inte | errupt.<br>g of the UA<br>upt.<br>Level Interri<br>g of the VB<br>errupts. | RT1 interru<br>upt.<br>US interrup | pt.<br>t. | ISE. |       |              |

### SFR Definition 9.12. EIP2: Extended Interrupt Priority 2

| R/W                        | R/W                                                                                                                                     | R/W                                                                                                          | R/W                                                                                                         | R/W                                                                                            | R/W  | R/W  | R/W   | Reset Value  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|-------|--------------|

| -                          | -                                                                                                                                       | -                                                                                                            | -                                                                                                           | -                                                                                              | -    | PS1  | PVBUS | 0000000      |

| Bit7                       | Bit6                                                                                                                                    | Bit5                                                                                                         | Bit4                                                                                                        | Bit3                                                                                           | Bit2 | Bit1 | Bit0  | SFR Address: |

|                            |                                                                                                                                         |                                                                                                              |                                                                                                             |                                                                                                |      |      |       | 0xF7         |

| Bits7–2:<br>Bit1:<br>Bit0: | UNUSED. R<br>PS1: UART1<br>This bit sets<br>0: UART1 int<br>1: UART1 int<br>PVBUS: VBU<br>This bit sets<br>0: VBUS inte<br>1: VBUS inte | Interrupt F<br>the priority<br>terrupt set t<br>terrupts set<br>JS Level In<br>the priority<br>errupt set to | Priority Cont<br>of the UAR<br>o low priorit<br>to high prior<br>terrupt Prio<br>of the VBU<br>low priority | rol.<br>T1 interrupt<br>ty level.<br>prity level.<br>rity Control.<br>S interrupt.<br>y level. |      |      |       |              |

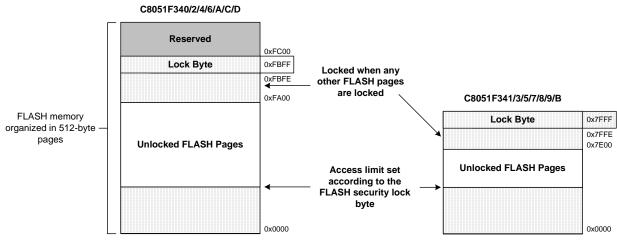

Figure 12.1. Flash Program Memory Map and Security Byte

| R/W      | R/W                           | R/W         | R/W         | R/W           | R/W          | R/W            | R/W          | Reset Value  |  |  |  |

|----------|-------------------------------|-------------|-------------|---------------|--------------|----------------|--------------|--------------|--|--|--|

| -        | USBFAE                        | -           | EMD2        | EMD1          | EMD0         | EALE1          | EALE0        | 00000011     |  |  |  |

| Bit7     | Bit6                          | Bit5        | Bit4        | Bit3          | Bit2         | Bit1           | Bit0         | -            |  |  |  |

|          | SFR Address: 0x85             |             |             |               |              |                |              |              |  |  |  |

|          |                               |             |             |               |              |                |              |              |  |  |  |

| Bit7:    | Unused. Rea                   |             |             |               |              |                |              |              |  |  |  |

| Bit6:    | USBFAE: US                    |             |             |               |              |                |              |              |  |  |  |

|          | 0: USB FIFO                   |             |             | •             |              |                |              | he menned    |  |  |  |

|          | 1: USB FIFO<br>in XRAM spa    |             |             |               |              |                |              |              |  |  |  |

|          | greater than                  |             |             |               |              |                |              |              |  |  |  |

|          | area with M                   |             |             | OTOOLI        |              | 2 × 0100       |              | 033 (113     |  |  |  |

| Bit5:    | Unused. Rea                   |             |             | care.         |              |                |              |              |  |  |  |

| Bit4:    | EMD2: EMIF                    |             |             |               |              |                |              |              |  |  |  |

|          | 0: EMIF oper                  | •           |             |               | mode.        |                |              |              |  |  |  |

|          | 1: EMIF oper                  |             |             |               | parate add   | ress and da    | ita pins).   |              |  |  |  |

| Bits3-2: | EMD1-0: EN                    |             | •           |               |              |                |              |              |  |  |  |

|          | These bits co                 |             |             |               |              |                |              |              |  |  |  |

|          | 00: Internal C                |             |             | on-chip XR    | AM only. Al  | Il effective a | addresses a  | alias to     |  |  |  |

|          | on-chip mem                   |             |             | A             | ь            |                |              |              |  |  |  |

|          | 01: Split Mod                 |             |             |               |              |                |              |              |  |  |  |

|          | directed on-c<br>off-chip MOV |             |             |               |              |                |              |              |  |  |  |

|          | resolve uppe                  |             |             |               |              |                |              |              |  |  |  |

|          | set to a page                 |             |             |               |              |                |              |              |  |  |  |

|          | 10: Split Mod                 |             |             |               | •            |                | boundary a   | are directed |  |  |  |

|          | on-chip. Acce                 |             |             |               |              |                |              |              |  |  |  |

|          | MOVX opera                    | tions use t | he contents | of EMI0CN     | I to determi | ne the high    | -byte of the | address.     |  |  |  |

|          | 11: External (                | Only: MOV   | X accesses  | s off-chip XF | RAM only. C  | n-chip XRA     | AM is not vi | sible to the |  |  |  |

|          | CPU.                          |             |             |               |              |                |              |              |  |  |  |

| Bits1–0: | EALE1-0: AL                   |             |             |               |              |                | = 0).        |              |  |  |  |

|          | 00: ALE high                  |             |             |               |              |                |              |              |  |  |  |

|          | 01: ALE high                  |             |             |               |              |                |              |              |  |  |  |

|          | 10: ALE high<br>11: ALE high  |             |             |               |              |                |              |              |  |  |  |

|          |                               |             | ow puise wi | uui – 4 0 I C |              | 0.             |              |              |  |  |  |

|          |                               |             |             |               |              |                |              |              |  |  |  |

#### 13.5. Multiplexed and Non-multiplexed Selection

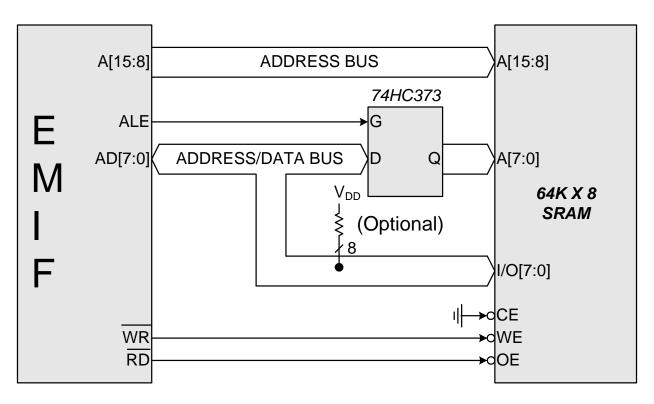

The External Memory Interface is capable of acting in a Multiplexed mode or a Non-multiplexed mode, depending on the state of the EMD2 (EMI0CF.4) bit.

#### 13.5.1. Multiplexed Configuration

In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 13.2.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the 'Q' outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time RD or WR is asserted.

See Section "13.7.2. Multiplexed Mode" on page 127 for more information.

Figure 13.2. Multiplexed Configuration Example

#### SFR Definition 14.3. OSCLCN: Internal L-F Oscillator Control

| R/W                                                                                                                                                                                                                                                                    | R                                                                                                                                                                                                                                            | R/W  | R      | R/W    | R/W    | R/W    | R/W    | Reset Value  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|--------|--------|--------|--------------|--|--|

| -                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                              |      |        |        |        |        |        |              |  |  |

| OSCLEN                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |      | OSCLF2 | OSCLF1 | OSCLF0 | OSCLD1 | OSCLD0 | 00vvvv00     |  |  |

| Bit7                                                                                                                                                                                                                                                                   | Bit6                                                                                                                                                                                                                                         | Bit5 | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   | SFR Address: |  |  |

|                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                              |      |        |        |        |        |        | 0x86         |  |  |

| Bit7:                                                                                                                                                                                                                                                                  | 0: Internal L-F Oscillator Disabled.                                                                                                                                                                                                         |      |        |        |        |        |        |              |  |  |

| Bit6:                                                                                                                                                                                                                                                                  | 1: Internal L-F Oscillator Enabled.     OSCLRDY: Internal L-F Oscillator Ready Flag.     0: Internal L-F Oscillator frequency not stabilized.     1: Internal L-F Oscillator frequency stabilized.                                           |      |        |        |        |        |        |              |  |  |

| Bits5–2: OSCLF[3:0]: Internal L-F Oscillator Frequency Control bits.<br>Fine-tune control bits for the internal L-F Oscillator frequency. When set to 0000b, the L-F oscillator operates at its fastest setting. When set to 1111b, the L-F oscillator operates at its |                                                                                                                                                                                                                                              |      |        |        |        |        |        |              |  |  |

| Bits1–0:                                                                                                                                                                                                                                                               | <ul> <li>slowest setting.</li> <li>OSCLD[1:0]: Internal L-F Oscillator Divider Select.</li> <li>00: Divide by 8 selected.</li> <li>01: Divide by 4selected.</li> <li>10: Divide by 2 selected.</li> <li>11: Divide by 1 selected.</li> </ul> |      |        |        |        |        |        |              |  |  |

|                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                              |      |        |        |        |        |        |              |  |  |

| SFR Definition | 15.8. P1: | Port1 Latch |

|----------------|-----------|-------------|

|----------------|-----------|-------------|

| R/W      | R/W<br>P1.6                                                                                                                 | R/W<br>P1.5                                                              | R/W<br>P1.4                               | R/W<br>P1.3                  | R/W<br>P1.2 | R/W<br>P1.1  | R/W<br>P1.0           | Reset Value<br>11111111 |

|----------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------|------------------------------|-------------|--------------|-----------------------|-------------------------|

| Bit7     | Bit6                                                                                                                        | Bit5                                                                     | Bit4                                      | Bit3                         | Bit2        | Bit1<br>(bit | Bit0<br>t addressable | SFR Address:<br>0x90    |

| Bits7–0: | P1.[7:0]<br>Write - Outp<br>0: Logic Low<br>1: Logic Higl<br>Read - Alwa<br>pin when co<br>0: P1.n pin is<br>1: P1.n pin is | / Output.<br>h Output (hi<br>ys reads '0'<br>nfigured as<br>s logic low. | gh impedar<br>if selected<br>digital inpu | nce if corres<br>as analog i | ponding P1  | MDOUT.n l    | bit = 0).             |                         |

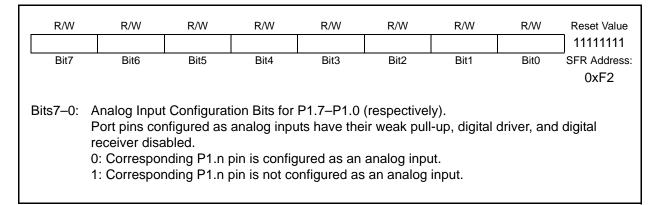

#### SFR Definition 15.9. P1MDIN: Port1 Input Mode

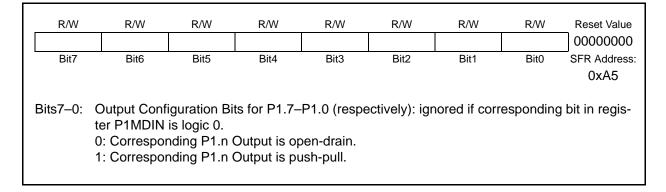

#### SFR Definition 15.10. P1MDOUT: Port1 Output Mode

| R/W                         | R/W                                                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                           | R/W                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                           | R/W                                                                                                                         | R/W                                                                                                                        | R/W                                                                                                      | Reset Value                                                                            |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

| BUSY                        |                                                                                                                                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                           | <b>K</b> /W                                                                                                                                                                                                                                         |                                                                                                                                                                                                                               |                                                                                                                             | R/W                                                                                                                        | K/ VV                                                                                                    | 00000000                                                                               |  |  |

|                             |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                               |                                                                                                                             |                                                                                                                            |                                                                                                          |                                                                                        |  |  |

| Bit7                        | Bit6                                                                                                                                                                                                                                                                                                                                                | BIt5                                                                                                                                                                                                                          | Bit4                                                                                                                                                                                                                                                | BIt3                                                                                                                                                                                                                          | Bit2                                                                                                                        | BIT                                                                                                                        | Bit0                                                                                                     | SFR Address:                                                                           |  |  |

|                             |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                               |                                                                                                                             |                                                                                                                            |                                                                                                          | 0x96                                                                                   |  |  |

| Bits7:<br>Bit6:<br>Bits5–0: | BUSY: USB0<br>This bit is user<br>initiate a read<br>target address<br>set to '1', hard<br>USB0DAT reg<br>Write:<br>0: No effect.<br>1: A USB0 ind<br>Read:<br>0: USB0DAT r<br>1: USB0 is bu<br>AUTORD: US<br>This bit is use<br>0: BUSY must<br>1: The next in<br>USB0DAT (US<br>USBADDR: U<br>These bits hol<br>lists the USB0<br>will target the | d during ir<br>of the US<br>s and BUS<br>ware will<br>jister. Soft<br>lirect regis<br>register da<br>sy access<br>B0 Regis<br>d for bloc<br>t be writte<br>direct regis<br>SBADDR<br>SB0 Indir<br>d a 6-bit a<br>) core regis | adirect USB<br>B0 register<br>SY bit may b<br>clear BUSY<br>ware shoul<br>ster read is<br>ata is valid.<br>sing an indir<br>ter Auto-reat<br>k FIFO reat<br>n manually<br>ster read w<br>bits will not<br>ect Registe<br>ddress use<br>sters and th | 0 register ad<br>targeted by<br>be written in<br>' when the t<br>d check BU<br>initiated at t<br>rect register<br>ad Flag<br>ds.<br>for each US<br>ill automatic<br>be changed<br>r Address<br>d to indirect<br>heir indirect | the USBAI<br>the same v<br>argeted reg<br>SY for '0' be<br>he address<br>(USB0DAT<br>SB0 indirect<br>cally be initia<br>d). | DDR bits (U<br>vrite to USE<br>ister data is<br>efore writing<br>specified b<br>register da<br>register rea<br>ated when s | ISB0ADR.<br>B0ADR. Af<br>s ready in t<br>g to USB0I<br>by the USB<br>ta is invali-<br>ad.<br>software re | [5-0]). The<br>ter BUSY is<br>the<br>DAT.<br>ADDR bits.<br>d.<br>eads<br>s. Table 16.2 |  |  |

#### USB Register Definition 16.13. CMINT: USB0 Common Interrupt

| R        | R                                                           | R            | R          | R              | R            | R             | R           | Reset Value  |  |  |  |

|----------|-------------------------------------------------------------|--------------|------------|----------------|--------------|---------------|-------------|--------------|--|--|--|

| -        | -                                                           | -            | -          | SOF            | RSTINT       | RSUINT        | SUSINT      | 00000000     |  |  |  |

| Bit7     | Bit6                                                        | Bit5         | Bit4       | Bit3           | Bit2         | Bit1          | Bit0        | USB Address: |  |  |  |

|          |                                                             |              |            |                |              | 0x06          |             |              |  |  |  |

| Bits7–4: | Unused. Rea                                                 |              |            | n't care.      |              |               |             |              |  |  |  |

| Bit3:    | SOF: Start o                                                |              | •          |                |              |               |             |              |  |  |  |

|          | Set by hardw                                                |              |            |                |              |               |             |              |  |  |  |

|          | ware: an inte<br>the actual SC                              | •            | •          |                | ware expec   | ts to receive | e a SOF ev  | ent, even li |  |  |  |

|          | This bit is cle                                             |              |            |                | 1INT registe | ər.           |             |              |  |  |  |

|          | 0: SOF interi                                               |              |            |                |              |               |             |              |  |  |  |

|          | 1: SOF interi                                               | rupt active. |            |                |              |               |             |              |  |  |  |

| Bit2:    | RSTINT: Res                                                 |              |            |                |              |               |             |              |  |  |  |

|          | Set by hardw                                                |              |            |                |              |               |             |              |  |  |  |

|          | This bit is cle<br>0: Reset inte                            |              |            |                | invi registe | ÷1.           |             |              |  |  |  |

|          | 1: Reset inte                                               |              |            |                |              |               |             |              |  |  |  |

| Bit1:    | RSUINT: Re                                                  |              |            | g Flag         |              |               |             |              |  |  |  |

|          | Set by hardw mode.                                          | vare when I  | Resume sig | naling is de   | tected on th | ne bus while  | e USB0 is i | n suspend    |  |  |  |

|          | This bit is cleared when software reads the CMINT register. |              |            |                |              |               |             |              |  |  |  |

|          | 0: Resume interrupt inactive.                               |              |            |                |              |               |             |              |  |  |  |

| D:+0.    | 1: Resume in                                                |              |            | а <u>Г</u> Іаа |              |               |             |              |  |  |  |

| Bit0:    | SUSINT: Sus<br>When Suspe                                   |              |            |                | N in registe |               | this hit is | eet by bard- |  |  |  |

|          | ware when S                                                 |              |            |                |              |               |             |              |  |  |  |

|          | reads the CM                                                |              | •          |                |              |               |             |              |  |  |  |

|          | 0: Suspend i                                                | •            |            |                |              |               |             |              |  |  |  |

|          | 1: Suspend i                                                | nterrupt ac  | ive.       |                |              |               |             |              |  |  |  |

|          |                                                             |              |            |                |              |               |             |              |  |  |  |

#### USB Register Definition 16.21. EOUTCSRL: USB0 OUT Endpoint Control Low Byte

| W     | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W                                                                          | R/W                                                          | R                           | R/W                | R            | R/W          | Reset Value          |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------|--------------------|--------------|--------------|----------------------|--|--|--|--|

| CLRDT | STSTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SDSTL                                                                        | FLUSH                                                        | DATERR                      | OVRUN              | FIFOFUL      | OPRDY        | 00000000             |  |  |  |  |

| Bit7  | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit5                                                                         | Bit4                                                         | Bit3                        | Bit2               | Bit1         | Bit0         | USB Address:<br>0x14 |  |  |  |  |

| Bit7: | 7: CLRDT: Clear Data Toggle<br>Write: Software should write '1' to this bit to reset the OUT endpoint data toggle to '0'.<br>Read: This bit always reads '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              |                                                              |                             |                    |              |              |                      |  |  |  |  |

| Bit6: | STSTL: Sent Stall<br>Hardware sets this bit to '1' when a STALL handshake signal is transmitted. This flag must<br>be cleared by software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |                                                              |                             |                    |              |              |                      |  |  |  |  |

| Bit5: | SDSTL: Sen<br>Software sho<br>'0' to this bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ould write '1                                                                |                                                              | •                           |                    |              |              | nould write          |  |  |  |  |

| Bit4: | <ul> <li>'0' to this bit to terminate the STALL signal. This bit has no effect in ISO mode.</li> <li>FLUSH: FIFO Flush</li> <li>Writing a '1' to this bit flushes the next packet to be read from the OUT endpoint FIFO. The FIFO pointer is reset and the OPRDY bit is cleared. If the FIFO contains multiple packets, software must write '1' to FLUSH for each packet. Hardware resets the FLUSH bit to '0' when the FIFO flush is complete.</li> <li>Note: If data for the current packet has already been read from the FIFO, the FLUSH bit should not be used to flush the packet. Instead, the entire data packet should be read from the</li> </ul> |                                                                              |                                                              |                             |                    |              |              |                      |  |  |  |  |

| Bit3: | DATERR: Da<br>In ISO mode<br>It is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | e, this bit is a when softwa                                                 |                                                              |                             |                    |              |              | uffing error.        |  |  |  |  |

| Bit2: | OVRUN: Data Overrun<br>This bit is set by hardware when an incoming data packet cannot be loaded into the OUT<br>endpoint FIFO. This bit is only valid in ISO mode, and must be cleared by software.<br>0: No data overrun.                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                              |                                                              |                             |                    |              |              |                      |  |  |  |  |

| Bit1: | 1: A data packet was lost because of a full FIFO since this flag was last cleared.<br>FIFOFUL: OUT FIFO Full<br>This bit indicates the contents of the OUT FIFO. If double buffering is enabled for the end-<br>point (DBIEN = '1'), the FIFO is full when the FIFO contains two packets. If DBIEN = '0', the                                                                                                                                                                                                                                                                                                                                               |                                                                              |                                                              |                             |                    |              |              |                      |  |  |  |  |

| Bit0: | FIFO is full v<br>0: OUT endp<br>1: OUT endp<br>OPRDY: OU<br>Hardware se<br>ware should                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | when the Fl<br>point FIFO i<br>point FIFO i<br>T Packet R<br>ets this bit to | FO contain<br>s not full.<br>s full.<br>eady<br>o '1' and ge | s one packe<br>nerates an i | et.<br>nterrupt wh | en a data pa | acket is ava | ailable. Soft-       |  |  |  |  |

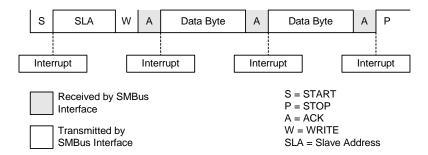

Figure 17.5. Typical Master Transmitter Sequence

|                    | Valu             | Values R                                                                     |                                                    | d |                                                    |                                                                                                 | Values<br>Written |     |     |

|--------------------|------------------|------------------------------------------------------------------------------|----------------------------------------------------|---|----------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------|-----|-----|

| Mode               | Status<br>Vector | ACKRQ                                                                        | ACKRQ<br>ARBLOST                                   |   | Current SMbus State                                | Typical Response Options                                                                        | STA               | STo | ACK |

|                    | 1110             | 0                                                                            | 0                                                  | х | A master START was generated.                      | Load slave address + R/W into SMB0DAT.                                                          | 0                 | 0   | х   |

|                    |                  | 0                                                                            | 0                                                  | 0 | A master data or address byte                      | Set STA to restart transfer.                                                                    | 1                 | 0   | Х   |

| Ē                  |                  | Ŭ                                                                            | U                                                  | Ŭ | was transmitted; NACK received.                    | Abort transfer.                                                                                 | 0                 | 1   | Х   |

| nsmitte            |                  |                                                                              |                                                    |   |                                                    | Load next data byte into SMB0DAT.                                                               | 0                 | 0   | х   |

| Tra                |                  |                                                                              |                                                    |   |                                                    | End transfer with STOP.                                                                         | 0                 | 1   | Х   |

| Master Transmitter | 1100             | 100<br>0 0 1 A master data or address byte<br>was transmitted; ACK received. | End transfer with STOP and start another transfer. | 1 | 1                                                  | х                                                                                               |                   |     |     |

| 2                  |                  |                                                                              |                                                    |   | was transmitted, ACI TECEIVEU.                     | Send repeated START.                                                                            | 1                 | 0   | Х   |

|                    |                  |                                                                              |                                                    |   |                                                    | Switch to Master Receiver<br>Mode (clear SI without writ-<br>ing new data to SMB0DAT).          | 0                 | 0   | x   |

|                    |                  |                                                                              |                                                    |   |                                                    | Acknowledge received byte;<br>Read SMB0DAT.                                                     | 0                 | 0   | 1   |

|                    |                  |                                                                              |                                                    |   |                                                    | Send NACK to indicate last byte, and send STOP.                                                 | 0                 | 0   | 0   |

|                    |                  |                                                                              |                                                    |   |                                                    | Send NACK to indicate last<br>byte, and send STOP fol-<br>lowed by START.                       | 1                 | 1   | 0   |

| ceiver             |                  |                                                                              |                                                    |   |                                                    | Send ACK followed by<br>repeated START.                                                         | 1                 | 0   | 1   |

| Master Receiver    | 1000             | 1                                                                            | 0                                                  | x | A master data byte was received;<br>ACK requested. | Send NACK to indicate last<br>byte, and send repeated<br>START.                                 | 1                 | 0   | 0   |

| Z                  |                  |                                                                              |                                                    |   |                                                    | Send ACK and switch to<br>Master Transmitter Mode<br>(write to SMB0DAT before<br>clearing SI).  | 0                 | 0   | 1   |

|                    |                  |                                                                              |                                                    |   |                                                    | Send NACK and switch to<br>Master Transmitter Mode<br>(write to SMB0DAT before<br>clearing SI). | 0                 | 0   | 0   |

Table 17.4. SMBus Status Decoding

#### Figure 19.6. UART Multi-Processor Mode Interconnect Diagram

| R/W    | R/W                                                                                                                                                                   | R              | R/W          | R/W            | R/W           | R/W            | R/W          | Reset Value     |  |  |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|----------------|---------------|----------------|--------------|-----------------|--|--|--|--|

| OVR1   | PERR1                                                                                                                                                                 | THRE1          | REN1         | TBX1           | RBX1          | TI1            | RI1          | 00100000        |  |  |  |  |

| Bit7   | Bit6                                                                                                                                                                  | Bit5           | Bit4         | Bit3           | Bit2          | Bit1           | Bit0         |                 |  |  |  |  |

|        |                                                                                                                                                                       |                |              |                |               |                | SFR Addres   | s: 0xD2         |  |  |  |  |

|        |                                                                                                                                                                       |                |              |                |               |                |              |                 |  |  |  |  |

| Bit7:  | OVR1: Rece                                                                                                                                                            |                |              |                |               |                |              |                 |  |  |  |  |

|        | This bit is used to indicate a receive FIFO overrun condition.                                                                                                        |                |              |                |               |                |              |                 |  |  |  |  |

|        | <ul><li>0: Receive FIFO Overrun has not occurred.</li><li>1: Receive FIFO Overrun has occurred (an incoming character was discarded due to a full</li></ul>           |                |              |                |               |                |              |                 |  |  |  |  |

|        | FIFO).                                                                                                                                                                | TFO Ovenu      | n nas occu   | neu (an inc    | oming chara   | acter was u    | iscarded c   | iue to a full   |  |  |  |  |

|        | This bit must                                                                                                                                                         | t he cleared   | to '0' by se | oftware        |               |                |              |                 |  |  |  |  |

| Bit6:  | PERR1: Par                                                                                                                                                            |                | •            | niware.        |               |                |              |                 |  |  |  |  |

|        | When parity                                                                                                                                                           | •              | -            | sed to indica  | ate that a pa | arity error ha | as occurre   | d. It is set to |  |  |  |  |

|        | '1' when the                                                                                                                                                          |                |              |                |               |                |              |                 |  |  |  |  |

|        | 0: Parity Erro                                                                                                                                                        | or has not o   | ccurred.     |                |               |                |              |                 |  |  |  |  |

|        | 1: Parity Erro                                                                                                                                                        |                |              |                |               |                |              |                 |  |  |  |  |

|        | This bit must                                                                                                                                                         |                |              |                |               |                |              |                 |  |  |  |  |

| Bit5:  | THRE1: Transmit Holding Register Empty Flag.                                                                                                                          |                |              |                |               |                |              |                 |  |  |  |  |

|        | <ul><li>0: Transmit Holding Register not Empty - do not write to SBUF1.</li><li>1: Transmit Holding Register Empty - it is safe to write to SBUF1.</li></ul>          |                |              |                |               |                |              |                 |  |  |  |  |

| Bit4:  |                                                                                                                                                                       |                |              | y - It is safe | to write to S | SBUF1.         |              |                 |  |  |  |  |

| DIL4.  | REN1: Receive Enable.                                                                                                                                                 |                |              |                |               |                |              |                 |  |  |  |  |

|        | This bit enables/disables the UART receiver. When disabled, bytes can still be read from the receive FIFO.                                                            |                |              |                |               |                |              |                 |  |  |  |  |

|        | 0: UART1 re                                                                                                                                                           |                | abled.       |                |               |                |              |                 |  |  |  |  |

|        | 1: UART1 re                                                                                                                                                           | •              |              |                |               |                |              |                 |  |  |  |  |

| Bit3:  | TBX1: Extra Transmission Bit.                                                                                                                                         |                |              |                |               |                |              |                 |  |  |  |  |

|        | The logic lev                                                                                                                                                         | el of this bit | will be ass  | signed to the  | e extra trans | smission bit   | when XB      | E1 is set to    |  |  |  |  |

|        | '1'. This bit is                                                                                                                                                      | s not used v   | vhen Parity  | is enabled.    |               |                |              |                 |  |  |  |  |

| Bit2:  | RBX1: Extra Receive Bit.                                                                                                                                              |                |              |                |               |                |              |                 |  |  |  |  |

|        | RBX1 is assigned the value of the extra bit when XBE1 is set to '1'. If XBE1 is cleared to '0',                                                                       |                |              |                |               |                |              |                 |  |  |  |  |

|        | RBX1 will be assigned the logic level of the first stop bit. This bit is not valid when Parity is                                                                     |                |              |                |               |                |              |                 |  |  |  |  |

| D:44 . | enabled.<br>TI1: Transmit Interrupt Flag.                                                                                                                             |                |              |                |               |                |              |                 |  |  |  |  |

| Bit1:  |                                                                                                                                                                       | •              | -            | hac haan tr    | anomittod o   | t the begin    | ning of the  |                 |  |  |  |  |

|        | Set to a '1' by hardware after data has been transmitted, at the beginning of the STOP bit.                                                                           |                |              |                |               |                |              |                 |  |  |  |  |

|        | When the UART1 interrupt is enabled, setting this bit causes the CPU to vector to the UART1 interrupt service routine. This bit must be cleared manually by software. |                |              |                |               |                |              |                 |  |  |  |  |

| Bit0:  | RI1: Receive                                                                                                                                                          |                |              |                |               | manaany by     | , contraro   |                 |  |  |  |  |

|        | Set to '1' by I                                                                                                                                                       |                |              | of data has    | been receiv   | ed by UAR      | Γ1 (set at t | he STOP bit     |  |  |  |  |

|        | sampling tim                                                                                                                                                          |                |              |                |               |                |              |                 |  |  |  |  |

|        | to vector to t                                                                                                                                                        | he UART1       | interrupt se | rvice routine  | e. This bit m | nust be clea   | red manua    | ally by soft-   |  |  |  |  |

|        | ware. Note the                                                                                                                                                        |                |              |                |               |                |              | FIFO. After     |  |  |  |  |

|        | the last byte                                                                                                                                                         | hac been c     | hifted from  |                |               |                |              |                 |  |  |  |  |

### SFR Definition 19.1. SCON1: UART1 Control

#### SFR Definition 20.2. SPI0CN: SPI0 Control

| R/W<br>SPIF | R/W<br>WCOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W<br>MODF          | R/W         | R/W<br>NSSMD1 | R/W  | R<br>TXBMT | R/W<br>SPIEN | Reset Value 00000110 |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|---------------|------|------------|--------------|----------------------|--|--|--|

| Bit7        | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit5                 | Bit4        | Bit3          | Bit2 | Bit1       | Bit0         | Bit<br>Addressable   |  |  |  |

|             | SFR Address: 0xF8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |             |               |      |            |              |                      |  |  |  |

| Bit 7:      | SPIF: SPI0 Interrupt Flag.<br>This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enabled,<br>setting this bit causes the CPU to vector to the SPI0 interrupt service routine. This bit is not                                                                                                                                                                                                                                                                                                       |                      |             |               |      |            |              |                      |  |  |  |

| Bit 6:      | automatically cleared by hardware. It must be cleared by software.<br>WCOL: Write Collision Flag.<br>This bit is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not<br>been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be<br>ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes. It                                                                                                                                         |                      |             |               |      |            |              |                      |  |  |  |

| Bit 5:      | must be cleared by software.<br>MODF: Mode Fault Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when a master mode<br>collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01). This bit is not auto-                                                                                                                                                                                                                                                                                        |                      |             |               |      |            |              |                      |  |  |  |