# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 40                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 20x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f344-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 14.3. OSCLCN: Internal L-F Oscillator Control              | . 134 |

|---------------------------------------------------------------------------|-------|

| SFR Definition 14.4. OSCXCN: External Oscillator Control                  | . 137 |

| SFR Definition 14.5. CLKMUL: Clock Multiplier Control                     | . 138 |

| SFR Definition 14.6. CLKSEL: Clock Select                                 |       |

| SFR Definition 15.1. XBR0: Port I/O Crossbar Register 0                   | . 148 |

| SFR Definition 15.2. XBR1: Port I/O Crossbar Register 1                   | . 149 |

| SFR Definition 15.3. XBR2: Port I/O Crossbar Register 2                   |       |

| SFR Definition 15.4. P0: Port0 Latch                                      |       |

| SFR Definition 15.5. P0MDIN: Port0 Input Mode                             |       |

| SFR Definition 15.6. P0MDOUT: Porto Output Mode                           |       |

| SFR Definition 15.7. P0SKIP: Port0 Skip                                   |       |

| SFR Definition 15.8. P1: Port1 Latch                                      |       |

| SFR Definition 15.9. P1MDIN: Port1 Input Mode                             | . 152 |

| SFR Definition 15.10. P1MDOUT: Port1 Output Mode                          |       |

| SFR Definition 15.11. P1SKIP: Port1 Skip                                  |       |

| SFR Definition 15.12. P2: Port2 Latch                                     |       |

| SFR Definition 15.13. P2MDIN: Port2 Input Mode                            | . 153 |

| SFR Definition 15.14. P2MDOUT: Port2 Output Mode                          |       |

| SFR Definition 15.15. P2SKIP: Port2 Skip                                  |       |

| SFR Definition 15.16. P3: Port3 Latch                                     |       |

| SFR Definition 15.17. P3MDIN: Port3 Input Mode                            |       |

| SFR Definition 15.18. P3MDOUT: Port3 Output Mode                          |       |

| SFR Definition 15.19. P3SKIP: Port3 Skip                                  |       |

| SFR Definition 15.20. P4: Port4 Latch                                     |       |

| SFR Definition 15.21. P4MDIN: Port4 Input Mode                            | . 157 |

| SFR Definition 15.22. P4MDOUT: Port4 Output Mode                          |       |

| SFR Definition 16.1. USB0XCN: USB0 Transceiver Control                    |       |

| SFR Definition 16.2. USB0ADR: USB0 Indirect Address                       | . 163 |

| SFR Definition 16.3. USB0DAT: USB0 Data                                   |       |

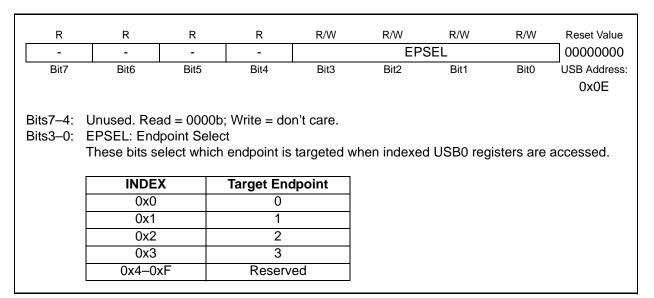

| USB Register Definition 16.4. INDEX: USB0 Endpoint Index                  |       |

| USB Register Definition 16.5. CLKREC: Clock Recovery Control              |       |

| USB Register Definition 16.6. FIFOn: USB0 Endpoint FIFO Access            |       |

| USB Register Definition 16.7. FADDR: USB0 Function Address                |       |

| USB Register Definition 16.8. POWER: USB0 Power                           |       |

| USB Register Definition 16.9. FRAMEL: USB0 Frame Number Low               |       |

| USB Register Definition 16.10. FRAMEH: USB0 Frame Number High             |       |

| USB Register Definition 16.11. IN1INT: USB0 IN Endpoint Interrupt         |       |

| USB Register Definition 16.12. OUT1INT: USB0 Out Endpoint Interrupt       |       |

| USB Register Definition 16.13. CMINT: USB0 Common Interrupt               |       |

| USB Register Definition 16.14. IN1IE: USB0 IN Endpoint Interrupt Enable   |       |

| USB Register Definition 16.15. OUT1IE: USB0 Out Endpoint Interrupt Enable |       |

| USB Register Definition 16.16. CMIE: USB0 Common Interrupt Enable         |       |

| USB Register Definition 16.17. E0CSR: USB0 Endpoint0 Control              |       |

| USB Register Definition 16.18. E0CNT: USB0 Endpoint 0 Data Count          |       |

|                                                                           |       |

| Ordering Part Number | MIPS (Peak) | Flash Memory (Bytes) | RAM  | Calibrated Internal Oscillator | Low Frequency Oscillator | USB with 1k Endpoint RAM | Supply Voltage Regulator | SMBus/I2C    | Enhanced SPI | UARTs | Timers (16-bit) | Programmable Counter Array | Digital Port I/Os | External Memory Interface (EMIF) | 10-bit 200 ksps ADC | Temperature Sensor | Voltage Reference | Analog Comparators | Package |

|----------------------|-------------|----------------------|------|--------------------------------|--------------------------|--------------------------|--------------------------|--------------|--------------|-------|-----------------|----------------------------|-------------------|----------------------------------|---------------------|--------------------|-------------------|--------------------|---------|

| C8051F340-GQ         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 40                | $\checkmark$                     | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | TQFP48  |

| C8051F341-GQ         | 48          | 32k                  | 2304 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 40                | $\checkmark$                     | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | TQFP48  |

| C8051F342-GQ         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F342-GM         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | QFN32   |

| C8051F343-GQ         | 48          | 32k                  | 2304 | $\checkmark$                   | ~                        | ~                        | ~                        | $\checkmark$ | $\checkmark$ | 1     | 4               | ~                          | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F343-GM         | 48          | 32k                  | 2304 | $\checkmark$                   | ~                        | ~                        | ~                        | $\checkmark$ | $\checkmark$ | 1     | 4               | ~                          | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | QFN32   |

| C8051F344-GQ         | 25          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 40                | $\checkmark$                     | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | TQFP48  |

| C8051F345-GQ         | 25          | 32k                  | 2304 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 40                | $\checkmark$                     | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | TQFP48  |

| C8051F346-GQ         | 25          | 64k                  | 4352 | $\checkmark$                   | —                        | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F346-GM         | 25          | 64k                  | 4352 | $\checkmark$                   | —                        | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | QFN32   |

| C8051F347-GQ         | 25          | 32k                  | 2304 | $\checkmark$                   | _                        | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F347-GM         | 25          | 32k                  | 2304 | $\checkmark$                   | _                        | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | _                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | QFN32   |

| C8051F348-GQ         | 25          | 32k                  | 2304 | $\checkmark$                   | ~                        | ~                        | $\checkmark$             | <            | $\checkmark$ | 2     | 4               | ~                          | 40                | $\checkmark$                     |                     | _                  | _                 | 2                  | TQFP48  |

| C8051F349-GQ         | 25          | 32k                  | 2304 | $\checkmark$                   | ~                        | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | _                                |                     | —                  | _                 | 2                  | LQFP32  |

| C8051F349-GM         | 25          | 32k                  | 2304 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | _                                |                     | —                  | —                 | 2                  | QFN32   |

| C8051F34A-GQ         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 25                | _                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F34A-GM         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 25                | _                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | QFN32   |

| C8051F34B-GQ         | 48          | 32k                  | 2304 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 25                |                                  | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F34B-GM         | 48          | 32k                  | 2304 | ~                              | ~                        | ~                        | ~                        | $\checkmark$ | ~            | 2     | 4               | ~                          | 25                | _                                | $\checkmark$        | ~                  | ~                 | 2                  | QFN32   |

| C8051F34C-GQ         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 40                | $\checkmark$                     | _                   |                    |                   | 2                  | TQFP48  |

| C8051F34D-GQ         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | _                   | —                  | —                 | 2                  | LQFP32  |

Table 1.1. Product Selection Guide

#### Table 4.1. Pin Definitions for the C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D (Continued)

| Nama | Pin Nu | mbers  | Turne            | Description                                                           |

|------|--------|--------|------------------|-----------------------------------------------------------------------|

| Name | 48-pin | 32-pin | Туре             | Description                                                           |

| P1.0 | 46     | 26     | D I/O or<br>A In | Port 1.0. See <b>Section 15</b> for a complete description of Port 1. |

| P1.1 | 45     | 25     | D I/O or<br>A In | Port 1.1.                                                             |

| P1.2 | 44     | 24     | D I/O or<br>A In | Port 1.2.                                                             |

| P1.3 | 43     | 23     | D I/O or<br>A In | Port 1.3.                                                             |

| P1.4 | 42     | 22     | D I/O or<br>A In | Port 1.4.                                                             |

| P1.5 | 41     | 21     | D I/O or<br>A In | Port 1.5.                                                             |

| P1.6 | 40     | 20     | D I/O or<br>A In | Port 1.6.                                                             |

| P1.7 | 39     | 19     | D I/O or<br>A In | Port 1.7.                                                             |

| P2.0 | 38     | 18     | D I/O or<br>A In | Port 2.0. See <b>Section 15</b> for a complete description of Port 2. |

| P2.1 | 37     | 17     | D I/O or<br>A In | Port 2.1.                                                             |

| P2.2 | 36     | 16     | D I/O or<br>A In | Port 2.2.                                                             |

| P2.3 | 35     | 15     | D I/O or<br>A In | Port 2.3.                                                             |

| P2.4 | 34     | 14     | D I/O or<br>A In | Port 2.4.                                                             |

| P2.5 | 33     | 13     | D I/O or<br>A In | Port 2.5.                                                             |

| P2.6 | 32     | 12     | D I/O or<br>A In | Port 2.6.                                                             |

| P2.7 | 31     | 11     | D I/O or<br>A In | Port 2.7.                                                             |

| P3.0 | 30     | —      | D I/O or<br>A In | Port 3.0. See <b>Section 15</b> for a complete description of Port 3. |

| P3.1 | 29     | _      | D I/O or<br>A In | Port 3.1.                                                             |

| P3.2 | 28     | —      | D I/O or<br>A In | Port 3.2.                                                             |

#### SFR Definition 5.2. AMX0N: AMUX0 Negative Channel Select

| R        | R            | R         | R/W           | R/W          | R/W     | R/W                     | R/W          | Reset Value |

|----------|--------------|-----------|---------------|--------------|---------|-------------------------|--------------|-------------|

| -        | -            | -         | AMX0N4        | AMX0N3       | AMX0N2  | AMX0N1                  | AMX0N0       | 00000000    |

| Bit7     | Bit6         | Bit5      | Bit4          | Bit3         | Bit2    | Bit1                    | Bit0         | SFR Address |

|          |              |           |               |              |         |                         |              | 0xBA        |

| Bito7 5. | UNUSED. R    | ood - 000 | h: Mrito – de | n't coro     |         |                         |              |             |

|          | AMX0N4-0:    |           | ,             |              |         |                         |              |             |

| Dito+ 0. | Note that wh |           |               |              |         | DC0 operate             | es in Sinale | -ended      |

|          | mode. For al |           |               |              |         |                         |              |             |

|          |              |           | 5 1           | ,            | •       |                         |              |             |

|          | AMX0         | N4-0      |               | Negative I   |         |                         | gative Inpu  | t           |

|          |              |           | (32-          | pin Packag   | je)     |                         | Package)     |             |

|          | 000          |           |               | P1.0         |         |                         | 2.0          |             |

|          | 000          |           |               | P1.1         |         |                         | 2.1          |             |

|          | 000          |           |               | P1.2         |         | P2.2                    |              |             |

|          | 000          |           |               | P1.3         |         | P2.3                    |              |             |

|          | 001          |           |               | P1.4         |         |                         | 2.5          |             |

|          | 001          |           |               | P1.5         |         |                         | 2.6          |             |

|          | 001          |           |               | P1.6         |         |                         | 3.0          |             |

|          | 001          |           |               | P1.7         |         |                         | 3.1          |             |

|          | 010          |           |               | P2.0         |         | P3.4                    |              |             |

|          | 010          |           |               | P2.1         |         | P3.5                    |              |             |

|          | 010          |           |               | P2.2         |         | P3.7                    |              |             |

|          | 010          |           |               | P2.3         |         | P4.0                    |              |             |

|          | 011          |           |               | P2.4         |         | P4.3                    |              |             |

|          | 011          |           |               | P2.5         |         | P4.4                    |              |             |

|          | 011          |           |               | P2.6         |         | P4.5                    |              |             |

|          | 011          |           |               | P2.7         |         | P4.6<br>RESERVED        |              |             |

|          | 100          |           |               | P3.0<br>P0.0 |         | -                       | 0.3          |             |

|          | 100          |           |               | P0.0<br>P0.1 |         |                         | 0.3          |             |

|          | 100          |           |               | P0.1<br>P0.4 |         |                         | 1.1          |             |

|          | 100          |           |               | P0.4<br>P0.5 |         |                         | 1.1          |             |

|          | 10101 -      |           |               | ESERVED      |         |                         |              |             |

|          | 111          |           | K             | VREF         |         | RESERVED<br>VREF        |              |             |

|          | 111          |           |               | ngle-Ended   | Mode) ( |                         |              |             |

|          |              |           |               |              |         | GND (Single-Ended Mode) |              |             |

#### SFR Definition 5.6. ADC0CN: ADC0 Control

| R/W                                                                                            | R/W                                                                                                                                                                                              | R/W          | R/W             | R/W             | R/W            | R/W           | R/W           | Reset Value  |  |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|-----------------|----------------|---------------|---------------|--------------|--|

| AD0EN                                                                                          | AD0TM                                                                                                                                                                                            | AD0INT       | AD0BUSY         | <b>ADOWINT</b>  | AD0CM2         | AD0CM1        | AD0CM0        | 00000000     |  |

| Bit7                                                                                           | Bit6                                                                                                                                                                                             | Bit5         | Bit4            | Bit3            | Bit2           | Bit1          | Bit0          | SFR Address: |  |

|                                                                                                |                                                                                                                                                                                                  |              |                 |                 |                | (bi           | t addressable | ) 0xE8       |  |

| D.1.7                                                                                          |                                                                                                                                                                                                  |              | D'/             |                 |                |               |               |              |  |

| Bit7:                                                                                          | ADOEN: ADO                                                                                                                                                                                       |              |                 | nower obut      |                |               |               |              |  |

|                                                                                                | 0: ADC0 Dis<br>1: ADC0 Ena                                                                                                                                                                       |              |                 |                 |                | orsions       |               |              |  |

| Bit6:                                                                                          | ADOTM: AD                                                                                                                                                                                        |              |                 | and ready it    |                | 61310113.     |               |              |  |

| Dito:                                                                                          | 0: Normal Tr                                                                                                                                                                                     |              |                 | 0 is enabled    | d, tracking is | s continuou   | s unless a    | conversion   |  |

|                                                                                                | is in progres                                                                                                                                                                                    |              |                 |                 | , J            |               |               |              |  |

|                                                                                                | 1: Low-powe                                                                                                                                                                                      |              | ode: Trackin    | g Defined b     | y AD0CM2-      | -0 bits (see  | below).       |              |  |

| Bit5:                                                                                          | AD0INT: AD                                                                                                                                                                                       |              |                 |                 |                |               |               |              |  |

|                                                                                                | 0: ADC0 has                                                                                                                                                                                      |              |                 |                 | since the la   | ast time AD   | 0INT was c    | leared.      |  |

| <b>D</b> '' 4                                                                                  | 1: ADC0 has                                                                                                                                                                                      | •            |                 | version.        |                |               |               |              |  |

| Bit4:                                                                                          | AD0BUSY: A<br>Read:                                                                                                                                                                              | ADC0 Busy    | / Bit.          |                 |                |               |               |              |  |

|                                                                                                | 0: ADC0 cor                                                                                                                                                                                      | woreion is   | complete or     | a conversi      | on is not cu   | rrently in nr |               | OINT is sot  |  |

|                                                                                                | to logic 1 on                                                                                                                                                                                    |              |                 |                 |                |               | ogress. AD    | 011113361    |  |

|                                                                                                | 1: ADC0 cor                                                                                                                                                                                      |              |                 |                 |                |               |               |              |  |

|                                                                                                | Write:                                                                                                                                                                                           |              | 1 3 3 3 3       |                 |                |               |               |              |  |

|                                                                                                | 0: No Effect.                                                                                                                                                                                    |              |                 |                 |                |               |               |              |  |

|                                                                                                | 1: Initiates A                                                                                                                                                                                   |              |                 |                 |                |               |               |              |  |

| Bit3:                                                                                          | ADOWINT: A                                                                                                                                                                                       |              | •               | •               | -              |               | <i>a</i>      |              |  |

|                                                                                                | 0: ADC0 Wir                                                                                                                                                                                      |              |                 |                 |                | ed since this | s flag was I  | ast cleared. |  |

| Bits2–0:                                                                                       | 1: ADC0 Wir<br>AD0CM2-0:                                                                                                                                                                         |              |                 |                 |                |               |               |              |  |

| DII52-0.                                                                                       | When AD0T                                                                                                                                                                                        |              |                 |                 | Select.        |               |               |              |  |

|                                                                                                | 000: ADC0 cc                                                                                                                                                                                     |              | tiated on eve   | rv write of '1' | to AD0BUS      | Y.            |               |              |  |

|                                                                                                | 001: ADC0 cc                                                                                                                                                                                     |              |                 |                 |                |               |               |              |  |

|                                                                                                | 010: ADC0 cc                                                                                                                                                                                     |              |                 |                 |                |               |               |              |  |

|                                                                                                | 011: ADC0 co                                                                                                                                                                                     |              |                 |                 |                | тр            |               |              |  |

|                                                                                                | 100: ADC0 cc<br>101: ADC0 cc                                                                                                                                                                     |              |                 |                 |                | IR.           |               |              |  |

|                                                                                                | 11x: Reserved                                                                                                                                                                                    |              |                 |                 | 5.             |               |               |              |  |

|                                                                                                | When AD0T                                                                                                                                                                                        |              |                 |                 |                |               |               |              |  |

|                                                                                                | 000: Tracking                                                                                                                                                                                    | initiated on | write of '1' to | AD0BUSY a       | nd lasts 3 SA  | AR clocks, fo | llowed by co  | onversion.   |  |

|                                                                                                | 001: Tracking initiated on overflow of Timer 0 and lasts 3 SAR clocks, followed by conversion.<br>010: Tracking initiated on overflow of Timer 2 and lasts 3 SAR clocks, followed by conversion. |              |                 |                 |                |               |               |              |  |

|                                                                                                |                                                                                                                                                                                                  |              |                 |                 |                |               |               |              |  |

|                                                                                                | 011: Tracking initiated on overflow of Timer 1 and lasts 3 SAR clocks, followed by conversion.<br>100: ADC0 tracks only when CNVSTR input is logic low; conversion starts on rising CNVSTR edg   |              |                 |                 |                |               |               |              |  |

| 101: Tracking initiated on overflow of Timer 3 and lasts 3 SAR clocks, followed by conversion. |                                                                                                                                                                                                  |              |                 |                 |                |               |               |              |  |

|                                                                                                | 11x: Reserved                                                                                                                                                                                    |              |                 |                 |                |               | -             |              |  |

|                                                                                                |                                                                                                                                                                                                  |              |                 |                 |                |               |               |              |  |

|                                                                                                |                                                                                                                                                                                                  |              |                 |                 |                |               |               |              |  |

#### 9.1.2. MOVX Instruction and Program Memory

In the CIP-51, the MOVX instruction serves three purposes: accessing on-chip XRAM, accessing off-chip data XRAM (only on C8051F340/1/4/5/8 devices), and accessing on-chip program Flash memory. The Flash access feature provides a mechanism for user software to update program code and use the program memory space for non-volatile data storage (see Section "12. Flash Memory" on page 107). The External Memory Interface (only on C8051F340/1/4/5/8 devices) provides a fast access interface to off-chip data XRAM (or memory-mapped peripherals) via the MOVX instruction. Refer to Section "13. External Data Memory Interface and On-Chip XRAM" on page 114. for details.

| Mnemonic          | Description                              | Bytes | Clock<br>Cycles |

|-------------------|------------------------------------------|-------|-----------------|

|                   | Arithmetic Operations                    | I     |                 |

| ADD A, Rn         | Add register to A                        | 1     | 1               |

| ADD A, direct     | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri        | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data      | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn        | Add register to A with carry             | 1     | 1               |

| ADDC A, direct    | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri       | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data     | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn        | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct    | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri       | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data     | Subtract immediate from A with borrow    | 2     | 2               |

| INC A             | Increment A                              | 1     | 1               |

| INC Rn            | Increment register                       | 1     | 1               |

| INC direct        | Increment direct byte                    | 2     | 2               |

| INC @Ri           | Increment indirect RAM                   | 1     | 2               |

| DEC A             | Decrement A                              | 1     | 1               |

| DEC Rn            | Decrement register                       | 1     | 1               |

| DEC direct        | Decrement direct byte                    | 2     | 2               |

| DEC @Ri           | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR          | Increment Data Pointer                   | 1     | 1               |

| MUL AB            | Multiply A and B                         | 1     | 4               |

| DIV AB            | Divide A by B                            | 1     | 8               |

| DA A              | Decimal adjust A                         | 1     | 1               |

|                   | Logical Operations                       |       | 1               |

| ANL A, Rn         | AND Register to A                        | 1     | 1               |

| ANL A, direct     | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri        | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data      | AND immediate to A                       | 2     | 2               |

| ANL direct, A     | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn         | OR Register to A                         | 1     | 1               |

| ORL A, direct     | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri        | OR indirect RAM to A                     | 1     | 2               |

### Table 9.1. CIP-51 Instruction Set Summary

| Table 9.1. CIP-51 | Instruction | Set Summary | (Continued) |

|-------------------|-------------|-------------|-------------|

|                   |             |             |             |

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

|                      | Boolean Manipulation                                |       | 1               |

| CLR C                | Clear Carry                                         | 1     | 1               |

| CLR bit              | Clear direct bit                                    | 2     | 2               |

| SETB C               | Set Carry                                           | 1     | 1               |

| SETB bit             | Set direct bit                                      | 2     | 2               |

| CPL C                | Complement Carry                                    | 1     | 1               |

| CPL bit              | Complement direct bit                               | 2     | 2               |

| ANL C, bit           | AND direct bit to Carry                             | 2     | 2               |

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |

| JC rel               | Jump if Carry is set                                | 2     | 2/4             |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/4             |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/5             |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/5             |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3     | 3/5             |

|                      | Program Branching                                   |       |                 |

| ACALL addr11         | Absolute subroutine call                            | 2     | 4               |

| LCALL addr16         | Long subroutine call                                | 3     | 5               |

| RET                  | Return from subroutine                              | 1     | 6               |

| RETI                 | Return from interrupt                               | 1     | 6               |

| AJMP addr11          | Absolute jump                                       | 2     | 4               |

| LJMP addr16          | Long jump                                           | 3     | 5               |

| SJMP rel             | Short jump (relative address)                       | 2     | 4               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 4               |

| JZ rel               | Jump if A equals zero                               | 2     | 2/4             |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/4             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 3/5             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/5             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/5             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/6             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/4             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/5             |

| NOP                  | No operation                                        | 1     | 1               |

| R/W                                                                                           | R                                                                             | R/W          | R/W          | R                        | R/W                     | R/W                       | R                     | Reset Value  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------|--------------|--------------------------|-------------------------|---------------------------|-----------------------|--------------|--|--|--|--|

| USBRS                                                                                         | F FERROR                                                                      | CORSEF       | SWRSF        | WDTRSF                   | MCDRSF                  | PORSF                     | PINRSF                | Variable     |  |  |  |  |

| Bit7                                                                                          | Bit6                                                                          | Bit5         | Bit4         | Bit3                     | Bit2                    | Bit1                      | Bit0                  | SFR Address: |  |  |  |  |

|                                                                                               |                                                                               |              |              |                          |                         |                           |                       | 0xEF         |  |  |  |  |

|                                                                                               |                                                                               |              |              |                          |                         |                           |                       |              |  |  |  |  |

| Bit7:                                                                                         | USBRSF: U                                                                     | SB Reset F   | lag          |                          |                         |                           |                       |              |  |  |  |  |

|                                                                                               | 0: Read: Las                                                                  | st reset was | not a USB    | reset; Writ              | e: USB rese             | ets disabled              | ł.                    |              |  |  |  |  |

|                                                                                               | 1: <b>Read:</b> Last reset was a USB reset; <b>Write:</b> USB resets enabled. |              |              |                          |                         |                           |                       |              |  |  |  |  |

| Bit6:                                                                                         | FERROR: Flash Error Indicator.                                                |              |              |                          |                         |                           |                       |              |  |  |  |  |

|                                                                                               | 0: Source of last reset was not a Flash read/write/erase error.               |              |              |                          |                         |                           |                       |              |  |  |  |  |

|                                                                                               | 1: Source of                                                                  |              |              |                          |                         |                           |                       |              |  |  |  |  |

| Bit5:                                                                                         | CORSEF: Co                                                                    | •            |              |                          | -                       | 0                         |                       |              |  |  |  |  |

|                                                                                               | 0: Read: So                                                                   | urce of last | reset was r  | not Compar               | ator0; Write            | : Compara                 | tor0 is not a         | a reset      |  |  |  |  |

|                                                                                               | source.                                                                       | waa af laat  | react was (  |                          | O. Mrites C.            |                           | in a recet            |              |  |  |  |  |

|                                                                                               | 1: Read: So<br>(active-low).                                                  | urce of last | reset was u  | Comparator               |                         | omparatoru                | is a reset s          | source       |  |  |  |  |

| Bit4:                                                                                         | SWRSF: Sof                                                                    | ftware Rese  | t Force and  | d Elag                   |                         |                           |                       |              |  |  |  |  |

| DIL4.                                                                                         | 0: <b>Read:</b> So                                                            |              |              | -                        | o the SWRS              | SE bit <sup>.</sup> Write | • No Effec            | t            |  |  |  |  |

|                                                                                               | 1: <b>Read:</b> So                                                            |              |              |                          |                         |                           |                       |              |  |  |  |  |

| Bit3:                                                                                         | WDTRSF: W                                                                     |              |              |                          |                         |                           | a oyotoini i          | 00011        |  |  |  |  |

|                                                                                               | 0: Source of                                                                  | -            |              | -                        |                         |                           |                       |              |  |  |  |  |

|                                                                                               | 1: Source of                                                                  | last reset w | as a WDT     | timeout.                 |                         |                           |                       |              |  |  |  |  |

| Bit2:                                                                                         | MCDRSF: N                                                                     | lissing Cloc | k Detector   | Flag.                    |                         |                           |                       |              |  |  |  |  |

|                                                                                               | 0: Read: So                                                                   | urce of last | reset was r  | not a Missin             | g Clock Det             | ector timed               | out; Write: I         | Missing      |  |  |  |  |

|                                                                                               | Clock Detect                                                                  |              |              |                          |                         |                           |                       |              |  |  |  |  |

|                                                                                               | 1: <b>Read:</b> So                                                            |              |              | -                        |                         |                           |                       | sing Clock   |  |  |  |  |

| 5                                                                                             | Detector ena                                                                  |              |              | -                        | clock condit            | ion is deteo              | cted.                 |              |  |  |  |  |

| Bit1:                                                                                         | PORSF: Pov                                                                    | -            | -            | -                        |                         |                           |                       |              |  |  |  |  |

|                                                                                               | This bit is se                                                                | -            | -            |                          | -                       |                           |                       |              |  |  |  |  |

|                                                                                               | monitor as a                                                                  | reset sourc  | e. Note: w   | riting '1' to            | this bit be             | fore the V <sub>D</sub>   | DD monitor            | is enabled   |  |  |  |  |

|                                                                                               | and stabiliz                                                                  |              |              |                          |                         |                           |                       |              |  |  |  |  |

|                                                                                               | 0: <b>Read:</b> Las                                                           | st reset was | not a pow    | er-on or V <sub>DI</sub> | <sub>D</sub> monitor re | set; Write:               | V <sub>DD</sub> monit | or is not a  |  |  |  |  |

|                                                                                               | reset source                                                                  |              |              |                          |                         |                           |                       |              |  |  |  |  |

|                                                                                               | 1: <b>Read:</b> Las                                                           | st reset was | a power-or   | n or V <sub>DD</sub> mo  | nitor reset;            | all other res             | et flags ind          | eterminate;  |  |  |  |  |

|                                                                                               | Write: V <sub>DD</sub> r                                                      | nonitor is a | reset source | ce.                      |                         |                           |                       |              |  |  |  |  |

| Bit0:                                                                                         | PINRSF: HV                                                                    | V Pin Reset  | Flag.        | _                        |                         |                           |                       |              |  |  |  |  |

|                                                                                               | 0: Source of                                                                  |              |              |                          |                         |                           |                       |              |  |  |  |  |

|                                                                                               | 1: Source of                                                                  | last reset w | /as RST pir  | า.                       |                         |                           |                       |              |  |  |  |  |

|                                                                                               |                                                                               | 4            |              |                          |                         |                           | la alla at c a f      | 1            |  |  |  |  |

|                                                                                               | or bits that ac                                                               |              |              |                          |                         |                           |                       | •            |  |  |  |  |

| read), read-modify-write instructions read and modify the source enable only. This applies to |                                                                               |              |              |                          |                         |                           |                       |              |  |  |  |  |

| 5113. 031                                                                                     | bits: USBRSF, C0RSEF, SWRSF, MCDRSF, PORSF.                                   |              |              |                          |                         |                           |                       |              |  |  |  |  |

|                                                                                               |                                                                               |              |              |                          |                         |                           |                       |              |  |  |  |  |

### SFR Definition 11.2. RSTSRC: Reset Source

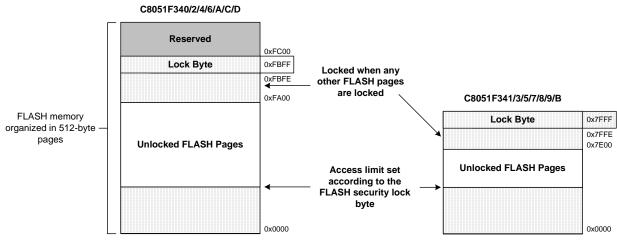

Figure 12.1. Flash Program Memory Map and Security Byte

| Internal Oscillator |                                           |                              |  |  |  |  |  |  |  |  |

|---------------------|-------------------------------------------|------------------------------|--|--|--|--|--|--|--|--|

| Clock Signal        | Input Source Selection                    | Register Bit Settings        |  |  |  |  |  |  |  |  |

| USB Clock           | External Oscillator / 4                   | USBCLK = 101b                |  |  |  |  |  |  |  |  |

| External Oscillator | Crystal Oscillator Mode<br>24 MHz Crystal | XOSCMD = 110b<br>XFCN = 111b |  |  |  |  |  |  |  |  |

### SFR Definition 14.6. CLKSEL: Clock Select

|   | R/W  | R/W  | R/W    | R/W  | R/W  | R/W  | R/W   | R/W  | Reset Value |

|---|------|------|--------|------|------|------|-------|------|-------------|

|   | -    |      | USBCLK |      | -    |      | CLKSL |      | 00000000    |

| - | Bit7 | Bit6 | Bit5   | Bit4 | Bit3 | Bit2 | Bit1  | Bit0 | SFR Address |

|   |      |      |        |      |      |      |       |      | 0xA9        |

Bit 7: Unused. Read = 0b; Write = don't care.

Bits6–4: USBCLK2–0: USB Clock Select

These bits select the clock supplied to USB0. When operating USB0 in full-speed mode, the selected clock should be 48 MHz. When operating USB0 in low-speed mode, the selected clock should be 6 MHz.

| USBCLK | Selected Clock          |

|--------|-------------------------|

| 000    | 4x Clock Multiplier     |

| 001    | Internal Oscillator / 2 |

| 010    | External Oscillator     |

| 011    | External Oscillator / 2 |

| 100    | External Oscillator / 3 |

| 101    | External Oscillator / 4 |

| 110    | RESERVED                |

| 111    | RESERVED                |

Bit3: Unused. Read = 0b; Write = don't care.

Bits2–0: CLKSL2–0: System Clock Select

These bits select the system clock source. When operating from a system clock of 25 MHz or less, the FLRT bit should be set to '0'. When operating with a system clock of greater than 25 MHz (up to 48 MHz), the FLRT bit (FLSCL.4) should be set to '1'. See **Section "10. Prefetch Engine" on page 99** for more details.

| CLKSL                         | Selected Clock                                                             |

|-------------------------------|----------------------------------------------------------------------------|

| 000                           | Internal Oscillator (as determined by the<br>IFCN bits in register OSCICN) |

| 001                           | External Oscillator                                                        |

| 010                           | 4x Clock Multiplier / 2                                                    |

| 011*                          | 4x Clock Multiplier*                                                       |

| 100                           | Low-Frequency Oscillator                                                   |

| 101-111                       | RESERVED                                                                   |

| *Note: This option is only av | vailable on 48 MHz devices.                                                |

|                                   |   |   |        |          | <b>0</b>   |          | ~      |       |      |       |        | P        | 1          |         |     |    |   |      |      | P        | 2         |          |      |     |      |       | _      | F           | 3          | _            | _ | _ |

|-----------------------------------|---|---|--------|----------|------------|----------|--------|-------|------|-------|--------|----------|------------|---------|-----|----|---|------|------|----------|-----------|----------|------|-----|------|-------|--------|-------------|------------|--------------|---|---|

| SF Signals<br>(32-pin<br>Package) |   |   | XTAL1  | XTAL2    |            |          | CNVSTR | VREF  |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      | P     |        | 3.7<br>32-p |            |              |   |   |

| SF Signals<br>(48-pin<br>Package) |   |   |        |          |            |          | XTAL1  | XTAL2 |      |       |        | ALE      | CNVSTR     | VREF    | RD  | WR |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| PIN I/O                           | 0 | 1 | 2      | 3        | 4          | 5        | 6      | 7     | 0    | 1     | 2      | 3        | 4          | 5       | 6   | 7  | 0 | 1    | 2    | 3        | 4         | 5        | 6    | 7   | 0    | 1     | 2      | 3           | 4          | 5            | 6 | 7 |

| ТХ0                               |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| RX0                               |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| SCK                               |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| MISO                              |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| MOSI                              |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| NSS*                              |   |   |        |          |            | *NS      | S is   | only  | pinr | ned o | ut in  | 4-wi     | re S       | PI m    | ode |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

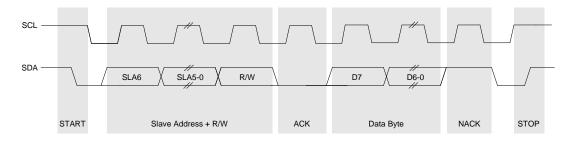

| SDA                               |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| SCL                               |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| CP0                               |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| CP0A                              |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| CP1                               |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| CP1A                              |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| SYSCLK                            |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| CEX0                              |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| CEX1                              |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| CEX2                              |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| CEX3                              |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| CEX4                              |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| ECI                               |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| то                                |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| T1                                |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

| TX1**                             |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   | **UA | ART1 | lava     | ilable    | e onl    | y on | C80 | 51F3 | 340/1 | /4/5/  | /8/A/       | B de       | vices        |   |   |

| RX1**                             |   |   |        |          |            |          |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |       |        |             |            |              |   |   |

|                                   | 0 | 0 | 0<br>P | 0<br>OSK | 0<br>IP[0: | 0<br>[7] | 0      | 0     | 0    | 0     | 0<br>P | 0<br>1SK | 0<br>IP[0: | 0<br>7] | 0   | 0  | 0 | 0    |      | 0<br>25K | 0<br>P[0: | 0<br>:7] | 0    | 0   | 0    | 0     | 0<br>P | 0<br>3SK    | 0<br>IP[0: | 0<br>7]      | 0 | ( |

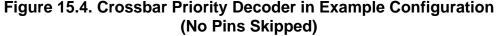

| SF Signals                        |   |   |        | -        |            |          |        |       | he C |       |        | Cro      |            | - 10/   | hon |    |   |      |      |          |           |          |      |     | Exa  | ample | e:     |             |            | 0x07<br>0x43 |   |   |

| R/W      | R/W                                                                                                                                                        | R/W                                                                                                                 | R/W                                                                                   | R/W                                         | R/W        | R/W           | R/W      | Reset Value          |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------|------------|---------------|----------|----------------------|