# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 40                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                |                                                                 |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 20x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f345-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 19.1. UART1 Block Diagram 21                                         |             |

|-----------------------------------------------------------------------------|-------------|

| Figure 19.2. UART1 Timing Without Parity or Extra Bit                       |             |

| Figure 19.3. UART1 Timing With Parity 21                                    | 5           |

| Figure 19.4. UART1 Timing With Extra Bit 21                                 | 5           |

| Figure 19.5. Typical UART Interconnect Diagram 21                           | 6           |

| Figure 19.6. UART Multi-Processor Mode Interconnect Diagram                 | 8           |

| 20. Enhanced Serial Peripheral Interface (SPI0)                             |             |

| Figure 20.1. SPI Block Diagram 22                                           | 22          |

| Figure 20.2. Multiple-Master Mode Connection Diagram                        |             |

| Figure 20.3. 3-Wire Single Master and Slave Mode Connection Diagram         |             |

| Figure 20.4. 4-Wire Single Master Mode and Slave Mode Connection Diagram 22 |             |

| Figure 20.5. Master Mode Data/Clock Timing 22                               |             |

| Figure 20.6. Slave Mode Data/Clock Timing (CKPHA = 0)                       |             |

| Figure 20.7. Slave Mode Data/Clock Timing (CKPHA = 1)                       |             |

| Figure 20.8. SPI Master Timing (CKPHA = 0) 23                               |             |

| Figure 20.9. SPI Master Timing (CKPHA = 1)                                  |             |

| Figure 20.10. SPI Slave Timing (CKPHA = 0)                                  |             |

| Figure 20.11. SPI Slave Timing (CKPHA = 1)                                  |             |

| 21. Timers                                                                  |             |

| Figure 21.1. T0 Mode 0 Block Diagram 23                                     | 36          |

| Figure 21.2. T0 Mode 2 Block Diagram                                        |             |

| Figure 21.3. T0 Mode 3 Block Diagram                                        |             |

| Figure 21.4. Timer 2 16-Bit Mode Block Diagram                              |             |

| Figure 21.5. Timer 2 8-Bit Mode Block Diagram                               |             |

| Figure 21.6. Timer 2 Capture Mode (T2SPLIT = '0')                           |             |

| Figure 21.7. Timer 2 Capture Mode $(T2SPLIT = '1')$                         |             |

| Figure 21.8. Timer 3 16-Bit Mode Block Diagram                              |             |

| Figure 21.9. Timer 3 8-Bit Mode Block Diagram                               |             |

| Figure 21.10. Timer 3 Capture Mode (T3SPLIT = '0')                          |             |

| Figure 21.11. Timer 3 Capture Mode (T3SPLIT = '1')                          | 52          |

| 22. Programmable Counter Array (PCA0)                                       |             |

| Figure 22.1. PCA Block Diagram                                              | 55          |

| Figure 22.2. PCA Counter/Timer Block Diagram                                |             |

| Figure 22.3. PCA Interrupt Block Diagram                                    |             |

| Figure 22.4. PCA Capture Mode Diagram                                       |             |

| Figure 22.5. PCA Software Timer Mode Diagram                                |             |

| Figure 22.6. PCA High Speed Output Mode Diagram                             |             |

| Figure 22.7. PCA Frequency Output Mode                                      |             |

| Figure 22.8. PCA 8-Bit PWM Mode Diagram                                     |             |

| Figure 22.9. PCA 16-Bit PWM Mode                                            |             |

| Figure 22.10. PCA Module 4 with Watchdog Timer Enabled                      |             |

| 23. C2 Interface                                                            | <i>,</i> -т |

| Figure 23.1. Typical C2 Pin Sharing                                         | 73          |

|                                                                             | -           |

### 2. Absolute Maximum Ratings

| Parameter                                                       | Conditions | Min  | Тур | Max | Units |

|-----------------------------------------------------------------|------------|------|-----|-----|-------|

| Ambient temperature under bias                                  |            | -55  |     | 125 | °C    |

| Storage Temperature                                             |            | -65  |     | 150 | °C    |

| Voltage on any Port I/O Pin or RST with respect to GND          |            | -0.3 |     | 5.8 | V     |

| Voltage on $V_{DD}$ with respect to GND                         |            | -0.3 |     | 4.2 | V     |

| Maximum Total current through $V_{DD}$ and GND                  |            |      |     | 500 | mA    |

| Maximum output current sunk by $\overline{RST}$ or any Port pin |            |      |     | 100 | mA    |

#### Table 2.1. Absolute Maximum Ratings\*

\*Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### SFR Definition 5.2. AMX0N: AMUX0 Negative Channel Select

| R        | R            | R         | R/W           | R/W              | R/W     | R/W               | R/W           | Reset Value |  |

|----------|--------------|-----------|---------------|------------------|---------|-------------------|---------------|-------------|--|

| -        | -            | -         | AMX0N4        | AMX0N3           | AMX0N2  | AMX0N1            | AMX0N0        | 00000000    |  |

| Bit7     | Bit6         | Bit5      | Bit4          | Bit3             | Bit2    | Bit1              | Bit0          | SFR Address |  |

|          |              |           |               |                  |         |                   |               | 0xBA        |  |

| Bito7 5. | UNUSED. R    | ood - 000 | h: Mrito – de | n't coro         |         |                   |               |             |  |

|          | AMX0N4-0:    |           | ,             |                  |         |                   |               |             |  |

| Dito+ 0. | Note that wh |           |               |                  |         | DC0 operate       | es in Sinale  | -ended      |  |

|          | mode. For al |           |               |                  |         |                   |               |             |  |

|          |              |           | 5 1           | ,                | •       |                   |               |             |  |

|          | AMX0         | N4-0      |               | Negative I       |         |                   | gative Inpu   | t           |  |

|          |              |           | (32-          | pin Packag       | je)     |                   | Package)      |             |  |

|          | 000          |           |               | P1.0             |         |                   | 2.0           |             |  |

|          | 000          |           |               | P1.1             |         |                   | 2.1           |             |  |

|          | 000          |           |               | P1.2             |         |                   | 2.2           |             |  |

|          | 000          |           |               | P1.3             |         |                   | P2.3          |             |  |

|          | 001          |           |               | P1.4             |         |                   | P2.5          |             |  |

|          | 001          |           |               | P1.5             |         |                   | P2.6          |             |  |

|          | 001          |           |               | P1.6             |         |                   | P3.0          |             |  |

|          | 001          |           | P1.7          |                  |         | P3.1              |               |             |  |

|          | 010          |           |               | P2.0             |         |                   | P3.4          |             |  |

|          | 010          |           |               | P2.1             |         |                   | P3.5          |             |  |

|          | 010          |           |               | P2.2             |         |                   | P3.7          |             |  |

|          | 010          |           |               | P2.3             |         |                   | P4.0          |             |  |

|          | 011          |           |               | P2.4             |         |                   | P4.3          |             |  |

|          | 011          |           |               | P2.5             |         |                   | P4.4          |             |  |

|          | 011          |           |               | P2.6             |         |                   | P4.5          |             |  |

|          | 011          |           |               | P2.7             |         |                   | P4.6          |             |  |

|          | 100          |           |               | P3.0             |         | RESERVED          |               |             |  |

|          | 100          |           |               | P0.0             |         | P0.3              |               |             |  |

|          | 100          |           |               | P0.1             |         | P0.4<br>P1.1      |               |             |  |

|          | 100          |           |               | P0.4             |         |                   | 1.1           |             |  |

|          | 10101 -      |           |               | P0.5<br>RESERVED |         |                   | T.Z<br>ERVED  |             |  |

|          | 111          |           | K             | VREF             |         |                   | REF           |             |  |

|          | 111          |           |               | ngle-Ended       | Mode) ( | or<br>SND (Single |               | de)         |  |

|          |              |           |               |                  |         | שוווטו סווועופ    | -டப்பு பிலும் |             |  |

#### Table 5.1. ADC0 Electrical Characteristics

#### $V_{DD}$ = 3.0 V, VREF = 2.40 V, -40 to +85 °C unless otherwise specified

| Parameter                                               | Conditions                                              | Min         | Тур      | Max             | Units    |

|---------------------------------------------------------|---------------------------------------------------------|-------------|----------|-----------------|----------|

|                                                         | DC Accuracy                                             |             |          | I               |          |

| Resolution                                              |                                                         |             | 10       |                 | bits     |

| Integral Nonlinearity                                   |                                                         |             | ±0.5     | ±1              | LSB      |

| Differential Nonlinearity                               | Guaranteed Monotonic                                    |             | ±0.5     | ±1              | LSB      |

| Offset Error                                            |                                                         | -15         | 0        | +15             | LSB      |

| Full Scale Error                                        |                                                         | -15         | -1       | +15             | LSB      |

| Offset Temperature Coefficient                          |                                                         |             | 10       |                 | ppm/°C   |

| Dynamic Performance (10 kHz                             | z sine-wave Single-ended inpu                           | ut, 1 dB be | low Full | Scale, 2        | 00 ksps) |

| Signal-to-Noise Plus Distortion                         |                                                         | 51          | 52.5     |                 | dB       |

| Total Harmonic Distortion                               | Up to the 5 <sup>th</sup> harmonic                      |             | -67      |                 | dB       |

| Spurious-Free Dynamic Range                             |                                                         |             | 78       |                 | dB       |

|                                                         | Conversion Rate                                         |             |          |                 |          |

| SAR Conversion Clock                                    |                                                         |             |          | 3               | MHz      |

| Conversion Time in SAR Clocks                           |                                                         | 10          |          |                 | clocks   |

| Track/Hold Acquisition Time                             |                                                         | 300         |          |                 | ns       |

| Throughput Rate                                         |                                                         |             |          | 200             | ksps     |

|                                                         | Analog Inputs                                           |             |          |                 |          |

| ADC Input Voltage Range                                 | Single Ended (AIN+ – GND)<br>Differential (AIN+ – AIN–) | 0<br>–VREF  |          | VREF<br>VREF    | V<br>V   |

| Absolute Pin Voltage with respect to GND                | Single Ended or Differential                            | 0           |          | V <sub>DD</sub> | V        |

| Input Capacitance                                       |                                                         |             | 5        |                 | pF       |

|                                                         | Temperature Sensor                                      |             |          |                 |          |

| Linearity <sup>1</sup>                                  |                                                         |             | ±0.1     |                 | °C       |

| Gain                                                    |                                                         |             | 2.86     |                 | mV/°C    |

| Gain Error <sup>2</sup>                                 |                                                         |             | ±33.5    |                 | µV/⁰C    |

| Offset <sup>1</sup>                                     | (Temp = 0 °C)                                           |             | 776      |                 | mV       |

| Offset Error <sup>2</sup>                               |                                                         |             | ±8.51    |                 | mV       |

|                                                         | Power Specifications                                    | 1           |          | 1               |          |

| Power Supply Current (V <sub>DD</sub> supplied to ADC0) | Operating Mode, 200 ksps                                |             | 400      | 900             | μA       |

| Power Supply Rejection                                  |                                                         |             | ±0.3     |                 | mV/V     |

Notes:

1. Includes ADC offset, gain, and linearity variations.

2. Represents one standard deviation from the mean.

#### 9.4. Power Management Modes

The CIP-51 core has two software programmable power management modes: Idle and Stop. Idle mode halts the CPU while leaving the peripherals and clocks active. In Stop mode, the CPU is halted, all interrupts, are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not affected). Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode consumes the least power. Figure 1.15 describes the Power Control Register (PCON) used to control the CIP-51's power management modes.

Although the CIP-51 has Idle and Stop modes built in (as with any standard 8051 architecture), power management of the entire MCU is better accomplished through system clock and individual peripheral management. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off the oscillators lowers power consumption considerably; however a reset is required to restart the MCU.

The internal oscillator can be placed in Suspend mode (see **Section "14. Oscillators" on page 131**). In Suspend mode, the internal oscillator is stopped until a non-idle USB event is detected, or the VBUS input signal matches the polarity selected by the VBPOL bit in register REGOCN (SFR Definition 8.1).

#### 9.4.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to **Section "11.6. PCA Watchdog Timer Reset" on page 103** for more information on the use and configuration of the WDT.

#### 9.4.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100 µsec.

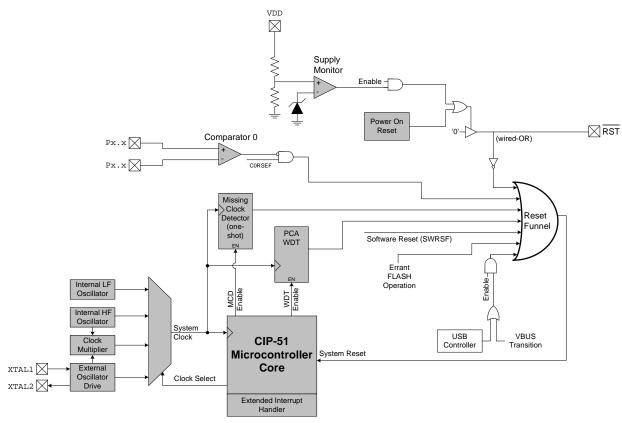

### 11. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pull-ups are enabled during and after the reset. For  $V_{DD}$  Monitor and Power-On Resets, the RST pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. Refer to **Section "14. Oscillators" on page 131** for information on selecting and configuring the system clock source. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source (**Section "22.3. Watchdog Timer Mode" on page 264** details the use of the Watchdog Timer). Program execution begins at location 0x0000.

Figure 11.1. Reset Sources

#### **13.3.** Configuring the External Memory Interface

Configuring the External Memory Interface consists of five steps:

- 1. Configure the Output Modes of the associated port pins as either push-pull or open-drain (push-pull is most common), and skip the associated pins in the crossbar.

- 2. Configure Port latches to "park" the EMIF pins in a dormant state (usually by setting them to logic '1').

- 3. Select Multiplexed mode or Non-multiplexed mode.

- 4. Select the memory mode (on-chip only, split mode without bank select, split mode with bank select, or off-chip only).

- 5. Set up timing to interface with off-chip memory or peripherals.

Each of these five steps is explained in detail in the following sections. The Port selection, Multiplexed mode selection, and Mode bits are located in the EMI0CF register shown in SFR Definition 13.2.

#### 13.4. Port Configuration

The External Memory Interface appears on Ports 4, 3, 2, and 1 when it is used for off-chip memory access. When the EMIF is used, the Crossbar should be configured to skip over the control lines P1.7 (WR), P1.6 ( $\overline{RD}$ ), and if multiplexed mode is selected P1.3 (ALE) using the P1SKIP register. For more information about configuring the Crossbar, see Section "Figure 15.1. Port I/O Functional Block Diagram (Port 0 through Port 3)" on page 142.

The External Memory Interface claims the associated Port pins for memory operations ONLY during the execution of an off-chip MOVX instruction. Once the MOVX instruction has completed, control of the Port pins reverts to the Port latches or to the Crossbar settings for those pins. See Section "15. Port Input/ Output" on page 142 for more information about the Crossbar and Port operation and configuration. The Port latches should be explicitly configured to 'park' the External Memory Interface pins in a dormant state, most commonly by setting them to a logic 1.

During the execution of the MOVX instruction, the External Memory Interface will explicitly disable the drivers on all Port pins that are acting as Inputs (Data[7:0] during a READ operation, for example). The Output mode of the Port pins (whether the pin is configured as Open-Drain or Push-Pull) is unaffected by the External Memory Interface operation, and remains controlled by the PnMDOUT registers. In most cases, the output modes of all EMIF pins should be configured for push-pull mode.

#### SFR Definition 13.1. EMI0CN: External Memory Interface Control

|     | R/W                             | R/W                                           | R/W                                                                     | R/W                                            | R/W                                | R/W    | R/W    | R/W          | Reset Value |

|-----|---------------------------------|-----------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------|------------------------------------|--------|--------|--------------|-------------|

| P   | GSEL7                           | PGSEL6                                        | PGSEL5                                                                  | PGSEL4                                         | PGSEL3                             | PGSEL2 | PGSEL1 | PGSEL0       | 0000000     |

|     | Bit7                            | Bit6                                          | Bit5                                                                    | Bit4                                           | Bit3                               | Bit2   | Bit1   | Bit0         |             |

|     |                                 |                                               |                                                                         |                                                |                                    |        |        | SFR Address: | 0xAA        |

| Bit | T<br>a<br>R<br>0<br>0<br>0<br>0 | ddress whe<br>AM.<br>x00: 0x000<br>x01: 0x010 | Page Select<br>on using an<br>0 to 0x00FF<br>0 to 0x01FF<br>00 to 0xFEF | Bits provid<br>8-bit MOV><br><del>-</del><br>F | its.<br>le the high t<br>( command |        |        |              |             |

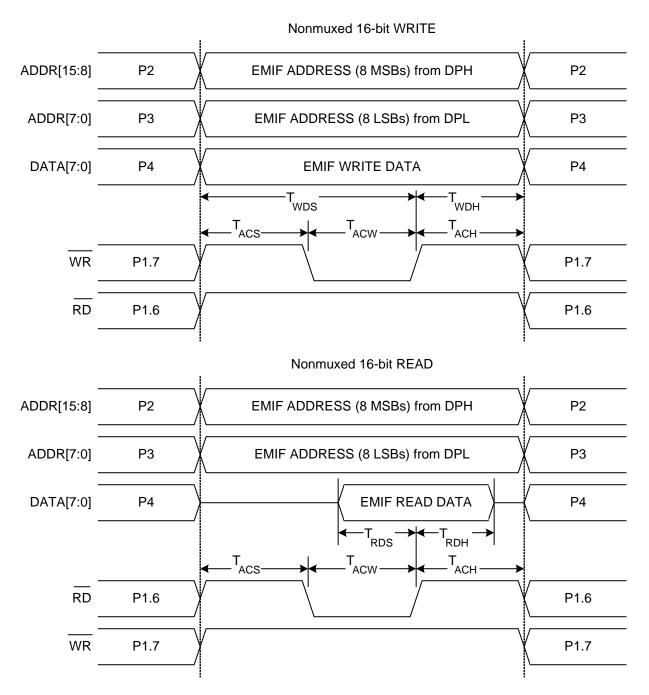

#### 13.7.1. Non-multiplexed Mode

13.7.1.1.16-bit MOVX: EMI0CF[4:2] = '101', '110', or '111'.

Figure 13.5. Non-multiplexed 16-bit MOVX Timing

#### 14.1. Programmable Internal High-Frequency (H-F) Oscillator

All C8051F34x devices include a programmable internal oscillator that defaults as the system clock after a system reset. The internal oscillator period can be programmed via the OSCICL register shown in SFR Definition 14.2. The OSCICL register is factory calibrated to obtain a 12 MHz internal oscillator frequency. Electrical specifications for the precision internal oscillator are given in Table 14.1 on page 141. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

#### 14.1.1. Internal H-F Oscillator Suspend Mode

The internal high-frequency oscillator may be placed in Suspend mode by writing '1' to the SUSPEND bit in register OSCICN. In Suspend mode, the internal H-F oscillator is stopped until a non-idle USB event is detected (**Section 16**) or VBUS matches the polarity selected by the VBPOL bit in register REGOCN (**Section 8.2**). Note that the USB transceiver can still detect USB events when it is disabled.

|          | _             |                | _            |               |              |               |             |              |

|----------|---------------|----------------|--------------|---------------|--------------|---------------|-------------|--------------|

| R/W      | R             | R/W            | R            | R/W           | R/W          | R/W           | R/W         | Reset Value  |

| IOSCEN   | N IFRDY       | SUSPEND        | -            | -             | -            | IFCN1         | IFCN0       | 10000000     |

| Bit7     | Bit6          | Bit5           | Bit4         | Bit3          | Bit2         | Bit1          | Bit0        | SFR Address: |

|          |               |                |              |               |              |               |             | 0xB2         |

|          |               |                |              |               |              |               |             |              |

| Bit7:    | IOSCEN: Int   | •••••••        |              | able Bit.     |              |               |             |              |

|          | 0: Internal H |                |              |               |              |               |             |              |

|          | 1: Internal H |                |              |               |              |               |             |              |

| Bit6:    | IFRDY: Inter  |                |              |               |              |               |             |              |

|          | 0: Internal H |                |              |               |              |               |             |              |

|          | 1: Internal H |                | •            | at program    | med freque   | ncy.          |             |              |

| Bit5:    | SUSPEND:      |                |              |               |              |               |             |              |

|          | Writing a '1' |                |              |               |              |               |             |              |

|          | re-started or |                |              | event (i.e.,  | RESUME s     | signaling) or | · VBUS inte | errupt event |

|          | (see SFR D    | ,              |              |               |              |               |             |              |

|          | UNUSED. R     |                |              |               |              |               |             |              |

| Bits1–0: |               |                |              |               |              | _             |             |              |

|          | 00: SYSCL     |                |              |               |              | •             |             |              |

|          | 01: SYSCL     |                |              |               |              | •             |             |              |

|          | 10: SYSCL     |                |              |               |              | •             |             |              |

|          | 11: SYSCLK    | c derived from | m Internal H | H-F Oscillate | or divided b | y 1.          |             |              |

|          |               |                |              |               |              |               |             |              |

|          |               |                |              |               |              |               |             |              |

#### SFR Definition 14.1. OSCICN: Internal H-F Oscillator Control

| SFR Definition 14.4 | . OSCXCN: External | <b>Oscillator Control</b> |

|---------------------|--------------------|---------------------------|

|---------------------|--------------------|---------------------------|

|                   |             | R/W                                            | R/W          | R             | R/W                     | R/W   | R/W        | Reset Value                                    |  |  |  |  |  |  |

|-------------------|-------------|------------------------------------------------|--------------|---------------|-------------------------|-------|------------|------------------------------------------------|--|--|--|--|--|--|

| XTLVLD            | XOSCM       | D2 XOSCMD1                                     | XOSCMD0      | -             | XFCN2                   | XFCN1 | XFCN0      | 00000000                                       |  |  |  |  |  |  |

| Bit7              | Bit6        | Bit5                                           | Bit4         | Bit3          | Bit2                    | Bit1  | Bit0       | SFR Address                                    |  |  |  |  |  |  |

|                   |             |                                                |              |               |                         |       |            | 0xB1                                           |  |  |  |  |  |  |

| Bit7:             |             | Crystal Occillat                               | or Valid Ela |               |                         |       |            |                                                |  |  |  |  |  |  |

| DILT.             |             | Crystal Oscillat<br>Ily when XOSCI             |              | ıy.           |                         |       |            |                                                |  |  |  |  |  |  |

|                   |             | l Oscillator is ur                             |              | t vet stable. |                         |       |            |                                                |  |  |  |  |  |  |

|                   |             | l Oscillator is ru                             |              |               |                         |       |            |                                                |  |  |  |  |  |  |

| Bits6–4:          | •           | 02–0: External (                               | -            |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   | 00x: Exte   | ernal Oscillator o                             | circuit off. |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   | 010: Exte   | ernal CMOS Clo                                 | ck Mode.     |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   |             | ernal CMOS Clo                                 |              | th divide by  | v 2 stage.              |       |            |                                                |  |  |  |  |  |  |

|                   |             | Oscillator Mode                                |              |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   | •           | acitor Oscillator                              |              |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   |             | stal Oscillator M                              |              |               |                         |       |            |                                                |  |  |  |  |  |  |

| D:+2.             |             | tal Oscillator M                               |              |               | age.                    |       |            |                                                |  |  |  |  |  |  |

| Bit3:<br>Bits2–0: |             | ED. Read = 0, <sup>v</sup><br>D: External Osci |              |               | ol Rite                 |       |            |                                                |  |  |  |  |  |  |

| DIISZ-U.          |             | See table belov                                | •            | iency Contr   | OI DIIS.                |       |            |                                                |  |  |  |  |  |  |

|                   |             |                                                |              |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   |             | Crystal (XOSC                                  | ,            |               | CMD = 10x)              |       | CMD = 10   | <)                                             |  |  |  |  |  |  |

|                   | 000         | f ≤ 32 kł                                      |              | f ≤ 25        |                         |       | tor = 0.87 |                                                |  |  |  |  |  |  |

|                   | 001         | 32 kHz < f ≤                                   |              |               | f ≤ 50 kHz              |       | ctor = 2.6 |                                                |  |  |  |  |  |  |

|                   | 010         | 84 kHz < f ≤ 2                                 |              |               | ≤ 100 kHz               |       | ctor = 7.7 |                                                |  |  |  |  |  |  |

|                   | 011         | 225 kHz < f ≤                                  |              |               | f ≤ 200 kHz             |       | ctor = 22  |                                                |  |  |  |  |  |  |

|                   | 100         | 590 kHz < f ≤                                  |              |               | f ≤ 400 kHz             |       | ctor = 65  |                                                |  |  |  |  |  |  |

|                   | 101         | 1.5 MHz < f ≤                                  |              |               | f ≤ 800 kHz             |       | tor = 180  |                                                |  |  |  |  |  |  |

|                   | 110         | 4 MHz < f ≤ 1                                  |              |               | f ≤ 1.6 MHz             |       | ctor = 664 |                                                |  |  |  |  |  |  |

|                   | 111         | 10 MHz < f ≤                                   | 30 MHz       | 1.6 MHz <     | $f \le 3.2 \text{ MHz}$ | K Fac | tor = 1590 |                                                |  |  |  |  |  |  |

| CRYSTA            | L MODE (    | Circuit from Fig                               | ure 14.1, O  | ption 1; XO   | SCMD = 11               | x)    |            |                                                |  |  |  |  |  |  |

|                   | •           | KFCN value to r                                |              | •             |                         | ,     |            |                                                |  |  |  |  |  |  |

|                   |             |                                                |              |               |                         |       |            |                                                |  |  |  |  |  |  |

| RC MOD            | •           | from Figure 14.                                | •            |               | •                       |       |            |                                                |  |  |  |  |  |  |

|                   |             | KFCN value to r                                | •            | ency range    | :                       |       |            |                                                |  |  |  |  |  |  |

|                   |             | 10 <sup>3</sup> ) / (R x C), w                 |              |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   |             | ency of clock in                               |              |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   | •           | citor value in pF                              |              |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   | K = Pull-   | up resistor value                              | e in κΩ      |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   | (Circuit fr | om Figure 14.1,                                | Ontion 2. V  | ( <u>)</u>    | 10v)                    |       |            |                                                |  |  |  |  |  |  |

|                   |             | K Factor (KF) fo                               |              |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   |             | C x V <sub>DD</sub> ), where                   |              | aon neque     | ity uconeu.             |       |            |                                                |  |  |  |  |  |  |

|                   | -           | ency of clock in                               |              |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   | •           | citor value the >                              |              | ηpF           |                         |       |            |                                                |  |  |  |  |  |  |

|                   |             |                                                |              |               |                         |       |            |                                                |  |  |  |  |  |  |

|                   |             |                                                |              |               |                         |       |            | V <sub>DD</sub> = Power Supply on MCU in volts |  |  |  |  |  |  |

| Internal Oscillator |                                           |                              |  |  |  |  |

|---------------------|-------------------------------------------|------------------------------|--|--|--|--|

| Clock Signal        | Input Source Selection                    | Register Bit Settings        |  |  |  |  |

| USB Clock           | External Oscillator / 4                   | USBCLK = 101b                |  |  |  |  |

| External Oscillator | Crystal Oscillator Mode<br>24 MHz Crystal | XOSCMD = 110b<br>XFCN = 111b |  |  |  |  |

#### SFR Definition 14.6. CLKSEL: Clock Select

|   | R/W  | R/W  | R/W    | R/W  | R/W  | R/W  | R/W   | R/W  | Reset Value |

|---|------|------|--------|------|------|------|-------|------|-------------|

|   | -    |      | USBCLK |      | -    |      | CLKSL |      | 00000000    |

| - | Bit7 | Bit6 | Bit5   | Bit4 | Bit3 | Bit2 | Bit1  | Bit0 | SFR Address |

|   |      |      |        |      |      |      |       |      | 0xA9        |

Bit 7: Unused. Read = 0b; Write = don't care.

Bits6–4: USBCLK2–0: USB Clock Select

These bits select the clock supplied to USB0. When operating USB0 in full-speed mode, the selected clock should be 48 MHz. When operating USB0 in low-speed mode, the selected clock should be 6 MHz.

| USBCLK | Selected Clock          |

|--------|-------------------------|

| 000    | 4x Clock Multiplier     |

| 001    | Internal Oscillator / 2 |

| 010    | External Oscillator     |

| 011    | External Oscillator / 2 |

| 100    | External Oscillator / 3 |

| 101    | External Oscillator / 4 |

| 110    | RESERVED                |

| 111    | RESERVED                |

Bit3: Unused. Read = 0b; Write = don't care.

Bits2–0: CLKSL2–0: System Clock Select

These bits select the system clock source. When operating from a system clock of 25 MHz or less, the FLRT bit should be set to '0'. When operating with a system clock of greater than 25 MHz (up to 48 MHz), the FLRT bit (FLSCL.4) should be set to '1'. See **Section "10. Prefetch Engine" on page 99** for more details.

| CLKSL                                                   | Selected Clock                                                             |  |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|

| 000                                                     | Internal Oscillator (as determined by the<br>IFCN bits in register OSCICN) |  |  |  |  |  |

| 001                                                     | External Oscillator                                                        |  |  |  |  |  |

| 010                                                     | 4x Clock Multiplier / 2                                                    |  |  |  |  |  |

| 011*                                                    | 4x Clock Multiplier*                                                       |  |  |  |  |  |

| 100                                                     | Low-Frequency Oscillator                                                   |  |  |  |  |  |

| 101-111                                                 | RESERVED                                                                   |  |  |  |  |  |

| *Note: This option is only available on 48 MHz devices. |                                                                            |  |  |  |  |  |

#### 16.1. Endpoint Addressing

A total of eight endpoint pipes are available. The control endpoint (Endpoint0) always functions as a bi-directional IN/OUT endpoint. The other endpoints are implemented as three pairs of IN/OUT endpoint pipes:

| Endpoint   | Associated Pipes | USB Protocol Address |  |  |

|------------|------------------|----------------------|--|--|

| Endpoint0  | Endpoint0 IN     | 0x00                 |  |  |

| Enapointo  | Endpoint0 OUT    | 0x00                 |  |  |

| Endpoint1  | Endpoint1 IN     | 0x81                 |  |  |

| Endpoint   | Endpoint1 OUT    | 0x01                 |  |  |

| Endpoint2  | Endpoint2 IN     | 0x82                 |  |  |

| LIndpointz | Endpoint2 OUT    | 0x02                 |  |  |

| Endpoint3  | Endpoint3 IN     | 0x83                 |  |  |

| Endpoint3  | Endpoint3 OUT    | 0x03                 |  |  |

Table 16.1. Endpoint Addressing Scheme

#### 16.2. USB Transceiver

The USB Transceiver is configured via the USB0XCN register shown in SFR Definition 16.1. This configuration includes Transceiver enable/disable, pull-up resistor enable/disable, and device speed selection (Full or Low Speed). When bit SPEED = '1', USB0 operates as a Full Speed USB function, and the on-chip pull-up resistor (if enabled) appears on the D+ pin. When bit SPEED = '0', USB0 operates as a Low Speed USB function, and the on-chip pull-up resistor (if enabled) appears on the D- pin. Bits4-0 of register USB0XCN can be used for Transceiver testing as described in SFR Definition 16.1. The pull-up resistor is enabled only when VBUS is present (see **Section "8.2. VBUS Detection" on page 69** for details on VBUS detection).

Important Note: The USB clock should be active before the Transceiver is enabled.

| Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            | R/W                                                                                                        | R/W                                                                              | R/W                                                                | R/W                                           | R/W                      | R/W                       | R/W                      | Reset Value |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------|--------------------------|---------------------------|--------------------------|-------------|--|

| <ul> <li>This SFR is used to indirectly read and write USB0 registers.</li> <li>Write Procedure: <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write data to USB0DAT.</li> <li>Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> </ol> </li> <li>Read Procedure: <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ul> |                            | USB0DAT 000                                                                                                |                                                                                  |                                                                    |                                               |                          |                           |                          |             |  |

| <ul> <li>This SFR is used to indirectly read and write USB0 registers.</li> <li>Write Procedure: <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write data to USB0DAT.</li> <li>Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> </ol> </li> <li>Read Procedure: <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ul> | Bit7                       | Bit6                                                                                                       | Bit5                                                                             | Bit4                                                               | Bit3                                          | Bit2                     | Bit1                      | Bit0                     | SFR Address |  |

| <ul> <li>Write Procedure:</li> <li>1. Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>2. Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>3. Write data to USB0DAT.</li> <li>4. Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> <li>Read Procedure:</li> <li>1. Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>2. Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>3. Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ul>                                                                           |                            |                                                                                                            |                                                                                  |                                                                    |                                               |                          |                           |                          | 0x97        |  |

| <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write data to USB0DAT.</li> <li>Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> <li>Read Procedure:         <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ol>                                                                                                      | Т                          | This SFR is                                                                                                | used to indi                                                                     | rectly read                                                        | and write U                                   | SB0 registe              | ers.                      |                          |             |  |

| <ol> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write data to USB0DAT.</li> <li>Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> <li>Read Procedure:         <ol> <li>Poll for BUSY (USB_0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ol>                                                                                                                                                     | ٧                          | Nrite Proced                                                                                               | dure:                                                                            |                                                                    |                                               |                          |                           |                          |             |  |

| <ol> <li>Write data to USB0DAT.</li> <li>Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> <li>Read Procedure:         <ol> <li>Poll for BUSY (USB_0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ol>                                                                                                                                                                                                                                            |                            |                                                                                                            |                                                                                  |                                                                    |                                               |                          |                           |                          |             |  |

| <ul> <li>4. Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> <li>Read Procedure: <ol> <li>Poll for BUSY (USB_0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                 |                            |                                                                                                            |                                                                                  |                                                                    | ddress into                                   | the USBAD                | DR bits in I              | register U               | SB0ADR.     |  |

| <ul> <li>Read Procedure:</li> <li>1. Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>2. Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>3. Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       |                            |                                                                                                            |                                                                                  |                                                                    |                                               |                          |                           | • • •                    |             |  |

| <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                         |                            |                                                                                                            |                                                                                  | ha ckinnad                                                         |                                               |                          | no lisen ra               | valetor)                 |             |  |

| <ol> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                          | 4. Repeat (S                                                                                               | Step z may                                                                       | ne svibben                                                         | when whun                                     | ig to the sar            |                           | egister).                |             |  |

| <ol> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i<br/>same write).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |                                                                                                            |                                                                                  | be skipped                                                         | when whun                                     | ig to the sat            |                           | egister).                |             |  |

| same write).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F                          | Read Proced                                                                                                | dure:                                                                            |                                                                    |                                               | ig to the sar            |                           | egister).                |             |  |

| 4. Poll for BUSY (USB 0ADR.7) => '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | F<br>1                     | Read Proced                                                                                                | dure:<br>USY (USB                                                                | 0ADR.7) =                                                          | > '0'.                                        | -                        |                           |                          | SB0ADR.     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | F<br>1<br>2                | Read Proced<br>1. Poll for B<br>2. Load the<br>3. Write '1' t                                              | dure:<br>USY (USB<br>target USB<br>to the BUSY                                   | 0ADR.7) =<br>0 register a                                          | > '0'.<br>ddress into                         | the USBAD                | DR bits in I              | register U               |             |  |

| 5. Read data from USB0DAT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | F<br>1<br>2<br>3           | Read Proced<br>1. Poll for B<br>2. Load the<br>3. Write '1' t<br>same writ                                 | dure:<br>USY (USB<br>target USB<br>to the BUSY<br>te).                           | 0ADR.7) =<br>0 register a<br>′ bit in regis                        | > '0'.<br>ddress into<br>ter USB0AI           | the USBAD                | DR bits in I              | register U               |             |  |

| <ol><li>Repeat from Step 2 (Step 2 may be skipped when reading the same USB0 register<br/>may be skipped when the AUTORD bit (USB0ADR.6) is logic 1).</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | F<br>1<br>2<br>3<br>4<br>5 | Read Proced<br>1. Poll for B<br>2. Load the<br>3. Write '1' t<br>same writ<br>4. Poll for B<br>5. Read dat | dure:<br>USY (USB<br>target USB<br>to the BUSY<br>te).<br>USY (USB<br>a from USB | 0ADR.7) =<br>0 register a<br>′ bit in regis<br>0ADR.7) =<br>00DAT. | > '0'.<br>ddress into<br>ter USB0AI<br>> '0'. | the USBAD<br>DR (steps 2 | DR bits in i<br>and 3 can | register U<br>be perfori | med in the  |  |

#### SFR Definition 16.3. USB0DAT: USB0 Data

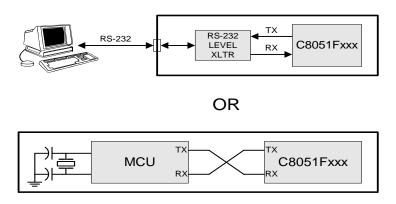

Figure 18.3. UART Interconnect Diagram

#### 18.2.1. 8-Bit UART

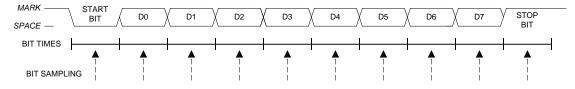

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 18.4. 8-Bit UART Timing Diagram

| Parameter                                             | Description                                      | Min                          | Max                     | Units |  |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------|------------------------------|-------------------------|-------|--|--|--|--|--|

| Master Mode Timing* (See Figure 20.8 and Figure 20.9) |                                                  |                              |                         |       |  |  |  |  |  |

| т <sub>мскн</sub>                                     | SCK High Time                                    | 1 x T <sub>SYSCLK</sub>      |                         | ns    |  |  |  |  |  |

| T <sub>MCKL</sub>                                     | SCK Low Time                                     | 1 x T <sub>SYSCLK</sub>      |                         | ns    |  |  |  |  |  |

| T <sub>MIS</sub>                                      | MISO Valid to SCK Shift Edge                     | 1 x T <sub>SYSCLK</sub> + 20 |                         | ns    |  |  |  |  |  |

| т <sub>мін</sub>                                      | SCK Shift Edge to MISO Change                    | 0                            |                         | ns    |  |  |  |  |  |

|                                                       | Slave Mode Timing* (See Figure 20.10             | and Figure 20.11)            | I                       |       |  |  |  |  |  |

| T <sub>SE</sub>                                       | NSS Falling to First SCK Edge                    | 2 x T <sub>SYSCLK</sub>      |                         | ns    |  |  |  |  |  |

| T <sub>SD</sub>                                       | Last SCK Edge to NSS Rising                      | 2 x T <sub>SYSCLK</sub>      |                         | ns    |  |  |  |  |  |

| T <sub>SEZ</sub>                                      | NSS Falling to MISO Valid                        |                              | 4 x T <sub>SYSCLK</sub> | ns    |  |  |  |  |  |

| T <sub>SDZ</sub>                                      | NSS Rising to MISO High-Z                        |                              | 4 x T <sub>SYSCLK</sub> | ns    |  |  |  |  |  |

| тскн                                                  | SCK High Time                                    | 5 x T <sub>SYSCLK</sub>      |                         | ns    |  |  |  |  |  |

| Т <sub>СКL</sub>                                      | SCK Low Time                                     | 5 x T <sub>SYSCLK</sub>      |                         | ns    |  |  |  |  |  |

| T <sub>SIS</sub>                                      | MOSI Valid to SCK Sample Edge                    | 2 x T <sub>SYSCLK</sub>      |                         | ns    |  |  |  |  |  |

| T <sub>SIH</sub>                                      | SCK Sample Edge to MOSI Change                   | 2 x T <sub>SYSCLK</sub>      |                         | ns    |  |  |  |  |  |

| Т <sub>SOH</sub>                                      | SCK Shift Edge to MISO Change                    |                              | 4 x T <sub>SYSCLK</sub> | ns    |  |  |  |  |  |

| T <sub>SLH</sub>                                      | Last SCK Edge to MISO Change (CKPHA = 1<br>ONLY) | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |  |  |  |  |  |

Table 20.1. SPI Slave Timing Parameters

\*Note:  $T_{SYSCLK}$  is equal to one period of the device system clock (SYSCLK).

#### SFR Definition 21.4. TL0: Timer 0 Low Byte

| R/W  | R/W                                                                                         | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |  |  |

|------|---------------------------------------------------------------------------------------------|------|------|------|------|------|------|--------------|--|--|

|      |                                                                                             |      |      |      |      |      |      | 00000000     |  |  |

| Bit7 | Bit6                                                                                        | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |  |  |

|      |                                                                                             |      |      |      |      |      |      | 0x8A         |  |  |

|      | Bits 7–0: TL0: Timer 0 Low Byte.<br>The TL0 register is the low byte of the 16-bit Timer 0. |      |      |      |      |      |      |              |  |  |

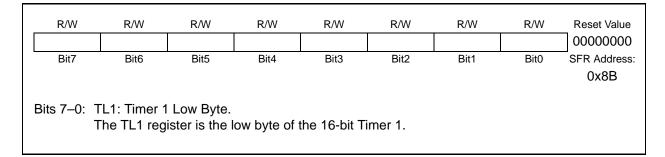

#### SFR Definition 21.5. TL1: Timer 1 Low Byte

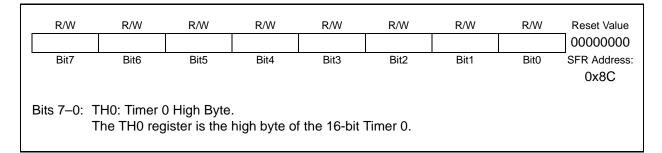

#### SFR Definition 21.6. TH0: Timer 0 High Byte

#### SFR Definition 21.7. TH1: Timer 1 High Byte

|      | R/W                                                                                           | R/W          | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |  |

|------|-----------------------------------------------------------------------------------------------|--------------|------|------|------|------|------|------|--------------|--|

|      |                                                                                               | <b>D</b> lia |      |      |      | Disc |      | Dia  | 00000000     |  |

|      | Bit7                                                                                          | Bit6         | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |  |

|      |                                                                                               |              |      |      |      |      |      |      | 0x8D         |  |

| Bits | Bits 7–0: TH1: Timer 1 High Byte.<br>The TH1 register is the high byte of the 16-bit Timer 1. |              |      |      |      |      |      |      |              |  |

#### SFR Definition 22.4. PCA0L: PCA Counter/Timer Low Byte

| R/W                                                                                                                                 | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value          |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|----------------------|--|--|

| Bit7                                                                                                                                | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xF9 |  |  |

| 0xl<br>Bits 7–0: PCA0L: PCA Counter/Timer Low Byte.<br>The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. |      |      |      |      |      |      |      |                      |  |  |

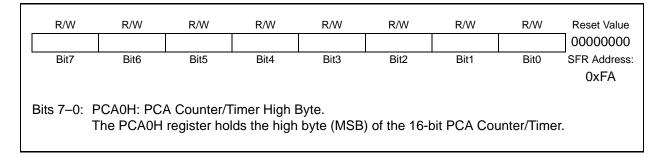

### SFR Definition 22.5. PCA0H: PCA Counter/Timer High Byte

#### SFR Definition 22.6. PCA0CPLn: PCA Capture Module Low Byte

| R/W                                                                                                                                                | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value 00000000               |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------------------------------------|--|

| Bit7                                                                                                                                               | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:                       |  |