Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Not For New Designs                                            |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART, USB                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 21x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f346-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1        | System Overview                                      | 17 |

|----------|------------------------------------------------------|----|

|          | Absolute Maximum Ratings                             |    |

| 3.       |                                                      |    |

| 4.       | Pinout and Package Definitions                       |    |

| <br>5.   | 10-Bit ADC (ADC0, C8051F340/1/2/3/4/5/6/7/A/B Only)  |    |

| 0.       | 5.1. Analog Multiplexer                              |    |

|          | 5.2. Temperature Sensor                              |    |

|          | 5.3. Modes of Operation                              |    |

|          | 5.3.1. Starting a Conversion                         |    |

|          | 5.3.2. Tracking Modes                                |    |

|          | 5.3.3. Settling Time Requirements                    |    |

|          | 5.4. Programmable Window Detector                    |    |

|          | 5.4.1. Window Detector In Single-Ended Mode          |    |

|          | 5.4.2. Window Detector In Differential Mode          |    |

| 6        | Voltage Reference (C8051F340/1/2/3/4/5/6/7/A/B Only) |    |

| о.<br>7. | Comparators                                          | 57 |

|          | Comparators<br>Voltage Regulator (REG0)              | 59 |

| 0.       |                                                      |    |

|          | 8.1. Regulator Mode Selection                        |    |

| •        | 8.2. VBUS Detection                                  |    |

| 9.       | CIP-51 Microcontroller                               |    |

|          | 9.1. Instruction Set                                 |    |

|          | 9.1.1. Instruction and CPU Timing                    |    |

|          | 9.1.2. MOVX Instruction and Program Memory           |    |

|          | 9.2. Memory Organization.                            |    |

|          | 9.2.1. Program Memory                                |    |

|          | 9.2.2. Data Memory                                   |    |

|          | 9.2.3. General Purpose Registers                     |    |

|          | 9.2.4. Bit Addressable Locations                     |    |

|          | 9.2.5. Stack                                         |    |

|          | 9.2.6. Special Function Registers                    |    |

|          | 9.2.7. Register Descriptions                         |    |

|          | 9.3. Interrupt Handler                               |    |

|          | 9.3.1. MCU Interrupt Sources and Vectors             |    |

|          | 9.3.2. External Interrupts                           |    |

|          | 9.3.3. Interrupt Priorities                          |    |

|          | 9.3.4. Interrupt Latency                             |    |

|          | 9.3.5. Interrupt Register Descriptions               | 90 |

|          | 9.4. Power Management Modes                          | 97 |

|          | 9.4.1. Idle Mode                                     | 97 |

|          | 9.4.2. Stop Mode                                     | 97 |

| 10       | Prefetch Engine                                      | 99 |

| 11.      | Reset Sources 1                                      | 00 |

|          | 11.1.Power-On Reset 1                                | 01 |

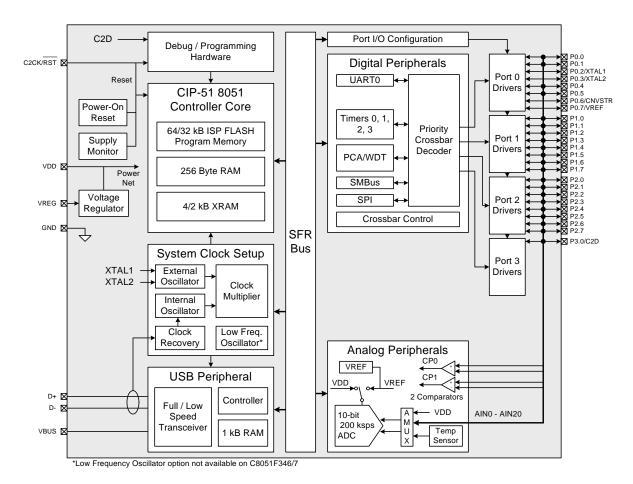

# C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

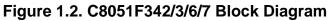

#### SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte

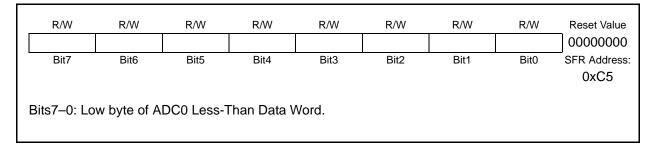

### SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte

## C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

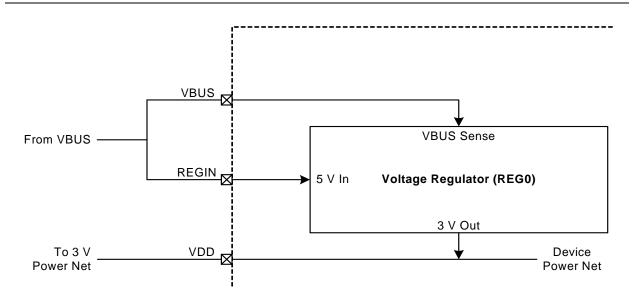

Figure 8.1. REG0 Configuration: USB Bus-Powered

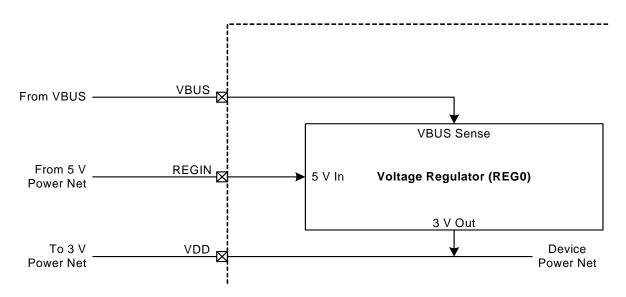

Figure 8.2. REG0 Configuration: USB Self-Powered

## 9. CIP-51 Microcontroller

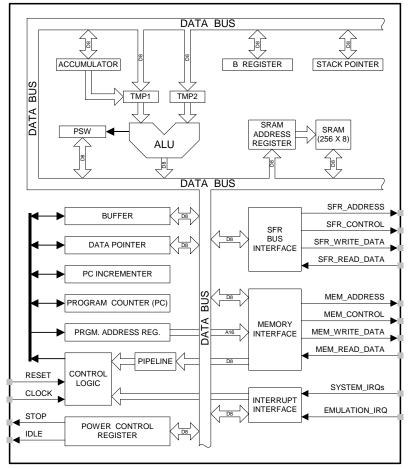

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. Included are four 16-bit counter/timers (see description in **Section 21**), an enhanced full-duplex UART (see description in **Section 18**), an Enhanced SPI (see description in **Section 20**), 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space (**Section 9.2.6**), and 25 Port I/O (see description in **Section 15**). The CIP-51 also includes on-chip debug hardware (see description in **Section 23**), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 9.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 0 to 48 MHz Clock Frequency

- 256 Bytes of Internal RAM

- 25 Port I/O

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### Figure 9.1. CIP-51 Block Diagram

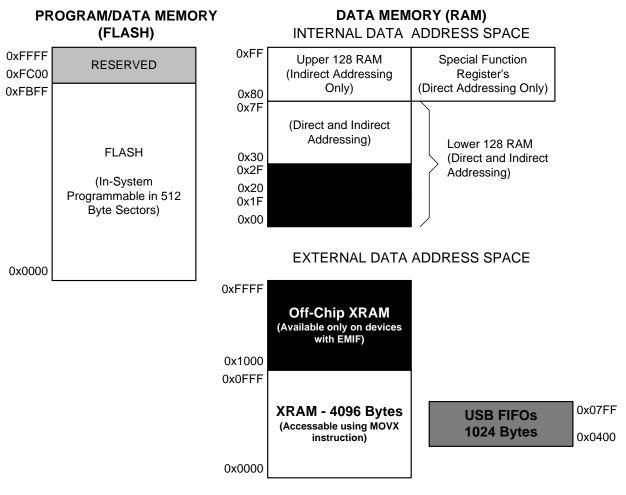

#### 9.2. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The CIP-51 memory organization is shown in Figure 9.2 and Figure 9.3.

Figure 9.2. On-Chip Memory Map for 64 kB Devices

#### SFR Definition 9.6. B: B Register

|   | R/W      | R/W                           | R/W  | R/W         | R/W        | R/W          | R/W         | R/W         | Reset Value  |

|---|----------|-------------------------------|------|-------------|------------|--------------|-------------|-------------|--------------|

| [ | B.7      | B.6                           | B.5  | B.4         | B.3        | B.2          | B.1         | B.0         | 00000000     |

| - | Bit7     | Bit6                          | Bit5 | Bit4        | Bit3       | Bit2         | Bit1        | Bit0        | SFR Address: |

|   |          |                               |      |             |            |              | (bit        | addressable | ) 0xF0       |

| E | Bits7–0: | B: B Registe<br>This register |      | a second ad | ccumulator | or certain a | rithmetic o | perations.  |              |

#### 9.3. Interrupt Handler

The CIP-51 includes an extended interrupt system supporting multiple interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE-EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### 9.3.1. MCU Interrupt Sources and Vectors

The MCU supports multiple interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 9.4 on page 90. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### 9.3.2. External Interrupts

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (**Section "21.1. Timer 0 and Timer 1" on page 235**) select level or edge sensitive. The following table lists the possible configurations.

# C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 9.13). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see **Section "15.1. Priority Crossbar Decoder" on page 144** for complete details on configuring the Crossbar). In the typical configuration, the external interrupt pin should be skipped in the crossbar and configured as open-drain with the pin latch set to '1'.

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

#### 9.3.3. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP or EIP2) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 9.4.

#### 9.3.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 6 system clock cycles: 1 clock cycle to detect the interrupt and 5 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 20 system clock cycles: 1 clock cycle to detect the interrupt, 6 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 5 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

Note that the CPU is stalled during Flash write/erase operations and USB FIFO MOVX accesses (see **Section "13.2. Accessing USB FIFO Space" on page 115**). Interrupt service latency will be increased for interrupts occurring while the CPU is stalled. The latency for these situations will be determined by the standard interrupt service procedure (as described above) and the amount of time the CPU is stalled.

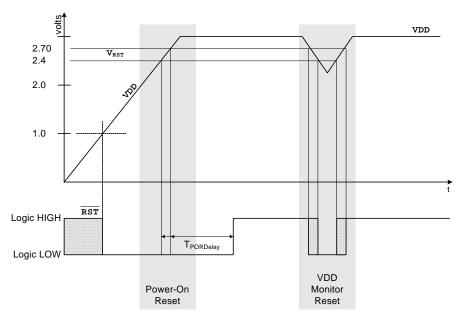

#### 11.1. Power-On Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. A Power-On Reset delay (T<sub>PORDelay</sub>) occurs before the device is released from reset; this delay is typically less than 0.3 ms. Figure 11.2. plots the power-on and V<sub>DD</sub> monitor reset timing.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> monitor is enabled following a power-on reset.

Software can force a power-on reset by writing '1' to the PINRSF bit in register RSTSRC.

Figure 11.2. Power-On and  $V_{\text{DD}}$  Monitor Reset Timing

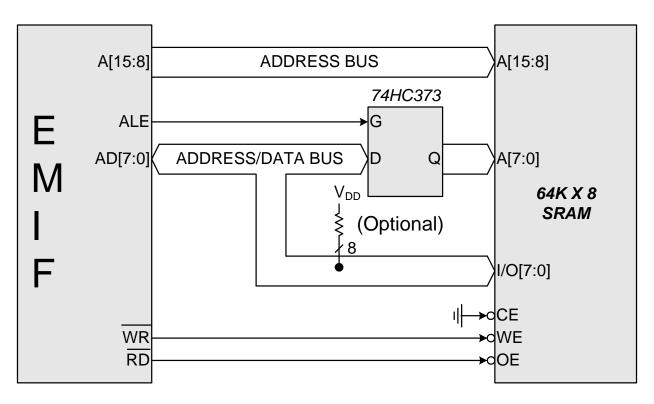

#### 13.5. Multiplexed and Non-multiplexed Selection

The External Memory Interface is capable of acting in a Multiplexed mode or a Non-multiplexed mode, depending on the state of the EMD2 (EMI0CF.4) bit.

#### 13.5.1. Multiplexed Configuration

In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 13.2.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the 'Q' outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time RD or WR is asserted.

See Section "13.7.2. Multiplexed Mode" on page 127 for more information.

Figure 13.2. Multiplexed Configuration Example

#### 14.3.3. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 14.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation. If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

$$f = \frac{1.23(10^3)}{\text{RC}} = \frac{1.23(10^3)}{[246 \times 50]} = 0.1 \text{ MHz} = 100 \text{ kHz}$$

Referring to the table in SFR Definition 14.4, the required XFCN setting is 010b. Programming XFCN to a higher setting in RC mode will improve frequency accuracy at an increased external oscillator supply current.

#### 14.3.4. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 14.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation from the equations below. Assume  $V_{DD} = 3.0$  V and C = 50 pF:

$$f = \frac{KF}{(C \times V_{DD})} = \frac{KF}{(50 \text{ x } 3)\text{MHz}}$$

$$f = \frac{KF}{150 \text{ MHz}}$$

If a frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 14.4 as KF = 22:

$$f = \frac{22}{150} = 0.146$$

MHz, or 146 kHz

Therefore, the XFCN value to use in this example is 011b.

136

| R/W   | R/W                       | R/W                      | R/W              | R/W            | R/W       | R/W   | R/W   | Reset Value  |

|-------|---------------------------|--------------------------|------------------|----------------|-----------|-------|-------|--------------|

| CP1AE |                           | CPOAE                    | CP0E             | SYSCKE         | SMB0E     | SPIOE | URTOE | 00000000     |

| Bit7  | Bit6                      | Bit5                     | Bit4             | Bit3           | Bit2      | Bit1  | Bit0  | SFR Address: |

| DIL7  | DILO                      | БЦЭ                      | DIL4             | BIIS           | DILZ      | DILI  | DILU  | OxE1         |

|       |                           |                          |                  |                |           |       |       | UXEI         |

| Bit7: | CP1AE: Cor                | nnarator1 A              | synchrono        | us Output F    | nahle     |       |       |              |

| Ditr. | 0: Asynchroi              | •                        |                  | •              |           |       |       |              |

|       | 1: Asynchro               |                          |                  |                |           |       |       |              |

| Bit6: | CP1E: Com                 |                          |                  | •              |           |       |       |              |

|       | 0: CP1 unav               |                          | •                |                |           |       |       |              |

|       | 1: CP1 route              | ed to Port pi            | n.               |                |           |       |       |              |

| Bit5: | CP0AE: Cor                | nparator0 <sup>•</sup> A | synchrono        | us Output E    | nable     |       |       |              |

|       | 0: Asynchro               | nous CP0 u               | navailable       | at Port pin.   |           |       |       |              |

|       | 1: Asynchro               | nous CP0 re              | outed to Po      | ort pin.       |           |       |       |              |

| Bit4: | CP0E: Com                 | parator0 Ou              | tput Enable      | e              |           |       |       |              |

|       | 0: CP0 unav               |                          |                  |                |           |       |       |              |

|       | 1: CP0 route              |                          |                  |                |           |       |       |              |

| Bit3: | SYSCKE: /S                |                          | •                |                |           |       |       |              |

|       | 0: /SYSCLK                |                          |                  |                |           |       |       |              |

|       | 1: /SYSCLK                |                          |                  | oin.           |           |       |       |              |

| Bit2: | SMB0E: SM                 |                          |                  |                |           |       |       |              |

|       | 0: SMBus I/               |                          | •                | ins.           |           |       |       |              |

| DIM   | 1: SMBus I/               |                          | Port pins.       |                |           |       |       |              |

| Bit1: | SPI0E: SPI                |                          | • D = = • = := = |                |           |       |       |              |

|       | 0: SPI I/O ur             |                          | •                |                |           |       |       |              |

| Dit0. | 1: SPI I/O ro             |                          | •                |                |           |       |       |              |

| Bit0: | URT0E: UAI<br>0: UART0 I/ |                          | •                |                |           |       |       |              |

|       | 1: UARTO T                |                          |                  |                | nd P0 5   |       |       |              |

|       | 1. UAILIO I.              | NO, INNO 100             |                  | . pins r 0.4 a | nu r 0.J. |       |       |              |

|       |                           |                          |                  |                |           |       |       |              |

#### SFR Definition 15.1. XBR0: Port I/O Crossbar Register 0

| USB Register<br>Name | USB Register<br>Address | Description                                     | Page Number |

|----------------------|-------------------------|-------------------------------------------------|-------------|

| Name                 | Address                 | Interrupt Registers                             |             |

|                      | 0.00                    |                                                 | 470         |

| IN1INT               | 0x02                    | Endpoint0 and Endpoints1-3 IN Interrupt Flags   | 173         |

| OUT1INT              | 0x04                    | Endpoints1-3 OUT Interrupt Flags                | 173         |

| CMINT                | 0x06                    | Common USB Interrupt Flags                      | 174         |

| IN1IE                | 0x07                    | Endpoint0 and Endpoints1-3 IN Interrupt Enables | 175         |

| OUT1IE               | 0x09                    | Endpoints1-3 OUT Interrupt Enables              | 175         |

| CMIE                 | 0x0B                    | Common USB Interrupt Enables                    | 176         |

|                      |                         | Common Registers                                |             |

| FADDR                | 0x00                    | Function Address                                | 169         |

| POWER                | 0x01                    | Power Management                                | 171         |

| FRAMEL               | 0x0C                    | Frame Number Low Byte                           | 172         |

| FRAMEH               | 0x0D                    | Frame Number High Byte                          | 172         |

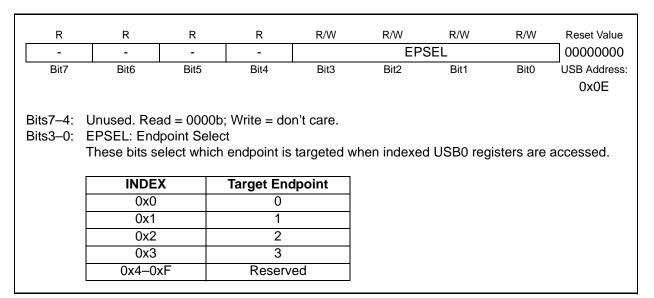

| INDEX                | 0x0E                    | Endpoint Index Selection                        | 165         |

| CLKREC               | 0x0F                    | Clock Recovery Control                          | 166         |

| FIFOn                | 0x20-0x23               | Endpoints0-3 FIFOs                              | 168         |

|                      |                         | Indexed Registers                               |             |

| E0CSR                | 0x11                    | Endpoint0 Control / Status                      | 179         |

| EINCSRL              | 0.00                    | Endpoint IN Control / Status Low Byte           | 182         |

| EINCSRH              | 0x12                    | Endpoint IN Control / Status High Byte          | 183         |

| EOUTCSRL             | 0x14                    | Endpoint OUT Control / Status Low Byte          | 185         |

| EOUTCSRH             | 0x15                    | Endpoint OUT Control / Status High Byte         | 186         |

| E0CNT                | 0x16                    | Number of Received Bytes in Endpoint0 FIFO      | 180         |

| EOUTCNTL             | 01X0                    | Endpoint OUT Packet Count Low Byte              | 186         |

| EOUTCNTH             | 0x17                    | Endpoint OUT Packet Count High Byte             | 186         |

#### Table 16.2. USB0 Controller Registers

#### USB Register Definition 16.4. INDEX: USB0 Endpoint Index

#### 17.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 17.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER and TXMODE indicate the master/slave state and transmit/receive modes, respectively.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a '1' to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a '1' to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 17.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

Table 17.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 17.4 for SMBus status decoding using the SMB0CN register.

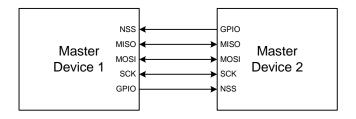

Figure 20.2. Multiple-Master Mode Connection Diagram

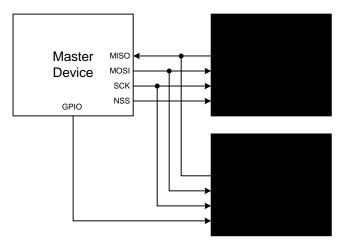

Figure 20.4. 4-Wire Single Master Mode and Slave Mode Connection Diagram

#### 20.5. Serial Clock Timing

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 20.5. For slave mode, the clock and data relationships are shown in Figure 20.6 and Figure 20.7.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 20.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 20.5. Master Mode Data/Clock Timing

# C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

#### 21.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

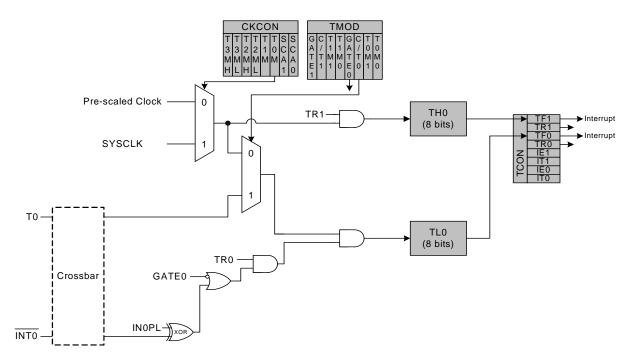

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/ timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

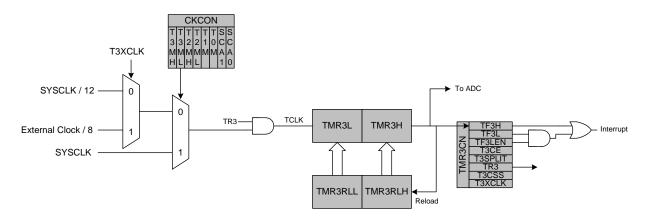

#### 21.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode, (split) 8-bit auto-reload mode, USB Start-of-Frame (SOF) capture mode, or Low-Frequency Oscillator (LFO) Rising Edge capture mode. The Timer 3 operation mode is defined by the T3SPLIT (TMR3CN.3), T3CE (TMR3CN.4) bits, and T3CSS (TMR3CN.1) bits.

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 3 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 21.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is '0' and T3CE = '0', Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TM3RLL) is loaded into the Timer 3 register as shown in Figure 21.4, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled, an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x00.

Figure 21.8. Timer 3 16-Bit Mode Block Diagram

| R/W   | R/W                                                                                     | R/W           | R/W          | R/W           | R/W           | R/W           | R/W          | Reset Value  |  |  |

|-------|-----------------------------------------------------------------------------------------|---------------|--------------|---------------|---------------|---------------|--------------|--------------|--|--|

| TF3H  | TF3L                                                                                    | TF3LEN        | T3CE         | T3SPLIT       | TR3           | T3CSS         | T3XCLK       | 00000000     |  |  |

| Bit7  | Bit6                                                                                    | Bit5          | Bit4         | Bit3          | Bit2          | Bit1          | Bit0         | SFR Address: |  |  |

|       |                                                                                         |               |              |               |               |               |              | 0x91         |  |  |

|       |                                                                                         |               |              |               |               |               |              |              |  |  |

| Bit7: | TF3H: Time                                                                              |               |              | -             |               |               |              |              |  |  |

|       | Set by hard                                                                             |               |              |               |               |               |              |              |  |  |

|       | this will occu                                                                          |               |              |               |               |               |              |              |  |  |

|       | enabled, set                                                                            | •             |              |               |               |               |              |              |  |  |

| Ditc  | TF3H is not                                                                             |               |              |               | and must      | be cleared i  | by software  |              |  |  |

| Bit6: | TF3L: Timer<br>Set by hard                                                              |               |              | •             | orflowe from  | m OvEE to O   |              | this hit is  |  |  |

|       | set, an interi                                                                          |               |              |               |               |               |              |              |  |  |

|       | will set wher                                                                           |               |              |               |               |               |              |              |  |  |

|       | ically cleared                                                                          | •             |              | o regulación  |               |               |              | or automat   |  |  |

| Bit5: | TF3LEN: Tir                                                                             |               |              | pt Enable.    |               |               |              |              |  |  |

|       | This bit enal                                                                           |               | •            | •             | errupts. If T | F3LEN is s    | et and Time  | er 3 inter-  |  |  |

|       | rupts are en                                                                            |               |              |               |               |               |              |              |  |  |

|       | This bit shou                                                                           | uld be cleare | d when op    | perating Time | er 3 in 16-b  | it mode.      |              |              |  |  |

|       | 0: Timer 3 L                                                                            | ow Byte inte  | rrupts disa  | abled.        |               |               |              |              |  |  |

|       | 1: Timer 3 L                                                                            | •             | •            | bled.         |               |               |              |              |  |  |

| Bit4: | T3CE: Timer 3 Capture Enable                                                            |               |              |               |               |               |              |              |  |  |

|       | 0: Capture f                                                                            |               |              |               |               |               |              |              |  |  |

|       |                                                                                         |               |              | imer is in ca |               |               |              |              |  |  |

|       | by bit T3CS                                                                             |               |              |               |               |               |              |              |  |  |

|       | (TMR3H and<br>TMR3RLH),                                                                 | ,             |              |               |               |               | икзкеп а     | na           |  |  |

| Bit3: | T3SPLIT: Ti                                                                             |               |              | -             | eu (il ellabi | eu).          |              |              |  |  |

| Dito. | When this bi                                                                            |               |              |               | bit timers v  | with auto-re  | load         |              |  |  |

|       | 0: Timer 3 o                                                                            |               | •            |               |               |               | loud.        |              |  |  |

|       | 1: Timer 3 o                                                                            |               |              |               |               |               |              |              |  |  |

| Bit2: | TR3: Timer                                                                              |               |              |               |               |               |              |              |  |  |

|       | This bit enables/disables Timer 3. In 8-bit mode, this bit enables/disables TMR3H only; |               |              |               |               |               |              |              |  |  |

|       | TMR3L is al                                                                             | •             | ed in this m | node.         |               |               |              |              |  |  |

|       | 0: Timer 3 d                                                                            |               |              |               |               |               |              |              |  |  |

|       | 1: Timer 3 e                                                                            |               |              |               |               |               |              |              |  |  |

| Bit1: | T3CSS: Tim                                                                              | •             |              |               |               |               | (4)          |              |  |  |

|       | This bit sele                                                                           |               | •            |               | men bit 13    | CE IS SET TO  | 1.           |              |  |  |

|       | 0: Capture s                                                                            |               |              |               |               | ator          |              |              |  |  |

| Bit0: | 1: Capture s<br>T3XCLK: Tir                                                             |               |              |               |               | a.01.         |              |              |  |  |

| Dito. | This bit sele                                                                           |               |              |               | ner 3. If Ti  | mer 3 is in 8 | 3-bit mode   | this bit     |  |  |

|       | selects the e                                                                           |               |              |               |               |               |              |              |  |  |

|       | Select bits (                                                                           |               |              |               |               | •             |              |              |  |  |

|       | external cloc                                                                           |               |              | -             |               |               |              |              |  |  |

|       | 0: Timer 3 e                                                                            | xternal clock | selection    | is the syster | n clock div   | ided by 12.   |              |              |  |  |

|       |                                                                                         |               |              | is the extern |               | •             | Note that th | e external   |  |  |

|       | oscillator so                                                                           | urce divided  | by 8 is sy   | nchronized w  | vith the sys  | stem clock.   |              |              |  |  |

### SFR Definition 21.13. TMR3CN: Timer 3 Control

#### 22.4. Register Descriptions for PCA

Following are detailed descriptions of the special function registers related to the operation of the PCA.

### SFR Definition 22.1. PCA0CN: PCA Control

|                | R/W                                                                                                                                                                         | R/W                                                                                                                                                             | R/W                                                                                                                                               | R/W                                                                                                                                            | R/W                                                                                                                    | R/W                                                                                      | R/W                                                                                              | Reset Value                                                         |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|

| CF             | CR                                                                                                                                                                          | -                                                                                                                                                               | CCF4                                                                                                                                              | CCF3                                                                                                                                           | CCF2                                                                                                                   | CCF1                                                                                     | CCF0                                                                                             | 0000000                                                             |  |  |  |  |

| Bit7           | Bit6                                                                                                                                                                        | Bit5                                                                                                                                                            | Bit4                                                                                                                                              | Bit3                                                                                                                                           | Bit2                                                                                                                   | Bit1                                                                                     | Bit0                                                                                             | SFR Addres                                                          |  |  |  |  |

|                |                                                                                                                                                                             |                                                                                                                                                                 |                                                                                                                                                   |                                                                                                                                                |                                                                                                                        | (bit                                                                                     | addressable                                                                                      | ) 0xD8                                                              |  |  |  |  |

| Bit7:          | CF: PCA Co                                                                                                                                                                  | unter/Time                                                                                                                                                      | r Overflow F                                                                                                                                      | lag.                                                                                                                                           |                                                                                                                        |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

|                | Set by hardv                                                                                                                                                                | vare when                                                                                                                                                       | the PCA Co                                                                                                                                        | unter/Timer                                                                                                                                    | overflows f                                                                                                            | rom 0xFFFI                                                                               | to 0x000                                                                                         | 0. When the                                                         |  |  |  |  |

|                | Counter/Tim                                                                                                                                                                 |                                                                                                                                                                 |                                                                                                                                                   |                                                                                                                                                |                                                                                                                        |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

|                | to the PCA i                                                                                                                                                                | nterrupt se                                                                                                                                                     | rvice routine                                                                                                                                     | . This bit is                                                                                                                                  | not automa                                                                                                             | tically clear                                                                            | ed by harc                                                                                       | ware and                                                            |  |  |  |  |

|                | must be clea                                                                                                                                                                | ared by sof                                                                                                                                                     | tware.                                                                                                                                            |                                                                                                                                                |                                                                                                                        |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

| Bit6:          | CR: PCA Co                                                                                                                                                                  | ounter/Time                                                                                                                                                     | er Run Contr                                                                                                                                      | ol.                                                                                                                                            |                                                                                                                        |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

|                | This bit enab                                                                                                                                                               |                                                                                                                                                                 |                                                                                                                                                   | Counter/Tim                                                                                                                                    | ier.                                                                                                                   |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

|                | 0: PCA Cou                                                                                                                                                                  |                                                                                                                                                                 |                                                                                                                                                   |                                                                                                                                                |                                                                                                                        |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

|                | 1: PCA Cou                                                                                                                                                                  |                                                                                                                                                                 |                                                                                                                                                   |                                                                                                                                                |                                                                                                                        |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

| Bit5:          | UNUSED. R                                                                                                                                                                   | ,                                                                                                                                                               |                                                                                                                                                   |                                                                                                                                                |                                                                                                                        |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

| Bit4:          |                                                                                                                                                                             | CCF4: PCA Module 4 Capture/Compare Flag.<br>This bit is set by hardware when a match or capture occurs. When the CCF4 interrupt is                              |                                                                                                                                                   |                                                                                                                                                |                                                                                                                        |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

|                |                                                                                                                                                                             |                                                                                                                                                                 |                                                                                                                                                   |                                                                                                                                                | •                                                                                                                      |                                                                                          |                                                                                                  | •                                                                   |  |  |  |  |

|                | enabled, set                                                                                                                                                                | -                                                                                                                                                               |                                                                                                                                                   |                                                                                                                                                |                                                                                                                        | •                                                                                        |                                                                                                  | outine. Thi                                                         |  |  |  |  |

| D:40.          | bit is not aut                                                                                                                                                              |                                                                                                                                                                 |                                                                                                                                                   |                                                                                                                                                | a must be d                                                                                                            | cleared by s                                                                             | sontware.                                                                                        |                                                                     |  |  |  |  |

| Bit3:          | CCF3: PCA                                                                                                                                                                   |                                                                                                                                                                 | •                                                                                                                                                 |                                                                                                                                                | nturo ocou                                                                                                             | a Mhanth                                                                                 | o CCE2 int                                                                                       | orrupt in                                                           |  |  |  |  |

|                | This bit is set by hardware when a match or capture occurs. When the CCF3 interrupt is                                                                                      |                                                                                                                                                                 |                                                                                                                                                   |                                                                                                                                                |                                                                                                                        |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

|                | enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software. |                                                                                                                                                                 |                                                                                                                                                   |                                                                                                                                                |                                                                                                                        |                                                                                          |                                                                                                  |                                                                     |  |  |  |  |

|                |                                                                                                                                                                             | •                                                                                                                                                               |                                                                                                                                                   | ardwara an                                                                                                                                     |                                                                                                                        | loarod by a                                                                              | offware                                                                                          | outine. This                                                        |  |  |  |  |

| Sit2.          | bit is not aut                                                                                                                                                              | omatically                                                                                                                                                      | cleared by h                                                                                                                                      |                                                                                                                                                |                                                                                                                        | cleared by s                                                                             | oftware.                                                                                         | outine. This                                                        |  |  |  |  |

| Bit2:          | bit is not aut<br>CCF2: PCA                                                                                                                                                 | omatically<br>Module 2 (                                                                                                                                        | cleared by h<br>Capture/Con                                                                                                                       | npare Flag.                                                                                                                                    | d must be o                                                                                                            | -                                                                                        |                                                                                                  |                                                                     |  |  |  |  |

| 3it2:          | bit is not aut<br>CCF2: PCA<br>This bit is se                                                                                                                               | omatically<br>Module 2 (<br>t by hardw                                                                                                                          | cleared by h<br>Capture/Con<br>are when a                                                                                                         | npare Flag.<br>match or ca                                                                                                                     | d must be o<br>pture occur                                                                                             | s. When th                                                                               | e CCF2 int                                                                                       | errupt is                                                           |  |  |  |  |

| Bit2:          | bit is not aut<br>CCF2: PCA<br>This bit is se<br>enabled, set                                                                                                               | omatically<br>Module 2 (<br>t by hardw<br>ting this bit                                                                                                         | cleared by h<br>Capture/Con<br>are when a<br>causes the                                                                                           | npare Flag.<br>match or ca<br>CPU to veo                                                                                                       | d must be o<br>pture occur<br>tor to the P                                                                             | s. When th<br>CA interrup                                                                | e CCF2 int<br>ot service re                                                                      | errupt is                                                           |  |  |  |  |

|                | bit is not aut<br>CCF2: PCA<br>This bit is se<br>enabled, set<br>bit is not aut                                                                                             | omatically<br>Module 2 (<br>t by hardw<br>ting this bit<br>omatically                                                                                           | cleared by h<br>Capture/Con<br>are when a<br>causes the<br>cleared by h                                                                           | npare Flag.<br>match or ca<br>CPU to veo<br>ardware an                                                                                         | d must be o<br>pture occur<br>tor to the P                                                                             | s. When th<br>CA interrup                                                                | e CCF2 int<br>ot service re                                                                      | errupt is                                                           |  |  |  |  |

| Bit2:<br>Bit1: | bit is not aut<br>CCF2: PCA<br>This bit is se<br>enabled, set<br>bit is not aut<br>CCF1: PCA                                                                                | omatically<br>Module 2 (<br>It by hardw<br>ting this bit<br>omatically<br>Module 1 (                                                                            | cleared by h<br>Capture/Con<br>are when a<br>causes the<br>cleared by h<br>Capture/Con                                                            | npare Flag.<br>match or ca<br>CPU to veo<br>ardware an<br>npare Flag.                                                                          | d must be o<br>pture occur<br>tor to the P<br>d must be o                                                              | s. When th<br>CA interrup<br>cleared by s                                                | e CCF2 int<br>et service re<br>oftware.                                                          | errupt is<br>outine. This                                           |  |  |  |  |

|                | bit is not aut<br>CCF2: PCA<br>This bit is se<br>enabled, set<br>bit is not aut<br>CCF1: PCA<br>This bit is se                                                              | omatically<br>Module 2 (<br>at by hardw<br>ting this bit<br>omatically<br>Module 1 (<br>at by hardw                                                             | cleared by h<br>Capture/Con<br>are when a<br>causes the<br>cleared by h<br>Capture/Con<br>are when a                                              | npare Flag.<br>match or ca<br>CPU to veo<br>ardware an<br>npare Flag.<br>match or ca                                                           | d must be o<br>pture occur<br>tor to the P<br>d must be o<br>pture occur                                               | s. When th<br>CA interrup<br>cleared by s                                                | e CCF2 int<br>at service re<br>software.<br>e CCF1 int                                           | errupt is<br>outine. This<br>errupt is                              |  |  |  |  |