Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

|                            |                                                                |

| Product Status             | Not For New Designs                                            |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 21x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f347-gm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

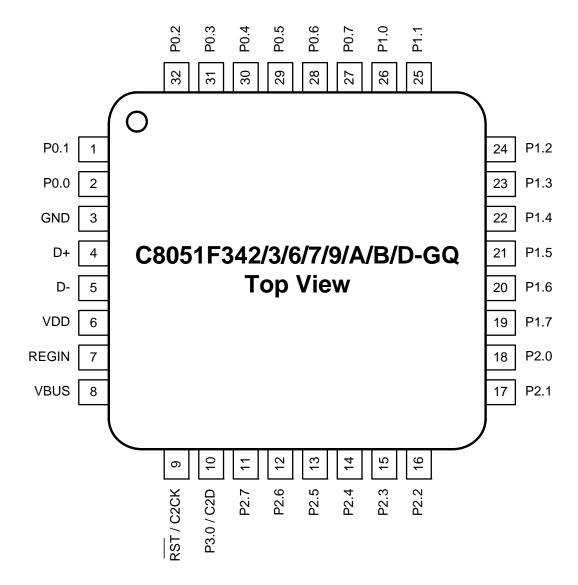

### 4. Pinout and Package Definitions

Table 4.1. Pin Definitions for the C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

| Nome            | Pin Nu | mbers  | Tura             | Description                                                                                                                                                                                  |  |

|-----------------|--------|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name            | 48-pin | 32-pin | Туре             | Description                                                                                                                                                                                  |  |

| V <sub>DD</sub> | 10     | 6      | Power In         | 2.7-3.6 V Power Supply Voltage Input.                                                                                                                                                        |  |

|                 |        |        | Power<br>Out     | 3.3 V Voltage Regulator Output. See <b>Section 8</b> .                                                                                                                                       |  |

| GND             | 7      | 3      |                  | Ground.                                                                                                                                                                                      |  |

| RST/            | 13     | 9      | D I/O            | Device Reset. Open-drain output of internal POR or $V_{DD}$ monitor. An external source can initiate a system reset by driving this pin low for at least 15 $\mu$ s. See <b>Section 11</b> . |  |

| C2CK            |        |        | D I/O            | Clock signal for the C2 Debug Interface.                                                                                                                                                     |  |

| C2D             | 14     |        | D I/O            | Bi-directional data signal for the C2 Debug Interface.                                                                                                                                       |  |

| P3.0 /<br>C2D   | _      | 10     | D I/O<br>D I/O   | Port 3.0. See <b>Section 15</b> for a complete description of F 3.                                                                                                                           |  |

| OZD             |        |        | D 1/O            | Bi-directional data signal for the C2 Debug Interface.                                                                                                                                       |  |

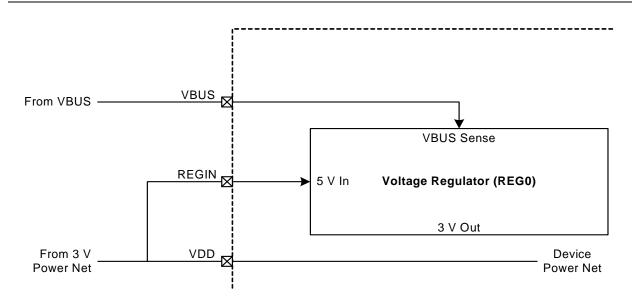

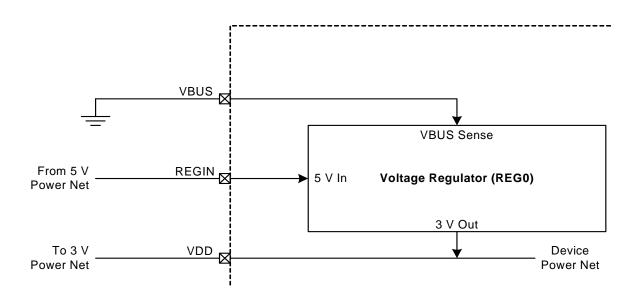

| REGIN           | 11     | 7      | Power In         | 5 V Regulator Input. This pin is the input to the on-chip voltage regulator.                                                                                                                 |  |

| VBUS            | 12     | 8      | D In             | VBUS Sense Input. This pin should be connected to the VBUS signal of a USB network. A 5 V signal on this pin indicates a USB network connection.                                             |  |

| D+              | 8      | 4      | D I/O            | USB D+.                                                                                                                                                                                      |  |

| D-              | 9      | 5      | D I/O            | USB D                                                                                                                                                                                        |  |

| P0.0            | 6      | 2      | D I/O or<br>A In | Port 0.0. See <b>Section 15</b> for a complete description of Port 0.                                                                                                                        |  |

| P0.1            | 5      | 1      | D I/O or<br>A In | Port 0.1.                                                                                                                                                                                    |  |

| P0.2            | 4      | 32     | D I/O or<br>A In | Port 0.2.                                                                                                                                                                                    |  |

| P0.3            | 3      | 31     | D I/O or<br>A In | Port 0.3.                                                                                                                                                                                    |  |

| P0.4            | 2      | 30     | D I/O or<br>A In | Port 0.4.                                                                                                                                                                                    |  |

| P0.5            | 1      | 29     | D I/O or<br>A In | Port 0.5.                                                                                                                                                                                    |  |

| P0.6            | 48     | 28     | D I/O or<br>A In | Port 0.6.                                                                                                                                                                                    |  |

| P0.7            | 47     | 27     | D I/O or<br>A In | Port 0.7.                                                                                                                                                                                    |  |

Figure 4.4. LQFP-32 Pinout Diagram (Top View)

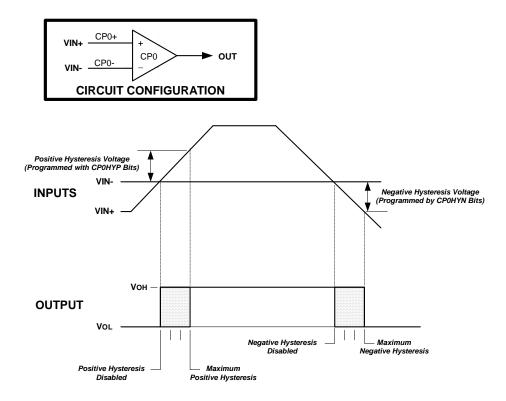

Figure 7.2. Comparator Hysteresis Plot

Comparator hysteresis is programmed using Bits3-0 in the Comparator Control Register CPTnCN (shown in SFR Definition 7.1 and SFR Definition 7.4). The amount of negative hysteresis voltage is determined by the settings of the CPnHYN bits. As shown in Figure 7.2, various levels of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPnHYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see **Section "9.3. Interrupt Handler" on page 88.**) The CPnFIF flag is set to '1' upon a Comparator falling-edge, and the CPnRIF flag is set to '1' upon the Comparator rising-edge. Once set, these bits remain set until cleared by software. The output state of the Comparator can be obtained at any time by reading the CPnOUT bit. The Comparator is enabled by setting the CPnEN bit to '1', and is disabled by clearing this bit to '0'.

Figure 8.3. REG0 Configuration: USB Self-Powered, Regulator Disabled

Figure 8.4. REG0 Configuration: No USB Connection

### SFR Definition 8.1. REG0CN: Voltage Regulator Control

| DAM    | Б      | DAM   | DAM    | DAM      | DAM      | D 444    | DAM      | Danet Value  |

|--------|--------|-------|--------|----------|----------|----------|----------|--------------|

| R/W    | ĸ      | R/W   | R/W    | R/W      | R/W      | R/W      | R/W      | Reset Value  |

| REGDIS | VBSTAT | VBPOL | REGMOD | Reserved | Reserved | Reserved | Reserved | 00000000     |

| Bit7   | Bit6   | Bit5  | Bit4   | Bit3     | Bit2     | Bit1     | Bit0     | SFR Address: |

|        |        |       |        |          |          |          |          | 0xC9         |

Bit7: REGDIS: Voltage Regulator Disable.

0: Voltage Regulator Enabled.

1: Voltage Regulator Disabled.

Bit6: VBSTAT: VBUS Signal Status.

0: VBUS signal currently absent (device not attached to USB network).

1: VBUS signal currently present (device attached to USB network).

Bit5: VBPOL: VBUS Interrupt Polarity Select.

This bit selects the VBUS interrupt polarity.

0: VBUS interrupt active when VBUS is low.

1: VBUS interrupt active when VBUS is high.

Bit4: REGMOD: Voltage Regulator Mode Select.

This bit selects the Voltage Regulator mode. When REGMOD is set to '1', the voltage regu-

lator operates in low power (suspend) mode.0: USB0 Voltage Regulator in normal mode.1: USB0 Voltage Regulator in low power mode.

Bits3–0: Reserved. Read = 0000b. Must Write = 0000b.

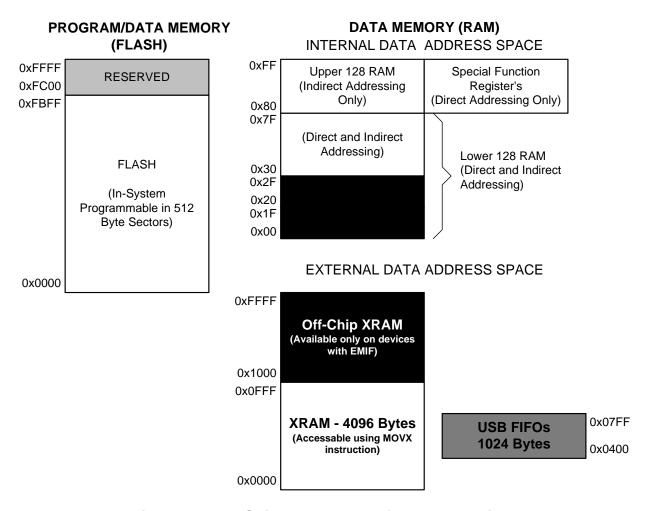

### 9.2. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The CIP-51 memory organization is shown in Figure 9.2 and Figure 9.3.

Figure 9.2. On-Chip Memory Map for 64 kB Devices

### SFR Definition 9.9. EIE1: Extended Interrupt Enable 1

| R/W  | R/W  | R/W  | R/W   | R/W   | R/W    | R/W   | R/W   | Reset Value  |

|------|------|------|-------|-------|--------|-------|-------|--------------|

| ET3  | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | EUSB0 | ESMB0 | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4  | Bit3  | Bit2   | Bit1  | Bit0  | SFR Address: |

|      |      |      |       |       |        |       |       | 0vE6         |

Bit7: ET3: Enable Timer 3 Interrupt.

This bit sets the masking of the Timer 3 interrupt.

0: Disable Timer 3 interrupts.

1: Enable interrupt requests generated by the TF3L or TF3H flags.

Bit6: ECP1: Enable Comparator1 (CP1) Interrupt.

This bit sets the masking of the CP1 interrupt.

0: Disable CP1 interrupts.

1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags.

Bit5: ECP0: Enable Comparator0 (CP0) Interrupt.

This bit sets the masking of the CP0 interrupt.

0: Disable CP0 interrupts.

1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.

Bit4: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.

This bit sets the masking of the PCA0 interrupts.

0: Disable all PCA0 interrupts.

1: Enable interrupt requests generated by PCA0.

Bit3: EADC0: Enable ADC0 Conversion Complete Interrupt.

This bit sets the masking of the ADC0 Conversion Complete interrupt.

0: Disable ADC0 Conversion Complete interrupt.

1: Enable interrupt requests generated by the AD0INT flag.

Bit2: EWADC0: Enable Window Comparison ADC0 Interrupt.

This bit sets the masking of ADC0 Window Comparison interrupt.

0: Disable ADC0 Window Comparison interrupt.

1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).

Bit1: EUSB0: Enable USB0 Interrupt.

This bit sets the masking of the USB0 interrupt.

0: Disable all USB0 interrupts.

1: Enable interrupt requests generated by USB0.

Bit0: ESMB0: Enable SMBus (SMB0) Interrupt.

This bit sets the masking of the SMB0 interrupt.

0: Disable all SMB0 interrupts.

1: Enable interrupt requests generated by SMB0.

### 10. Prefetch Engine

The 48 MHz versions of the C8051F34x family of devices incorporate a 2-byte prefetch engine. Because the access time of the FLASH memory is 40 ns, and the minimum instruction time is roughly 20 ns, the prefetch engine is necessary for full-speed code execution. Instructions are read from FLASH memory two bytes at a time by the prefetch engine, and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine allows instructions to be executed at full speed. When a code branch occurs, the processor may be stalled for up to two clock cycles while the next set of code bytes is retrieved from FLASH memory. The FLRT bit (FLSCL.4) determines how many clock cycles are used to read each set of two code bytes from FLASH. When operating from a system clock of 25 MHz or less, the FLRT bit should be set to '0' so that the prefetch engine takes only one clock cycle for each read. When operating with a system clock of greater than 25 MHz (up to 48 MHz), the FLRT bit should be set to '1', so that each prefetch code read lasts for two clock cycles.

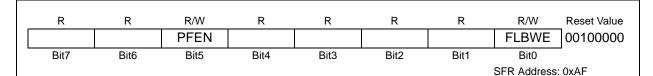

#### SFR Definition 10.1. PFE0CN: Prefetch Engine Control

Bits 7-6: Unused. Read = 00b; Write = Don't Care

Bit 5: PFEN: Prefetch Enable.

This bit enables the prefetch engine.

0: Prefetch engine is disabled.

1: Prefetch engine is enabled.

Bits 4–1: Unused. Read = 0000b; Write = Don't Care

Bit 0: FLBWE: FLASH Block Write Enable.

This bit allows block writes to FLASH memory from software.

0: Each byte of a software FLASH write is written individually.

1: FLASH bytes are written in groups of two.

#### 11.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pull-up and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 11.1 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

#### 11.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If more than 100 µs pass between rising edges on the system clock, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read '1', signifying the MCD as the reset source; otherwise, this bit reads '0'. Writing a '1' to the MCDRSF bit enables the Missing Clock Detector; writing a '0' disables it. The state of the RST pin is unaffected by this reset.

#### 11.5. Comparator Reset

Comparator can be configured as a reset source by writing a '1' to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), a system reset is generated. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read '1' signifying Comparator0 as the reset source; otherwise, this bit reads '0'. The state of the RST pin is unaffected by this reset.

#### 11.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "22.3. Watchdog Timer Mode" on page 264; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to '1'. The state of the RST pin is unaffected by this reset.

#### 11.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to "1", and a MOVX write operation is attempted above address 0x7FFF (32 kB Flash devices) or 0xFBFF (64 kB Flash devices).

- A Flash read is attempted above user code space. This occurs when a MOVC operation is attempted above address 0x7FFF (32 kB Flash devices) or 0xFBFF (64 kB Flash devices).

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above 0x7FFF (32 kB Flash devices) or 0xFBFF (64 kB Flash devices).

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "12.3. Security Options" on page 109).

- A Flash Write or Erase is attempted when the V<sub>DD</sub> monitor is not enabled.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the RST pin is unaffected by this reset.

#### SFR Definition 12.3. FLSCL: Flash Scale

|   | R/W  | R/W      | R/W      | R/W  | R/W      | R/W      | R/W      | R/W      | Reset Value  |

|---|------|----------|----------|------|----------|----------|----------|----------|--------------|

|   | FOSE | Reserved | Reserved | FLRT | Reserved | Reserved | Reserved | Reserved | 10000000     |

| • | Bit7 | Bit6     | Bit5     | Bit4 | Bit3     | Bit2     | Bit1     | Bit0     | SFR Address: |

|   |      |          |          |      |          |          |          |          | 0vB6         |

Bits7: FOSE: Flash One-shot Enable

This bit enables the Flash read one-shot. When the Flash one-shot disabled, the Flash sense amps are enabled for a full clock cycle during Flash reads. At system clock frequencies below 10 MHz, disabling the Flash one-shot will increase system power consumption.

0: Flash one-shot disabled.

1: Flash one-shot enabled.

Bits6-5: RESERVED. Read = 00b. Must Write 00b.

Bit 4: FLRT: FLASH Read Time.

This bit should be programmed to the smallest allowed value, according to the system clock

speed.

0: SYSCLK <= 25 MHz. 1: SYSCLK <= 48 MHz.

Bits3-0: RESERVED. Read = 0000b. Must Write 0000b.

#### 13.6.1. Internal XRAM Only

When EMIOCF.[3:2] are set to '00', all MOVX instructions will target the internal XRAM space on the device. Memory accesses to addresses beyond the populated space will wrap on 2k or 4k boundaries (depending on the RAM available on the device). As an example, the addresses 0x1000 and 0x2000 both evaluate to address 0x0000 in on-chip XRAM space.

- 8-bit MOVX operations use the contents of EMIOCN to determine the high-byte of the effective address and R0 or R1 to determine the low-byte of the effective address.

- 16-bit MOVX operations use the contents of the 16-bit DPTR to determine the effective address.

#### 13.6.2. Split Mode without Bank Select

When EMIOCF.[3:2] are set to '01', the XRAM memory map is split into two areas, on-chip space and off-chip space.

- Effective addresses below the internal XRAM size boundary will access on-chip XRAM space.

- Effective addresses above the internal XRAM size boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is

on-chip or off-chip. However, in the "No Bank Select" mode, an 8-bit MOVX operation will not drive the

upper 8-bits A[15:8] of the Address Bus during an off-chip access. This allows the user to manipulate

the upper address bits at will by setting the Port state directly via the port latches. This behavior is in

contrast with "Split Mode with Bank Select" described below. The lower 8-bits of the Address Bus

A[7:0] are driven, determined by R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or off-chip, and unlike 8-bit MOVX operations, the full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

#### 14. Oscillators

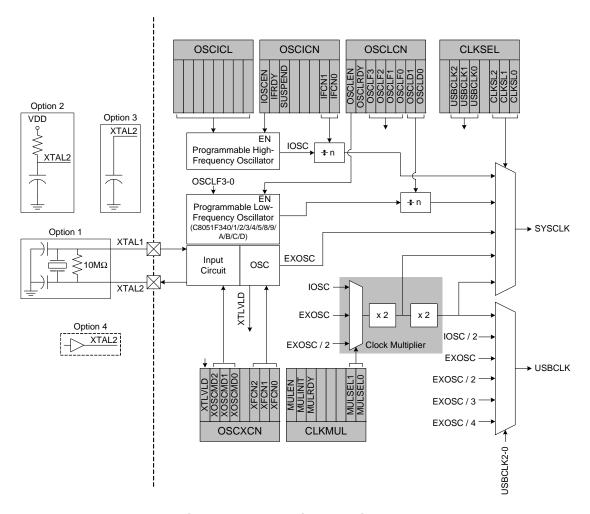

C8051F34x devices include a programmable internal high-frequency oscillator, a programmable internal low-frequency oscillator (C8051F340/1/2/3/4/5/8/9/A/B/C/D), an external oscillator drive circuit, and a 4x Clock Multiplier. The internal high-frequency and low-frequency oscillators can be enabled/disabled and adjusted using the special function registers, as shown in Figure 14.1. The system clock (SYSCLK) can be derived from either of the internal oscillators, the external oscillator circuit, or the 4x Clock Multiplier divided by 2. The USB clock (USBCLK) can be derived from the internal oscillator, external oscillator, or 4x Clock Multiplier. Oscillator electrical specifications are given in Table 14.1.

Figure 14.1. Oscillator Diagram

#### SFR Definition 14.4. OSCXCN: External Oscillator Control

| R      | R/W     | R/W     | R/W     | R    | R/W   | R/W   | R/W   | Reset Value  |

|--------|---------|---------|---------|------|-------|-------|-------|--------------|

| XTLVLD | XOSCMD2 | XOSCMD1 | XOSCMD0 | -    | XFCN2 | XFCN1 | XFCN0 | 00000000     |

| Bit7   | Bit6    | Bit5    | Bit4    | Bit3 | Bit2  | Bit1  | Bit0  | SFR Address: |

|        |         |         |         |      |       |       |       | 0xR1         |

Bit7: XTLVLD: Crystal Oscillator Valid Flag.

(Read only when XOSCMD = 11x.)

0: Crystal Oscillator is unused or not yet stable.

1: Crystal Oscillator is running and stable.

Bits6-4: XOSCMD2-0: External Oscillator Mode Bits.

00x: External Oscillator circuit off. 010: External CMOS Clock Mode.

011: External CMOS Clock Mode with divide by 2 stage.

100: RC Oscillator Mode.

101: Capacitor Oscillator Mode.110: Crystal Oscillator Mode.

111: Crystal Oscillator Mode with divide by 2 stage.

Bit3: RESERVED. Read = 0, Write = don't care.

Bits2-0: XFCN2-0: External Oscillator Frequency Control Bits.

000-111: See table below:

| XFCN | Crystal (XOSCMD = 11x) | RC (XOSCMD = 10x)     | C (XOSCMD = 10x) |

|------|------------------------|-----------------------|------------------|

| 000  | f≤32 kHz               | f≤25 kHz              | K Factor = 0.87  |

| 001  | 32 kHz < f ≤ 84kHz     | 25 kHz < f ≤ 50 kHz   | K Factor = 2.6   |

| 010  | 84 kHz < f ≤ 225 kHz   | 50 kHz < f ≤ 100 kHz  | K Factor = 7.7   |

| 011  | 225 kHz < f ≤ 590 kHz  | 100 kHz < f ≤ 200 kHz | K Factor = 22    |

| 100  | 590 kHz < f ≤ 1.5 MHz  | 200 kHz < f ≤ 400 kHz | K Factor = 65    |

| 101  | 1.5 MHz < f ≤ 4 MHz    | 400 kHz < f ≤ 800 kHz | K Factor = 180   |

| 110  | 4 MHz < f ≤ 10 MHz     | 800 kHz < f ≤ 1.6 MHz | K Factor = 664   |

| 111  | 10 MHz < f ≤ 30 MHz    | 1.6 MHz < f ≤ 3.2 MHz | K Factor = 1590  |

**CRYSTAL MODE** (Circuit from Figure 14.1, Option 1; XOSCMD = 11x) Choose XFCN value to match crystal or resonator frequency.

**RC MODE** (Circuit from Figure 14.1, Option 2; XOSCMD = 10x)

Choose XFCN value to match frequency range:

$f = 1.23(10^3) / (R \times C)$ , where

f = frequency of clock in MHz

C = capacitor value in pF

R = Pull-up resistor value in  $k\Omega$

**C MODE** (Circuit from Figure 14.1, Option 3; XOSCMD = 10x)

Choose K Factor (KF) for the oscillation frequency desired:

$f = KF / (C \times V_{DD})$ , where

f = frequency of clock in MHz

C = capacitor value the XTAL2 pin in pF

V<sub>DD</sub> = Power Supply on MCU in volts

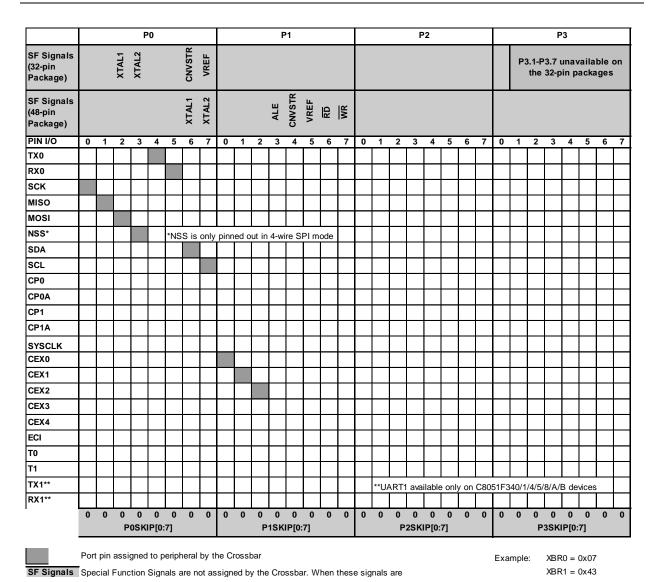

Figure 15.4. Crossbar Priority Decoder in Example Configuration (No Pins Skipped)

SILICON LABS

### 16.1. Endpoint Addressing

A total of eight endpoint pipes are available. The control endpoint (Endpoint0) always functions as a bi-directional IN/OUT endpoint. The other endpoints are implemented as three pairs of IN/OUT endpoint pipes:

Table 16.1. Endpoint Addressing Scheme

| Endpoint    | Associated Pipes | USB Protocol Address |  |  |

|-------------|------------------|----------------------|--|--|

| Endpoint0   | Endpoint0 IN     | 0x00                 |  |  |

| Enapointo   | Endpoint0 OUT    | 0x00                 |  |  |

| Endpoint1   | Endpoint1 IN     | 0x81                 |  |  |

| Enapointi   | Endpoint1 OUT    | 0x01                 |  |  |

| Endpoint2   | Endpoint2 IN     | 0x82                 |  |  |

| Litupolitiz | Endpoint2 OUT    | 0x02                 |  |  |

| Endpoint3   | Endpoint3 IN     | 0x83                 |  |  |

| Litupolitio | Endpoint3 OUT    | 0x03                 |  |  |

#### 16.2. USB Transceiver

The USB Transceiver is configured via the USB0XCN register shown in SFR Definition 16.1. This configuration includes Transceiver enable/disable, pull-up resistor enable/disable, and device speed selection (Full or Low Speed). When bit SPEED = '1', USB0 operates as a Full Speed USB function, and the on-chip pull-up resistor (if enabled) appears on the D+ pin. When bit SPEED = '0', USB0 operates as a Low Speed USB function, and the on-chip pull-up resistor (if enabled) appears on the D- pin. Bits4-0 of register USB0XCN can be used for Transceiver testing as described in SFR Definition 16.1. The pull-up resistor is enabled only when VBUS is present (see **Section "8.2. VBUS Detection" on page 69** for details on VBUS detection).

Important Note: The USB clock should be active before the Transceiver is enabled.

SILICON LABS

#### 16.5. FIFO Management

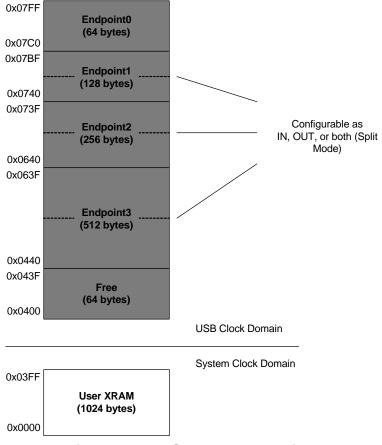

1024 bytes of on-chip XRAM are used as FIFO space for USB0. This FIFO space is split between Endpoints0-3 as shown in Figure 16.3. FIFO space allocated for Endpoints1-3 is configurable as IN, OUT, or both (Split Mode: half IN, half OUT).

Figure 16.3. USB FIFO Allocation

#### 16.5.1. FIFO Split Mode

The FIFO space for Endpoints1-3 can be split such that the upper half of the FIFO space is used by the IN endpoint, and the lower half is used by the OUT endpoint. For example: if the Endpoint3 FIFO is configured for Split Mode, the upper 256 bytes (0x0540 to 0x063F) are used by Endpoint3 IN and the lower 256 bytes (0x0440 to 0x053F) are used by Endpoint3 OUT.

If an endpoint FIFO is not configured for Split Mode, that endpoint IN/OUT pair's FIFOs are combined to form a single IN *or* OUT FIFO. In this case only one direction of the endpoint IN/OUT pair may be used at a time. The endpoint direction (IN/OUT) is determined by the DIRSEL bit in the corresponding endpoint's EINCSRH register (see SFR Definition 16.20).

#### SFR Definition 17.2. SMB0CN: SMBus Control

| R      | R      | R/W  | R/W  | R     | R       | R/W  | R/W  | Reset Value        |

|--------|--------|------|------|-------|---------|------|------|--------------------|

| MASTER | TXMODE | STA  | STO  | ACKRQ | ARBLOST | ACK  | SI   | 00000000           |

| Bit7   | Bit6   | Bit5 | Bit4 | Bit3  | Bit2    | Bit1 | Bit0 | Bit<br>Addressable |

SFR Address: 0xC0

Bit7: MASTER: SMBus Master/Slave Indicator.

This read-only bit indicates when the SMBus is operating as a master.

0: SMBus operating in Slave Mode.

1: SMBus operating in Master Mode.

Bit6: TXMODE: SMBus Transmit Mode Indicator.

This read-only bit indicates when the SMBus is operating as a transmitter.

0: SMBus in Receiver Mode.

1: SMBus in Transmitter Mode.

Bit5: STA: SMBus Start Flag.

Write:

0: No Start generated.

1: When operating as a master, a START condition is transmitted if the bus is free (If the bus is not free, the START is transmitted after a STOP is received or a timeout is detected). If STA is set by software as an active Master, a repeated START will be generated after the next ACK cycle.

Read:

0: No Start or repeated Start detected.

1: Start or repeated Start detected.

Bit4: STO: SMBus Stop Flag.

Write:

0: No STOP condition is transmitted.

1: Setting STO to logic 1 causes a STOP condition to be transmitted after the next ACK cycle. When the STOP condition is generated, hardware clears STO to logic 0. If both STA and STO are set, a STOP condition is transmitted followed by a START condition.

Read:

0: No Stop condition detected.

1: Stop condition detected (if in Slave Mode) or pending (if in Master Mode).

Bit3: ACKRQ: SMBus Acknowledge Request

This read-only bit is set to logic 1 when the SMBus has received a byte and needs the ACK bit to be written with the correct ACK response value.

Bit2: ARBLOST: SMBus Arbitration Lost Indicator.

This read-only bit is set to logic 1 when the SMBus loses arbitration while operating as a transmitter. A lost arbitration while a slave indicates a bus error condition.

Bit1: ACK: SMBus Acknowledge Flag.

This bit defines the out-going ACK level and records incoming ACK levels. It should be written each time a byte is received (when ACKRQ=1), or read after each byte is transmitted.

0: A "not acknowledge" has been received (if in Transmitter Mode) OR will be transmitted (if in Receiver Mode).

1: An "acknowledge" has been received (if in Transmitter Mode) OR will be transmitted (if in Receiver Mode).

Bit0: SI: SMBus Interrupt Flag.

This bit is set by hardware under the conditions listed in Table 17.3. SI must be cleared by software. While SI is set, SCL is held low and the SMBus is stalled.

### SFR Definition 18.2. SBUF0: Serial (UART0) Port Data Buffer

| R/V | V | R/W         | Reset Value |

|-----|---|------|------|------|------|------|------|-------------|-------------|

|     |   |      |      |      |      |      |      |             | 00000000    |

| Bit | 7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0        | _           |

|     |   |      |      |      |      |      |      | SFR Address | : 0x99      |

Bits7–0: SBUF0[7:0]: Serial Data Buffer Bits 7–0 (MSB-LSB)

This SFR accesses two registers; a transmit shift register and a receive latch register. When data is written to SBUF0, it goes to the transmit shift register and is held for serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of SBUF0 returns the contents of the receive latch.

#### SFR Definition 20.3. SPI0CKR: SPI0 Clock Rate

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

| SCR7 | SCR6 | SCR5 | SCR4 | SCR3 | SCR2 | SCR1 | SCR0 | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | <del>_</del> |

SFR Address: 0xA2

#### Bits 7-0: SCR7-SCR0: SPI0 Clock Rate.

These bits determine the frequency of the SCK output when the SPI0 module is configured for master mode operation. The SCK clock frequency is a divided version of the system clock, and is given in the following equation, where SYSCLK is the system clock frequency and SPIOCKR is the 8-bit value held in the SPIOCKR register.

$$f_{SCK} = \frac{SYSCLK}{2 \times (SPI0CKR + 1)}$$

Example: If SYSCLK = 2 MHz and SPI0CKR = 0x04,

$$f_{SCK} = \frac{2000000}{2 \times (4+1)}$$

$$f_{SCK} = 200kHz$$

$$f_{SCK} = 200kHz$$

#### SFR Definition 20.4. SPI0DAT: SPI0 Data

|   | R/W        | Reset Value |

|---|------|------|------|------|------|------|------|------------|-------------|

|   |      |      |      |      |      |      |      |            | 00000000    |

| - | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0       | <del></del> |

|   |      |      |      |      |      |      |      | SFR Addres | s: 0xA3     |

#### Bits 7-0: SPI0DAT: SPI0 Transmit and Receive Data.

The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer.

SILICON LABS

### SFR Definition 21.14. TMR3RLL: Timer 3 Reload Register Low Byte

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

Bits 7-0: TMR3RLL: Timer 3 Reload Register Low Byte.

TMR3RLL holds the low byte of the reload value for Timer 3 when operating in auto-reload mode, or the captured value of the TMR3L register when operating in capture mode.

#### SFR Definition 21.15. TMR3RLH: Timer 3 Reload Register High Byte

| R/W  | Reset Value          |

|------|------|------|------|------|------|------|------|----------------------|

|      |      |      |      |      |      |      |      | 00000000             |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0x93 |

Bits 7-0: TMR3RLH: Timer 3 Reload Register High Byte.

The TMR3RLH holds the high byte of the reload value for Timer 3 when operating in auto-reload mode, or the captured value of the TMR3H register when operating in capture mode.

#### SFR Definition 21.16. TMR3L: Timer 3 Low Byte

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0x94         |

Bits 7-0: TMR3L: Timer 3 Low Byte.

In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In 8-bit mode, TMR3L contains the 8-bit low byte timer value.

#### SFR Definition 21.17. TMR3H Timer 3 High Byte

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0x95         |

Bits 7-0: TMR3H: Timer 3 High Byte.

In 16-bit mode, the TMR3H register contains the high byte of the 16-bit Timer 3. In 8-bit mode, TMR3H contains the 8-bit high byte timer value.