# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                          |

| Number of I/O              | 40                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f348-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### List of Figures

| 1. System Overview                                                            |    |

|-------------------------------------------------------------------------------|----|

| Figure 1.1. C8051F340/1/4/5 Block Diagram                                     | 19 |

| Figure 1.2. C8051F342/3/6/7 Block Diagram                                     | 20 |

| Figure 1.3. C8051F348/C Block Diagram                                         |    |

| Figure 1.4. C8051F349/D Block Diagram                                         |    |

| Figure 1.5. C8051F34A/B Block Diagram                                         | 23 |

| 4. Pinout and Package Definitions                                             |    |

| Figure 4.1. TQFP-48 Pinout Diagram (Top View)                                 | 31 |

| Figure 4.2. TQFP-48 Package Diagram                                           |    |

| Figure 4.3. TQFP-48 Recommended PCB Land Pattern                              |    |

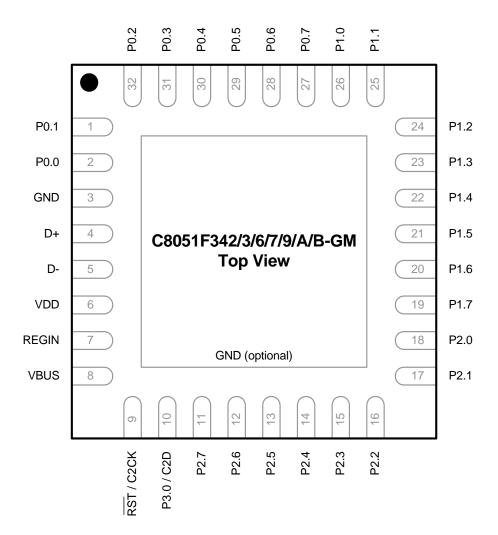

| Figure 4.4. LQFP-32 Pinout Diagram (Top View)                                 |    |

| Figure 4.5. LQFP-32 Package Diagram                                           |    |

| Figure 4.6. LQFP-32 Recommended PCB Land Pattern                              | 36 |

| Figure 4.7. QFN-32 Pinout Diagram (Top View)                                  |    |

| 5. 10-Bit ADC (ADC0, C8051F340/1/2/3/4/5/6/7/A/B Only)                        |    |

| Figure 5.1. ADC0 Functional Block Diagram                                     | 41 |

| Figure 5.2. Temperature Sensor Transfer Function                              | 43 |

| Figure 5.3. Temperature Sensor Error with 1-Point Calibration (VREF = 2.40 V) | 44 |

| Figure 5.4. 10-Bit ADC Track and Conversion Example Timing                    | 46 |

| Figure 5.5. ADC0 Equivalent Input Circuits                                    | 47 |

| Figure 5.6. ADC Window Compare Example: Right-Justified Single-Ended Data     | 54 |

| Figure 5.7. ADC Window Compare Example: Left-Justified Single-Ended Data      | 54 |

| Figure 5.8. ADC Window Compare Example: Right-Justified Differential Data     | 55 |

| Figure 5.9. ADC Window Compare Example: Left-Justified Differential Data      | 55 |

| 6. Voltage Reference (C8051F340/1/2/3/4/5/6/7/A/B Only)                       |    |

| Figure 6.1. Voltage Reference Functional Block Diagram                        | 57 |

| 7. Comparators                                                                |    |

| Figure 7.1. Comparator Functional Block Diagram                               | 60 |

| Figure 7.2. Comparator Hysteresis Plot                                        |    |

| 8. Voltage Regulator (REG0)                                                   |    |

| Figure 8.1. REG0 Configuration: USB Bus-Powered                               |    |

| Figure 8.2. REG0 Configuration: USB Self-Powered                              | 70 |

| Figure 8.3. REG0 Configuration: USB Self-Powered, Regulator Disabled          | 71 |

| Figure 8.4. REG0 Configuration: No USB Connection                             | 71 |

| 9. CIP-51 Microcontroller                                                     |    |

| Figure 9.1. CIP-51 Block Diagram                                              | 73 |

| Figure 9.2. On-Chip Memory Map for 64 kB Devices                              |    |

| Figure 9.3. On-Chip Memory Map for 32 kB Devices                              | 80 |

| 11. Reset Sources                                                             |    |

| Figure 11.1. Reset Sources 1                                                  |    |

| Figure 11.2. Power-On and VDD Monitor Reset Timing 1                          | 01 |

| Figure 19.1. UART1 Block Diagram 21                                         |             |

|-----------------------------------------------------------------------------|-------------|

| Figure 19.2. UART1 Timing Without Parity or Extra Bit                       |             |

| Figure 19.3. UART1 Timing With Parity 21                                    | 5           |

| Figure 19.4. UART1 Timing With Extra Bit 21                                 | 5           |

| Figure 19.5. Typical UART Interconnect Diagram 21                           | 6           |

| Figure 19.6. UART Multi-Processor Mode Interconnect Diagram                 | 8           |

| 20. Enhanced Serial Peripheral Interface (SPI0)                             |             |

| Figure 20.1. SPI Block Diagram 22                                           | 22          |

| Figure 20.2. Multiple-Master Mode Connection Diagram                        |             |

| Figure 20.3. 3-Wire Single Master and Slave Mode Connection Diagram         |             |

| Figure 20.4. 4-Wire Single Master Mode and Slave Mode Connection Diagram 22 |             |

| Figure 20.5. Master Mode Data/Clock Timing 22                               |             |

| Figure 20.6. Slave Mode Data/Clock Timing (CKPHA = 0)                       |             |

| Figure 20.7. Slave Mode Data/Clock Timing (CKPHA = 1)                       |             |

| Figure 20.8. SPI Master Timing (CKPHA = 0) 23                               |             |

| Figure 20.9. SPI Master Timing (CKPHA = 1)                                  |             |

| Figure 20.10. SPI Slave Timing (CKPHA = 0)                                  |             |

| Figure 20.11. SPI Slave Timing (CKPHA = 1)                                  |             |

| 21. Timers                                                                  |             |

| Figure 21.1. T0 Mode 0 Block Diagram 23                                     | 36          |

| Figure 21.2. T0 Mode 2 Block Diagram                                        |             |

| Figure 21.3. T0 Mode 3 Block Diagram                                        |             |

| Figure 21.4. Timer 2 16-Bit Mode Block Diagram                              |             |

| Figure 21.5. Timer 2 8-Bit Mode Block Diagram                               |             |

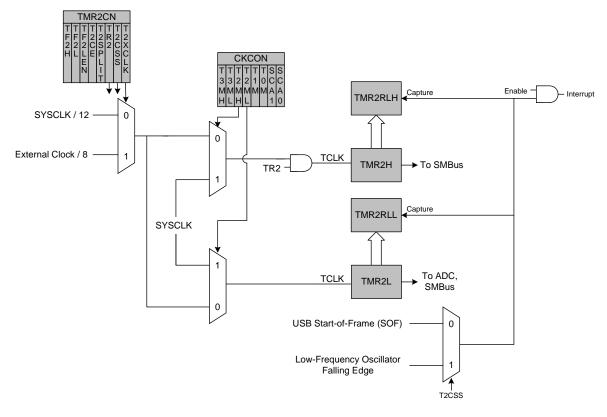

| Figure 21.6. Timer 2 Capture Mode (T2SPLIT = '0')                           |             |

| Figure 21.7. Timer 2 Capture Mode $(T2SPLIT = '1')$                         |             |

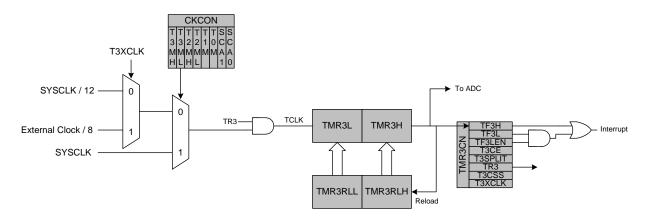

| Figure 21.8. Timer 3 16-Bit Mode Block Diagram                              |             |

| Figure 21.9. Timer 3 8-Bit Mode Block Diagram                               |             |

| Figure 21.10. Timer 3 Capture Mode (T3SPLIT = '0')                          |             |

| Figure 21.11. Timer 3 Capture Mode (T3SPLIT = '1')                          | 52          |

| 22. Programmable Counter Array (PCA0)                                       |             |

| Figure 22.1. PCA Block Diagram                                              | 55          |

| Figure 22.2. PCA Counter/Timer Block Diagram                                |             |

| Figure 22.3. PCA Interrupt Block Diagram                                    |             |

| Figure 22.4. PCA Capture Mode Diagram                                       |             |

| Figure 22.5. PCA Software Timer Mode Diagram                                |             |

| Figure 22.6. PCA High Speed Output Mode Diagram                             |             |

| Figure 22.7. PCA Frequency Output Mode                                      |             |

| Figure 22.8. PCA 8-Bit PWM Mode Diagram                                     |             |

| Figure 22.9. PCA 16-Bit PWM Mode                                            |             |

| Figure 22.10. PCA Module 4 with Watchdog Timer Enabled                      |             |

| 23. C2 Interface                                                            | <i>,</i> -т |

| Figure 23.1. Typical C2 Pin Sharing                                         | 73          |

|                                                                             | -           |

Figure 4.7. QFN-32 Pinout Diagram (Top View)

### **Table 9.3. Special Function Registers**

| Register | Address | Description                               | Page |

|----------|---------|-------------------------------------------|------|

| ACC      | 0xE0    | Accumulator                               | 87   |

| ADC0CF   | 0xBC    | ADC0 Configuration                        | 50   |

| ADC0CN   | 0xE8    | ADC0 Control                              | 51   |

| ADC0GTH  | 0xC4    | ADC0 Greater-Than Compare High            | 52   |

| ADC0GTL  | 0xC3    | ADC0 Greater-Than Compare Low             | 52   |

| ADC0H    | 0xBE    | ADC0 High                                 | 50   |

| ADC0L    | 0xBD    | ADC0 Low                                  | 50   |

| ADC0LTH  | 0xC6    | ADC0 Less-Than Compare Word High          | 53   |

| ADC0LTL  | 0xC5    | ADC0 Less-Than Compare Word Low           | 53   |

| AMX0N    | 0xBA    | AMUX0 Negative Channel Select             | 49   |

| AMX0P    | 0xBB    | AMUX0 Positive Channel Select             | 48   |

| В        | 0xF0    | B Register                                | 88   |

| CKCON    | 0x8E    | Clock Control                             | 241  |

| CLKMUL   | 0xB9    | Clock Multiplier                          | 138  |

| CLKSEL   | 0xA9    | Clock Select                              | 140  |

| CPT0CN   | 0x9B    | Comparator0 Control                       | 62   |

| CPT0MD   | 0x9D    | Comparator0 Mode Selection                | 64   |

| CPT0MX   | 0x9F    | Comparator0 MUX Selection                 | 63   |

| CPT1CN   | 0x9A    | Comparator1 Control                       | 65   |

| CPT1MD   | 0x9C    | Comparator1 Mode Selection                | 67   |

| CPT1MX   | 0x9E    | Comparator1 MUX Selection                 | 66   |

| DPH      | 0x83    | Data Pointer High                         | 86   |

| DPL      | 0x82    | Data Pointer Low                          | 86   |

| EIE1     | 0xE6    | Extended Interrupt Enable 1               | 93   |

| EIE2     | 0xE7    | Extended Interrupt Enable 2               | 95   |

| EIP1     | 0xF6    | Extended Interrupt Priority 1             | 94   |

| EIP2     | 0xF7    | Extended Interrupt Priority 2             | 95   |

| EMI0CN   | 0xAA    | External Memory Interface Control         | 117  |

| EMI0CF   | 0x85    | External Memory Interface Configuration   | 118  |

| EMIOTC   | 0x84    | External Memory Interface Timing          | 123  |

| FLKEY    | 0xB7    | Flash Lock and Key                        | 112  |

| FLSCL    | 0xB6    | Flash Scale                               | 113  |

| IE       | 0xA8    | Interrupt Enable                          | 91   |

| IP       | 0xB8    | Interrupt Priority                        | 92   |

| IT01CF   | 0xE4    | INT0/INT1 Configuration                   | 96   |

| OSCICL   | 0xB3    | Internal Oscillator Calibration           | 133  |

| OSCICN   | 0xB2    | Internal Oscillator Control               | 132  |

| OSCLCN   | 0x86    | Internal Low-Frequency Oscillator Control | 134  |

| OSCXCN   | 0xB1    | External Oscillator Control               | 137  |

| P0       | 0x80    | Port 0 Latch                              | 150  |

| POMDIN   | 0xF1    | Port 0 Input Mode Configuration           | 150  |

| POMDOUT  | 0xA4    | Port 0 Output Mode Configuration          | 151  |

| POSKIP   | 0xD4    | Port 0 Skip                               | 151  |

| P1       | 0x90    | Port 1 Latch                              | 152  |

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

### Table 9.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register | Address | Description                       | Page |

|----------|---------|-----------------------------------|------|

| P1MDIN   | 0xF2    | Port 1 Input Mode Configuration   | 152  |

| P1MDOUT  | 0xA5    | Port 1 Output Mode Configuration  | 152  |

| P1SKIP   | 0xD5    | Port 1 Skip                       | 153  |

| P2       | 0xA0    | Port 2 Latch                      | 153  |

| P2MDIN   | 0xF3    | Port 2 Input Mode Configuration   | 153  |

| P2MDOUT  | 0xA6    | Port 2 Output Mode Configuration  | 154  |

| P2SKIP   | 0xD6    | Port 2 Skip                       | 154  |

| P3       | 0xB0    | Port 3 Latch                      | 155  |

| P3MDIN   | 0xF4    | Port 3 Input Mode Configuration   | 155  |

| P3MDOUT  | 0xA7    | Port 3 Output Mode Configuration  | 155  |

| P3SKIP   | 0xDF    | Port 3Skip                        | 156  |

| P4       | 0xC7    | Port 4 Latch                      | 156  |

| P4MDIN   | 0xF5    | Port 4 Input Mode Configuration   | 157  |

| P4MDOUT  | 0xAE    | Port 4 Output Mode Configuration  | 157  |

| PCA0CN   | 0xD8    | PCA Control                       | 266  |

| PCA0CPH0 | 0xFC    | PCA Capture 0 High                | 270  |

| PCA0CPH1 | 0xEA    | PCA Capture 1 High                | 270  |

| PCA0CPH2 | 0xEC    | PCA Capture 2 High                | 270  |

| PCA0CPH3 | 0xEE    | PCA Capture 3High                 | 270  |

| PCA0CPH4 | 0xFE    | PCA Capture 4 High                | 270  |

| PCA0CPL0 | 0xFB    | PCA Capture 0 Low                 | 269  |

| PCA0CPL1 | 0xE9    | PCA Capture 1 Low                 | 269  |

| PCA0CPL2 | 0xEB    | PCA Capture 2 Low                 | 269  |

| PCA0CPL3 | 0xED    | PCA Capture 3 Low                 | 269  |

| PCA0CPL4 | 0xFD    | PCA Capture 4 Low                 | 269  |

| PCA0CPM0 | 0xDA    | PCA Module 0 Mode Register        | 268  |

| PCA0CPM1 | 0xDB    | PCA Module 1 Mode Register        | 268  |

| PCA0CPM2 | 0xDC    | PCA Module 2 Mode Register        | 268  |

| PCA0CPM3 | 0xDD    | PCA Module 3 Mode Register        | 268  |

| PCA0CPM4 | 0xDE    | PCA Module 4 Mode Register        | 268  |

| PCA0H    | 0xFA    | PCA Counter High                  | 269  |

| PCA0L    | 0xF9    | PCA Counter Low                   | 269  |

| PCA0MD   | 0xD9    | PCA Mode                          | 267  |

| PCON     | 0x87    | Power Control                     | 98   |

| PFE0CN   | 0xAF    | Prefetch Engine Control           | 99   |

| PSCTL    | 0x8F    | Program Store R/W Control         | 112  |

| PSW      | 0xD0    | Program Status Word               | 87   |

| REF0CN   | 0xD1    | Voltage Reference Control         | 58   |

| REG0CN   | 0xC9    | Voltage Regulator Control         | 72   |

| RSTSRC   | 0xEF    | Reset Source Configuration/Status | 105  |

| SBCON1   | 0xAC    | UART1 Baud Rate Generator Control | 220  |

| SBRLH1   | 0xB5    | UART1 Baud Rate Generator High    | 221  |

| SBRLL1   | 0xB4    | UART1 Baud Rate Generator Low     | 221  |

| SBUF1    | 0xD3    | UART1 Data Buffer                 | 220  |

| SCON1    | 0xD2    | UART1 Control                     | 218  |

| SFR Definition 9.11. EIE2: Extended Interrupt Enable 2 |

|--------------------------------------------------------|

|--------------------------------------------------------|

| R/W                        | R/W                                                                                                                                                                                                                                                                                                                                                                                        | R/W  | R/W  | R/W  | R/W  | R/W  | R/W   | Reset Value  |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|-------|--------------|--|

| -                          | -                                                                                                                                                                                                                                                                                                                                                                                          | -    | -    | -    | -    | ES1  | EVBUS | 00000000     |  |

| Bit7                       | Bit6                                                                                                                                                                                                                                                                                                                                                                                       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0  | SFR Address: |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                            |      |      |      |      |      |       | 0xE7         |  |

| Bits7–2:<br>Bit1:<br>Bit0: | UNUSED. Read = 000000b. Write = don't care.<br>ES1: Enable UART1 Interrupt.<br>This bit sets the masking of the UART1 interrupt.<br>0: Disable UART1 interrupt.<br>1: Enable UART1 interrupt.<br>EVBUS: Enable VBUS Level Interrupt.<br>This bit sets the masking of the VBUS interrupt.<br>0: Disable all VBUS interrupts.<br>1: Enable interrupt requests generated by VBUS level sense. |      |      |      |      |      |       |              |  |

### SFR Definition 9.12. EIP2: Extended Interrupt Priority 2

| R/W                        | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W   | Reset Value  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|-------|--------------|

| -                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -    | -    | -    | -    | PS1  | PVBUS | 0000000      |

| Bit7                       | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0  | SFR Address: |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |      |      |      |      |       | 0xF7         |

| Bits7–2:<br>Bit1:<br>Bit0: | UNUSED. Read = 000000b. Write = don't care.<br>PS1: UART1 Interrupt Priority Control.<br>This bit sets the priority of the UART1 interrupt.<br>0: UART1 interrupt set to low priority level.<br>1: UART1 interrupts set to high priority level.<br>PVBUS: VBUS Level Interrupt Priority Control.<br>This bit sets the priority of the VBUS interrupt.<br>0: VBUS interrupt set to low priority level.<br>1: VBUS interrupt set to high priority level. |      |      |      |      |      |       |              |

### **Table 14.1. Oscillator Electrical Characteristics**

#### $V_{DD}$ = 2.7 to 3.6 V; -40 to +85 °C unless otherwise specified

| Parameter                                                              | Conditions                                      | Min   | Тур   | Max   | Units  |  |  |

|------------------------------------------------------------------------|-------------------------------------------------|-------|-------|-------|--------|--|--|

| Internal High-Frequency Oscillator (Using Factory-Calibrated Settings) |                                                 |       |       |       |        |  |  |

| Oscillator Frequency                                                   | IFCN = 11b                                      | 11.82 | 12.00 | 12.18 | MHz    |  |  |

| Oscillator Supply Current<br>(from V <sub>DD</sub> )                   | 24 °C, V <sub>DD</sub> = 3.0 V,<br>OSCICN.7 = 1 | _     | 685   | —     | μA     |  |  |

| Internal Low-Frequency Oscillator (Using Factory-Calibrated Settings)  |                                                 |       |       |       |        |  |  |

| Oscillator Frequency                                                   | OSCLD = 11b                                     | 72    | 80    | 99    | kHz    |  |  |

| Oscillator Supply Current<br>(from V <sub>DD</sub> )                   | 24 °C, V <sub>DD</sub> = 3.0 V,<br>OSCLCN.7 = 1 | _     | 7.0   | _     | μA     |  |  |

| External USB Clock Require                                             | ements                                          |       |       |       |        |  |  |

| USD Clock Fraguency'                                                   | Full Speed Mode                                 | 47.88 | 48    | 48.12 | N 41 I |  |  |

| USB Clock Frequency*                                                   | Low Speed Mode                                  | 5.91  | 6     | 6.09  | MHz    |  |  |

\*Note: Applies only to external oscillator sources.

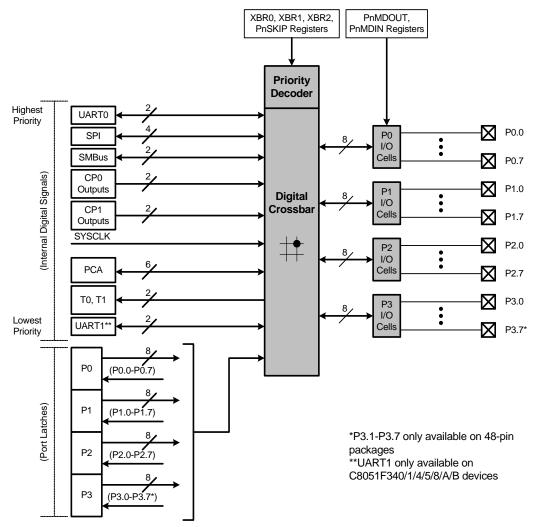

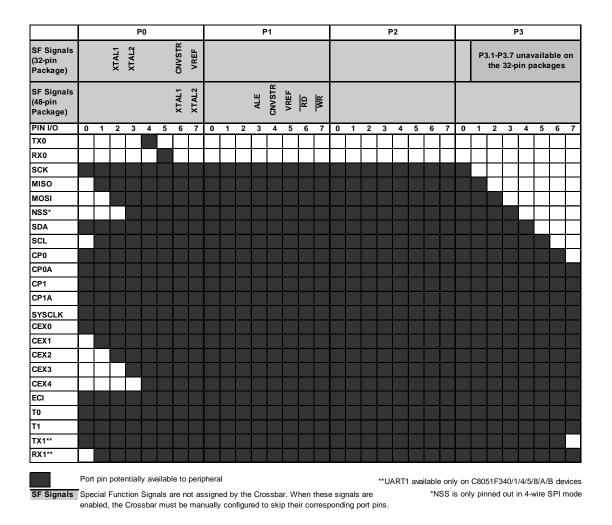

### 15. Port Input/Output

Digital and analog resources are available through 40 I/O pins (48-pin packages) or 25 I/O pins (32-pin packages). Port pins are organized as shown in Figure 15.1. Each of the Port pins can be defined as general-purpose I/O (GPIO) or analog input; Port pins P0.0-P3.7 can be assigned to one of the internal digital resources as shown in Figure 15.3. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 15.3 and Figure 15.4). The registers XBR0, XBR1, and XBR2 defined in SFR Definition 15.1, SFR Definition 15.2, and SFR Definition 15.3, are used to select internal digital functions.

All Port I/Os are 5 V tolerant (refer to Figure 15.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0, 1, 2, 3, 4). Complete Electrical Specifications for Port I/O are given in Table 15.1 on page 158.

#### **15.1.** Priority Crossbar Decoder

The Priority Crossbar Decoder (Figure 15.3) assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that resource (excluding UART0, which is always at pins 4 and 5). If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that are to be used for analog input, dedicated functions, or GPIO.

**Important Note on Crossbar Configuration:** If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding PnSKIP bit should be set. This applies to the VREF signal, external oscillator pins (XTAL1, XTAL2), the ADC's external conversion start signal (CNVSTR), EMIF control signals, and any selected ADC or Comparator inputs. The PnSKIP registers may also be used to skip pins to be used as GPIO. The Crossbar skips selected pins as if they were already assigned, and moves to the next unassigned pin. Figure 15.3 shows all the possible pins available to each peripheral. Figure 15.4 shows the Crossbar Decoder priority with no Port pins skipped. Figure 15.5 shows a Crossbar example with pins P0.2, P0.3, and P1.0 skipped.

| R/W   | R/W                                                               | R/W                               | R/W         | R/W         | R/W   | R/W   | R/W   | Reset Value |  |

|-------|-------------------------------------------------------------------|-----------------------------------|-------------|-------------|-------|-------|-------|-------------|--|

| CP1AE |                                                                   | CPOAE                             | CP0E        | SYSCKE      | SMB0E | SPIOE | URTOE | 00000000    |  |

| Bit7  | Bit6                                                              |                                   |             |             |       |       |       |             |  |

| Biti  | Bito                                                              | Bito                              | BRT         | Bito        | DILL  | Bitt  | Dito  | 0xE1        |  |

|       |                                                                   |                                   |             |             |       |       |       |             |  |

| Bit7: | CP1AE: Cor                                                        | nparator1 A                       | svnchrono   | us Output E | nable |       |       |             |  |

|       | 0: Asynchro                                                       | •                                 |             | •           |       |       |       |             |  |

|       | 1: Asynchro                                                       |                                   |             |             |       |       |       |             |  |

| Bit6: | CP1E: Com                                                         | parator1 Ou                       | tput Enable | Э           |       |       |       |             |  |

|       | 0: CP1 unav                                                       | ailable at P                      | ort pin.    |             |       |       |       |             |  |

|       | 1: CP1 route                                                      | ed to Port pi                     | n.          |             |       |       |       |             |  |

| Bit5: | CP0AE: Cor                                                        | nparator0 A                       | synchrono   | us Output E | nable |       |       |             |  |

|       | 0: Asynchro                                                       |                                   |             |             |       |       |       |             |  |

|       | 1: Asynchro                                                       |                                   |             |             |       |       |       |             |  |

| Bit4: | CP0E: Com                                                         |                                   | •           | Э           |       |       |       |             |  |

|       | 0: CP0 unav                                                       |                                   | •           |             |       |       |       |             |  |

|       | 1: CP0 route                                                      |                                   |             |             |       |       |       |             |  |

| Bit3: | SYSCKE: /S                                                        |                                   | •           |             |       |       |       |             |  |

|       | 0: /SYSCLK                                                        |                                   |             |             |       |       |       |             |  |

| Dito  | 1: /SYSCLK                                                        |                                   |             | oin.        |       |       |       |             |  |

| Bit2: | SMB0E: SM                                                         |                                   |             |             |       |       |       |             |  |

|       | 0: SMBus I/                                                       |                                   |             | ins.        |       |       |       |             |  |

| Bit1: |                                                                   | 1: SMBus I/O routed to Port pins. |             |             |       |       |       |             |  |

| DILI. | SPI0E: SPI I/O Enable                                             |                                   |             |             |       |       |       |             |  |

|       | 0: SPI I/O unavailable at Port pins.                              |                                   |             |             |       |       |       |             |  |

| Bit0: | 1: SPI I/O routed to Port pins.<br>URT0E: UART0 I/O Output Enable |                                   |             |             |       |       |       |             |  |

| Dito. | 0: UARTO I/O unavailable at Port pins.                            |                                   |             |             |       |       |       |             |  |

|       | 1: UART0 TX0, RX0 routed to Port pins P0.4 and P0.5.              |                                   |             |             |       |       |       |             |  |

|       |                                                                   | ,                                 |             | F           |       |       |       |             |  |

|       |                                                                   |                                   |             |             |       |       |       |             |  |

### SFR Definition 15.1. XBR0: Port I/O Crossbar Register 0

### USB Register Definition 16.13. CMINT: USB0 Common Interrupt

| R                                            | R                                                                                                                                                                                                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R                                                                                                                                                                                                                                                         | R                                                                                                                                                              | R                                                                         | R                                                                        | R                                             | Reset Value                               |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------|

| -                                            | -                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                         | SOF                                                                                                                                                            | RSTINT                                                                    | RSUINT                                                                   | SUSINT                                        | 00000000                                  |

| Bit7                                         | Bit6                                                                                                                                                                                                                                                                                                                                                                                             | Bit5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit4                                                                                                                                                                                                                                                      | Bit3                                                                                                                                                           | Bit2                                                                      | Bit1                                                                     | Bit0                                          | USB Address:                              |

| Diti                                         | Dito                                                                                                                                                                                                                                                                                                                                                                                             | Dito                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DILT                                                                                                                                                                                                                                                      | DIG                                                                                                                                                            | DILZ                                                                      | Ditt                                                                     | Dito                                          |                                           |

| Bits7–4:<br>Bit3:<br>Bit2:<br>Bit1:<br>Bit1: | Unused. Rea<br>SOF: Start of<br>Set by hardw<br>ware: an inter<br>the actual SO<br>This bit is cle<br>0: SOF intern<br>1: SOF intern<br>RSTINT: Res<br>Set by hardw<br>This bit is cle<br>0: Reset inte<br>1: Reset inte<br>RSUINT: Res<br>Set by hardw<br>mode.<br>This bit is cle<br>0: Resume ir<br>SUSINT: Sus<br>When Susper<br>ware when S<br>reads the CM<br>0: Suspend i<br>1: Suspend i | f Frame Int<br>vare when a<br>prrupt will be<br>DF signal is<br>eared when<br>rupt inactive.<br>set Interrup<br>vare when I<br>eared when<br>rrupt inactive<br>sume Interrupt active<br>sume Interrupt active<br>sume Interrupt ina<br>herrupt inactive<br>sume Interrupt ina<br>herrupt act<br>spend Inter<br>end detections<br>support active<br>support a | errupt<br>a SOF token<br>e generated<br>s missed or<br>software re-<br>e.<br>t-pending F<br>Reset signa<br>software re-<br>ve.<br>e.<br>"upt-pending<br>software re-<br>ctive.<br>ive.<br>rupt-pending<br>n is enable<br>gnaling is de-<br>er.<br>active. | n is receive<br>when hard<br>corrupted.<br>eads the CM<br>lag<br>ling is dete<br>eads the CM<br>g Flag<br>naling is de<br>eads the CM<br>g Flag<br>d (bit SUSE | ware expec<br>/INT registe<br>cted on the<br>/INT registe<br>/INT registe | ets to receive<br>er.<br>bus.<br>er.<br>he bus while<br>er.<br>er POWER) | e a SOF ev<br>e USB0 is in<br>, this bit is s | ent, even if<br>n suspend<br>set by hard- |

| SFR Definition 17.2 | SMB0CN: SMBus Control |

|---------------------|-----------------------|

|---------------------|-----------------------|

| R     | R                                                                                                                              | R/W         | R/W          | R            | R                | R/W         | R/W          | Reset Value        |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|--------------|------------------|-------------|--------------|--------------------|--|--|--|--|

| MASTE | R TXMODE                                                                                                                       | STA         | STO          | ACKRQ        | ARBLOST          | ACK         | SI           | 00000000           |  |  |  |  |

| Bit7  | Bit6                                                                                                                           | Bit5        | Bit4         | Bit3         | Bit2             | Bit1        | Bit0         | Bit<br>Addressable |  |  |  |  |

|       |                                                                                                                                |             |              |              |                  |             | SFR Addres   |                    |  |  |  |  |

|       |                                                                                                                                |             |              |              |                  |             |              |                    |  |  |  |  |

| Bit7: | MASTER: SM                                                                                                                     |             |              |              |                  |             |              |                    |  |  |  |  |

|       | This read-only bit indicates when the SMBus is operating as a master.                                                          |             |              |              |                  |             |              |                    |  |  |  |  |

|       | 0: SMBus operating in Slave Mode.<br>1: SMBus operating in Master Mode.                                                        |             |              |              |                  |             |              |                    |  |  |  |  |

| Bit6: |                                                                                                                                |             |              |              |                  |             |              |                    |  |  |  |  |

| Dito. | TXMODE: SMBus Transmit Mode Indicator.<br>This read-only bit indicates when the SMBus is operating as a transmitter.           |             |              |              |                  |             |              |                    |  |  |  |  |

|       | 0: SMBus in F                                                                                                                  |             |              |              | o oporating a    | o a tranon  |              |                    |  |  |  |  |

|       | 1: SMBus in T                                                                                                                  |             |              |              |                  |             |              |                    |  |  |  |  |

| Bit5: | STA: SMBus                                                                                                                     | Start Flag. |              |              |                  |             |              |                    |  |  |  |  |

|       | Write:                                                                                                                         |             |              |              |                  |             |              |                    |  |  |  |  |

|       | 0: No Start ge                                                                                                                 |             |              |              |                  |             |              |                    |  |  |  |  |

|       | 1: When operating as a master, a START condition is transmitted if the bus is free (If the bus                                 |             |              |              |                  |             |              |                    |  |  |  |  |

|       | is not free, the START is transmitted after a STOP is received or a timeout is detected). If                                   |             |              |              |                  |             |              |                    |  |  |  |  |

|       | STA is set by software as an active Master, a repeated START will be generated after the next ACK cycle.                       |             |              |              |                  |             |              |                    |  |  |  |  |

|       | Read:                                                                                                                          |             |              |              |                  |             |              |                    |  |  |  |  |

|       | 0: No Start or repeated Start detected.                                                                                        |             |              |              |                  |             |              |                    |  |  |  |  |

|       | 1: Start or repeated Start detected.                                                                                           |             |              |              |                  |             |              |                    |  |  |  |  |

| Bit4: | STO: SMBus                                                                                                                     | Stop Flag   |              |              |                  |             |              |                    |  |  |  |  |

|       | Write:                                                                                                                         |             |              | _            |                  |             |              |                    |  |  |  |  |

|       | 0: No STOP condition is transmitted.<br>1: Setting STO to logic 1 causes a STOP condition to be transmitted after the next ACK |             |              |              |                  |             |              |                    |  |  |  |  |

|       | -                                                                                                                              | -           |              |              |                  |             |              |                    |  |  |  |  |

|       | cycle. When t                                                                                                                  |             |              | -            |                  |             | -            |                    |  |  |  |  |

|       | and STO are set, a STOP condition is transmitted followed by a START condition.<br>Read:                                       |             |              |              |                  |             |              |                    |  |  |  |  |

|       | 0: No Stop co                                                                                                                  | ndition de  | tected.      |              |                  |             |              |                    |  |  |  |  |

|       | 1: Stop condit                                                                                                                 |             |              | ve Mode) c   | or pending (if i | in Master   | Mode).       |                    |  |  |  |  |

| Bit3: | ACKRQ: SME                                                                                                                     | Bus Ackno   | wledge Re    | quest        |                  |             |              |                    |  |  |  |  |

|       | This read-only bit is set to logic 1 when the SMBus has received a byte and needs the ACK                                      |             |              |              |                  |             |              |                    |  |  |  |  |

| DVA   | bit to be writte                                                                                                               |             |              |              | e value.         |             |              |                    |  |  |  |  |

| Bit2: | ARBLOST: SI                                                                                                                    |             |              |              |                  | hitrotion . | uhila anara  | 1                  |  |  |  |  |

|       | This read-only transmitter. A                                                                                                  | •           | •            |              |                  |             | •            | iting as a         |  |  |  |  |

| Bit1: | ACK: SMBus                                                                                                                     |             |              |              |                  |             | uon.         |                    |  |  |  |  |

| Ditt. | This bit define                                                                                                                |             | 0 0          | level and r  | ecords incom     | ina ACK le  | evels. It sh | ould be writ       |  |  |  |  |

|       | ten each time                                                                                                                  |             |              |              |                  |             |              |                    |  |  |  |  |

|       |                                                                                                                                |             | •            |              | ,                |             |              |                    |  |  |  |  |

|       | 0: A "not acknowledge" has been received (if in Transmitter Mode) OR will be transmitted (if in Receiver Mode).                |             |              |              |                  |             |              |                    |  |  |  |  |

|       | 1: An "acknowledge" has been received (if in Transmitter Mode) OR will be transmitted (if in                                   |             |              |              |                  |             |              |                    |  |  |  |  |

| Bito  | Receiver Mode).                                                                                                                |             |              |              |                  |             |              |                    |  |  |  |  |

| Bit0: | SI: SMBus Int                                                                                                                  | •           | -            |              |                  |             |              | aloored by         |  |  |  |  |

|       | This bit is set                                                                                                                | by nardwa   | are under th | ie condition | is listed in Tal | ole 17.3. S | o must de    | cleared by         |  |  |  |  |

|                   | Values Read      |       |         |     |                                                                                               |                                                                        | Values<br>Written |     |     |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|-------------------|------------------|-------|---------|-----|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------|-----|-----|---|---|---|---|---|---|---|--------------------------------|---------------------------------------------|---------------------------------------------------------|--------------------------------------|---|---|---|

| Mode              | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                                                                           | Typical Response Options                                               |                   | STo | ACK |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

| er .              |                  | 0     | 0       | 0   | A slave byte was transmitted;<br>NACK received.                                               | No action required (expect-<br>ing STOP condition).                    | 0                 | 0   | х   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

| Slave Transmitter | 0100             | 0     | 0       | 1   | A slave byte was transmitted;<br>ACK received.                                                | Load SMB0DAT with next data byte to transmit.                          | 0                 | 0   | х   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   |                  | 0     | 1       | х   | A Slave byte was transmitted;<br>error detected.                                              | No action required (expect-<br>ing Master to end transfer).            | 0                 | 0   | х   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

| Slav              | 0101             | 0     | x       | x   | An illegal STOP or bus error was<br>detected while a Slave Transmis-<br>sion was in progress. |                                                                        |                   |     | x   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   | 0010             | 1     | 0       | x   | A slave address was received;                                                                 | Acknowledge received address.                                          | 0                 | 0   | 1   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   |                  |       | U       | ^   |                                                                                               | Do not acknowledge received address.                                   | 0                 | 0   | 0   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   |                  |       |         |     |                                                                                               | Acknowledge received address.                                          |                   | 0   | 1   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   |                  | 1     | 1       | 1   | 1                                                                                             | 1                                                                      | 1                 | 1   | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1                              | x                                           | Lost arbitration as master; slave address received; ACK | Do not acknowledge received address. | 0 | 0 | 0 |

|                   |                  |       |         |     |                                                                                               | Reschedule failed transfer;<br>do not acknowledge received<br>address. | 1                 | 0   | 0   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

| iver              | 0010             | 0     | 1       | х   | Lost arbitration while attempting a                                                           | Abort failed transfer.                                                 | 0                 | 0   | Х   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

| Slave Receive     |                  |       |         |     | repeated START.                                                                               | Reschedule failed transfer.                                            | 1                 | 0   | Х   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   | 0001             | 1     | 1       | Х   | Lost arbitration while attempting a STOP.                                                     | No action required (transfer complete/aborted).                        | 0                 | 0   | 0   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   |                  | 0     | 0       | х   | A STOP was detected while<br>addressed as a Slave Transmitter<br>or Slave Receiver.           | Clear STO.                                                             | 0                 | 0   | x   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   |                  | 0     | ) 1     | х   | Lost arbitration due to a detected                                                            | Abort transfer.                                                        |                   | 0   | Х   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   |                  |       |         | ^   | STOP.                                                                                         | Reschedule failed transfer.                                            |                   | 0   | Х   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   | 0000             | 1     | 1       | 1   | 1                                                                                             | 1                                                                      | 1                 | 1   | 1   | 1 | 1 | 1 | 1 | 1 | 0 | x | A slave byte was received; ACK | Acknowledge received byte;<br>Read SMB0DAT. | 0                                                       | 0                                    | 1 |   |   |

|                   |                  |       |         |     | requested.                                                                                    | Do not acknowledge received byte.                                      |                   | 0   | 0   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   |                  | 1     | 1       | x   | Lost arbitration while transmitting                                                           | Abort failed transfer.                                                 | 0                 | 0   | 0   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

|                   |                  |       |         |     | a data byte as master.                                                                        | Reschedule failed transfer.                                            | 1                 | 0   | 0   |   |   |   |   |   |   |   |                                |                                             |                                                         |                                      |   |   |   |

Table 17.4. SMBus Status Decoding (Continued)

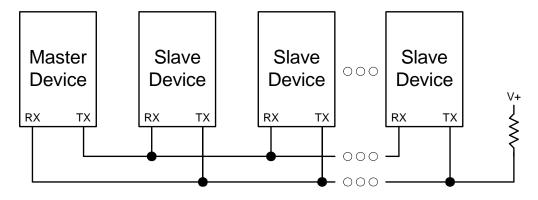

Figure 18.6. UART Multi-Processor Mode Interconnect Diagram

### **19.3.** Configuration and Operation

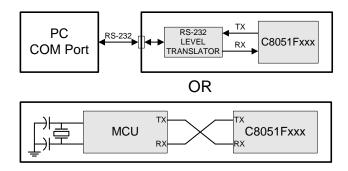

UART1 provides standard asynchronous, full duplex communication. It can operate in a point-to-point serial communications application, or as a node on a multi-processor serial interface. To operate in a point-to-point application, where there are only two devices on the serial bus, the MCE1 bit in SMOD1 should be cleared to '0'. For operation as part of a multi-processor communications bus, the MCE1 and XBE1 bits should both be set to '1'. In both types of applications, data is transmitted from the microcontroller on the TX1 pin, and received on the RX1 pin. The TX1 and RX1 pins are configured using the crossbar and the Port I/O registers, as detailed in **Section "15. Port Input/Output" on page 142**.

In typical UART communications, The transmit (TX) output of one device is connected to the receive (RX) input of the other device, either directly or through a bus transceiver, as shown in Figure 19.5.

Figure 19.5. Typical UART Interconnect Diagram

### 19.3.1. Data Transmission

Data transmission is double-buffered, and begins when software writes a data byte to the SBUF1 register. Writing to SBUF1 places data in the Transmit Holding Register, and the Transmit Holding Register Empty flag (THRE1) will be cleared to '0'. If the UARTs shift register is empty (i.e., no transmission is in progress) the data will be placed in the shift register, and the THRE1 bit will be set to '1'. If a transmission is in progress, the data will remain in the Transmit Holding Register until the current transmission is complete. The TI1 Transmit Interrupt Flag (SCON1.1) will be set at the end of any transmission (the beginning of the stop-bit time). If enabled, an interrupt will occur when TI1 is set.