Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                          |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | · .                                                            |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | ·                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f349-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Tables

| 1. | System Overview                                                        |     |

|----|------------------------------------------------------------------------|-----|

|    | Table 1.1. Product Selection Guide                                     | 18  |

| 2. | Absolute Maximum Ratings                                               |     |

|    | Table 2.1. Absolute Maximum Ratings*                                   | 24  |

| 3. | Global DC Electrical Characteristics                                   |     |

|    | Table 3.1. Global DC Electrical Characteristics                        | 25  |

|    | Table 3.2. Index to Electrical Characteristics Tables                  | 27  |

| 4. | Pinout and Package Definitions                                         |     |

|    | Table 4.1. Pin Definitions for the C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D | 28  |

|    | Table 4.2. TQFP-48 Package Dimensions                                  | 32  |

|    | Table 4.3. TQFP-48 PCB Land Pattern Dimensions                         | 33  |

|    | Table 4.4. LQFP-32 Package Dimensions                                  | 35  |

|    | Table 4.5. LQFP-32 PCB Land Pattern Dimensions                         |     |

| 5. | 10-Bit ADC (ADC0, C8051F340/1/2/3/4/5/6/7/A/B Only)                    |     |

|    | Table 5.1. ADC0 Electrical Characteristics                             | 56  |

| 6. | Voltage Reference (C8051F340/1/2/3/4/5/6/7/A/B Only)                   |     |

|    | Table 6.1. Voltage Reference Electrical Characteristics                | 58  |

| 7. | Comparators                                                            |     |

|    | Table 7.1. Comparator Electrical Characteristics                       | 68  |

| 8. | Voltage Regulator (REG0)                                               |     |

|    | Table 8.1. Voltage Regulator Electrical Specifications                 | 69  |

| 9. | CIP-51 Microcontroller                                                 |     |

|    | Table 9.1. CIP-51 Instruction Set Summary                              | 75  |

|    | Table 9.2. Special Function Register (SFR) Memory Map                  | 82  |

|    | Table 9.3. Special Function Registers                                  | 83  |

|    | Table 9.4. Interrupt Summary                                           | 90  |

| 11 | . Reset Sources                                                        |     |

|    | Table 11.1. Reset Electrical Characteristics         1                 | 106 |

| 12 | 2. Flash Memory                                                        |     |

|    | Table 12.1. Flash Electrical Characteristics                           | 109 |

| 13 | B. External Data Memory Interface and On-Chip XRAM                     |     |

|    | Table 13.1. AC Parameters for External Memory Interface         1      | 130 |

| 14 | I. Oscillators                                                         |     |

|    | Table 14.1. Oscillator Electrical Characteristics         1            | 141 |

| 15 | 5. Port Input/Output                                                   |     |

|    | Table 15.1. Port I/O DC Electrical Characteristics    1                | 158 |

| 16 | 6. Universal Serial Bus Controller (USB0)                              |     |

|    | Table 16.1. Endpoint Addressing Scheme         1                       |     |

|    | Table 16.2. USB0 Controller Registers         1                        |     |

|    | Table 16.3. FIFO Configurations   1                                    |     |

|    | Table 16.4. USB Transceiver Electrical Characteristics         1       | 187 |

| 17 | 7. SMBus                                                               |     |

|    | Table 17.1. SMBus Clock Source Selection         1                     | 192 |

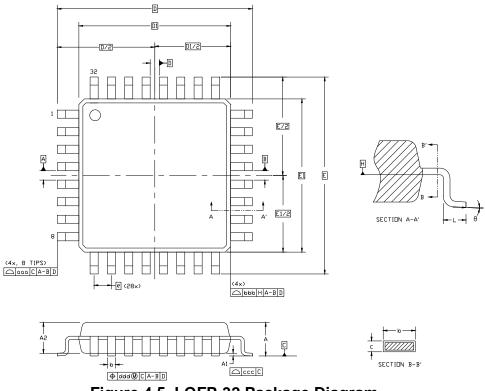

Figure 4.5. LQFP-32 Package Diagram

| Table 4.4. LQ | LL-27 LACK | age Dimensio | ons  |  |  |  |  |  |  |

|---------------|------------|--------------|------|--|--|--|--|--|--|

| Dimension     | Min        | Nom          | Max  |  |  |  |  |  |  |

| A             | —          | —            | 1.60 |  |  |  |  |  |  |

| A1            | 0.05       | —            | 0.15 |  |  |  |  |  |  |

| A2            | 1.35       | 1.40         | 1.45 |  |  |  |  |  |  |

| b             | 0.30       | 0.37         | 0.45 |  |  |  |  |  |  |

| С             | 0.09       | —            | 0.20 |  |  |  |  |  |  |

| D             |            | 9.00 BSC     |      |  |  |  |  |  |  |

| D1            |            | 7.00 BSC     |      |  |  |  |  |  |  |

| е             |            | 0.80 BSC     |      |  |  |  |  |  |  |

| E             |            | 9.00 BSC     |      |  |  |  |  |  |  |

| E1            |            | 7.00 BSC     |      |  |  |  |  |  |  |

| L             | 0.45       | 0.60         | 0.75 |  |  |  |  |  |  |

| aaa           |            | 0.20         |      |  |  |  |  |  |  |

| bbb           |            | 0.20         |      |  |  |  |  |  |  |

| CCC           |            | 0.10         |      |  |  |  |  |  |  |

| ddd           |            | 0.20         |      |  |  |  |  |  |  |

| θ             | 0°         | 3.5°         | 7°   |  |  |  |  |  |  |

### Table 4.4. LQFP-32 Package Dimensions

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS-026, variation BBA.

- **4.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

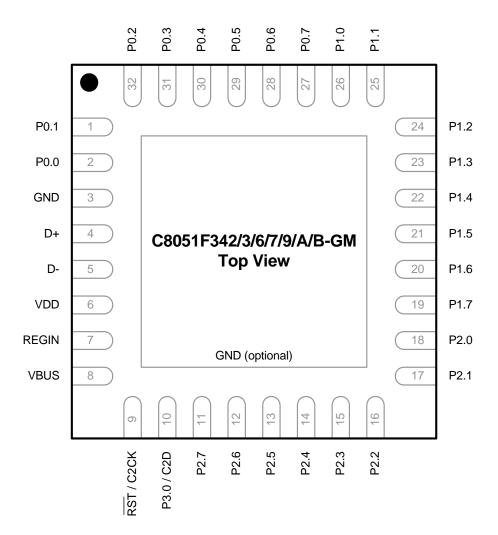

Figure 4.7. QFN-32 Pinout Diagram (Top View)

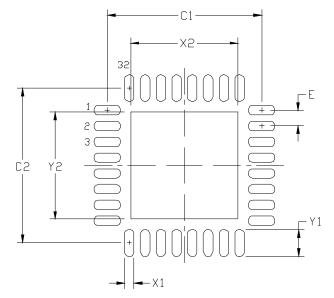

Figure 4.9. QFN-32 Recommended PCB Land Pattern

| Dimension | Min  | Max  |  |  |  |  |  |

|-----------|------|------|--|--|--|--|--|

| C1        | 4.80 | 4.90 |  |  |  |  |  |

| C2        | 4.80 | 4.90 |  |  |  |  |  |

| E         | 0.50 | BSC  |  |  |  |  |  |

| X1        | 0.20 | 0.30 |  |  |  |  |  |

| Dimension | Min  | Max  |

|-----------|------|------|

| X2        | 3.20 | 3.40 |

| Y1        | 0.75 | 0.85 |

| Y2        | 3.20 | 3.40 |

#### Notes:

#### General:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design:

All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60µm minimum, all the way around the pad.

#### Stencil Design:

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- **7.** A 3x3 array of 1.0 mm openings on a 1.2mm pitch should be used for the center pad to assure the proper paste volume.

#### Card Assembly:

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 9.13). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see **Section "15.1. Priority Crossbar Decoder" on page 144** for complete details on configuring the Crossbar). In the typical configuration, the external interrupt pin should be skipped in the crossbar and configured as open-drain with the pin latch set to '1'.

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

### 9.3.3. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP or EIP2) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 9.4.

### 9.3.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 6 system clock cycles: 1 clock cycle to detect the interrupt and 5 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 20 system clock cycles: 1 clock cycle to detect the interrupt, 6 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 5 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

Note that the CPU is stalled during Flash write/erase operations and USB FIFO MOVX accesses (see **Section "13.2. Accessing USB FIFO Space" on page 115**). Interrupt service latency will be increased for interrupts occurring while the CPU is stalled. The latency for these situations will be determined by the standard interrupt service procedure (as described above) and the amount of time the CPU is stalled.

| R/W   | R/W                           | R/W          | R/W             | R/W            | R/W           | R/W      | R/W          | Reset Value |

|-------|-------------------------------|--------------|-----------------|----------------|---------------|----------|--------------|-------------|

| -     | PSPI0                         | PT2          | PS0             | PT1            | PX1           | PT0      | PX0          | 1000000     |

| Bit7  | Bit6                          | Bit5         | Bit4            | Bit3           | Bit2          | Bit1     | Bit0         | SFR Address |

|       |                               |              |                 |                |               | (bi      | t addressabl | e) 0xB8     |

| Bit7: | UNUSED. Re                    | ead = 1, W   | /rite = don't ( | care.          |               |          |              |             |

| Bit6: | PSPI0: Seria                  | •            |                 | · /            | rupt Priority | Control. |              |             |

|       | This bit sets                 |              |                 |                |               |          |              |             |

|       | 0: SPI0 interi                | •            |                 |                |               |          |              |             |

|       | 1: SPI0 interi                |              |                 |                |               |          |              |             |

| Bit5: | PT2: Timer 2                  | •            |                 |                |               |          |              |             |

|       | This bit sets                 |              |                 |                | t.            |          |              |             |

|       | 0: Timer 2 int                |              |                 |                |               |          |              |             |

| Bit4: | 1: Timer 2 inf                |              |                 |                |               |          |              |             |

| DIL4. | PS0: UART0                    | •            | •               |                |               |          |              |             |

|       | This bit sets<br>0: UART0 int | • •          |                 |                | l.            |          |              |             |

|       | 1: UARTO int                  | •            |                 |                |               |          |              |             |

| Bit3: | PT1: Timer 1                  | •            | • •             |                |               |          |              |             |

| Dito. | This bit sets                 | •            |                 |                | t             |          |              |             |

|       | 0: Timer 1 int                |              |                 | •              |               |          |              |             |

|       | 1: Timer 1 int                | •            |                 |                |               |          |              |             |

| Bit2: | PX1: Externa                  |              | • •             | •              |               |          |              |             |

|       | This bit sets                 |              |                 |                | ot 1 interrup | t.       |              |             |

|       | 0: External Ir                |              |                 |                | ·             |          |              |             |

|       | 1: External Ir                | nterrupt 1 s | et to high p    | riority level. |               |          |              |             |

| Bit1: | PT0: Timer 0                  | Interrupt I  | Priority Cont   | rol.           |               |          |              |             |

|       | This bit sets                 | the priority | of the Time     | r 0 interrup   | t.            |          |              |             |

|       | 0: Timer 0 int                | terrupt set  | to low priori   | ty level.      |               |          |              |             |

|       | 1: Timer 0 int                | •            | • •             |                |               |          |              |             |

| Bit0: | PX0: Externa                  |              |                 |                |               |          |              |             |

|       | This bit sets                 |              |                 |                | ot 0 interrup | t.       |              |             |

|       | 0: External Ir                | •            |                 |                |               |          |              |             |

|       | 1: External Ir                | terrunt 0 s  | et to high n    | riority level  |               |          |              |             |

## SFR Definition 9.8. IP: Interrupt Priority

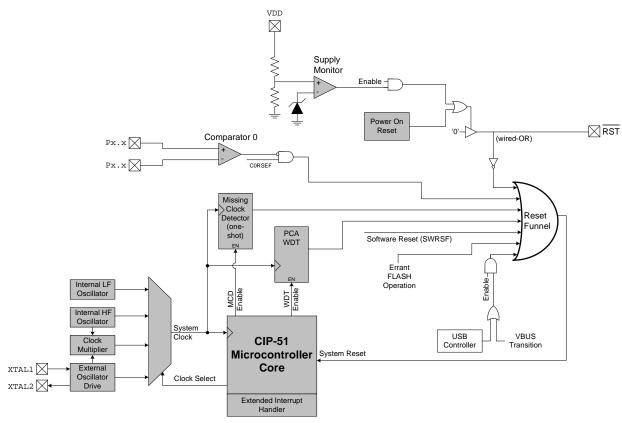

## 11. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pull-ups are enabled during and after the reset. For  $V_{DD}$  Monitor and Power-On Resets, the RST pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. Refer to **Section "14. Oscillators" on page 131** for information on selecting and configuring the system clock source. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source (**Section "22.3. Watchdog Timer Mode" on page 264** details the use of the Watchdog Timer). Program execution begins at location 0x0000.

Figure 11.1. Reset Sources

| Parameter                   | Description                                    | Min*                    | Max*                     | Units |

|-----------------------------|------------------------------------------------|-------------------------|--------------------------|-------|

| T <sub>ACS</sub>            | Address / Control Setup Time                   | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ACW</sub>            | Address / Control Pulse Width                  | 1 x T <sub>SYSCLK</sub> | 16 x T <sub>SYSCLK</sub> | ns    |

| T <sub>ACH</sub>            | Address / Control Hold Time                    | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEH</sub>           | Address Latch Enable High Time                 | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEL</sub>           | Address Latch Enable Low Time                  | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>WDS</sub>            | Write Data Setup Time                          | 1 x T <sub>SYSCLK</sub> | 19 x T <sub>SYSCLK</sub> | ns    |

| T <sub>WDH</sub>            | Write Data Hold Time                           | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>RDS</sub>            | Read Data Setup Time                           | 20                      |                          | ns    |

| T <sub>RDH</sub>            | Read Data Hold Time                            | 0                       |                          | ns    |

| lote: T <sub>SYSCLK</sub> i | s equal to one period of the device system clo | ck (SYSCLK).            |                          | •     |

Table 13.1. AC Parameters for External Memory Interface

|                                   |   |   |        |          | <b>0</b>   |         | ~      |       |      |       |        | P        | 1          |         |     |    |   |      |      | P        | 2         |          |      |     |      |          | _      | P             | °3         | _            | _     | _ |

|-----------------------------------|---|---|--------|----------|------------|---------|--------|-------|------|-------|--------|----------|------------|---------|-----|----|---|------|------|----------|-----------|----------|------|-----|------|----------|--------|---------------|------------|--------------|-------|---|

| SF Signals<br>(32-pin<br>Package) |   |   | XTAL1  | XTAL2    |            |         | CNVSTR | VREF  |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      | P:       |        | 3.7 u<br>32-p |            |              |       |   |

| SF Signals<br>(48-pin<br>Package) |   |   |        |          |            |         | XTAL1  | XTAL2 |      |       |        | ALE      | CNVSTR     | VREF    | RD  | WR |   |      |      |          |           |          |      |     |      | <u> </u> |        |               |            |              |       |   |

| PIN I/O                           | 0 | 1 | 2      | 3        | 4          | 5       | 6      | 7     | 0    | 1     | 2      | 3        | 4          | 5       | 6   | 7  | 0 | 1    | 2    | 3        | 4         | 5        | 6    | 7   | 0    | 1        | 2      | 3             | 4          | 5            | 6     | 7 |

| ТХ0                               |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| RX0                               |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| SCK                               |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| MISO                              |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| MOSI                              |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| NSS*                              |   |   |        |          |            | *NS     | S is   | only  | pinr | ned c | ut in  | 4-wi     | re S       | Pl m    | ode |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| SDA                               |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| SCL                               |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| CP0                               |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| CP0A                              |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| CP1                               |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| CP1A                              |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| SYSCLK                            |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| CEX0                              |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| CEX1                              |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| CEX2                              |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| CEX3                              |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| CEX4                              |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| ECI                               |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       |   |

| то                                |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       | Γ |

| T1                                |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          |      |     |      |          |        |               |            |              |       | Γ |

| TX1**                             |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   | **U/ | ART1 | ava      | ilable    | e only   | y on | C80 | 51F3 | 40/1     | /4/5/  | 8/A/          | B de       | vices        | <br>; |   |

| RX1**                             |   |   |        |          |            |         |        |       |      |       |        |          |            |         |     |    |   |      |      |          |           |          | ĺ    |     |      |          |        |               |            |              |       |   |

|                                   | 0 | 0 | 0<br>P | 0<br>0SK | 0<br>IP[0: | 0<br>7] | 0      | 0     | 0    | 0     | 0<br>P | 0<br>1SK | 0<br>IP[0: | 0<br>7] | 0   | 0  | 0 | 0    |      | 0<br>2SK | 0<br>P[0: | 0<br>:7] | 0    | 0   | 0    | 0        | 0<br>P | 0<br>3SK      | 0<br>IP[0: | 0<br>:7]     | 0     | ( |

| SF Signals                        |   |   |        | -        |            |         |        |       | he C |       |        | Cro      |            | - 10/   |     |    |   |      |      |          |           |          |      |     | Exa  | mple     | e:     |               |            | 0x07<br>0x43 |       |   |

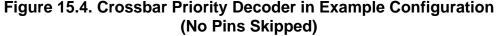

## SFR Definition 15.11. P1SKIP: Port1 Skip

| R/W          | R/W                                                                                              | R/W                                                     | R/W                                                        | R/W                                                      | R/W                                                     | R/W                   | R/W  | Reset Value 00000000          |

|--------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|-----------------------|------|-------------------------------|

| Bit7         | Bit6                                                                                             | Bit5                                                    | Bit4                                                       | Bit3                                                     | Bit2                                                    | Bit1                  | Bit0 | SFR Address:<br>0xD5          |

| ר<br>וג<br>נ | P1SKIP[7:0]:<br>These bits se<br>og inputs (fo<br>ator circuit, (<br>): Correspon<br>: Correspon | elect Port p<br>r ADC or C<br>CNVSTR in<br>iding P1.n p | ins to be sk<br>omparator)<br>put) should<br>pin is not sk | ipped by the<br>or used as<br>be skipped<br>ipped by the | e Crossbar<br>special fund<br>by the Cro<br>e Crossbar. | ctions (VRE<br>ssbar. |      | sed as ana-<br>xternal oscil- |

## SFR Definition 15.12. P2: Port2 Latch

| R/W<br>P2.7 | R/W<br>P2.6                                                                                                                   | R/W<br>P2.5                                                                 | R/W<br>P2.4                               | R/W<br>P2.3                  | R/W<br>P2.2 | R/W<br>P2.1 | R/W<br>P2.0    | Reset Value<br>11111111 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------|------------------------------|-------------|-------------|----------------|-------------------------|

| Bit7        | Bit6                                                                                                                          | Bit5                                                                        | Bit4                                      | Bit3                         | Bit2        | Bit1        | Bit0           | SFR Address:            |

|             |                                                                                                                               |                                                                             |                                           |                              |             | (bi         | t addressable) | 0xA0                    |

| Bits7–0:    | P2.[7:0]<br>Write - Outpu<br>0: Logic Low<br>1: Logic High<br>Read - Alwa<br>pin when cou<br>0: P2.n pin is<br>1: P2.n pin is | o Output.<br>In Output (hi<br>ys reads '0'<br>Infigured as<br>Is logic low. | gh impedar<br>if selected<br>digital inpu | nce if corres<br>as analog i | ponding P2  | 2MDOUT.n l  | bit = 0).      |                         |

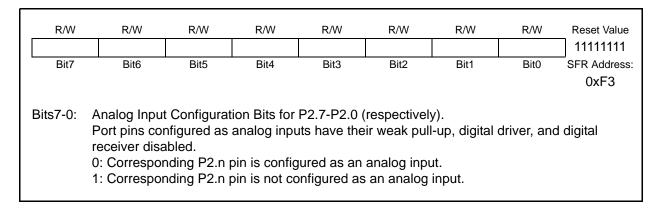

## SFR Definition 15.13. P2MDIN: Port2 Input Mode

### USB Register Definition 16.14. IN1IE: USB0 IN Endpoint Interrupt Enable

| R/W      | R/W                                  | R/W           | R/W        | R/W       | R/W  | R/W  | R/W  | Reset Value  |  |  |  |

|----------|--------------------------------------|---------------|------------|-----------|------|------|------|--------------|--|--|--|

| -        | -                                    | -             | -          | IN3E      | IN2E | IN1E | EP0E | 00001111     |  |  |  |

| Bit7     | Bit6                                 | Bit5          | Bit4       | Bit3      | Bit2 | Bit1 | Bit0 | USB Address: |  |  |  |

|          |                                      |               |            |           |      |      |      | 0x07         |  |  |  |

| Bits7–4: | Unused. Rea                          | ad = 0000b.   | Write = do | n't care. |      |      |      |              |  |  |  |

| Bit3:    | IN3E: IN Endpoint 3 Interrupt Enable |               |            |           |      |      |      |              |  |  |  |

|          | 0: IN Endpoint 3 interrupt disabled. |               |            |           |      |      |      |              |  |  |  |

|          | 1: IN Endpoint 3 interrupt enabled.  |               |            |           |      |      |      |              |  |  |  |

| Bit2:    | IN2E: IN Endpoint 2 Interrupt Enable |               |            |           |      |      |      |              |  |  |  |

|          | 0: IN Endpoint 2 interrupt disabled. |               |            |           |      |      |      |              |  |  |  |

|          | 1: IN Endpoint 2 interrupt enabled.  |               |            |           |      |      |      |              |  |  |  |

| Bit1:    | IN1E: IN Endpoint 1 Interrupt Enable |               |            |           |      |      |      |              |  |  |  |

|          | 0: IN Endpoint 1 interrupt disabled. |               |            |           |      |      |      |              |  |  |  |

|          | 1: IN Endpoint 1 interrupt enabled.  |               |            |           |      |      |      |              |  |  |  |

| Bit0:    | EP0E: Endpoint 0 Interrupt Enable    |               |            |           |      |      |      |              |  |  |  |

|          | 0: Endpoint (                        |               |            |           |      |      |      |              |  |  |  |

|          | 1: Endpoint (                        | ) interrunt e | nahled     |           |      |      |      |              |  |  |  |

## USB Register Definition 16.15. OUT1IE: USB0 Out Endpoint Interrupt Enable

| R/W          | R/W                                                                             | R/W        | R/W        | R/W      | R/W   | R/W   | R/W  | Reset Value  |  |  |  |

|--------------|---------------------------------------------------------------------------------|------------|------------|----------|-------|-------|------|--------------|--|--|--|

| -            | -                                                                               | -          | -          | OUT3E    | OUT2E | OUT1E | -    | 00001110     |  |  |  |

| Bit7         | Bit6                                                                            | Bit5       | Bit4       | Bit3     | Bit2  | Bit1  | Bit0 | USB Address: |  |  |  |

|              |                                                                                 |            |            |          |       |       |      | 0x09         |  |  |  |

| Bits7–4:     | Unused, Rea                                                                     | ad – 0000b | Write – do | n't care |       |       |      |              |  |  |  |

| Bit3:        | 0                                                                               |            |            |          |       |       |      |              |  |  |  |

| Dito.        | OUT3E: OUT Endpoint 3 Interrupt Enable<br>0: OUT Endpoint 3 interrupt disabled. |            |            |          |       |       |      |              |  |  |  |

|              | 1: OUT Endpoint 3 interrupt enabled.                                            |            |            |          |       |       |      |              |  |  |  |

| Bit2:        |                                                                                 |            |            |          |       |       |      |              |  |  |  |

| DILZ.        | OUT2E: OUT Endpoint 2 Interrupt Enable                                          |            |            |          |       |       |      |              |  |  |  |

|              | 0: OUT Endpoint 2 interrupt disabled.<br>1: OUT Endpoint 2 interrupt enabled.   |            |            |          |       |       |      |              |  |  |  |

| <b>D</b> '44 |                                                                                 |            | •          |          |       |       |      |              |  |  |  |

| Bit1:        | OUT1E: OUT Endpoint 1 Interrupt Enable                                          |            |            |          |       |       |      |              |  |  |  |

|              | 0: OUT Endpoint 1 interrupt disabled.                                           |            |            |          |       |       |      |              |  |  |  |

|              | 1: OUT Endp                                                                     |            | •          |          |       |       |      |              |  |  |  |

|              | Unused. Rea                                                                     |            |            |          |       |       |      |              |  |  |  |

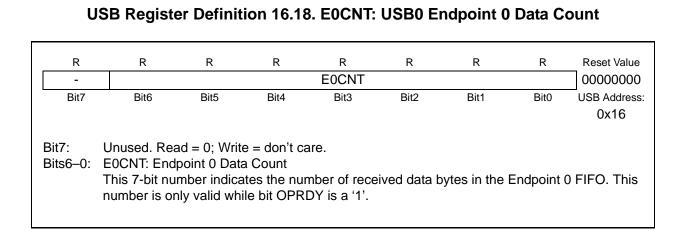

## 16.11. Configuring Endpoints1-3

Endpoints1-3 are configured and controlled through their own sets of the following control/status registers: IN registers EINCSRL and EINCSRH, and OUT registers EOUTCSRL and EOUTCSRH. Only one set of endpoint control/status registers is mapped into the USB register address space at a time, defined by the contents of the INDEX register (USB Register Definition 16.4).

Endpoints1-3 can be configured as IN, OUT, or both IN/OUT (Split Mode) as described in **Section 16.5.1**. The endpoint mode (Split/Normal) is selected via the SPLIT bit in register EINCSRH.

When SPLIT = '1', the corresponding endpoint FIFO is split, and both IN and OUT pipes are available.

When SPLIT = '0', the corresponding endpoint functions as either IN or OUT; the endpoint direction is selected by the DIRSEL bit in register EINCSRH.

### 16.12. Controlling Endpoints1-3 IN

Endpoints1-3 IN are managed via USB registers EINCSRL and EINCSRH. All IN endpoints can be used for Interrupt, Bulk, or Isochronous transfers. Isochronous (ISO) mode is enabled by writing '1' to the ISO bit in register EINCSRH. Bulk and Interrupt transfers are handled identically by hardware.

An Endpoint1-3 IN interrupt is generated by any of the following conditions:

- 1. An IN packet is successfully transferred to the host.

- 2. Software writes '1' to the FLUSH bit (EINCSRL.3) when the target FIFO is not empty.

- 3. Hardware generates a STALL condition.

#### 16.12.1.Endpoints1-3 IN Interrupt or Bulk Mode

When the ISO bit (EINCSRH.6) = '0' the target endpoint operates in Bulk or Interrupt Mode. Once an endpoint has been configured to operate in Bulk/Interrupt IN mode (typically following an Endpoint0 SET\_IN-TERFACE command), firmware should load an IN packet into the endpoint IN FIFO and set the INPRDY bit (EINCSRL.0). Upon reception of an IN token, hardware will transmit the data, clear the INPRDY bit, and generate an interrupt.

## 17.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I2C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I2C-Bus Specification -- Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification -- Version 1.1, SBS Implementers Forum.

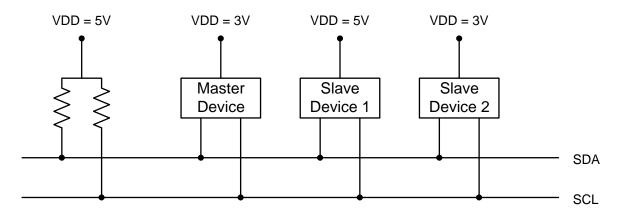

## 17.2. SMBus Configuration

Figure 17.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pull-up resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

## 17.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the Master in a system; any device who transmits a START and a slave address becomes the master for the duration of that transfer.

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7-1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Each byte that is received (by a master or slave) must be acknowledged (ACK) with a low SDA during a high SCL (see Figure 17.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

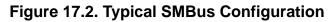

Figure 18.6. UART Multi-Processor Mode Interconnect Diagram

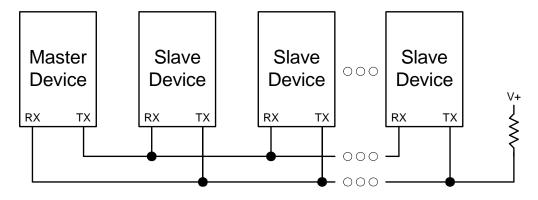

# 20. Enhanced Serial Peripheral Interface (SPI0)

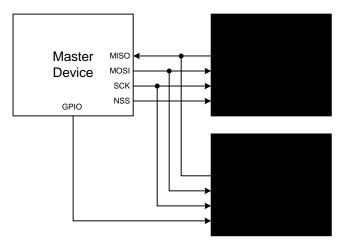

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

Figure 20.1. SPI Block Diagram

### 20.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

#### 20.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

### 20.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

### 20.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 20.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

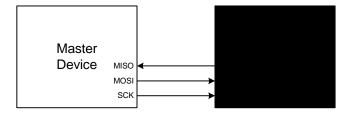

- NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

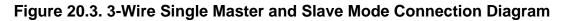

- 2. NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 20.2, Figure 20.3, and Figure 20.4 for typical connection diagrams of the various operational modes. Note that the setting of NSSMD bits affects the pinout of the device. When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "15. Port Input/Output" on page 142 for general purpose port I/O and crossbar information.

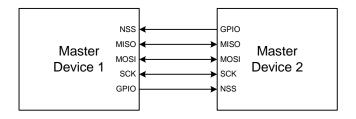

Figure 20.2. Multiple-Master Mode Connection Diagram

Figure 20.4. 4-Wire Single Master Mode and Slave Mode Connection Diagram

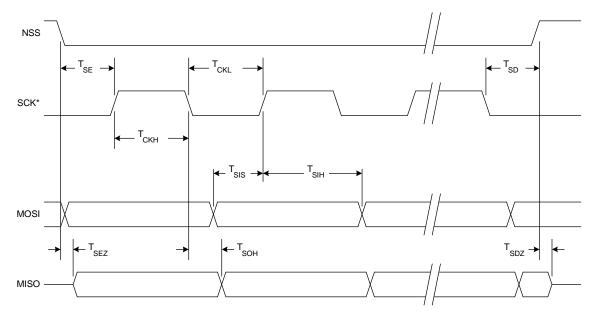

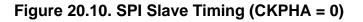

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

Figure 20.11. SPI Slave Timing (CKPHA = 1)

| R/W      | R/W                                                                                                                                            | R/W                           | R/W         | R/W         | R/W         | R/W          | R/W          | Reset Value |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------|-------------|-------------|--------------|--------------|-------------|--|--|--|

| ТЗМН     | T3ML                                                                                                                                           | T2MH                          | T2ML        | T1M         | TOM         | SCA1         | SCA0         | 0000000     |  |  |  |

| Bit7     | Bit6                                                                                                                                           | Bit5                          | Bit4        | Bit3        | Bit2        | Bit1         | Bit0         | SFR Addres  |  |  |  |

|          |                                                                                                                                                |                               |             |             |             |              |              | 0x8E        |  |  |  |

| 0:47.    |                                                                                                                                                | or 2 Lliah Di                 | ta Claak Sc | laat        |             |              |              |             |  |  |  |

| Bit7:    |                                                                                                                                                | er 3 High By<br>ects the cloc |             |             | 3 high hyte | a if Timor 3 | is configur  | od in split |  |  |  |

|          |                                                                                                                                                | node. T3MF                    |             |             |             |              | is connigur  | cu in spin  |  |  |  |

|          |                                                                                                                                                | high byte us                  |             |             |             |              | R3CN.        |             |  |  |  |

|          |                                                                                                                                                | nigh byte us                  |             | •           |             |              |              |             |  |  |  |

| Bit6:    |                                                                                                                                                | er 3 Low Byt                  |             |             |             |              |              |             |  |  |  |

|          |                                                                                                                                                | ects the cloc                 |             |             |             |              | in split 8-b | oit timer   |  |  |  |

|          |                                                                                                                                                | bit selects th                |             |             |             |              |              |             |  |  |  |

|          |                                                                                                                                                | ow byte use                   |             | •           | he T3XCL    | K bit in TMR | CN.          |             |  |  |  |

|          |                                                                                                                                                | ow byte use                   |             |             |             |              |              |             |  |  |  |

| Bit5:    |                                                                                                                                                | er 2 High By                  |             |             | O bigh but  | if Timor O   | ia aanfigur  | ad in anlit |  |  |  |

|          |                                                                                                                                                | ects the cloc<br>node. T2MF   |             |             |             |              | is conligur  | ed in split |  |  |  |

|          |                                                                                                                                                |                               | •           |             |             |              | R2CN         |             |  |  |  |

|          | <ul><li>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.</li><li>1: Timer 2 high byte uses the system clock.</li></ul> |                               |             |             |             |              |              |             |  |  |  |

| Bit4:    | T2ML: Timer 2 Low Byte Clock Select.                                                                                                           |                               |             |             |             |              |              |             |  |  |  |

|          | This bit selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer                                                  |                               |             |             |             |              |              |             |  |  |  |

|          | mode, this bit selects the clock supplied to the lower 8-bit timer.                                                                            |                               |             |             |             |              |              |             |  |  |  |

|          | 0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.                                                                        |                               |             |             |             |              |              |             |  |  |  |

|          | 1: Timer 2 low byte uses the system clock.                                                                                                     |                               |             |             |             |              |              |             |  |  |  |

| Bit3:    | T1M: Timer 1 Clock Select.                                                                                                                     |                               |             |             |             |              |              |             |  |  |  |

|          | This select the clock source supplied to Timer 1. T1M is ignored when C/T1 is set to logic 1                                                   |                               |             |             |             |              |              |             |  |  |  |

|          | 0: Timer 1 uses the clock defined by the prescale bits, SCA1-SCA0.                                                                             |                               |             |             |             |              |              |             |  |  |  |

| Bit2:    | 1: Timer 1 uses the system clock.<br>T0M: Timer 0 Clock Select.                                                                                |                               |             |             |             |              |              |             |  |  |  |

| DILZ.    | This bit selects the clock source supplied to Timer 0. T0M is ignored when C/T0 is set to                                                      |                               |             |             |             |              |              |             |  |  |  |

|          | logic 1.                                                                                                                                       |                               |             |             |             |              |              |             |  |  |  |

|          | 0: Counter/Timer 0 uses the clock defined by the prescale bits, SCA1-SCA0.                                                                     |                               |             |             |             |              |              |             |  |  |  |

|          | 1: Counter/Timer 0 uses the system clock.                                                                                                      |                               |             |             |             |              |              |             |  |  |  |

| Bits1–0: | SCA1-SCA0: Timer 0/1 Prescale Bits.                                                                                                            |                               |             |             |             |              |              |             |  |  |  |

|          | These bits control the division of the clock supplied to Timer 0 and/or Timer 1 if configured                                                  |                               |             |             |             |              |              |             |  |  |  |

|          | to use prescaled clock inputs.                                                                                                                 |                               |             |             |             |              |              |             |  |  |  |

|          | SCA1                                                                                                                                           | SCA0                          | Preso       | aled Clock  |             |              |              |             |  |  |  |

|          | 0                                                                                                                                              | 0                             |             | ock divided |             |              |              |             |  |  |  |

|          | 0                                                                                                                                              | 1                             |             | ock divided |             |              |              |             |  |  |  |

|          | 1                                                                                                                                              | 0                             | •           | ock divided | -           |              |              |             |  |  |  |

|          | 1                                                                                                                                              | 1                             |             |             |             |              |              |             |  |  |  |

|          |                                                                                                                                                |                               |             | ock aiviaea | υνοι        |              |              |             |  |  |  |

|          |                                                                                                                                                | rnal clock div                |             | ock divided | -           |              |              |             |  |  |  |

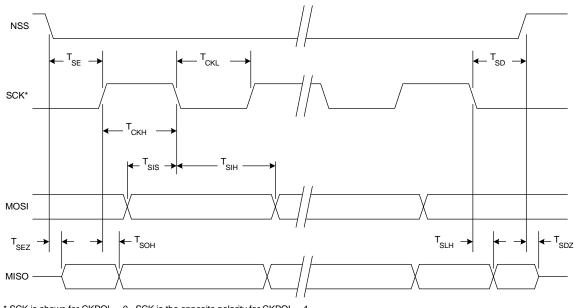

When T2SPLIT = '1', the Timer 2 registers (TMR2H and TMR2L) act as two 8-bit counters. Each counter counts up independently and overflows from 0xFF to 0x00. Each time a capture event is received, the contents of the Timer 2 registers are latched into the Timer 2 Reload registers (TMR2RLH and TMR2RLL). A Timer 2 interrupt is generated if enabled.

Figure 21.7. Timer 2 Capture Mode (T2SPLIT = '1')