Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 17x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f34a-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 19.1. UART1 Block Diagram 21                                         |    |

|-----------------------------------------------------------------------------|----|

| Figure 19.2. UART1 Timing Without Parity or Extra Bit                       |    |

| Figure 19.3. UART1 Timing With Parity 21                                    | 15 |

| Figure 19.4. UART1 Timing With Extra Bit 21                                 | 15 |

| Figure 19.5. Typical UART Interconnect Diagram 21                           | 16 |

| Figure 19.6. UART Multi-Processor Mode Interconnect Diagram                 | 18 |

| 20. Enhanced Serial Peripheral Interface (SPI0)                             |    |

| Figure 20.1. SPI Block Diagram 22                                           | 22 |

| Figure 20.2. Multiple-Master Mode Connection Diagram                        |    |

| Figure 20.3. 3-Wire Single Master and Slave Mode Connection Diagram         |    |

| Figure 20.4. 4-Wire Single Master Mode and Slave Mode Connection Diagram 22 |    |

| Figure 20.5. Master Mode Data/Clock Timing 22                               |    |

| Figure 20.6. Slave Mode Data/Clock Timing (CKPHA = 0)                       |    |

| Figure 20.7. Slave Mode Data/Clock Timing (CKPHA = 1)                       |    |

| Figure 20.8. SPI Master Timing (CKPHA = 0)                                  |    |

| Figure 20.9. SPI Master Timing (CKPHA = 1)                                  |    |

| Figure 20.10. SPI Slave Timing (CKPHA = 0)                                  |    |

| Figure 20.11. SPI Slave Timing (CKPHA = 1)                                  |    |

| 21. Timers                                                                  |    |

| Figure 21.1. T0 Mode 0 Block Diagram23                                      | 36 |

| Figure 21.2. T0 Mode 2 Block Diagram 23                                     |    |

| Figure 21.3. T0 Mode 3 Block Diagram                                        |    |

| Figure 21.4. Timer 2 16-Bit Mode Block Diagram                              |    |

| Figure 21.5. Timer 2 8-Bit Mode Block Diagram                               |    |

| Figure 21.6. Timer 2 Capture Mode (T2SPLIT = '0')                           |    |

| Figure 21.7. Timer 2 Capture Mode (T2SPLIT = '1')                           |    |

| Figure 21.8. Timer 3 16-Bit Mode Block Diagram                              |    |

| Figure 21.9. Timer 3 8-Bit Mode Block Diagram                               |    |

| Figure 21.10. Timer 3 Capture Mode (T3SPLIT = '0')                          |    |

| Figure 21.11. Timer 3 Capture Mode (T3SPLIT = '1')                          | 52 |

| 22. Programmable Counter Array (PCA0)                                       | -  |

| Figure 22.1. PCA Block Diagram                                              | 55 |

| Figure 22.2. PCA Counter/Timer Block Diagram                                |    |

| Figure 22.3. PCA Interrupt Block Diagram                                    |    |

| Figure 22.4. PCA Capture Mode Diagram                                       |    |

| Figure 22.5. PCA Software Timer Mode Diagram                                |    |

| Figure 22.6. PCA High Speed Output Mode Diagram                             |    |

| Figure 22.7. PCA Frequency Output Mode                                      |    |

| Figure 22.8. PCA 8-Bit PWM Mode Diagram                                     |    |

| Figure 22.9. PCA 16-Bit PWM Mode                                            |    |

| Figure 22.10. PCA Module 4 with Watchdog Timer Enabled                      |    |

| 23. C2 Interface                                                            |    |

| Figure 23.1. Typical C2 Pin Sharing                                         | 73 |

|                                                                             | -  |

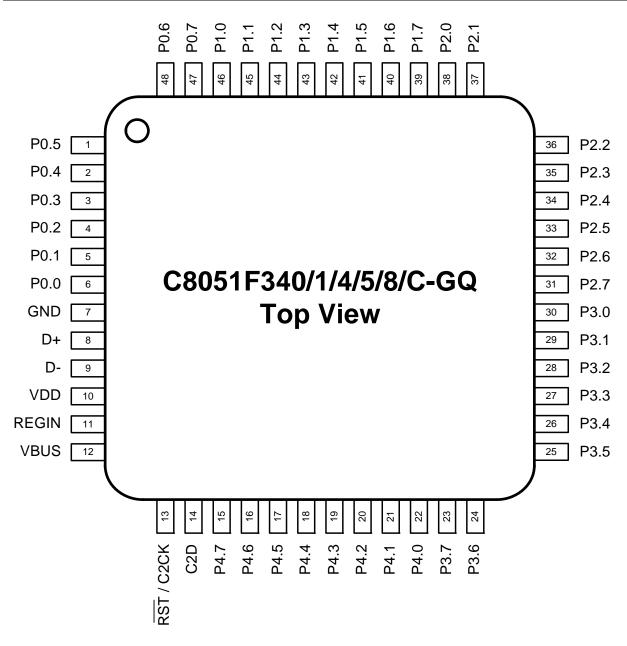

Figure 4.1. TQFP-48 Pinout Diagram (Top View)

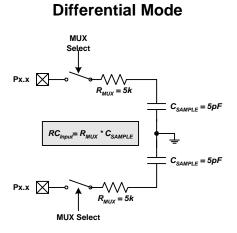

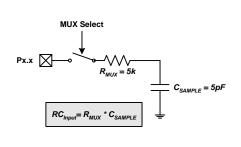

### 5.3.3. Settling Time Requirements

When the ADC0 input configuration is changed (i.e., a different AMUX0 selection is made), a minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the minimum tracking time requirements.

Figure 5.5 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 5.1. When measuring the Temperature Sensor output or  $V_{DD}$  with respect to GND,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 5.1 for ADC0 minimum settling time requirements.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

## Equation 5.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

*n* is the ADC resolution in bits (10).

Single-Ended Mode

## Figure 5.5. ADC0 Equivalent Input Circuits

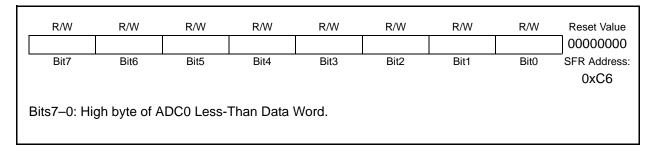

## SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte

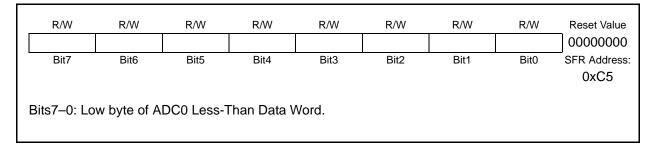

## SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte

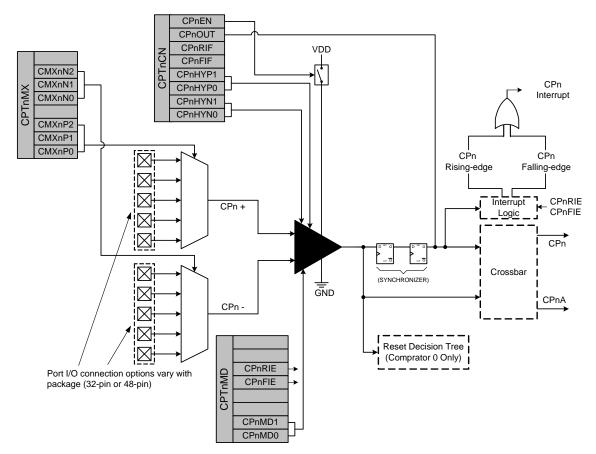

Figure 7.1. Comparator Functional Block Diagram

Comparator outputs can be polled in software, used as an interrupt source, and/or routed to a Port pin. When routed to a Port pin, Comparator outputs are available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP mode (with no system clock active). When disabled, the Comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and supply current falls to less than 100 nA. See **Section "15.1. Priority Crossbar Decoder" on page 144** for details on configuring Comparator outputs via the digital Crossbar. Comparator inputs can be externally driven from -0.25 V to (V<sub>DD</sub>) + 0.25 V without damage or upset. The complete Comparator electrical specifications are given in Table 7.1.

Comparator response time may be configured in software via the CPTnMD registers (see SFR Definition 7.3 and SFR Definition 7.6). Selecting a longer response time reduces the Comparator supply current. See Table 7.1 for complete timing and supply current specifications.

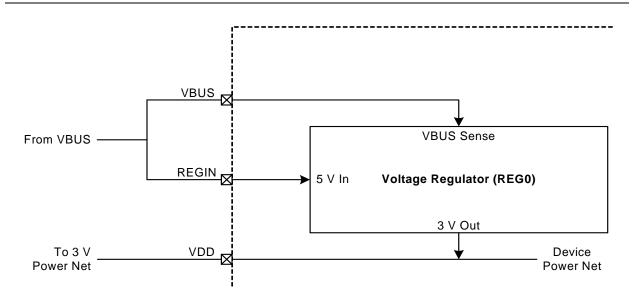

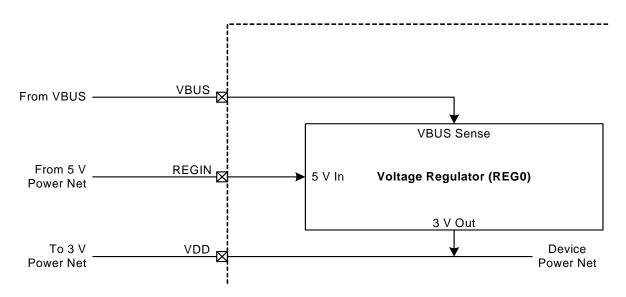

Figure 8.1. REG0 Configuration: USB Bus-Powered

Figure 8.2. REG0 Configuration: USB Self-Powered

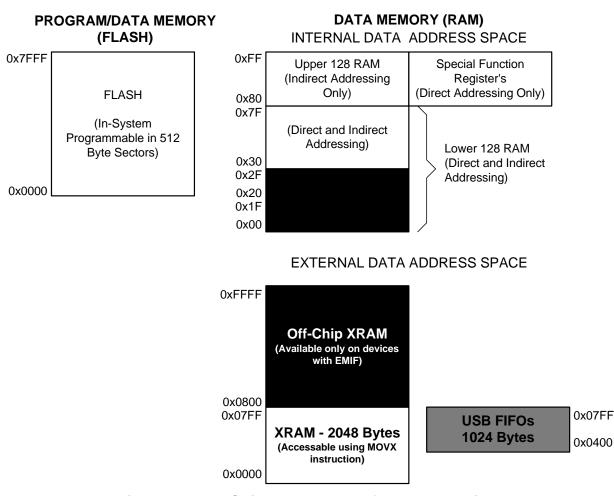

Figure 9.3. On-Chip Memory Map for 32 kB Devices

### 9.2.1. Program Memory

The CIP-51 core has a 64k-byte program memory space. The C8051F34x implements 64k or 32k bytes of this program memory space as in-system, re-programmable Flash memory. Note that on the 64k versions of the C8051F34x, addresses above 0xFBFF are reserved.

Program memory is normally assumed to be read-only. However, the CIP-51 can write to program memory by setting the Program Store Write Enable bit (PSCTL.0) and using the MOVX instruction. This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to **Section "12. Flash Memory" on page 107** for further details.

### 9.2.6. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the CIP-51's resources and peripherals. The CIP-51 duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the MCU. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 9.2 lists the SFRs implemented in the CIP-51 System Controller.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the datasheet, as indicated in Table 9.3, for a detailed description of each register.

| F8 | SPI0CN | PCA0L    | PCA0H    | PCA0CPL0 | PCA0CPH0 | PCA0CPL4 | PCA0CPH4 | VDM0CN  |

|----|--------|----------|----------|----------|----------|----------|----------|---------|

| F0 | В      | P0MDIN   | P1MDIN   | P2MDIN   | P3MDIN   | P4MDIN   | EIP1     | EIP2    |

| E8 | ADC0CN | PCA0CPL1 | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 | PCA0CPL3 | PCA0CPH3 | RSTSRC  |

| E0 | ACC    | XBR0     | XBR1     | XBR2     | IT01CF   | SMOD1    | EIE1     | EIE2    |

| D8 | PCA0CN | PCA0MD   | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 | PCA0CPM3 | PCA0CPM4 | P3SKIP  |

| D0 | PSW    | REF0CN   | SCON1    | SBUF1    | P0SKIP   | P1SKIP   | P2SKIP   | USB0XCN |

| C8 | TMR2CN | REG0CN   | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H    | -        | -       |

| C0 | SMB0CN | SMB0CF   | SMB0DAT  | ADC0GTL  | ADC0GTH  | ADC0LTL  | ADC0LTH  | P4      |

| B8 | IP     | CLKMUL   | AMX0N    | AMX0P    | ADC0CF   | ADC0L    | ADC0H    | -       |

| B0 | P3     | OSCXCN   | OSCICN   | OSCICL   | SBRLL1   | SBRLH1   | FLSCL    | FLKEY   |

| A8 | IE     | CLKSEL   | EMIOCN   | -        | SBCON1   | -        | P4MDOUT  | PFE0CN  |

| A0 | P2     | SPI0CFG  | SPI0CKR  | SPI0DAT  | POMDOUT  | P1MDOUT  | P2MDOUT  | P3MDOUT |

| 98 | SCON0  | SBUF0    | CPT1CN   | CPT0CN   | CPT1MD   | CPT0MD   | CPT1MX   | CPT0MX  |

| 90 | P1     | TMR3CN   | TMR3RLL  | TMR3RLH  | TMR3L    | TMR3H    | USB0ADR  | USB0DAT |

| 88 | TCON   | TMOD     | TL0      | TL1      | TH0      | TH1      | CKCON    | PSCTL   |

| 80 | P0     | SP       | DPL      | DPH      | EMI0TC   | EMI0CF   | OSCLCN   | PCON    |

| -  | 0(8)   | 1(9)     | 2(A)     | 3(B)     | 4(C)     | 5(D)     | 6(E)     | 7(F)    |

### Table 9.2. Special Function Register (SFR) Memory Map

(bit addressable)

| R/W   | R/W                                                                                              | R/W                                                                                              | R/W             | R/W            | R/W           | R/W      | R/W          | Reset Value |  |  |  |

|-------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------|----------------|---------------|----------|--------------|-------------|--|--|--|

| -     | PSPI0                                                                                            | PT2                                                                                              | PS0             | PT1            | PX1           | PT0      | PX0          | 1000000     |  |  |  |

| Bit7  | Bit6                                                                                             | Bit5                                                                                             | Bit4            | Bit3           | Bit2          | Bit1     | Bit0         | SFR Address |  |  |  |

|       |                                                                                                  |                                                                                                  |                 |                |               | (bi      | t addressabl | e) 0xB8     |  |  |  |

| Bit7: | UNUSED. Re                                                                                       | ead = 1, W                                                                                       | /rite = don't d | care.          |               |          |              |             |  |  |  |

| Bit6: | PSPI0: Seria                                                                                     | •                                                                                                |                 | · · ·          | rupt Priority | Control. |              |             |  |  |  |

|       | This bit sets                                                                                    |                                                                                                  |                 |                |               |          |              |             |  |  |  |

|       | 0: SPI0 interi                                                                                   | •                                                                                                |                 |                |               |          |              |             |  |  |  |

|       | 1: SPI0 interi                                                                                   |                                                                                                  |                 |                |               |          |              |             |  |  |  |

| Bit5: | PT2: Timer 2                                                                                     | •                                                                                                |                 |                |               |          |              |             |  |  |  |

|       | This bit sets                                                                                    |                                                                                                  |                 |                | t.            |          |              |             |  |  |  |

|       | 0: Timer 2 int                                                                                   |                                                                                                  |                 |                |               |          |              |             |  |  |  |

| Bit4: | 1: Timer 2 inf                                                                                   |                                                                                                  |                 |                |               |          |              |             |  |  |  |

| DIL4. | PS0: UART0                                                                                       | •                                                                                                | •               |                |               |          |              |             |  |  |  |

|       | This bit sets the priority of the UART0 interrupt.                                               |                                                                                                  |                 |                |               |          |              |             |  |  |  |

|       | 0: UART0 interrupt set to low priority level.<br>1: UART0 interrupts set to high priority level. |                                                                                                  |                 |                |               |          |              |             |  |  |  |

| Bit3: |                                                                                                  | •                                                                                                | • •             |                |               |          |              |             |  |  |  |

| Dito. |                                                                                                  | PT1: Timer 1 Interrupt Priority Control.<br>This bit sets the priority of the Timer 1 interrupt. |                 |                |               |          |              |             |  |  |  |

|       | 0: Timer 1 int                                                                                   |                                                                                                  |                 | •              |               |          |              |             |  |  |  |

|       | 1: Timer 1 int                                                                                   | •                                                                                                |                 |                |               |          |              |             |  |  |  |

| Bit2: | PX1: Externa                                                                                     |                                                                                                  | • •             |                |               |          |              |             |  |  |  |

|       | This bit sets                                                                                    |                                                                                                  |                 |                | ot 1 interrup | t.       |              |             |  |  |  |

|       | 0: External Ir                                                                                   |                                                                                                  |                 |                | ·             |          |              |             |  |  |  |

|       | 1: External Ir                                                                                   | nterrupt 1 s                                                                                     | et to high p    | riority level. |               |          |              |             |  |  |  |

| Bit1: | PT0: Timer 0                                                                                     | Interrupt I                                                                                      | Priority Cont   | rol.           |               |          |              |             |  |  |  |

|       | This bit sets                                                                                    | the priority                                                                                     | of the Time     | r 0 interrup   | t.            |          |              |             |  |  |  |

|       | 0: Timer 0 int                                                                                   | terrupt set                                                                                      | to low priori   | ty level.      |               |          |              |             |  |  |  |

|       | 1: Timer 0 int                                                                                   |                                                                                                  | • •             |                |               |          |              |             |  |  |  |

| Bit0: | PX0: Externa                                                                                     |                                                                                                  |                 |                |               |          |              |             |  |  |  |

|       | This bit sets                                                                                    |                                                                                                  |                 |                | ot 0 interrup | t.       |              |             |  |  |  |

|       | 0: External Ir                                                                                   | •                                                                                                |                 |                |               |          |              |             |  |  |  |

|       | 1: External Ir                                                                                   | nterrupt 0 s                                                                                     | set to high p   | riority level  |               |          |              |             |  |  |  |

## SFR Definition 9.8. IP: Interrupt Priority

### SFR Definition 9.13. IT01CF: INT0/INT1 Configuration

| R/W            | R/W                              | R/W          | R/W           | R/W           | R/W          | R/W           | R/W          | Reset Value  |

|----------------|----------------------------------|--------------|---------------|---------------|--------------|---------------|--------------|--------------|

| IN1PL          | IN1SL2                           | IN1SL1       | IN1SL0        | INOPL         | IN0SL2       | IN0SL1        | INOSLO       | 00000001     |

| Bit7           | Bit6                             | Bit5         | Bit4          | Bit3          | Bit2         | Bit1          | Bit0         | SFR Address  |

| Ditt           | Bito                             | Dito         | DILT          | Dito          | DILZ         | Diti          | Dito         | 0xE4         |

| Note: Re       | fer to SFR Def                   | inition 21   | 1 for INITO/1 | edae- or le   | wal-consitiv | o interrunt ( | election     |              |

| NOLE. INE      |                                  | 11111011 21. |               | euge- of le   | ver-sensitiv | eintenupt     |              |              |

| Bit7:          | IN1PL: INT1                      | Polarity     |               |               |              |               |              |              |

| Dit <i>i</i> . | 0: INT1 input                    |              | <b>\</b> \//  |               |              |               |              |              |

|                | 1: INT1 input                    |              |               |               |              |               |              |              |

| Bits6–4:       | IN1SL2-0: IN                     |              |               | Bits          |              |               |              |              |

|                | These bits se                    |              |               |               | INT1. Note   | that this pi  | n assignme   | ent is inde- |

|                | pendent of th                    | e Crossba    | r; INT1 will  | monitor the   | assigned F   | ort pin with  | out disturbi | ng the       |

|                | peripheral that                  | at has beer  | n assigned    | the Port pin  | via the Cro  | ssbar. The    | Crossbar w   | /ill not     |

|                | assign the Po                    |              |               |               |              | the selected  | d pin (accor | nplished by  |

|                | setting to '1' t                 | he corresp   | onding bit i  | in register F | POSKIP).     |               |              |              |

|                |                                  |              |               |               |              |               |              |              |

|                | IN1SL2-0                         | INT          | 1 Port Pin    |               |              |               |              |              |

|                | 000                              |              | P0.0          |               |              |               |              |              |

|                | 001                              |              | P0.1          |               |              |               |              |              |

|                | 010                              |              | P0.2          |               |              |               |              |              |

|                | 011                              |              | P0.3          |               |              |               |              |              |

|                | 100                              |              | P0.4          |               |              |               |              |              |

|                | 101                              |              | P0.5          |               |              |               |              |              |

|                | 110                              |              | P0.6          |               |              |               |              |              |

|                | 111                              |              | P0.7          |               |              |               |              |              |

| D:40.          |                                  | Delevite     |               |               |              |               |              |              |

| Bit3:          | INOPL: INTO                      |              |               |               |              |               |              |              |

|                | 0: INT0 interr<br>1: INT0 interr | •            |               |               |              |               |              |              |

| Bits2–0:       | INT0SL2-0: I                     |              |               | n Rits        |              |               |              |              |

| DI(02 0.       | These bits se                    |              |               |               | INTO Note    | that this pi  | n assignme   | ent is inde- |

|                | pendent of th                    |              |               |               |              |               |              |              |

|                | peripheral that                  |              |               |               |              |               |              |              |

|                | assign the Pc                    |              |               |               |              |               |              |              |

|                | setting to '1' t                 | he corresp   | onding bit i  | in register F | OSKIP).      |               |              |              |

|                |                                  |              |               |               |              |               |              |              |

|                | IN0SL2-0                         | INT          | 0 Port Pin    |               |              |               |              |              |

|                | 000                              |              | P0.0          |               |              |               |              |              |

|                | 001                              |              | P0.1          |               |              |               |              |              |

|                | 010                              |              | P0.2          |               |              |               |              |              |

|                | 011                              |              | P0.3          |               |              |               |              |              |

|                |                                  |              | P0.4          |               |              |               |              |              |

|                | 100                              |              |               |               |              |               |              |              |

|                | 100<br>101                       |              | P0.5          |               |              |               |              |              |

|                |                                  |              |               |               |              |               |              |              |

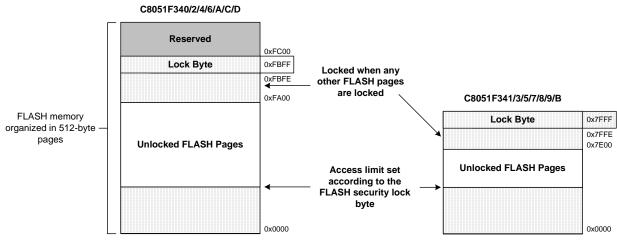

Figure 12.1. Flash Program Memory Map and Security Byte

| R/W      | R/W                          | R/W                                                                       | R/W            | R/W            | R/W                 | R/W                  | R/W         | Reset Value  |  |  |  |  |

|----------|------------------------------|---------------------------------------------------------------------------|----------------|----------------|---------------------|----------------------|-------------|--------------|--|--|--|--|

| K/W      | USBFAE                       | F/W                                                                       | EMD2           | EMD1           | EMD0                | EALE1                | EALE0       | 00000011     |  |  |  |  |

| Bit7     | Bit6                         | Bit5                                                                      | Bit4           | Bit3           | Bit2                | Bit1                 | Bit0        |              |  |  |  |  |

| Diti     | SFR Address: 0x85            |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          |                              |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

| Bit7:    | Unused. Rea                  | ad = 0b. Wr                                                               | rite = don't d | care.          |                     |                      |             |              |  |  |  |  |

| Bit6:    | USBFAE: US                   | Unused. Read = 0b. Write = don't care.<br>USBFAE: USB FIFO Access Enable. |                |                |                     |                      |             |              |  |  |  |  |

|          | 0: USB FIFO                  | RAM not a                                                                 | available th   | rough MOV      | X instructio        | ns.                  |             |              |  |  |  |  |

|          | 1: USB FIFO                  | RAM avai                                                                  | lable using    | MOVX instr     | uctions. Th         | e 1k of USE          | 3 RAM will  | be mapped    |  |  |  |  |

|          | in XRAM spa                  |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          | greater than                 |                                                                           |                | e SYSCLK       | (USBCLK <u>&gt;</u> | <u>&gt;</u> 2 x SYSC | LK) to acc  | ess this     |  |  |  |  |

|          | area with Mo                 |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

| Bit5:    | Unused. Rea                  |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

| Bit4:    | EMD2: EMIF                   | •                                                                         |                |                |                     |                      |             |              |  |  |  |  |

|          | 0: EMIF oper                 |                                                                           | •              |                |                     |                      | (           |              |  |  |  |  |

| D:402 01 | 1: EMIF oper                 |                                                                           |                |                | parate add          | ress and da          | ta pins).   |              |  |  |  |  |

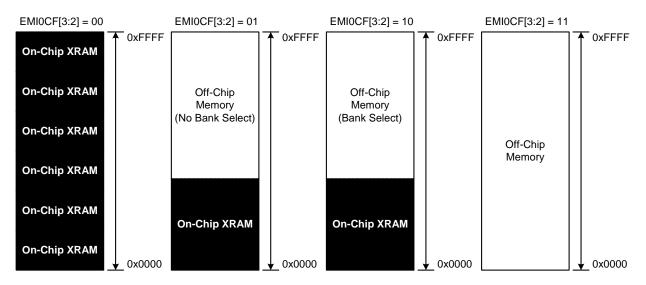

| Bits3–2: | EMD1–0: EM<br>These bits co  |                                                                           |                |                | vtornal Mar         | mon (Intorfo         | <b>~</b>    |              |  |  |  |  |

|          | 00: Internal C               |                                                                           |                |                |                     |                      |             | alias to     |  |  |  |  |

|          | on-chip mem                  |                                                                           |                |                | AIVI OIIIY. A       |                      | 00162262    |              |  |  |  |  |

|          | 01: Split Mod                |                                                                           |                | · Accesses     | helow the c         | on-chin XRA          | M hounda    | rv are       |  |  |  |  |

|          | directed on-c                |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          | off-chip MOV                 |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          | resolve uppe                 |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          | set to a page                |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          | 10: Split Mod                | le with Ban                                                               | k Select: A    | ccesses bel    | ow the on-o         | chip XRAM            | boundary a  | are directed |  |  |  |  |

|          | on-chip. Acce                |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          | MOVX opera                   |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          | 11: External                 | Only: MOV                                                                 | X accesses     | s off-chip XF  | RAM only. C         | On-chip XRA          | M is not vi | sible to the |  |  |  |  |

|          | CPU.                         |                                                                           |                |                |                     |                      | - 1         |              |  |  |  |  |

| Bits1–0: | EALE1-0: AI                  |                                                                           |                |                |                     |                      | = 0).       |              |  |  |  |  |

|          | 00: ALE high                 |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          | 01: ALE high                 |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          | 10: ALE high<br>11: ALE high |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

|          | TT. ALE HIGH                 |                                                                           | ow puise w     | 1001 = 4 3 1 3 |                     | э.                   |             |              |  |  |  |  |

|          |                              |                                                                           |                |                |                     |                      |             |              |  |  |  |  |

### 13.5.2. Non-multiplexed Configuration

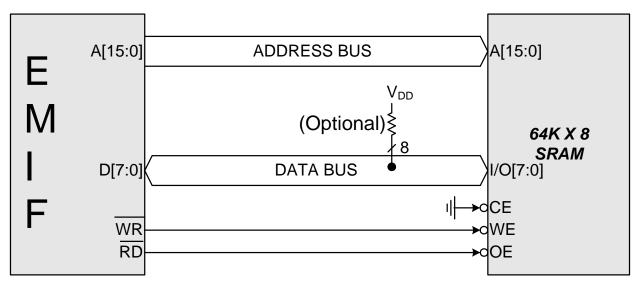

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Non-multiplexed Configuration is shown in Figure 13.3. See **Section "13.7.1. Non-multiplexed Mode" on page 124** for more information about Non-multiplexed operation.

Figure 13.3. Non-multiplexed Configuration Example

## 13.6. Memory Mode Selection

The external data memory space can be configured in one of four modes, shown in Figure 13.4, based on the EMIF Mode bits in the EMIOCF register (SFR Definition 13.2). These modes are summarized below. More information about the different modes can be found in **Section "13.7. Timing" on page 122**.

Figure 13.4. EMIF Operating Modes

| Parameter                   | Description                                    | Min*                    | Max*                     | Units |

|-----------------------------|------------------------------------------------|-------------------------|--------------------------|-------|

| T <sub>ACS</sub>            | Address / Control Setup Time                   | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ACW</sub>            | Address / Control Pulse Width                  | 1 x T <sub>SYSCLK</sub> | 16 x T <sub>SYSCLK</sub> | ns    |

| T <sub>ACH</sub>            | Address / Control Hold Time                    | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEH</sub>           | Address Latch Enable High Time                 | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEL</sub>           | Address Latch Enable Low Time                  | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>WDS</sub>            | Write Data Setup Time                          | 1 x T <sub>SYSCLK</sub> | 19 x T <sub>SYSCLK</sub> | ns    |

| T <sub>WDH</sub>            | Write Data Hold Time                           | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>RDS</sub>            | Read Data Setup Time                           | 20                      |                          | ns    |

| T <sub>RDH</sub>            | Read Data Hold Time                            | 0                       |                          | ns    |

| lote: T <sub>SYSCLK</sub> i | s equal to one period of the device system clo | ck (SYSCLK).            |                          | •     |

Table 13.1. AC Parameters for External Memory Interface

The E0CNT register (USB Register Definition 16.18) holds the number of received data bytes in the Endpoint0 FIFO.

Hardware will automatically detect protocol errors and send a STALL condition in response. Firmware may force a STALL condition to abort the current transfer. When a STALL condition is generated, the STSTL bit will be set to '1' and an interrupt generated. The following conditions will cause hardware to generate a STALL condition:

- 1. The host sends an OUT token during a OUT data phase after the DATAEND bit has been set to '1'.

- 2. The host sends an IN token during an IN data phase after the DATAEND bit has been set to '1'.

- 3. The host sends a packet that exceeds the maximum packet size for Endpoint0.

- 4. The host sends a non-zero length DATA1 packet during the status phase of an IN transaction.

- 5. Firmware sets the SDSTL bit (E0CSR.5) to '1'.

#### 16.10.1.Endpoint0 SETUP Transactions

All control transfers must begin with a SETUP packet. SETUP packets are similar to OUT packets, containing an 8-byte data field sent by the host. Any SETUP packet containing a command field of anything other than 8 bytes will be automatically rejected by USB0. An Endpoint0 interrupt is generated when the data from a SETUP packet is loaded into the Endpoint0 FIFO. Software should unload the command from the Endpoint0 FIFO, decode the command, perform any necessary tasks, and set the SOPRDY bit to indicate that it has serviced the OUT packet.

#### 16.10.2.Endpoint0 IN Transactions

When a SETUP request is received that requires USB0 to transmit data to the host, one or more IN requests will be sent by the host. For the first IN transaction, firmware should load an IN packet into the Endpoint0 FIFO, and set the INPRDY bit (E0CSR.1). An interrupt will be generated when an IN packet is transmitted successfully. Note that no interrupt will be generated if an IN request is received before firmware has loaded a packet into the Endpoint0 FIFO. If the requested data exceeds the maximum packet size for Endpoint0 (as reported to the host), the data should be split into multiple packets; each packet should be of the maximum packet size excluding the last (residual) packet. If the requested data is an integer multiple of the maximum packet size for Endpoint0, the last data packet should be a zero-length packet signaling the end of the transfer. Firmware should set the DATAEND bit to '1' after loading into the Endpoint0 FIFO the last data packet for a transfer.

Upon reception of the first IN token for a particular control transfer, Endpoint0 is said to be in Transmit Mode. In this mode, only IN tokens should be sent by the host to Endpoint0. The SUEND bit (E0CSR.4) is set to '1' if a SETUP or OUT token is received while Endpoint0 is in Transmit Mode.

Endpoint0 will remain in Transmit Mode until any of the following occur:

- 1. USB0 receives an Endpoint0 SETUP or OUT token.

- 2. Firmware sends a packet less than the maximum Endpoint0 packet size.

- 3. Firmware sends a zero-length packet.

Firmware should set the DATAEND bit (E0CSR.3) to '1' when performing (2) and (3) above.

The SIE will transmit a NAK in response to an IN token if there is no packet ready in the IN FIFO (INPRDY = '0').

#### 16.10.3.Endpoint0 OUT Transactions

When a SETUP request is received that requires the host to transmit data to USB0, one or more OUT requests will be sent by the host. When an OUT packet is successfully received by USB0, hardware will set the OPRDY bit (E0CSR.0) to '1' and generate an Endpoint0 interrupt. Following this interrupt, firmware should unload the OUT packet from the Endpoint0 FIFO and set the SOPRDY bit (E0CSR.6) to '1'.

If the amount of data required for the transfer exceeds the maximum packet size for Endpoint0, the data will be split into multiple packets. If the requested data is an integer multiple of the maximum packet size for Endpoint0 (as reported to the host), the host will send a zero-length data packet signaling the end of the transfer.

Upon reception of the first OUT token for a particular control transfer, Endpoint0 is said to be in Receive Mode. In this mode, only OUT tokens should be sent by the host to Endpoint0. The SUEND bit (E0CSR.4) is set to '1' if a SETUP or IN token is received while Endpoint0 is in Receive Mode.

Endpoint0 will remain in Receive mode until:

- 1. The SIE receives a SETUP or IN token.

- 2. The host sends a packet less than the maximum Endpoint0 packet size.

- 3. The host sends a zero-length packet.

Firmware should set the DATAEND bit (E0CSR.3) to '1' when the expected amount of data has been received. The SIE will transmit a STALL condition if the host sends an OUT packet after the DATAEND bit has been set by firmware. An interrupt will be generated with the STSTL bit (E0CSR.2) set to '1' after the STALL is transmitted.

space is made available in the FIFO for another incoming byte. If enabled, an interrupt will occur when RI1 is set. RI1 can only be cleared to '0' by software when there is no more information in the FIFO. The recommended procedure to empty the FIFO contents is as follows:

- 1. Clear RI1 to '0'.

- 2. Read SBUF1.

- 3. Check RI1, and repeat at step 1 if RI1 is set to '1'.

If the extra bit function is enabled (XBE1 = '1') and the parity function is disabled (PE1 = '0'), the extra bit for the oldest byte in the FIFO can be read from the RBX1 bit (SCON1.2). If the extra bit function is not enabled, the value of the stop bit for the oldest FIFO byte will be presented in RBX1. When the parity function is enabled (PE1 = '1'), hardware will check the received parity bit against the selected parity type (selected with S1PT[1:0]) when receiving data. If a byte with parity error is received, the PERR1 flag will be set to '1'. This flag must be cleared by software. Note: when parity is enabled, the extra bit function is not available.

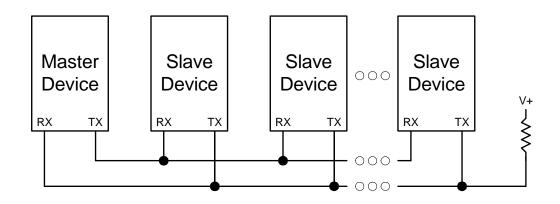

#### 19.3.3. Multiprocessor Communications

UART1 supports multiprocessor communication between a master processor and one or more slave processors by special use of the extra data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its extra bit is logic 1; in a data byte, the extra bit is always set to logic 0.

Setting the MCE1 bit (SMOD1.7) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the extra bit is logic 1 (RBX1 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned address. If the addresses match, the slave will clear its MCE1 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE1 bits set and do not generate interrupts on the reception of the following data bytes, thereby ignoring the data. Once the entire message is received, the addressed slave resets its MCE1 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

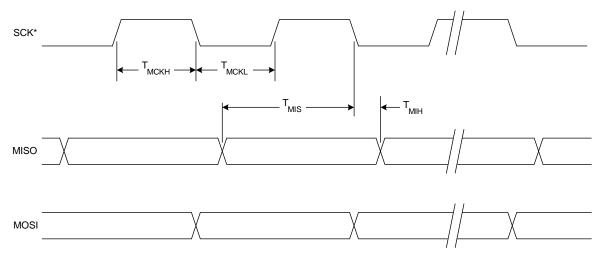

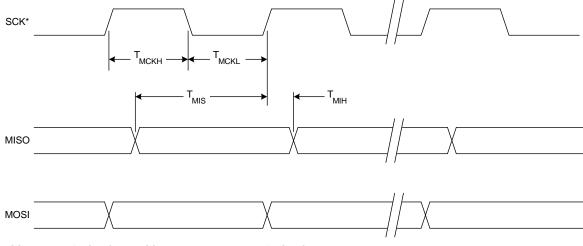

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

## Figure 20.9. SPI Master Timing (CKPHA = 1)

## 22. Programmable Counter Array (PCA0)

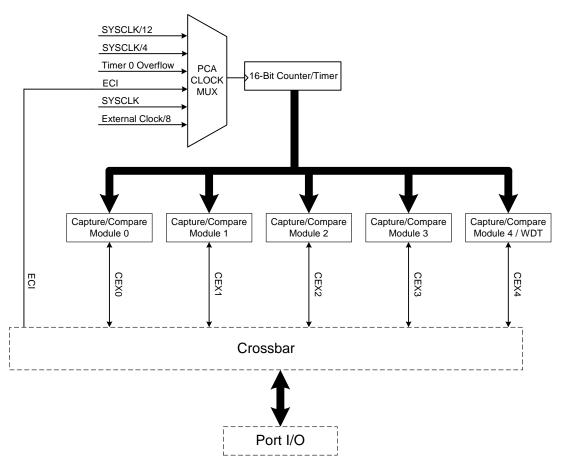

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and five 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "15.1. Priority Crossbar Decoder" on page 144 for details on configuring the Crossbar). The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each mode is described in Section "22.2. Capture/Compare Modules" on page 257). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 22.1

**Important Note:** The PCA Module 4 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See **Section 22.3** for details.

Figure 22.1. PCA Block Diagram