Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 17x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f34b-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

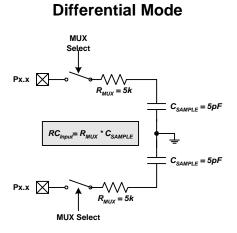

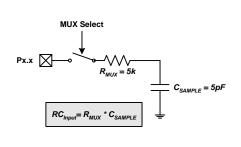

#### 5.3.3. Settling Time Requirements

When the ADC0 input configuration is changed (i.e., a different AMUX0 selection is made), a minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the minimum tracking time requirements.

Figure 5.5 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 5.1. When measuring the Temperature Sensor output or  $V_{DD}$  with respect to GND,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 5.1 for ADC0 minimum settling time requirements.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

### Equation 5.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

*n* is the ADC resolution in bits (10).

Single-Ended Mode

### Figure 5.5. ADC0 Equivalent Input Circuits

### SFR Definition 7.5. CPT1MX: Comparator1 MUX Selection

| R/W               | R/W                                                   | R/W                                                              | R/W                                                                  | R/W                                                                                                 | R/W       | R/W                                                                      | R/W      | Reset Value |

|-------------------|-------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------|----------|-------------|

| -                 | CMX1N2                                                | 2 CMX1N                                                          | 1 CMX1N                                                              | IO - C                                                                                              | CMX1P2    | CMX1P1                                                                   | CMX1P0   | 00000000    |

| Bit7              | Bit6                                                  | Bit5                                                             | Bit4                                                                 | Bit3                                                                                                | Bit2      | Bit1                                                                     | Bit0     | SFR Address |

|                   |                                                       |                                                                  |                                                                      |                                                                                                     |           |                                                                          |          | 0x9E        |

| Bit7:             | UNUSED.                                               | Read = 0b                                                        | , Write = do                                                         | on't care.                                                                                          |           |                                                                          |          |             |

| Bits6–4:          |                                                       |                                                                  | •                                                                    | r1 Negative Inpu                                                                                    |           |                                                                          |          |             |

|                   | These bits                                            | select which                                                     | ch Port pin                                                          | is used as the C                                                                                    | comparato | or1 negative                                                             | e input. |             |

|                   | CMX1N2                                                | CMX1N1                                                           | CMX1N0                                                               | Negative Inp<br>(32-pin Packa                                                                       |           | Negative Ir<br>18-pin Pack                                               |          |             |

|                   | 0                                                     | 0                                                                | 0                                                                    | P1.3                                                                                                | iye) (4   | P2.3                                                                     | aye)     |             |

|                   | 0                                                     | 0                                                                | 1                                                                    | P1.7                                                                                                |           | P3.1                                                                     |          |             |

|                   | 0                                                     | 1                                                                | 0                                                                    | P2.3                                                                                                |           | P4.0                                                                     |          |             |

|                   | 0                                                     | 1                                                                | 1                                                                    | P2.7                                                                                                |           | P4.6                                                                     |          |             |

|                   |                                                       |                                                                  | -                                                                    |                                                                                                     |           | P1.2                                                                     |          |             |

|                   |                                                       | 0                                                                | 0                                                                    | P0.5                                                                                                |           | P1 2                                                                     |          |             |

|                   | 1                                                     | 0                                                                | 0                                                                    | P0.5                                                                                                |           | P1.2                                                                     |          |             |

| Bit3:             |                                                       | -                                                                | -                                                                    |                                                                                                     |           | P1.2                                                                     |          |             |

|                   | UNUSED.                                               | Read = 0b                                                        | , Write = do                                                         |                                                                                                     | MUX Sel   |                                                                          |          |             |

| Bit3:<br>Bits2–0: | UNUSED.<br>CMX1P1-0                                   | Read = 0b<br>CMX1P0: 0                                           | , Write = do<br>Comparator                                           | on't care.                                                                                          |           | ect.                                                                     | input.   |             |

|                   | UNUSED.<br>CMX1P1-0                                   | Read = 0b<br>CMX1P0: 0                                           | , Write = dc<br>Comparator<br>ch Port pin                            | on't care.<br>1 Positive Input                                                                      | comparato | ect.<br>or1 positive<br><b>Positive In</b>                               | put      |             |

|                   | UNUSED.<br>CMX1P1–<br>These bits                      | Read = 0b<br>CMX1P0: 0<br>select whic                            | , Write = dc<br>Comparator<br>ch Port pin                            | on't care.<br>1 Positive Input<br>is used as the C                                                  | comparato | ect.<br>or1 positive                                                     | put      |             |

|                   | UNUSED.<br>CMX1P1–<br>These bits                      | Read = 0b<br>CMX1P0: 0<br>select whic                            | , Write = dc<br>Comparator<br>ch Port pin                            | on't care.<br>1 Positive Input<br>is used as the C<br><b>Positive Inp</b>                           | comparato | ect.<br>or1 positive<br><b>Positive In</b>                               | put      |             |

|                   | UNUSED.<br>CMX1P1–<br>These bits<br>CMX1P2            | Read = 0b<br>CMX1P0: 0<br>select whic<br><b>CMX1P1</b>           | , Write = do<br>Comparator<br>ch Port pin<br><b>CMX1P0</b>           | on't care.<br>1 Positive Input<br>is used as the C<br>Positive Inp<br>(32-pin Packa                 | comparato | ect.<br>or1 positive<br>Positive In<br>18-pin Pacl                       | put      |             |

|                   | UNUSED.<br>CMX1P1-0<br>These bits<br>CMX1P2<br>0      | Read = 0b<br>CMX1P0: C<br>select whic<br><b>CMX1P1</b><br>0      | , Write = dc<br>Comparator<br>ch Port pin<br><b>CMX1P0</b><br>0      | on't care.<br>1 Positive Input<br>is used as the C<br><b>Positive Inp</b><br>(32-pin Packa<br>P1.2  | comparato | ect.<br>pr1 positive<br><b>Positive In</b><br><b>18-pin Pacl</b><br>P2.2 | put      |             |

|                   | UNUSED.<br>CMX1P1-0<br>These bits<br>CMX1P2<br>0<br>0 | Read = 0b<br>CMX1P0: 0<br>select whic<br><b>CMX1P1</b><br>0<br>0 | , Write = dc<br>Comparator<br>ch Port pin<br><b>CMX1P0</b><br>0<br>1 | on't care.<br>1 Positive Input<br>is used as the C<br>Positive Inp<br>(32-pin Packa<br>P1.2<br>P1.6 | comparato | ect.<br>pr1 positive<br>Positive In<br>18-pin Pacl<br>P2.2<br>P3.0       | put      |             |

| SFR Definition 7.6. CPT1MD: Comparator1 Mc | ode Selection |

|--------------------------------------------|---------------|

|--------------------------------------------|---------------|

| R/W       | R/W                                     | R/W          | R/W         | R/W         | R/W       | R/W    | R/W    | Reset Value |  |  |  |  |  |

|-----------|-----------------------------------------|--------------|-------------|-------------|-----------|--------|--------|-------------|--|--|--|--|--|

| -         | -                                       | CP1RIE       | CP1FIE      | -           | -         | CP1MD1 | CP1MD0 | 00000010    |  |  |  |  |  |

| Bit7      | Bit6                                    | Bit5         | Bit4        | Bit3        | Bit2      | Bit1   | Bit0   | SFR Address |  |  |  |  |  |

|           |                                         |              |             |             |           |        |        | 0x9C        |  |  |  |  |  |

| Bits7–6:  | UNUSED. Read = 00b, Write = don't care. |              |             |             |           |        |        |             |  |  |  |  |  |

| Bit5:     | CP1RIE: Co                              |              |             |             | nable.    |        |        |             |  |  |  |  |  |

|           | 0: Compara                              | •            |             |             |           |        |        |             |  |  |  |  |  |

|           | 1: Comparat                             | •            | •           |             |           |        |        |             |  |  |  |  |  |

| Bit4:     | CP1FIE: Co                              |              |             |             | nable.    |        |        |             |  |  |  |  |  |

|           | 0: Comparat                             |              |             |             |           |        |        |             |  |  |  |  |  |

|           | 1: Comparat                             | •            | •           |             |           |        |        |             |  |  |  |  |  |

| Bits1–0:  | CP1MD1-C                                | •            | •           |             | t.        |        |        |             |  |  |  |  |  |

|           | These bits s                            | elect the re | sponse time | e for Compa | rator1.   |        |        |             |  |  |  |  |  |

|           | Mode                                    | CP1MD1       | CP1MD0      | CP1 Pos     | ponse Tim | 0*     |        |             |  |  |  |  |  |

|           | 0                                       |              |             |             | Response  |        |        |             |  |  |  |  |  |

|           | 1                                       | 0            | 1           |             |           |        |        |             |  |  |  |  |  |

|           |                                         |              |             |             |           |        |        |             |  |  |  |  |  |

|           | 2                                       | 1            | 0           |             |           |        |        |             |  |  |  |  |  |

|           | 2<br>3                                  | 1<br>1       | 0<br>1      | Lowe        | st Power  |        |        |             |  |  |  |  |  |

|           |                                         | 1<br>1       |             | Lowe        | st Power  |        |        |             |  |  |  |  |  |

| * See Tab |                                         | 1            | 1           |             | st Power  |        |        |             |  |  |  |  |  |

| Table 9.1. CIP-51 Instruction Set Summary | (Continued) |

|-------------------------------------------|-------------|

|-------------------------------------------|-------------|

| Mnemonic                            | Description                                | Bytes | Clock<br>Cycles |  |

|-------------------------------------|--------------------------------------------|-------|-----------------|--|

| ORL A, #data                        | OR immediate to A                          | 2     | 2               |  |

| ORL direct, A                       | OR A to direct byte                        | 2     | 2               |  |

| ORL direct, #data                   | OR immediate to direct byte                | 3     | 3               |  |

| XRL A, Rn                           | Exclusive-OR Register to A                 | 1     | 1               |  |

| XRL A, direct                       | Exclusive-OR direct byte to A              | 2     | 2               |  |

| XRL A, @Ri                          | Exclusive-OR indirect RAM to A             | 1     | 2               |  |

| XRL A, #data                        | Exclusive-OR immediate to A                | 2     | 2               |  |

| XRL direct, A                       | Exclusive-OR A to direct byte              | 2     | 2               |  |

| XRL direct, #data                   | Exclusive-OR immediate to direct byte      | 3     | 3               |  |

| CLR A                               | Clear A                                    | 1     | 1               |  |

| CPL A                               | Complement A                               | 1     | 1               |  |

| RL A                                | Rotate A left                              | 1     | 1               |  |

| RLC A                               | Rotate A left through Carry                | 1     | 1               |  |

| RR A                                | Rotate A right                             | 1     | 1               |  |

| RRC A                               | Rotate A right through Carry               | 1     | 1               |  |

| SWAP A                              | Swap nibbles of A                          | 1     | 1               |  |

| -                                   | Data Transfer                              |       |                 |  |

| MOV A, Rn                           | Move Register to A                         | 1     | 1               |  |

| MOV A, direct                       | Move direct byte to A                      | 2     | 2               |  |

| MOV A, @Ri                          | Move indirect RAM to A                     | 1     | 2               |  |

| MOV A, #data                        | Move immediate to A                        | 2     | 2               |  |

| MOV Rn, A                           | Move A to Register                         | 1     | 1               |  |

| MOV Rn, direct                      | Move direct byte to Register               | 2     | 2               |  |

| MOV Rn, #data                       | Move immediate to Register                 | 2     | 2               |  |

| MOV direct, A                       | Move A to direct byte                      | 2     | 2               |  |

| MOV direct, Rn                      | Move Register to direct byte               | 2     | 2               |  |

| MOV direct, direct                  | Move direct byte to direct byte            | 3     | 3               |  |

| MOV direct, @Ri                     | Move indirect RAM to direct byte           | 2     | 2               |  |

| MOV direct, @rti                    | Move immediate to direct byte              | 3     | 3               |  |

| MOV @Ri, A                          | Move A to indirect RAM                     | 1     | 2               |  |

| MOV @Ri, A<br>MOV @Ri, direct       | Move direct byte to indirect RAM           | 2     | 2               |  |

| MOV @Ri, #data                      | Move immediate to indirect RAM             | 2     | 2               |  |

| MOV @RI, #data<br>MOV DPTR, #data16 | Load DPTR with 16-bit constant             | 3     | 3               |  |

| MOVC A, @A+DPTR                     | Move code byte relative DPTR to A          | 1     | 3               |  |

| MOVC A, @A+DFTR<br>MOVC A, @A+PC    | Move code byte relative DFTR to A          | 1     | 3               |  |

|                                     |                                            |       |                 |  |

| MOVX A, @Ri                         | Move external data (8-bit address) to A    | 1     | 3               |  |

| MOVX @Ri, A                         | Move A to external data (8-bit address)    | 1     | 3               |  |

| MOVX A, @DPTR                       | Move external data (16-bit address) to A   | 1     | 3               |  |

| MOVX @DPTR, A                       | Move A to external data (16-bit address)   | 1     | 3               |  |

| PUSH direct                         | Push direct byte onto stack                | 2     | 2               |  |

| POP direct                          | Pop direct byte from stack                 | 2     | 2               |  |

| XCH A, Rn                           | Exchange Register with A                   | 1     | 1               |  |

| XCH A, direct                       | Exchange direct byte with A                | 2     | 2               |  |

| XCH A, @Ri                          | Exchange indirect RAM with A               | 1     | 2               |  |

| XCHD A, @Ri                         | Exchange low nibble of indirect RAM with A | 1     | 2               |  |

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 9.13). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see **Section "15.1. Priority Crossbar Decoder" on page 144** for complete details on configuring the Crossbar). In the typical configuration, the external interrupt pin should be skipped in the crossbar and configured as open-drain with the pin latch set to '1'.

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

#### 9.3.3. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP or EIP2) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 9.4.

### 9.3.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 6 system clock cycles: 1 clock cycle to detect the interrupt and 5 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 20 system clock cycles: 1 clock cycle to detect the interrupt, 6 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 5 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

Note that the CPU is stalled during Flash write/erase operations and USB FIFO MOVX accesses (see **Section "13.2. Accessing USB FIFO Space" on page 115**). Interrupt service latency will be increased for interrupts occurring while the CPU is stalled. The latency for these situations will be determined by the standard interrupt service procedure (as described above) and the amount of time the CPU is stalled.

| Interrupt Source               | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|--------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                          | 0x0000              | Тор               | None                                                                       | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(INT0) | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow               | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(INT1) | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow               | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                          | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                | Ν              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow               | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                           | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                | N              | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                           | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Y                | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| USB0                           | 0x0043              | 8                 | Special                                                                    | Ν                | N              | EUSB0<br>(EIE1.1)  | PUSB0<br>(EIP1.1)   |

| ADC0 Window<br>Compare         | 0x004B              | 9                 | ADOWINT<br>(ADC0CN.3)                                                      | Y                | N              | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| ADC0 Conversion<br>Complete    | 0x0053              | 10                | AD0INT (ADC0CN.5)                                                          | Y                | Ν              | EADC0<br>(EIE1.3)  | PADC0<br>(EIP1.3)   |

| Programmable Counter<br>Array  | 0x005B              | 11                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                           | Y                | N              | EPCA0<br>(EIE1.4)  | PPCA0<br>(EIP1.4)   |

| Comparator0                    | 0x0063              | 12                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | Ν                | Ν              | ECP0<br>(EIE1.5)   | PCP0<br>(EIP1.5)    |

| Comparator1                    | 0x006B              | 13                | CP1FIF (CPT1CN.4)<br>CP1RIF (CPT1CN.5)                                     | Ν                | Ν              | ECP1<br>(EIE1.6)   | PCP1<br>(EIP1.6)    |

| Timer 3 Overflow               | 0x0073              | 14                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | Ν                | N              | ET3<br>(EIE1.7)    | PT3<br>(EIP1.7)     |

| VBUS Level                     | 0x007B              | 15                | N/A                                                                        | N/A              | N/A            | EVBUS<br>(EIE2.0)  | PVBUS<br>(EIP2.0)   |

| UART1                          | 0x0083              | 16                | RI1 (SCON1.0)<br>TI1 (SCON1.1)                                             | Ν                | Ν              | ES1<br>(EIE2.1)    | PS1<br>(EIP2.1)     |

Table 9.4. Interrupt Summary

### 9.3.5. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

| R/W       | R                                                                    | R/W          | R/W          | R                        | R/W                     | R/W                       | R                     | Reset Value  |  |  |  |  |

|-----------|----------------------------------------------------------------------|--------------|--------------|--------------------------|-------------------------|---------------------------|-----------------------|--------------|--|--|--|--|

| USBRS     | F FERROR                                                             | CORSEF       | SWRSF        | WDTRSF                   | MCDRSF                  | PORSF                     | PINRSF                | Variable     |  |  |  |  |

| Bit7      | Bit6                                                                 | Bit5         | Bit4         | Bit3                     | Bit2                    | Bit1                      | Bit0                  | SFR Address: |  |  |  |  |

|           |                                                                      |              |              |                          |                         |                           |                       | 0xEF         |  |  |  |  |

|           |                                                                      |              |              |                          |                         |                           |                       |              |  |  |  |  |

| Bit7:     | 5                                                                    |              |              |                          |                         |                           |                       |              |  |  |  |  |

|           | 0: Read: Last reset was not a USB reset; Write: USB resets disabled. |              |              |                          |                         |                           |                       |              |  |  |  |  |

|           | 1: <b>Read:</b> Las                                                  | st reset was | a USB res    | et; <b>Write:</b> L      | JSB resets e            | enabled.                  |                       |              |  |  |  |  |

| Bit6:     | FERROR: F                                                            |              |              |                          |                         |                           |                       |              |  |  |  |  |

|           | 0: Source of                                                         |              |              |                          |                         | ror.                      |                       |              |  |  |  |  |

|           | 1: Source of                                                         |              |              |                          |                         |                           |                       |              |  |  |  |  |

| Bit5:     | CORSEF: Co                                                           | •            |              |                          | -                       | 0                         |                       |              |  |  |  |  |

|           | 0: Read: So                                                          | urce of last | reset was r  | not Compar               | ator0; Write            | : Compara                 | tor0 is not a         | a reset      |  |  |  |  |

|           | source.                                                              | waa af laat  | react was (  |                          | O. Mrites C.            |                           | in a recet            |              |  |  |  |  |

|           | 1: Read: So<br>(active-low).                                         | urce of last | reset was u  | Comparator               |                         | omparatoru                | is a reset s          | source       |  |  |  |  |

| Bit4:     | SWRSF: Sof                                                           | ftware Rese  | t Force and  | d Elag                   |                         |                           |                       |              |  |  |  |  |

| DIL4.     | 0: <b>Read:</b> So                                                   |              |              | -                        | o the SWRS              | SE bit <sup>.</sup> Write | • No Effec            | t            |  |  |  |  |

|           | 1: <b>Read:</b> So                                                   |              |              |                          |                         |                           |                       |              |  |  |  |  |

| Bit3:     | WDTRSF: W                                                            |              |              |                          |                         |                           | a oyotoini i          | 00011        |  |  |  |  |

|           | 0: Source of                                                         | -            |              | -                        |                         |                           |                       |              |  |  |  |  |

|           | 1: Source of                                                         | last reset w | as a WDT     | timeout.                 |                         |                           |                       |              |  |  |  |  |

| Bit2:     | MCDRSF: N                                                            | lissing Cloc | k Detector   | Flag.                    |                         |                           |                       |              |  |  |  |  |

|           | 0: Read: So                                                          | urce of last | reset was r  | not a Missin             | g Clock Det             | ector timed               | out; Write: I         | Missing      |  |  |  |  |

|           | Clock Detect                                                         |              |              |                          |                         |                           |                       |              |  |  |  |  |

|           | 1: <b>Read:</b> So                                                   |              |              | -                        |                         |                           |                       | sing Clock   |  |  |  |  |

| 5         | Detector ena                                                         |              |              | -                        | clock condit            | ion is deteo              | cted.                 |              |  |  |  |  |

| Bit1:     | PORSF: Pov                                                           | -            | -            | -                        |                         |                           |                       |              |  |  |  |  |

|           | This bit is se                                                       | -            | -            |                          | -                       |                           |                       |              |  |  |  |  |

|           | monitor as a                                                         | reset sourc  | e. Note: w   | riting '1' to            | this bit be             | fore the V <sub>D</sub>   | DD monitor            | is enabled   |  |  |  |  |

|           | and stabiliz                                                         |              |              |                          |                         |                           |                       |              |  |  |  |  |

|           | 0: <b>Read:</b> Las                                                  | st reset was | not a pow    | er-on or V <sub>DI</sub> | <sub>D</sub> monitor re | set; Write:               | V <sub>DD</sub> monit | or is not a  |  |  |  |  |

|           | reset source                                                         |              |              |                          |                         |                           |                       |              |  |  |  |  |

|           | 1: <b>Read:</b> Las                                                  | st reset was | a power-or   | n or V <sub>DD</sub> mo  | nitor reset;            | all other res             | et flags ind          | eterminate;  |  |  |  |  |

|           | Write: V <sub>DD</sub> r                                             | nonitor is a | reset source | ce.                      |                         |                           |                       |              |  |  |  |  |

| Bit0:     | PINRSF: HV                                                           | V Pin Reset  | Flag.        | _                        |                         |                           |                       |              |  |  |  |  |

|           | 0: Source of                                                         |              |              |                          |                         |                           |                       |              |  |  |  |  |

|           | 1: Source of                                                         | last reset w | /as RST pir  | า.                       |                         |                           |                       |              |  |  |  |  |

|           |                                                                      | 4            |              |                          |                         |                           | la alla at c a f      | 1            |  |  |  |  |

|           | or bits that ac                                                      |              |              |                          |                         |                           |                       | •            |  |  |  |  |

|           | ad-modify-wi<br>BRSF, C0RSE                                          |              |              |                          | y the sourd             |                           | miy. mis a            | hhines to    |  |  |  |  |

| 5113. 031 |                                                                      | ., 3₩٢,3٢,   |              |                          |                         |                           |                       |              |  |  |  |  |

|           |                                                                      |              |              |                          |                         |                           |                       |              |  |  |  |  |

### SFR Definition 11.2. RSTSRC: Reset Source

### SFR Definition 13.1. EMI0CN: External Memory Interface Control

|     | R/W                             | R/W                                           | R/W                                                                     | R/W                                            | R/W                                | R/W    | R/W    | R/W          | Reset Value |

|-----|---------------------------------|-----------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------|------------------------------------|--------|--------|--------------|-------------|

| P   | GSEL7                           | PGSEL6                                        | PGSEL5                                                                  | PGSEL4                                         | PGSEL3                             | PGSEL2 | PGSEL1 | PGSEL0       | 0000000     |

|     | Bit7                            | Bit6                                          | Bit5                                                                    | Bit4                                           | Bit3                               | Bit2   | Bit1   | Bit0         |             |

|     |                                 |                                               |                                                                         |                                                |                                    |        |        | SFR Address: | 0xAA        |

| Bit | T<br>a<br>R<br>0<br>0<br>0<br>0 | ddress whe<br>AM.<br>x00: 0x000<br>x01: 0x010 | Page Select<br>on using an<br>0 to 0x00FF<br>0 to 0x01FF<br>00 to 0xFEF | Bits provid<br>8-bit MOV><br><del>-</del><br>F | its.<br>le the high t<br>( command |        |        |              |             |

### 15.2. Port I/O Initialization

Port I/O initialization consists of the following steps:

- Step 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- Step 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- Step 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- Step 4. Assign Port pins to desired peripherals (XBR0, XBR1).

- Step 5. Enable the Crossbar (XBARE = '1').

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pull-up, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended. To configure a Port pin for digital input, write '0' to the corresponding bit in register PnMDOUT, and write '1' to the corresponding Port latch (register Pn).

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a '1' indicates a digital input, and a '0' indicates an analog input. All pins default to digital inputs on reset.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is '0', a weak pull-up is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pull-up is turned off on an output that is driving a '0' to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to '1' enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, the Configuration Wizard utility of the Silicon Labs IDE software will determine the Port I/O pin-assignments based on the XBRn Register settings.

**Important Note:** The Crossbar must be enabled to use Ports P0, P1, P2, and P3 as standard Port I/O in output mode. These Port output drivers are disabled while the Crossbar is disabled. Port 4 always functions as standard GPIO.

| R/W   | R/W                                               | R/W           | R/W         | R/W         | R/W     | R/W   | R/W   | Reset Value |  |  |

|-------|---------------------------------------------------|---------------|-------------|-------------|---------|-------|-------|-------------|--|--|

| CP1AE |                                                   | CPOAE         | CP0E        | SYSCKE      | SMB0E   | SPIOE | URTOE | 00000000    |  |  |

| Bit7  | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0                |               |             |             |         |       |       |             |  |  |

| Biti  | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Addre OxE1 |               |             |             |         |       |       |             |  |  |

|       | UXET                                              |               |             |             |         |       |       |             |  |  |

| Bit7: | CP1AE: Cor                                        | nparator1 A   | svnchrono   | us Output E | nable   |       |       |             |  |  |

|       | 0: Asynchro                                       | •             |             | •           |         |       |       |             |  |  |

|       | 1: Asynchro                                       |               |             |             |         |       |       |             |  |  |

| Bit6: | CP1E: Com                                         | parator1 Ou   | tput Enable | Э           |         |       |       |             |  |  |

|       | 0: CP1 unav                                       | ailable at P  | ort pin.    |             |         |       |       |             |  |  |

|       | 1: CP1 route                                      | ed to Port pi | n.          |             |         |       |       |             |  |  |

| Bit5: | CP0AE: Cor                                        | nparator0 A   | synchrono   | us Output E | nable   |       |       |             |  |  |

|       | 0: Asynchro                                       |               |             |             |         |       |       |             |  |  |

|       | 1: Asynchro                                       |               |             |             |         |       |       |             |  |  |

| Bit4: | CP0E: Com                                         |               | •           | Э           |         |       |       |             |  |  |

|       | 0: CP0 unav                                       |               | •           |             |         |       |       |             |  |  |

|       | 1: CP0 route                                      |               |             |             |         |       |       |             |  |  |

| Bit3: | SYSCKE: /S                                        |               | •           |             |         |       |       |             |  |  |

|       | 0: /SYSCLK                                        |               |             |             |         |       |       |             |  |  |

| Dito  | 1: /SYSCLK                                        |               |             | oin.        |         |       |       |             |  |  |

| Bit2: | SMB0E: SM                                         |               |             |             |         |       |       |             |  |  |

|       | 0: SMBus I/                                       |               |             | ins.        |         |       |       |             |  |  |

| Bit1: | 1: SMBus I/0<br>SPI0E: SPI                        |               | Port pins.  |             |         |       |       |             |  |  |

| DILI. | 0: SPI I/O ur                                     |               | t Dort ning |             |         |       |       |             |  |  |

|       | 1: SPI I/O u                                      |               | •           |             |         |       |       |             |  |  |

| Bit0: | URTOE: UAI                                        |               | •           |             |         |       |       |             |  |  |

| Dito. | 0: UARTO I/                                       |               | •           |             |         |       |       |             |  |  |

|       | 1: UARTO T                                        |               |             |             | nd P0 5 |       |       |             |  |  |

|       |                                                   | ,             |             | F           |         |       |       |             |  |  |

|       |                                                   |               |             |             |         |       |       |             |  |  |

### SFR Definition 15.1. XBR0: Port I/O Crossbar Register 0

| R/W      | R/W                                                                                                                                                                                                                                                                                                                                                          | R/W | R/W | R/W | R/W | R/W | R/W | Reset Value |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-------------|

| Bit7     | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Ad<br>0xA                                                                                                                                                                                                                                                                                                             |     |     |     |     |     |     |             |

| Bits7–0: | 0xA4<br>Bits7–0: Output Configuration Bits for P0.7–P0.0 (respectively): ignored if corresponding bit in regis-<br>ter P0MDIN is logic 0.<br>0: Corresponding P0.n Output is open-drain.<br>1: Corresponding P0.n Output is push-pull.<br>(Note: When SDA and SCL appear on any of the Port I/O, each are open-drain regardless<br>of the value of P0MDOUT). |     |     |     |     |     |     |             |

## SFR Definition 15.7. P0SKIP: Port0 Skip

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      |      |      |      |      |      | 0000000      |

| Bit7                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      |      |      |      |      |      | 0xD4         |

| <ul> <li>Bits7–0: P0SKIP[7:0]: Port0 Crossbar Skip Enable Bits.</li> <li>These bits select Port pins to be skipped by the Crossbar Decoder. Port pins used as analog inputs (for ADC or Comparator) or used as special functions (VREF input, external oscillator circuit, CNVSTR input) should be skipped by the Crossbar.</li> <li>0: Corresponding P0.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P0.n pin is skipped by the Crossbar.</li> </ul> |      |      |      |      |      |      |      |              |

### SFR Definition 15.14. P2MDOUT: Port2 Output Mode

| R/W    | R/W                                                        | R/W                         | R/W          | R/W        | R/W           | R/W            | R/W       | Reset Value          |

|--------|------------------------------------------------------------|-----------------------------|--------------|------------|---------------|----------------|-----------|----------------------|

| Bit7   | Bit6                                                       | Bit5                        | Bit4         | Bit3       | Bit2          | Bit1           | Bit0      | SFR Address:<br>0xA6 |

| t<br>( | Output Confi<br>ter P2MDIN<br>0: Correspor<br>1: Correspor | is logic 0.<br>Iding P2.n ( | Output is op | ben-drain. | ctively): igr | nored if corre | espondinç | g bit in regis-      |

## SFR Definition 15.15. P2SKIP: Port2 Skip

| R/W      | R/W                                                                                                 | R/W                                                     | R/W                                                         | R/W                                                     | R/W                                                     | R/W                   | R/W | Reset Value |  |

|----------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|-----------------------|-----|-------------|--|

| Bit7     | Bit6                                                                                                | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address:<br>0xD6 |                                                             |                                                         |                                                         |                       |     |             |  |

| Bits7–0: | P2SKIP[7:0]:<br>These bits se<br>log inputs (fo<br>lator circuit, (<br>0: Correspor<br>1: Correspor | elect Port p<br>or ADC or C<br>CNVSTR in<br>nding P2.n  | ins to be sk<br>comparator)<br>put) should<br>pin is not sk | ipped by the<br>or used as<br>be skipped<br>ipped by th | e Crossbar<br>special fund<br>by the Cro<br>e Crossbar. | ctions (VRE<br>ssbar. |     |             |  |

. . .

.. . .

| R        | R         | R       | R        | R        | R    | R    | R    | Reset Value |

|----------|-----------|---------|----------|----------|------|------|------|-------------|

|          |           |         | Frame Nu | mber Low |      |      |      | 0000000     |

| Bit7     | Bit6      | Bit5    | Bit4     | Bit3     | Bit2 | Bit1 | Bit0 | USB Address |

|          |           |         |          |          |      |      |      | 0x0C        |

| Bits7-0: | Frame Num | ber Low |          |          |      |      |      |             |

\_\_\_\_\_

- -

-

.

# USB Register Definition 16.10. FRAMEH: USB0 Frame Number High

| R<br>-   | R<br>-                                                  | R<br>-      | R<br>- | R<br>- | R<br>Fran   | R<br>ne Number | R<br>High | Reset Value |

|----------|---------------------------------------------------------|-------------|--------|--------|-------------|----------------|-----------|-------------|

| Bit7     | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 USB Address:<br>0x0D |             |        |        |             |                |           |             |

| Bits2-0: | Unused. Rea<br>Frame Numb<br>This register              | ber High By | te     |        | ved frame r | number.        |           |             |

### 16.8. Interrupts

.....

The read-only USB0 interrupt flags are located in the USB registers shown in USB Register Definition 16.11 through USB Register Definition 16.13. The associated interrupt enable bits are located in the USB registers shown in USB Register Definition 16.14 through USB Register Definition 16.16. A USB0 interrupt is generated when any of the USB interrupt flags is set to '1'. The USB0 interrupt is enabled via the EIE1 SFR (see Section "9.3. Interrupt Handler" on page 88).

Important Note: Reading a USB interrupt flag register resets all flags in that register to '0'.

### USB Register Definition 16.16. CMIE: USB0 Common Interrupt Enable

| -<br>Bit7 | _                                         |               |              | R/W  | R/W     | R/W     | R/W     | Reset Value |  |

|-----------|-------------------------------------------|---------------|--------------|------|---------|---------|---------|-------------|--|

| Bit7      | -                                         | -             | -            | SOFE | RSTINTE | RSUINTE | SUSINTE | 00000110    |  |

| Dici      | Bit6                                      | Bit5          | Bit4         | Bit3 | Bit2    | Bit1    | Bit0    | USB Address |  |

|           |                                           |               |              |      |         |         |         | 0x0B        |  |

| Bits7–4:  | Unused. Read = 0000b; Write = don't care. |               |              |      |         |         |         |             |  |

| Bit3:     | SOFE: Start                               | of Frame Ir   | nterrupt Ena | able |         |         |         |             |  |

|           | 0: SOF inter                              | rupt disable  | d.           |      |         |         |         |             |  |

|           | 1: SOF inter                              | rupt enable   | d.           |      |         |         |         |             |  |

| Bit2:     | RSTINTE: R                                | eset Interru  | pt Enable    |      |         |         |         |             |  |

|           | 0: Reset inte                             |               |              |      |         |         |         |             |  |

|           | 1: Reset inte                             | errupt enable | ed.          |      |         |         |         |             |  |

| Bit1:     | RSUINTE: F                                | Resume Inte   | rrupt Enabl  | le   |         |         |         |             |  |

|           | 0: Resume i                               | nterrupt disa | abled.       |      |         |         |         |             |  |

|           | 1: Resume i                               | nterrupt ena  | abled.       |      |         |         |         |             |  |

| Bit0:     | SUSINTE: S                                | uspend Inte   | errupt Enab  | le   |         |         |         |             |  |

|           | 0: Suspend                                | interrupt dis | abled.       |      |         |         |         |             |  |

|           | 1: Suspend                                | interrupt en  | abled.       |      |         |         |         |             |  |

### 16.9. The Serial Interface Engine

The Serial Interface Engine (SIE) performs all low level USB protocol tasks, interrupting the processor when data has successfully been transmitted or received. When receiving data, the SIE will interrupt the processor when a complete data packet has been received; appropriate handshaking signals are automatically generated by the SIE. When transmitting data, the SIE will interrupt the processor when a complete data packet has been received; appropriate handshaking signals are automatically generated by the SIE. When transmitting data, the SIE will interrupt the processor when a complete data packet has been transmitted and the appropriate handshake signal has been received.

The SIE will not interrupt the processor when corrupted/erroneous packets are received.

### 16.10. Endpoint0

Endpoint0 is managed through the USB register E0CSR (USB Register Definition 16.17). The INDEX register must be loaded with 0x00 to access the E0CSR register.

An Endpoint0 interrupt is generated when:

- 1. A data packet (OUT or SETUP) has been received and loaded into the Endpoint0 FIFO. The OPRDY bit (E0CSR.0) is set to '1' by hardware.

- 2. An IN data packet has successfully been unloaded from the Endpoint0 FIFO and transmitted to the host; INPRDY is reset to '0' by hardware.

- 3. An IN transaction is completed (this interrupt generated during the status stage of the transaction).

- 4. Hardware sets the STSTL bit (E0CSR.2) after a control transaction ended due to a protocol violation.

- 5. Hardware sets the SUEND bit (E0CSR.4) because a control transfer ended before firmware sets the DATAEND bit (E0CSR.3).

Writing '1' to INPRDY without writing any data to the endpoint FIFO will cause a zero-length packet to be transmitted upon reception of the next IN token.

A Bulk or Interrupt pipe can be shut down (or Halted) by writing '1' to the SDSTL bit (EINCSRL.4). While SDSTL = '1', hardware will respond to all IN requests with a STALL condition. Each time hardware generates a STALL condition, an interrupt will be generated and the STSTL bit (EINCSRL.5) set to '1'. The STSTL bit must be reset to '0' by firmware.

Hardware will automatically reset INPRDY to '0' when a packet slot is open in the endpoint FIFO. Note that if double buffering is enabled for the target endpoint, it is possible for firmware to load two packets into the IN FIFO at a time. In this case, hardware will reset INPRDY to '0' immediately after firmware loads the first packet into the FIFO and sets INPRDY to '1'. An interrupt will not be generated in this case; an interrupt will only be generated when a data packet is transmitted.

When firmware writes '1' to the FCDT bit (EINCSRH.3), the data toggle for each IN packet will be toggled continuously, regardless of the handshake received from the host. This feature is typically used by Interrupt endpoints functioning as rate feedback communication for Isochronous endpoints. When FCDT = '0', the data toggle bit will only be toggled when an ACK is sent from the host in response to an IN packet.

#### 16.12.2.Endpoints1-3 IN Isochronous Mode

When the ISO bit (EINCSRH.6) is set to '1', the target endpoint operates in Isochronous (ISO) mode. Once an endpoint has been configured for ISO IN mode, the host will send one IN token (data request) per frame; the location of data within each frame may vary. Because of this, it is recommended that double buffering be enabled for ISO IN endpoints.

Hardware will automatically reset INPRDY (EINCSRL.0) to '0' when a packet slot is open in the endpoint FIFO. Note that if double buffering is enabled for the target endpoint, it is possible for firmware to load two packets into the IN FIFO at a time. In this case, hardware will reset INPRDY to '0' immediately after firmware loads the first packet into the FIFO and sets INPRDY to '1'. An interrupt will not be generated in this case; an interrupt will only be generated when a data packet is transmitted.

If there is not a data packet ready in the endpoint FIFO when USB0 receives an IN token from the host, USB0 will transmit a zero-length data packet and set the UNDRUN bit (EINCSRL.2) to '1'.

The ISO Update feature (see **Section 16.7**) can be useful in starting a double buffered ISO IN endpoint. If the host has already set up the ISO IN pipe (has begun transmitting IN tokens) when firmware writes the first data packet to the endpoint FIFO, the next IN token may arrive and the first data packet sent before firmware has written the second (double buffered) data packet to the FIFO. The ISO Update feature ensures that any data packet written to the endpoint FIFO will not be transmitted during the current frame; the packet will only be sent after a SOF signal has been received.

### USB Register Definition 16.22. EOUTCSRH: USB0 OUT Endpoint Control High Byte

| R/W<br>DBOEN | R/W         R/W         R         R         R         Reset Value           N         ISO         -         -         -         -         00000000 |            |             |              |              |             |      |              |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|--------------|--------------|-------------|------|--------------|

| Bit7         | Bit6                                                                                                                                               | Bit5       | Bit4        | Bit3         | Bit2         | Bit1        | Bit0 | USB Address: |

|              | 0x15                                                                                                                                               |            |             |              |              |             |      |              |

| Bit7:        | Bit7: DBOEN: Double-buffer Enable<br>0: Double-buffering disabled for the selected OUT endpoint.                                                   |            |             |              |              |             |      |              |

| DitC         | 1: Double-bu                                                                                                                                       | -          |             | selected O   | UT endpoir   | nt.         |      |              |

| Bit6:        | ISO: Isochro<br>This bit enab                                                                                                                      |            |             | us transfers | s on the cur | rent endpoi | nt.  |              |

|              | 0: Endpoint of                                                                                                                                     |            |             |              |              |             |      |              |

|              | 1: Endpoint configured for isochronous transfers.                                                                                                  |            |             |              |              |             |      |              |

| Bits5–0:     | Unused. Rea                                                                                                                                        | ad = 00000 | Jb; Write = | don't care.  |              |             |      |              |

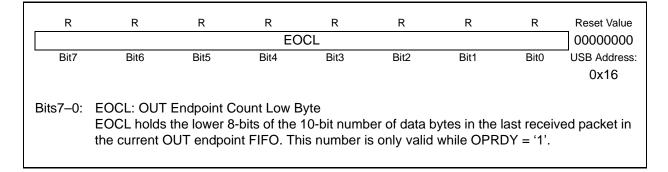

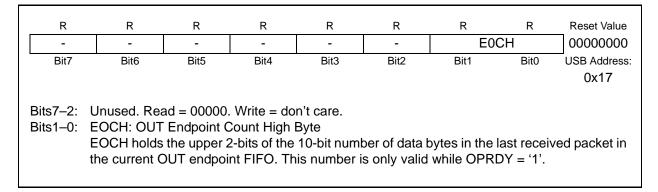

### USB Register Definition 16.23. EOUTCNTL: USB0 OUT Endpoint Count Low

### USB Register Definition 16.24. EOUTCNTH: USB0 OUT Endpoint Count High

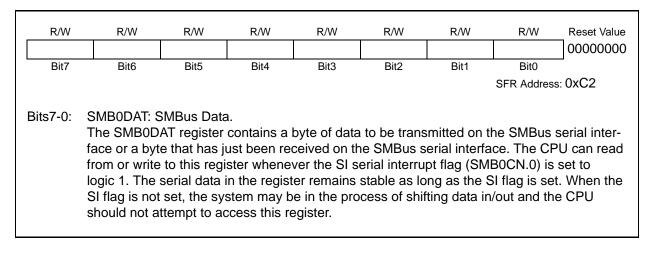

#### 17.4.3. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

### SFR Definition 17.3. SMB0DAT: SMBus Data

## 17.5. SMBus Transfer Modes

The SMBus interface may be configured to operate as master and/or slave. At any particular time, it will be operating in one of the following four modes: Master Transmitter, Master Receiver, Slave Transmitter, or Slave Receiver. The SMBus interface enters Master Mode any time a START is generated, and remains in Master Mode until it loses an arbitration or generates a STOP. An SMBus interrupt is generated at the end of all SMBus byte frames; however, note that the interrupt is generated before the ACK cycle when operating as a receiver, and after the ACK cycle when operating as a transmitter.

### 17.5.1. Master Transmitter Mode

Serial data is transmitted on SDA while the serial clock is output on SCL. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 0 (WRITE). The master then transmits one or more bytes of serial data. After each byte is transmitted, an acknowledge bit is generated by the slave. The transfer is ended when the STO bit is set and a STOP is generated. Note that the interface will switch to Master Receiver Mode if SMB0DAT is not written following a Master Transmitter interrupt. Figure 17.5 shows a typical Master Transmitter sequence. Two transmit data bytes are shown, though any number of bytes may be transmitted. Notice that the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode.

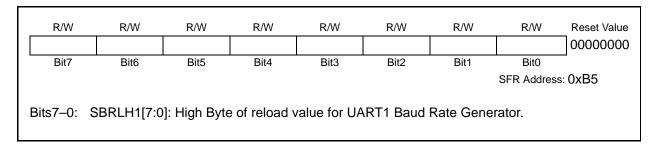

### SFR Definition 19.5. SBRLH1: UART1 Baud Rate Generator High Byte

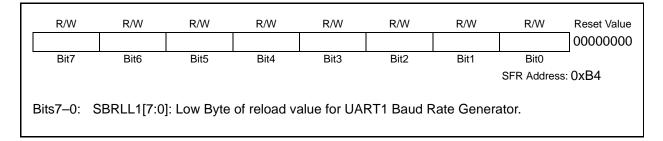

### SFR Definition 19.6. SBRLL1: UART1 Baud Rate Generator Low Byte

#### 21.2.2. 8-bit Timers with Auto-Reload

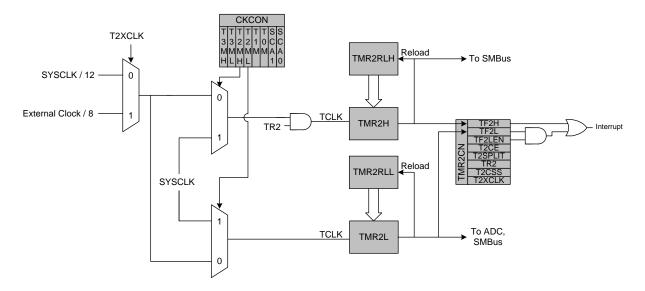

When T2SPLIT = '1' and T2CE = '0', Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 21.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |