#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 48MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 17x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-LQFP                                                         |

| Supplier Device Package    | 32-LQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f34b-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

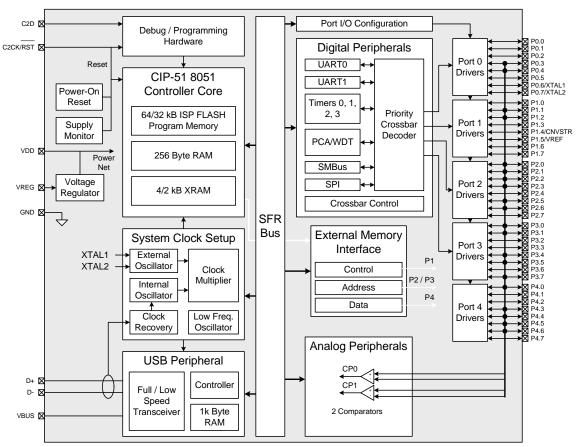

Figure 1.3. C8051F348/C Block Diagram

## Table 5.1. ADC0 Electrical Characteristics

### $V_{DD}$ = 3.0 V, VREF = 2.40 V, -40 to +85 °C unless otherwise specified

| Parameter                                               | Conditions                                              | Min         | Тур      | Max             | Units    |

|---------------------------------------------------------|---------------------------------------------------------|-------------|----------|-----------------|----------|

|                                                         | DC Accuracy                                             |             |          | I               |          |

| Resolution                                              |                                                         |             | 10       |                 | bits     |

| Integral Nonlinearity                                   |                                                         |             | ±0.5     | ±1              | LSB      |

| Differential Nonlinearity                               | Guaranteed Monotonic                                    |             | ±0.5     | ±1              | LSB      |

| Offset Error                                            |                                                         | -15         | 0        | +15             | LSB      |

| Full Scale Error                                        |                                                         | -15         | -1       | +15             | LSB      |

| Offset Temperature Coefficient                          |                                                         |             | 10       |                 | ppm/°C   |

| Dynamic Performance (10 kHz                             | z sine-wave Single-ended inpu                           | ut, 1 dB be | low Full | Scale, 2        | 00 ksps) |

| Signal-to-Noise Plus Distortion                         |                                                         | 51          | 52.5     |                 | dB       |

| Total Harmonic Distortion                               | Up to the 5 <sup>th</sup> harmonic                      |             | -67      |                 | dB       |

| Spurious-Free Dynamic Range                             |                                                         |             | 78       |                 | dB       |

|                                                         | Conversion Rate                                         |             |          |                 |          |

| SAR Conversion Clock                                    |                                                         |             |          | 3               | MHz      |

| Conversion Time in SAR Clocks                           |                                                         | 10          |          |                 | clocks   |

| Track/Hold Acquisition Time                             |                                                         | 300         |          |                 | ns       |

| Throughput Rate                                         |                                                         |             |          | 200             | ksps     |

|                                                         | Analog Inputs                                           |             |          |                 |          |

| ADC Input Voltage Range                                 | Single Ended (AIN+ – GND)<br>Differential (AIN+ – AIN–) | 0<br>–VREF  |          | VREF<br>VREF    | V<br>V   |

| Absolute Pin Voltage with respect to GND                | Single Ended or Differential                            | 0           |          | V <sub>DD</sub> | V        |

| Input Capacitance                                       |                                                         |             | 5        |                 | pF       |

|                                                         | Temperature Sensor                                      |             |          |                 |          |

| Linearity <sup>1</sup>                                  |                                                         |             | ±0.1     |                 | °C       |

| Gain                                                    |                                                         |             | 2.86     |                 | mV/°C    |

| Gain Error <sup>2</sup>                                 |                                                         |             | ±33.5    |                 | µV/⁰C    |

| Offset <sup>1</sup>                                     | (Temp = 0 °C)                                           |             | 776      |                 | mV       |

| Offset Error <sup>2</sup>                               |                                                         |             | ±8.51    |                 | mV       |

|                                                         | Power Specifications                                    | 1           |          | 1               |          |

| Power Supply Current (V <sub>DD</sub> supplied to ADC0) | Operating Mode, 200 ksps                                |             | 400      | 900             | μA       |

| Power Supply Rejection                                  |                                                         |             | ±0.3     |                 | mV/V     |

Notes:

1. Includes ADC offset, gain, and linearity variations.

2. Represents one standard deviation from the mean.

# 8. Voltage Regulator (REG0)

C8051F34x devices include a voltage regulator (REG0). When enabled, the REG0 output appears on the  $V_{DD}$  pin and can be used to power external devices. REG0 can be enabled/disabled by software using bit REGEN in register REG0CN. See Table 8.1 for REG0 electrical characteristics.

Note that the VBUS signal must be connected to the VBUS pin when using the device in a USB network. The VBUS signal should only be connected to the REGIN pin when operating the device as a bus-powered function. REG0 configuration options are shown in Figure 8.1–Figure 8.4.

#### 8.1. Regulator Mode Selection

REG0 offers a low power mode intended for use when the device is in suspend mode. In this low power mode, the REG0 output remains as specified; however the REG0 dynamic performance (response time) is degraded. See Table 8.1 for normal and low power mode supply current specifications. The REG0 mode selection is controlled via the REGMOD bit in register REG0CN.

#### 8.2. VBUS Detection

When the USB Function Controller is used (see section **Section "16. Universal Serial Bus Controller (USB0)" on page 159**), the VBUS signal should be connected to the VBUS pin. The VBSTAT bit (register REGOCN) indicates the current logic level of the VBUS signal. If enabled, a VBUS interrupt will be generated when the VBUS signal matches the polarity selected by the VBPOL bit in register REGOCN. The VBUS interrupt is level-sensitive, and has no associated interrupt pending flag. The VBUS interrupt will be active as long as the VBUS signal matches the polarity selected by VBPOL. See Table 8.1 for VBUS input parameters.

**Important Note:** When USB is selected as a reset source, a system reset will be generated when the VBUS signal matches the polarity selected by the VBPOL bit. See **Section "11. Reset Sources" on page 100** for details on selecting USB as a reset source

#### Table 8.1. Voltage Regulator Electrical Specifications

| -40 to +85 | 5 °C unless | otherwise | specified. |

|------------|-------------|-----------|------------|

|------------|-------------|-----------|------------|

| Parameter                                       | Conditions                                                  | Min | Тур      | Max       | Units |

|-------------------------------------------------|-------------------------------------------------------------|-----|----------|-----------|-------|

| Input Voltage Range <sup>1</sup>                |                                                             | 2.7 |          | 5.25      | V     |

| Output Voltage (V <sub>DD</sub> ) <sup>2</sup>  | Output Current = 1 to 100 mA                                | 3.0 | 3.3      | 3.6       | V     |

| Output Current <sup>2</sup>                     |                                                             |     |          | 100       | mA    |

| VBUS Detection Input Low Voltage                |                                                             |     |          | 1.0       | V     |

| VBUS Detection Input High Voltage               |                                                             | 3.0 |          |           | V     |

| Bias Current                                    | Normal Mode (REGMOD = '0')<br>Low Power Mode (REGMOD = '1') |     | 65<br>35 | 111<br>61 | μA    |

| Dropout Voltage (V <sub>DO</sub> ) <sup>3</sup> |                                                             |     | 1        |           | mV/mA |

#### Notes:

1. Input range specified for regulation. When an external regulator is used, should be tied to  $V_{DD}$ .

- 2. Output current is total regulator output, including any current required by the C8051F34x.

- 3. The minimum input voltage is 2.70 V or VDD +  $V_{DO}$  (max load), whichever is greater.

#### 9.2.6. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the CIP-51's resources and peripherals. The CIP-51 duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the MCU. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 9.2 lists the SFRs implemented in the CIP-51 System Controller.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the datasheet, as indicated in Table 9.3, for a detailed description of each register.

| F8 | SPI0CN | PCA0L    | PCA0H    | PCA0CPL0 | PCA0CPH0 | PCA0CPL4 | PCA0CPH4 | VDM0CN  |

|----|--------|----------|----------|----------|----------|----------|----------|---------|

| F0 | В      | P0MDIN   | P1MDIN   | P2MDIN   | P3MDIN   | P4MDIN   | EIP1     | EIP2    |

| E8 | ADC0CN | PCA0CPL1 | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 | PCA0CPL3 | PCA0CPH3 | RSTSRC  |

| E0 | ACC    | XBR0     | XBR1     | XBR2     | IT01CF   | SMOD1    | EIE1     | EIE2    |

| D8 | PCA0CN | PCA0MD   | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 | PCA0CPM3 | PCA0CPM4 | P3SKIP  |

| D0 | PSW    | REF0CN   | SCON1    | SBUF1    | P0SKIP   | P1SKIP   | P2SKIP   | USB0XCN |

| C8 | TMR2CN | REG0CN   | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H    | -        | -       |

| C0 | SMB0CN | SMB0CF   | SMB0DAT  | ADC0GTL  | ADC0GTH  | ADC0LTL  | ADC0LTH  | P4      |

| B8 | IP     | CLKMUL   | AMX0N    | AMX0P    | ADC0CF   | ADC0L    | ADC0H    | -       |

| B0 | P3     | OSCXCN   | OSCICN   | OSCICL   | SBRLL1   | SBRLH1   | FLSCL    | FLKEY   |

| A8 | IE     | CLKSEL   | EMIOCN   | -        | SBCON1   | -        | P4MDOUT  | PFE0CN  |

| A0 | P2     | SPI0CFG  | SPI0CKR  | SPI0DAT  | POMDOUT  | P1MDOUT  | P2MDOUT  | P3MDOUT |

| 98 | SCON0  | SBUF0    | CPT1CN   | CPT0CN   | CPT1MD   | CPT0MD   | CPT1MX   | CPT0MX  |

| 90 | P1     | TMR3CN   | TMR3RLL  | TMR3RLH  | TMR3L    | TMR3H    | USB0ADR  | USB0DAT |

| 88 | TCON   | TMOD     | TL0      | TL1      | TH0      | TH1      | CKCON    | PSCTL   |

| 80 | P0     | SP       | DPL      | DPH      | EMI0TC   | EMI0CF   | OSCLCN   | PCON    |

| -  | 0(8)   | 1(9)     | 2(A)     | 3(B)     | 4(C)     | 5(D)     | 6(E)     | 7(F)    |

#### Table 9.2. Special Function Register (SFR) Memory Map

(bit addressable)

## **Table 9.3. Special Function Registers**

| Register | Address | Description                               | Page |

|----------|---------|-------------------------------------------|------|

| ACC      | 0xE0    | Accumulator                               | 87   |

| ADC0CF   | 0xBC    | ADC0 Configuration                        | 50   |

| ADC0CN   | 0xE8    | ADC0 Control                              | 51   |

| ADC0GTH  | 0xC4    | ADC0 Greater-Than Compare High            | 52   |

| ADC0GTL  | 0xC3    | ADC0 Greater-Than Compare Low             | 52   |

| ADC0H    | 0xBE    | ADC0 High                                 | 50   |

| ADC0L    | 0xBD    | ADC0 Low                                  | 50   |

| ADC0LTH  | 0xC6    | ADC0 Less-Than Compare Word High          | 53   |

| ADC0LTL  | 0xC5    | ADC0 Less-Than Compare Word Low           | 53   |

| AMX0N    | 0xBA    | AMUX0 Negative Channel Select             | 49   |

| AMX0P    | 0xBB    | AMUX0 Positive Channel Select             | 48   |

| В        | 0xF0    | B Register                                | 88   |

| CKCON    | 0x8E    | Clock Control                             | 241  |

| CLKMUL   | 0xB9    | Clock Multiplier                          | 138  |

| CLKSEL   | 0xA9    | Clock Select                              | 140  |

| CPT0CN   | 0x9B    | Comparator0 Control                       | 62   |

| CPT0MD   | 0x9D    | Comparator0 Mode Selection                | 64   |

| CPT0MX   | 0x9F    | Comparator0 MUX Selection                 | 63   |

| CPT1CN   | 0x9A    | Comparator1 Control                       | 65   |

| CPT1MD   | 0x9C    | Comparator1 Mode Selection                | 67   |

| CPT1MX   | 0x9E    | Comparator1 MUX Selection                 | 66   |

| DPH      | 0x83    | Data Pointer High                         | 86   |

| DPL      | 0x82    | Data Pointer Low                          | 86   |

| EIE1     | 0xE6    | Extended Interrupt Enable 1               | 93   |

| EIE2     | 0xE7    | Extended Interrupt Enable 2               | 95   |

| EIP1     | 0xF6    | Extended Interrupt Priority 1             | 94   |

| EIP2     | 0xF7    | Extended Interrupt Priority 2             | 95   |

| EMI0CN   | 0xAA    | External Memory Interface Control         | 117  |

| EMI0CF   | 0x85    | External Memory Interface Configuration   | 118  |

| EMIOTC   | 0x84    | External Memory Interface Timing          | 123  |

| FLKEY    | 0xB7    | Flash Lock and Key                        | 112  |

| FLSCL    | 0xB6    | Flash Scale                               | 113  |

| IE       | 0xA8    | Interrupt Enable                          | 91   |

| IP       | 0xB8    | Interrupt Priority                        | 92   |

| IT01CF   | 0xE4    | INT0/INT1 Configuration                   | 96   |

| OSCICL   | 0xB3    | Internal Oscillator Calibration           | 133  |

| OSCICN   | 0xB2    | Internal Oscillator Control               | 132  |

| OSCLCN   | 0x86    | Internal Low-Frequency Oscillator Control | 134  |

| OSCXCN   | 0xB1    | External Oscillator Control               | 137  |

| P0       | 0x80    | Port 0 Latch                              | 150  |

| POMDIN   | 0xF1    | Port 0 Input Mode Configuration           | 150  |

| POMDOUT  | 0xA4    | Port 0 Output Mode Configuration          | 151  |

| POSKIP   | 0xD4    | Port 0 Skip                               | 151  |

| P1       | 0x90    | Port 1 Latch                              | 152  |

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

## 11.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pull-up and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 11.1 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### 11.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If more than 100 µs pass between rising edges on the system clock, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read '1', signifying the MCD as the reset source; otherwise, this bit reads '0'. Writing a '1' to the MCDRSF bit enables the Missing Clock Detector; writing a '0' disables it. The state of the RST pin is unaffected by this reset.

#### 11.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a '1' to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), a system reset is generated. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read '1' signifying Comparator0 as the reset source; otherwise, this bit reads '0'. The state of the RST pin is unaffected by this reset.

## 11.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in **Section "22.3. Watchdog Timer Mode" on page 264**; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to '1'. The state of the RST pin is unaffected by this reset.

#### 11.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to "1", and a MOVX write operation is attempted above address 0x7FFF (32 kB Flash devices) or 0xFBFF (64 kB Flash devices).

- A Flash read is attempted above user code space. This occurs when a MOVC operation is attempted above address 0x7FFF (32 kB Flash devices) or 0xFBFF (64 kB Flash devices).

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above 0x7FFF (32 kB Flash devices) or 0xFBFF (64 kB Flash devices).

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "12.3. Security Options" on page 109).

- A Flash Write or Erase is attempted when the V<sub>DD</sub> monitor is not enabled.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

## **Table 11.1. Reset Electrical Characteristics**

#### -40 to +85 °C unless otherwise specified.

| Parameter                                         | Conditions                                                                            | Min                   | Тур  | Max                   | Units |

|---------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| RST Output Low Voltage                            | $I_{OL}$ = 8.5 mA, $V_{DD}$ = 2.7 to 3.6 V                                            |                       |      | 0.6                   | V     |

| RST Input High Voltage                            |                                                                                       | 0.7 x V <sub>DD</sub> |      |                       | V     |

| RST Input Low Voltage                             |                                                                                       |                       |      | 0.3 x V <sub>DD</sub> |       |

| RST Input Pull-Up Current                         | RST = 0.0 V                                                                           |                       | 25   | 40                    | μA    |

| V <sub>DD</sub> POR Threshold (V <sub>RST</sub> ) |                                                                                       | 2.40                  | 2.55 | 2.70                  | V     |

| Missing Clock Detector Tim-<br>eout               | Time from last system clock ris-<br>ing edge to reset initiation                      | 100                   | 220  | 500                   | μs    |

| Reset Time Delay                                  | Delay between release of any<br>reset source and code execution<br>at location 0x0000 | 5.0                   |      |                       | μs    |

| Minimum RST Low Time to Generate a System Reset   |                                                                                       | 15                    |      |                       | μs    |

| V <sub>DD</sub> Monitor Turn-on Time              |                                                                                       | 100                   |      |                       | μs    |

| V <sub>DD</sub> Monitor Supply Current            |                                                                                       |                       | 20   | 50                    | μA    |

#### 14.4. 4x Clock Multiplier

The 4x Clock Multiplier allows a 12 MHz oscillator to generate the 48 MHz clock required for Full Speed USB communication (see **Section "16.4. USB Clock Configuration" on page 166**). A divided version of the Multiplier output can also be used as the system clock. C8051F340/1/2/3 devices can use the 48 MHz Clock Multiplier output as system clock. See Table 3.1, "Global DC Electrical Characteristics," on page 25 for system clock frequency specifications. See **Section 14.5** for details on system clock and USB clock source selection.

The 4x Clock Multiplier is configured via the CLKMUL register. The procedure for configuring and enabling the 4x Clock Multiplier is as follows:

- 1. Reset the Multiplier by writing 0x00 to register CLKMUL.

- 2. Select the Multiplier input source via the MULSEL bits.

- 3. Enable the Multiplier with the MULEN bit (CLKMUL | = 0x80).

- 4. Delay for  $>5 \ \mu s$ .

- 5. Initialize the Multiplier with the MULINIT bit (CLKMUL | = 0xC0).

- 6. Poll for MULRDY = '1'.

Important Note: When using an external oscillator as the input to the 4x Clock Multiplier, the external source must be enabled and stable before the Multiplier is initialized. See Section 14.5 for details on selecting an external oscillator source.

#### SFR Definition 14.5. CLKMUL: Clock Multiplier Control

| R/W      | R/W                                                                                           | R            | R/W       | R/W           | R/W          | R/W  | R/W  | Reset Value |  |  |  |

|----------|-----------------------------------------------------------------------------------------------|--------------|-----------|---------------|--------------|------|------|-------------|--|--|--|

| MULEN    |                                                                                               | MULRDY       | -         | -             | -            | MUL  |      | 00000000    |  |  |  |

| Bit7     | Bit6                                                                                          | Bit5         | -<br>Bit4 | -<br>Bit3     | -<br>Bit2    | Bit1 | Bit0 | SFR Address |  |  |  |

| DIL7     | DILO                                                                                          | DIID         | DIL4      | DIIJ          | DILZ         | DILI | BILU |             |  |  |  |

|          |                                                                                               |              |           |               |              |      |      | 0xB9        |  |  |  |

| Bit7:    | MULEN: Clo                                                                                    | ck Multinlie | r Enable  |               |              |      |      |             |  |  |  |

| Ditr.    | 0: Clock Multiplier disabled.                                                                 |              |           |               |              |      |      |             |  |  |  |

|          | 1: Clock Multiplier enabled.                                                                  |              |           |               |              |      |      |             |  |  |  |

| Bit6:    | MULINIT: Clock Multiplier Initialize                                                          |              |           |               |              |      |      |             |  |  |  |

| Ditto    | This bit should be a '0' when the Clock Multiplier is enabled. Once enabled, writing a '1' to |              |           |               |              |      |      |             |  |  |  |

|          | this bit will in                                                                              |              |           |               |              |      |      |             |  |  |  |

|          | is stabilized.                                                                                |              |           |               |              | 0000 |      |             |  |  |  |

| Bit5:    | MULRDY: C                                                                                     | lock Multipl | ier Readv |               |              |      |      |             |  |  |  |

|          | This read-on                                                                                  |              |           | us of the Cl  | ock Multipli | er.  |      |             |  |  |  |

|          | 0: Clock Mul                                                                                  |              |           |               |              |      |      |             |  |  |  |

|          | 1: Clock Mul                                                                                  | •            | •         |               |              |      |      |             |  |  |  |

| Bits4-2: | Unused. Rea                                                                                   |              |           | 't care.      |              |      |      |             |  |  |  |

|          | MULSEL: CI                                                                                    |              |           |               |              |      |      |             |  |  |  |

|          | These bits se                                                                                 |              |           |               | k Multiplier | ·    |      |             |  |  |  |

|          |                                                                                               |              |           |               | ·            |      |      |             |  |  |  |

|          | MU                                                                                            | LSEL         | S         | elected Clo   | ock          |      |      |             |  |  |  |

|          | (                                                                                             | 00           | In        | ternal Oscil  | ator         |      |      |             |  |  |  |

|          | (                                                                                             | 01           | Ex        | ternal Oscil  | lator        |      |      |             |  |  |  |

|          |                                                                                               | 10           | Exte      | ernal Oscilla | tor / 2      |      |      |             |  |  |  |

|          |                                                                                               | 11           |           | RESERVE       | D            |      |      |             |  |  |  |

|          |                                                                                               |              |           |               |              |      |      |             |  |  |  |

| R/W   | R/W                        | R/W           | R/W         | R/W         | R/W     | R/W   | R/W   | Reset Value  |

|-------|----------------------------|---------------|-------------|-------------|---------|-------|-------|--------------|

| CP1AE |                            | CPOAE         | CP0E        | SYSCKE      | SMB0E   | SPIOE | URTOE | 00000000     |

| Bit7  | Bit6                       | Bit5          | Bit4        | Bit3        | Bit2    | Bit1  | Bit0  | SFR Address: |

| Biti  | Bito                       | Bito          | BRT         | Bito        | DILL    | Bitt  | Dito  | 0xE1         |

|       |                            |               |             |             |         |       |       |              |

| Bit7: | CP1AE: Cor                 | nparator1 A   | svnchrono   | us Output E | nable   |       |       |              |

|       | 0: Asynchro                | •             |             | •           |         |       |       |              |

|       | 1: Asynchro                |               |             |             |         |       |       |              |

| Bit6: | CP1E: Com                  | parator1 Ou   | tput Enable | Э           |         |       |       |              |

|       | 0: CP1 unav                | ailable at P  | ort pin.    |             |         |       |       |              |

|       | 1: CP1 route               | ed to Port pi | n.          |             |         |       |       |              |

| Bit5: | CP0AE: Cor                 | nparator0 A   | synchrono   | us Output E | nable   |       |       |              |

|       | 0: Asynchro                |               |             |             |         |       |       |              |

|       | 1: Asynchro                |               |             |             |         |       |       |              |

| Bit4: | CP0E: Com                  |               | •           | Э           |         |       |       |              |

|       | 0: CP0 unav                |               | •           |             |         |       |       |              |

|       | 1: CP0 route               |               |             |             |         |       |       |              |

| Bit3: | SYSCKE: /S                 |               | •           |             |         |       |       |              |

|       | 0: /SYSCLK                 |               |             |             |         |       |       |              |

| Dito  | 1: /SYSCLK                 |               |             | oin.        |         |       |       |              |

| Bit2: | SMB0E: SM                  |               |             |             |         |       |       |              |

|       | 0: SMBus I/                |               |             | ins.        |         |       |       |              |

| Bit1: | 1: SMBus I/0<br>SPI0E: SPI |               | Port pins.  |             |         |       |       |              |

| DILI. | 0: SPI I/O ur              |               | t Dort ning |             |         |       |       |              |

|       | 1: SPI I/O u               |               | •           |             |         |       |       |              |

| Bit0: | URTOE: UAI                 |               | •           |             |         |       |       |              |

| Dito. | 0: UARTO I/                |               | •           |             |         |       |       |              |

|       | 1: UARTO T                 |               |             |             | nd P0 5 |       |       |              |

|       |                            | ,             |             | F           |         |       |       |              |

|       |                            |               |             |             |         |       |       |              |

## SFR Definition 15.1. XBR0: Port I/O Crossbar Register 0

## Table 15.1. Port I/O DC Electrical Characteristics

#### $V_{DD}$ = 2.7 to 3.6 V, -40 to +85 °C unless otherwise specified

| Parameters            | Conditions                                   | Min                   | Тур                   | Max | Units |

|-----------------------|----------------------------------------------|-----------------------|-----------------------|-----|-------|

|                       | I <sub>OH</sub> = –3 mA, Port I/O push-pull  | V <sub>DD</sub> – 0.7 |                       |     |       |

| Output High Voltage   | $I_{OH} = -10 \ \mu A$ , Port I/O push-pull  | V <sub>DD</sub> – 0.1 |                       |     | V     |

|                       | I <sub>OH</sub> = -10 mA, Port I/O push-pull |                       | V <sub>DD</sub> – 0.8 |     |       |

|                       | I <sub>OL</sub> = 8.5 mA                     |                       |                       | 0.6 |       |

| Output Low Voltage    | I <sub>OL</sub> = 10 μA                      |                       |                       | 0.1 | V     |

|                       | I <sub>OL</sub> = 25 mA                      |                       | 1.0                   |     |       |

| Input High Voltage    |                                              | 2.0                   |                       |     | V     |

| Input Low Voltage     |                                              |                       |                       | 0.8 | V     |

| Input Leakage Current | Weak Pull-up Off                             |                       |                       | ±1  |       |

| mput Leakage Current  | Weak Pull-up On, $V_{IN} = 0 V$              |                       | 25                    | 50  | μA    |

## SFR Definition 16.1. USB0XCN: USB0 Transceiver Control

| R/W      | R/W                                                                                                                                                                                                                                                                                           | R/W                                                                                                                                                                                                                                                                                         | R/W                         | R/W                           | R         |       | R        |      | R        | Reset Value          |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|-----------|-------|----------|------|----------|----------------------|--|--|--|

| PREN     |                                                                                                                                                                                                                                                                                               | SPEED                                                                                                                                                                                                                                                                                       |                             | PHYTST0                       | DFRE      | С     | Dp       |      | Dn       | 00000000             |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                                                                                          | Bit5                                                                                                                                                                                                                                                                                        | Bit4                        | Bit3                          | Bit2      | -     | Bit1     |      | Bit0     | SFR Address:<br>0xD7 |  |  |  |

| Bit7:    | PREN: Interna<br>The location of<br>0: Internal pull-<br>1: Internal pull-<br>work).                                                                                                                                                                                                          | f the pull-<br>-up resist                                                                                                                                                                                                                                                                   | up resistor<br>tor disabled | (D+ or D–) is<br>(device effe | ctively o | detad | ched fro | om t | he USB n |                      |  |  |  |

| Bit6:    | PHYEN: Physi<br>This bit enable<br>0: Transceiver                                                                                                                                                                                                                                             | PHYEN: Physical Layer Enable<br>This bit enables/disables the USB0 physical layer transceiver.<br>0: Transceiver disabled (suspend).<br>1: Transceiver enabled (normal).<br>SPEED: USB0 Speed Select                                                                                        |                             |                               |           |       |          |      |          |                      |  |  |  |

| Bit5:    | SPEED: USB0 Speed Select<br>This bit selects the USB0 speed.<br>0: USB0 operates as a Low Speed device. If enabled, the internal pull-up resistor appears<br>on the D– line.<br>1: USB0 operates as a Full Speed device. If enabled, the internal pull-up resistor appears on<br>the D+ line. |                                                                                                                                                                                                                                                                                             |                             |                               |           |       |          |      |          |                      |  |  |  |

| Bits4–3: | PHYTST1–0: F<br>These bits can                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                             |                             | USB0 transc                   | eiver.    |       |          |      |          |                      |  |  |  |

|          | PHYTST[1:0]                                                                                                                                                                                                                                                                                   | ]                                                                                                                                                                                                                                                                                           | Мо                          | de                            |           | D+    | D–       |      |          |                      |  |  |  |

|          | 00b                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                             | •                           | non-test mod                  | ,         | Х     | Х        |      |          |                      |  |  |  |

|          | 01b                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                             |                             | al '1' Forced                 |           | 1     | 0        |      |          |                      |  |  |  |

|          | 10b                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                             |                             | al '0' Forced                 |           | 0     | 1        |      |          |                      |  |  |  |

|          | 11b                                                                                                                                                                                                                                                                                           | Mode                                                                                                                                                                                                                                                                                        | 3: Single-Er                | nded '0' Ford                 | ed        | 0     | 0        |      |          |                      |  |  |  |

| Bit2:    | DFREC: Differential Receiver<br>The state of this bit indicates the current differential value present on the D+ and D– lines<br>when PHYEN = '1'.<br>0: Differential '0' signaling on the bus.<br>1: Differential '1' signaling on the bus.                                                  |                                                                                                                                                                                                                                                                                             |                             |                               |           |       |          |      |          |                      |  |  |  |

| Bit1:    | Dp: D+ Signal Status<br>This bit indicates the current logic level of the D+ pin.<br>0: D+ signal currently at logic 0.                                                                                                                                                                       |                                                                                                                                                                                                                                                                                             |                             |                               |           |       |          |      |          |                      |  |  |  |

| Bit0:    | Dn: D- Signal S<br>This bit indicate<br>0: D- signal cu                                                                                                                                                                                                                                       | <ul> <li>1: D+ signal currently at logic 0.</li> <li>1: D+ signal currently at logic 1.</li> <li>Dn: D- Signal Status</li> <li>This bit indicates the current logic level of the D- pin.</li> <li>0: D- signal currently at logic 0.</li> <li>1: D- signal currently at logic 1.</li> </ul> |                             |                               |           |       |          |      |          |                      |  |  |  |

## 16.3. USB Register Access

The USB0 controller registers listed in Table 16.2 are accessed through two SFRs: USB0 Address (USB0ADR) and USB0 Data (USB0DAT). The USB0ADR register selects which USB register is targeted

### USB Register Definition 16.14. IN1IE: USB0 IN Endpoint Interrupt Enable

| R/W                                        | R/W           | R/W           | R/W          | R/W       | R/W  | R/W  | R/W  | Reset Value  |  |

|--------------------------------------------|---------------|---------------|--------------|-----------|------|------|------|--------------|--|

| -                                          | -             | -             | -            | IN3E      | IN2E | IN1E | EP0E | 00001111     |  |

| Bit7                                       | Bit6          | Bit5          | Bit4         | Bit3      | Bit2 | Bit1 | Bit0 | USB Address: |  |

|                                            |               |               |              |           |      |      |      | 0x07         |  |

| Bits7–4:                                   | Unused. Rea   | ad = 0000b.   | Write = do   | n't care. |      |      |      |              |  |

| Bit3: IN3E: IN Endpoint 3 Interrupt Enable |               |               |              |           |      |      |      |              |  |

|                                            | 0: IN Endpoi  | nt 3 interrup | ot disabled. |           |      |      |      |              |  |

|                                            | 1: IN Endpoi  | nt 3 interru  | ot enabled.  |           |      |      |      |              |  |

| Bit2:                                      | IN2E: IN End  | dpoint 2 Inte | errupt Enab  | le        |      |      |      |              |  |

|                                            | 0: IN Endpoi  | nt 2 interrup | ot disabled. |           |      |      |      |              |  |

|                                            | 1: IN Endpoi  | nt 2 interrup | ot enabled.  |           |      |      |      |              |  |

| Bit1:                                      | IN1E: IN End  | •             | •            | le        |      |      |      |              |  |

|                                            | 0: IN Endpoi  |               |              |           |      |      |      |              |  |

|                                            | 1: IN Endpoi  |               |              |           |      |      |      |              |  |

| Bit0:                                      | EP0E: Endpo   |               | •            |           |      |      |      |              |  |

|                                            | 0: Endpoint ( |               |              |           |      |      |      |              |  |

|                                            | 1: Endpoint ( | ) interrunt e | hahlad       |           |      |      |      |              |  |

## USB Register Definition 16.15. OUT1IE: USB0 Out Endpoint Interrupt Enable

| R/W          | R/W                                    | R/W                                                                             | R/W        | R/W      | R/W   | R/W   | R/W  | Reset Value  |

|--------------|----------------------------------------|---------------------------------------------------------------------------------|------------|----------|-------|-------|------|--------------|

| -            | -                                      | -                                                                               | -          | OUT3E    | OUT2E | OUT1E | -    | 00001110     |

| Bit7         | Bit6                                   | Bit5                                                                            | Bit4       | Bit3     | Bit2  | Bit1  | Bit0 | USB Address: |

|              |                                        |                                                                                 |            |          |       |       |      | 0x09         |

| Bits7–4:     | Unused, Rea                            | ad – 0000b                                                                      | Write – do | n't care |       |       |      |              |

| Bit3:        | 0                                      |                                                                                 |            |          |       |       |      |              |

| Dito.        |                                        | OUT3E: OUT Endpoint 3 Interrupt Enable<br>0: OUT Endpoint 3 interrupt disabled. |            |          |       |       |      |              |

|              |                                        |                                                                                 |            |          |       |       |      |              |

| Bit2:        |                                        | 1: OUT Endpoint 3 interrupt enabled.                                            |            |          |       |       |      |              |

| DILZ.        |                                        | OUT2E: OUT Endpoint 2 Interrupt Enable                                          |            |          |       |       |      |              |

|              |                                        | 0: OUT Endpoint 2 interrupt disabled.                                           |            |          |       |       |      |              |

| <b>D</b> '44 |                                        | 1: OUT Endpoint 2 interrupt enabled.                                            |            |          |       |       |      |              |

| Bit1:        |                                        | OUT1E: OUT Endpoint 1 Interrupt Enable                                          |            |          |       |       |      |              |

|              |                                        | 0: OUT Endpoint 1 interrupt disabled.                                           |            |          |       |       |      |              |

|              |                                        | 1: OUT Endpoint 1 interrupt enabled.                                            |            |          |       |       |      |              |

|              | Unused. Read = 0; Write = don't' care. |                                                                                 |            |          |       |       |      |              |

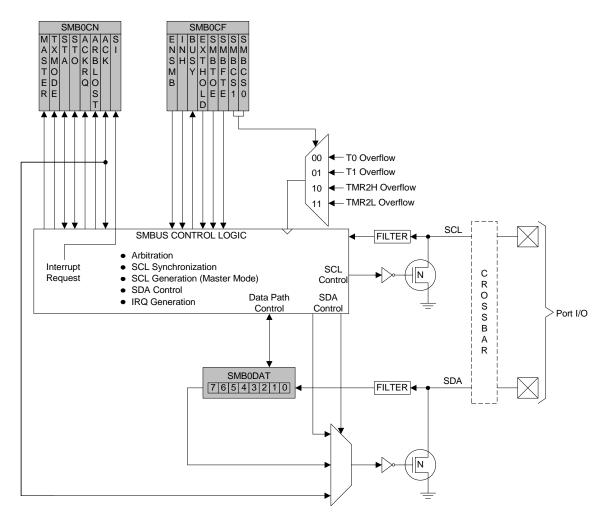

# 17. SMBus

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I2C serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/20th of the system clock as a master or slave (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

The SMBus interface may operate as a master and/or slave, and may function on a bus with multiple masters. The SMBus provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation. Three SFRs are associated with the SMBus: SMB0CF configures the SMBus; SMB0CN controls the status of the SMBus; and SMB0DAT is the data register, used for both transmitting and receiving SMBus data and slave addresses.

Figure 17.1. SMBus Block Diagram

## 17.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I2C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I2C-Bus Specification -- Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification -- Version 1.1, SBS Implementers Forum.

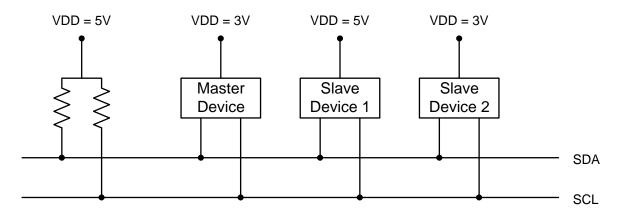

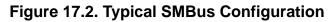

## 17.2. SMBus Configuration

Figure 17.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pull-up resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

## 17.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the Master in a system; any device who transmits a START and a slave address becomes the master for the duration of that transfer.

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7-1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Each byte that is received (by a master or slave) must be acknowledged (ACK) with a low SDA during a high SCL (see Figure 17.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

#### 17.4.3. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

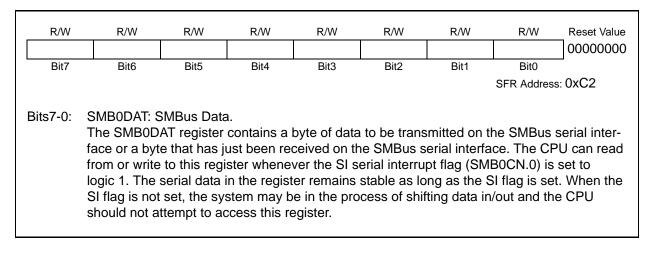

## SFR Definition 17.3. SMB0DAT: SMBus Data

## 17.5. SMBus Transfer Modes

The SMBus interface may be configured to operate as master and/or slave. At any particular time, it will be operating in one of the following four modes: Master Transmitter, Master Receiver, Slave Transmitter, or Slave Receiver. The SMBus interface enters Master Mode any time a START is generated, and remains in Master Mode until it loses an arbitration or generates a STOP. An SMBus interrupt is generated at the end of all SMBus byte frames; however, note that the interrupt is generated before the ACK cycle when operating as a receiver, and after the ACK cycle when operating as a transmitter.

#### 17.5.1. Master Transmitter Mode

Serial data is transmitted on SDA while the serial clock is output on SCL. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 0 (WRITE). The master then transmits one or more bytes of serial data. After each byte is transmitted, an acknowledge bit is generated by the slave. The transfer is ended when the STO bit is set and a STOP is generated. Note that the interface will switch to Master Receiver Mode if SMB0DAT is not written following a Master Transmitter interrupt. Figure 17.5 shows a typical Master Transmitter sequence. Two transmit data bytes are shown, though any number of bytes may be transmitted. Notice that the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode.

#### 19.1. Baud Rate Generator

The UART1 baud rate is generated by a dedicated 16-bit timer which runs from the controller's core clock (SYSCLK), and has prescaler options of 1, 4, 12, or 48. The timer and prescaler options combined allow for a wide selection of baud rates over many SYSCLK frequencies.

The baud rate generator is configured using three registers: SBCON1, SBRLH1, and SBRLL1. The UART1 Baud Rate Generator Control Register (SBCON1, SFR Definition 19.4) enables or disables the baud rate generator, and selects the prescaler value for the timer. The baud rate generator must be enabled for UART1 to function. Registers SBRLH1 and SBRLL1 contain a 16-bit reload value for the dedicated 16-bit timer. The internal timer counts up from the reload value on every clock tick. On timer overflows (0xFFFF to 0x0000), the timer is reloaded. For reliable UART operation, it is recommended that the UART baud rate is not configured for baud rates faster than SYSCLK/16. The baud rate for UART1 is defined in Equation 19.1.

Baud Rate =  $\frac{\text{SYSCLK}}{(65536 - (\text{SBRLH1:SBRLL1}))} \times \frac{1}{2} \times \frac{1}{\text{Prescaler}}$

#### Equation 19.1. UART1 Baud Rate

A quick reference for typical baud rates and system clock frequencies is given in Table 19.1.

|        | Target Baud<br>Rate (bps) | Actual Baud<br>Rate (bps) | Baud Rate<br>Error | Oscillator<br>Divide<br>Factor | SB1PS[1:0]<br>(Prescaler Bits) | Reload Value in SBRLH1:SBRLL1 |

|--------|---------------------------|---------------------------|--------------------|--------------------------------|--------------------------------|-------------------------------|

|        | 230400                    | 230769                    | 0.16%              | 52                             | 11                             | 0xFFE6                        |

| N      | 115200                    | 115385                    | 0.16%              | 104                            | 11                             | 0xFFCC                        |

| MHz    | 57600                     | 57692                     | 0.16%              | 208                            | 11                             | 0xFF98                        |

| 12     | 28800                     | 28846                     | 0.16%              | 416                            | 11                             | 0xFF30                        |

| Ш      | 14400                     | 14388                     | 0.08%              | 834                            | 11                             | 0xFE5F                        |

| SCLK   | 9600                      | 9600                      | 0.0%               | 1250                           | 11                             | 0xFD8F                        |

| SC     | 2400                      | 2400                      | 0.0%               | 5000                           | 11                             | 0xF63C                        |

| S      | 1200                      | 1200                      | 0.0%               | 10000                          | 11                             | 0xEC78                        |

|        | 230400                    | 230769                    | 0.16%              | 104                            | 11                             | 0xFFCC                        |

| 부      | 115200                    | 115385                    | 0.16%              | 208                            | 11                             | 0xFF98                        |

| MHz    | 57600                     | 57692                     | 0.16%              | 416                            | 11                             | 0xFF30                        |

| 24     | 28800                     | 28777                     | 0.08%              | 834                            | 11                             | 0xFE5F                        |

|        | 14400                     | 14406                     | 0.04%              | 1666                           | 11                             | 0xFCBF                        |

| SYSCLK | 9600                      | 9600                      | 0.0%               | 2500                           | 11                             | 0xFB1E                        |

| S<br>S | 2400                      | 2400                      | 0.0%               | 10000                          | 11                             | 0xEC78                        |

| S      | 1200                      | 1200                      | 0.0%               | 20000                          | 11                             | 0xD8F0                        |

|        | 230400                    | 230769                    | 0.16%              | 208                            | 11                             | 0xFF98                        |

| 부      | 115200                    | 115385                    | 0.16%              | 416                            | 11                             | 0xFF30                        |

| MHz    | 57600                     | 57554                     | 0.08%              | 834                            | 11                             | 0xFE5F                        |

| 48     | 28800                     | 28812                     | 0.04%              | 1666                           | 11                             | 0xFCBF                        |

|        | 14400                     | 14397                     | 0.02%              | 3334                           | 11                             | 0xF97D                        |

| SYSCLK | 9600                      | 9600                      | 0.0%               | 5000                           | 11                             | 0xF63C                        |

| ,SC    | 2400                      | 2400                      | 0.0%               | 20000                          | 11                             | 0xD8F0                        |

| ŝ      | 1200                      | 1200                      | 0.0%               | 40000                          | 11                             | 0xB1E0                        |

## Table 19.1. Baud Rate Generator Settings for Standard Baud Rates

## SFR Definition 19.2. SMOD1: UART1 Mode

| R/W      | R/W                                                                                           | R/W          | R/W          | R/W           | R/W           | R/W           | R/W          | Reset Value |

|----------|-----------------------------------------------------------------------------------------------|--------------|--------------|---------------|---------------|---------------|--------------|-------------|

| MCE1     | S1PT1                                                                                         | S1PT0        | PE1          | S1DL1         | S1DL0         | XBE1          | SBL1         | 00001100    |

| Bit7     | Bit6                                                                                          | Bit5         | Bit4         | Bit3          | Bit2          | Bit1          | Bit0         |             |

|          |                                                                                               |              |              |               |               |               | SFR Addres   | ss: 0xE5    |

|          |                                                                                               |              |              |               |               |               |              |             |

| Bit7:    | MCE1: Multi                                                                                   | •            |              |               |               |               |              |             |

|          | 0: RI will be                                                                                 |              |              |               |               |               |              |             |

|          | 1: RI will be                                                                                 | activated if | stop bit(s)  | and extra bi  | t are '1' (ex | tra bit must  | be enable    | d using     |

|          | XBE1).                                                                                        |              |              |               |               |               |              |             |

|          | Note: This fu                                                                                 |              | ot available | when hard     | vare parity   | is enabled.   |              |             |

| DIISO-D. | S1PT[1:0]: F<br>00: Odd                                                                       | anty type.   |              |               |               |               |              |             |

|          | 00. Odd<br>01: Even                                                                           |              |              |               |               |               |              |             |

|          | 10: Mark                                                                                      |              |              |               |               |               |              |             |

|          | 11: Space                                                                                     |              |              |               |               |               |              |             |

| Bit4:    | PE1: Parity                                                                                   | Enable.      |              |               |               |               |              |             |

|          | This bit activ                                                                                | vates hardw  | are parity g | eneration a   | nd checking   | g. The parit  | y type is se | elected by  |

|          | bits S1PT1-0                                                                                  |              |              | d.            |               |               |              |             |

|          | 0: Hardware                                                                                   |              |              |               |               |               |              |             |

|          | 1: Hardware                                                                                   |              |              |               |               |               |              |             |

| Bits3–2: | S1DL[1:0]: [                                                                                  |              |              |               |               |               |              |             |

|          | 00: 5-bit data                                                                                |              |              |               |               |               |              |             |

|          | 01: 6-bit data                                                                                |              |              |               |               |               |              |             |

|          | 10: 7-bit data<br>11: 8-bit data                                                              |              |              |               |               |               |              |             |

| Bit1:    |                                                                                               |              |              |               |               |               |              |             |

| Ditt.    | XBE1: Extra Bit Enable<br>When enabled, the value of TBX1 will be appended to the data field. |              |              |               |               |               |              |             |

|          | 0: Extra Bit Disabled.                                                                        |              |              |               |               |               |              |             |

|          | 1: Extra Bit B                                                                                | Enabled.     |              |               |               |               |              |             |

| Bit0:    | SBL1: Stop                                                                                    | Bit Length   |              |               |               |               |              |             |

|          | 0: Short - Ste                                                                                | •            |              |               |               |               |              |             |

|          | 1: Long - Sto                                                                                 | •            | ve for two b | oit times (da | ta length =   | 6, 7, or 8 bi | ts), or 1.5  | bit times   |

|          | (data length                                                                                  | = 5 bits).   |              |               |               |               |              |             |

|          |                                                                                               |              |              |               |               |               |              |             |

| L        |                                                                                               |              |              |               |               |               |              |             |

# C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

#### 21.2.2. 8-bit Timers with Auto-Reload

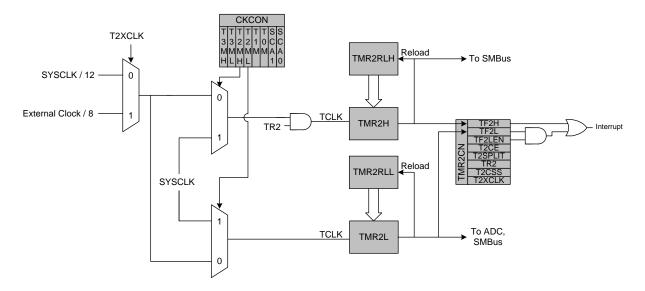

When T2SPLIT = '1' and T2CE = '0', Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 21.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled, an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 21.5. Timer 2 8-Bit Mode Block Diagram

# C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

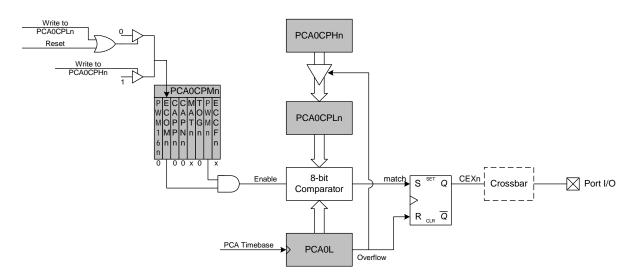

#### 22.2.5. 8-Bit Pulse Width Modulator Mode