# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                          |

| Number of I/O              | 40                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                   |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f34c-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 8. Voltage Regulator (REG0)

C8051F34x devices include a voltage regulator (REG0). When enabled, the REG0 output appears on the  $V_{DD}$  pin and can be used to power external devices. REG0 can be enabled/disabled by software using bit REGEN in register REG0CN. See Table 8.1 for REG0 electrical characteristics.

Note that the VBUS signal must be connected to the VBUS pin when using the device in a USB network. The VBUS signal should only be connected to the REGIN pin when operating the device as a bus-powered function. REG0 configuration options are shown in Figure 8.1–Figure 8.4.

#### 8.1. Regulator Mode Selection

REG0 offers a low power mode intended for use when the device is in suspend mode. In this low power mode, the REG0 output remains as specified; however the REG0 dynamic performance (response time) is degraded. See Table 8.1 for normal and low power mode supply current specifications. The REG0 mode selection is controlled via the REGMOD bit in register REG0CN.

#### 8.2. VBUS Detection

When the USB Function Controller is used (see section **Section "16. Universal Serial Bus Controller (USB0)" on page 159**), the VBUS signal should be connected to the VBUS pin. The VBSTAT bit (register REGOCN) indicates the current logic level of the VBUS signal. If enabled, a VBUS interrupt will be generated when the VBUS signal matches the polarity selected by the VBPOL bit in register REGOCN. The VBUS interrupt is level-sensitive, and has no associated interrupt pending flag. The VBUS interrupt will be active as long as the VBUS signal matches the polarity selected by VBPOL. See Table 8.1 for VBUS input parameters.

**Important Note:** When USB is selected as a reset source, a system reset will be generated when the VBUS signal matches the polarity selected by the VBPOL bit. See **Section "11. Reset Sources" on page 100** for details on selecting USB as a reset source

#### Table 8.1. Voltage Regulator Electrical Specifications

| -40 to +85 | 5 °C unless | otherwise | specified. |

|------------|-------------|-----------|------------|

|------------|-------------|-----------|------------|

| Parameter                                       | Conditions                                                  | Min | Тур      | Max       | Units |

|-------------------------------------------------|-------------------------------------------------------------|-----|----------|-----------|-------|

| Input Voltage Range <sup>1</sup>                |                                                             | 2.7 |          | 5.25      | V     |

| Output Voltage (V <sub>DD</sub> ) <sup>2</sup>  | Output Current = 1 to 100 mA                                | 3.0 | 3.3      | 3.6       | V     |

| Output Current <sup>2</sup>                     |                                                             |     |          | 100       | mA    |

| VBUS Detection Input Low Voltage                |                                                             |     |          | 1.0       | V     |

| VBUS Detection Input High Voltage               |                                                             | 3.0 |          |           | V     |

| Bias Current                                    | Normal Mode (REGMOD = '0')<br>Low Power Mode (REGMOD = '1') |     | 65<br>35 | 111<br>61 | μA    |

| Dropout Voltage (V <sub>DO</sub> ) <sup>3</sup> |                                                             |     | 1        |           | mV/mA |

#### Notes:

1. Input range specified for regulation. When an external regulator is used, should be tied to  $V_{DD}$ .

- 2. Output current is total regulator output, including any current required by the C8051F34x.

- 3. The minimum input voltage is 2.70 V or VDD +  $V_{DO}$  (max load), whichever is greater.

| R/W      | R                                                                                        | R/W         | R/W     | R/W      | R/W        | R/W          | R/W          | Reset Value  |  |

|----------|------------------------------------------------------------------------------------------|-------------|---------|----------|------------|--------------|--------------|--------------|--|

| REGDIS   |                                                                                          | VBPOL       | REGMOD  | Reserved | Reserved   | Reserved     | Reserved     |              |  |

| Bit7     | Bit6                                                                                     | Bit5        | Bit4    | Bit3     | Bit2       | Bit1         | Bit0         | SFR Address: |  |

|          |                                                                                          |             |         |          |            |              |              | 0xC9         |  |

| Bit7:    | REGDIS: Vo<br>0: Voltage R<br>1: Voltage R                                               | egulator En | abled.  | е.       |            |              |              |              |  |

| Bit6:    | VBSTAT: VB                                                                               | US Signal   | Status. |          |            |              |              |              |  |

|          | 0: VBUS sig                                                                              |             |         |          |            |              | x).          |              |  |

| <b>D</b> | 1: VBUS sig                                                                              |             | •••     |          | hed to USB | network).    |              |              |  |

| Bit5:    | VBPOL: VBU                                                                               |             |         |          |            |              |              |              |  |

|          | This bit select                                                                          |             |         |          |            |              |              |              |  |

|          | 0: VBUS inte<br>1: VBUS inte                                                             |             |         |          |            |              |              |              |  |

| Bit4:    | REGMOD: V                                                                                | •           |         | -        |            |              |              |              |  |

| DII4.    | This bit sele                                                                            |             |         |          | /hen REGM  | 10D is set t | o '1' the vo | ltade redu-  |  |

|          |                                                                                          |             |         |          |            | 100 13 301 1 |              | nage regu    |  |

|          | lator operates in low power (suspend) mode.<br>0: USB0 Voltage Regulator in normal mode. |             |         |          |            |              |              |              |  |

|          | 1: USB0 Voltage Regulator in low power mode.                                             |             |         |          |            |              |              |              |  |

| Bits3-0: | Bits3–0: Reserved. Read = 0000b. Must Write = 0000b.                                     |             |         |          |            |              |              |              |  |

|          |                                                                                          |             |         |          |            |              |              |              |  |

|          |                                                                                          |             |         |          |            |              |              |              |  |

#### SFR Definition 8.1. REG0CN: Voltage Regulator Control

| Table 9.1. CIP-51 Instruction Set Summary ( | (Continued) |

|---------------------------------------------|-------------|

|---------------------------------------------|-------------|

| Mnemonic                            | Mnemonic Description                       |   |   |  |

|-------------------------------------|--------------------------------------------|---|---|--|

| ORL A, #data                        | OR immediate to A                          | 2 | 2 |  |

| ORL direct, A                       | OR A to direct byte                        | 2 | 2 |  |

| ORL direct, #data                   | OR immediate to direct byte                | 3 | 3 |  |

| XRL A, Rn                           | Exclusive-OR Register to A                 | 1 | 1 |  |

| XRL A, direct                       | Exclusive-OR direct byte to A              | 2 | 2 |  |

| XRL A, @Ri                          | Exclusive-OR indirect RAM to A             | 1 | 2 |  |

| XRL A, #data                        | Exclusive-OR immediate to A                | 2 | 2 |  |

| XRL direct, A                       | Exclusive-OR A to direct byte              | 2 | 2 |  |

| XRL direct, #data                   | Exclusive-OR immediate to direct byte      | 3 | 3 |  |

| CLR A                               | Clear A                                    | 1 | 1 |  |

| CPL A                               | Complement A                               | 1 | 1 |  |

| RL A                                | Rotate A left                              | 1 | 1 |  |

| RLC A                               | Rotate A left through Carry                | 1 | 1 |  |

| RR A                                | Rotate A right                             | 1 | 1 |  |

| RRC A                               | Rotate A right through Carry               | 1 | 1 |  |

| SWAP A                              | Swap nibbles of A                          | 1 | 1 |  |

| -                                   | Data Transfer                              |   |   |  |

| MOV A, Rn                           | Move Register to A                         | 1 | 1 |  |

| MOV A, direct                       | Move direct byte to A                      | 2 | 2 |  |

| MOV A, @Ri                          | Move indirect RAM to A                     | 1 | 2 |  |

| MOV A, #data                        | Move immediate to A                        | 2 | 2 |  |

| MOV Rn, A                           | Move A to Register                         | 1 | 1 |  |

| MOV Rn, direct                      | Move direct byte to Register               | 2 | 2 |  |

| MOV Rn, #data                       | Move immediate to Register                 | 2 | 2 |  |

| MOV direct, A                       | Move A to direct byte                      | 2 | 2 |  |

| MOV direct, Rn                      | Move Register to direct byte               | 2 | 2 |  |

| MOV direct, direct                  | Move direct byte to direct byte            | 3 | 3 |  |

| MOV direct, @Ri                     | Move indirect RAM to direct byte           | 2 | 2 |  |

| MOV direct, @rti                    | Move immediate to direct byte              | 3 | 3 |  |

| MOV @Ri, A                          | Move A to indirect RAM                     | 1 | 2 |  |

| MOV @Ri, A<br>MOV @Ri, direct       | Move direct byte to indirect RAM           | 2 | 2 |  |

| MOV @Ri, #data                      | Move immediate to indirect RAM             | 2 | 2 |  |

| MOV @RI, #data<br>MOV DPTR, #data16 | Load DPTR with 16-bit constant             | 3 | 3 |  |

| MOVC A, @A+DPTR                     | Move code byte relative DPTR to A          | 1 | 3 |  |

| MOVC A, @A+DFTR<br>MOVC A, @A+PC    | Move code byte relative DFTR to A          | 1 | 3 |  |

|                                     |                                            |   |   |  |

| MOVX A, @Ri                         | Move external data (8-bit address) to A    | 1 | 3 |  |

| MOVX @Ri, A                         | Move A to external data (8-bit address)    | 1 | 3 |  |

| MOVX A, @DPTR                       | Move external data (16-bit address) to A   | 1 | 3 |  |

| MOVX @DPTR, A                       | Move A to external data (16-bit address)   | 1 | 3 |  |

| PUSH direct                         | Push direct byte onto stack                | 2 | 2 |  |

| POP direct                          | Pop direct byte from stack                 | 2 | 2 |  |

| XCH A, Rn                           | Exchange Register with A                   | 1 | 1 |  |

| XCH A, direct                       | Exchange direct byte with A                | 2 | 2 |  |

| XCH A, @Ri                          | Exchange indirect RAM with A               | 1 | 2 |  |

| XCHD A, @Ri                         | Exchange low nibble of indirect RAM with A | 1 | 2 |  |

### **Table 9.3. Special Function Registers**

| Register | Address | Description                               | Page |

|----------|---------|-------------------------------------------|------|

| ACC      | 0xE0    | Accumulator                               | 87   |

| ADC0CF   | 0xBC    | ADC0 Configuration                        | 50   |

| ADC0CN   | 0xE8    | ADC0 Control                              | 51   |

| ADC0GTH  | 0xC4    | ADC0 Greater-Than Compare High            | 52   |

| ADC0GTL  | 0xC3    | ADC0 Greater-Than Compare Low             | 52   |

| ADC0H    | 0xBE    | ADC0 High                                 | 50   |

| ADC0L    | 0xBD    | ADC0 Low                                  | 50   |

| ADC0LTH  | 0xC6    | ADC0 Less-Than Compare Word High          | 53   |

| ADC0LTL  | 0xC5    | ADC0 Less-Than Compare Word Low           | 53   |

| AMX0N    | 0xBA    | AMUX0 Negative Channel Select             | 49   |

| AMX0P    | 0xBB    | AMUX0 Positive Channel Select             | 48   |

| В        | 0xF0    | B Register                                | 88   |

| CKCON    | 0x8E    | Clock Control                             | 241  |

| CLKMUL   | 0xB9    | Clock Multiplier                          | 138  |

| CLKSEL   | 0xA9    | Clock Select                              | 140  |

| CPT0CN   | 0x9B    | Comparator0 Control                       | 62   |

| CPT0MD   | 0x9D    | Comparator0 Mode Selection                | 64   |

| CPT0MX   | 0x9F    | Comparator0 MUX Selection                 | 63   |

| CPT1CN   | 0x9A    | Comparator1 Control                       | 65   |

| CPT1MD   | 0x9C    | Comparator1 Mode Selection                | 67   |

| CPT1MX   | 0x9E    | Comparator1 MUX Selection                 | 66   |

| DPH      | 0x83    | Data Pointer High                         | 86   |

| DPL      | 0x82    | Data Pointer Low                          | 86   |

| EIE1     | 0xE6    | Extended Interrupt Enable 1               | 93   |

| EIE2     | 0xE7    | Extended Interrupt Enable 2               | 95   |

| EIP1     | 0xF6    | Extended Interrupt Priority 1             | 94   |

| EIP2     | 0xF7    | Extended Interrupt Priority 2             | 95   |

| EMI0CN   | 0xAA    | External Memory Interface Control         | 117  |

| EMI0CF   | 0x85    | External Memory Interface Configuration   | 118  |

| EMIOTC   | 0x84    | External Memory Interface Timing          | 123  |

| FLKEY    | 0xB7    | Flash Lock and Key                        | 112  |

| FLSCL    | 0xB6    | Flash Scale                               | 113  |

| IE       | 0xA8    | Interrupt Enable                          | 91   |

| IP       | 0xB8    | Interrupt Priority                        | 92   |

| IT01CF   | 0xE4    | INT0/INT1 Configuration                   | 96   |

| OSCICL   | 0xB3    | Internal Oscillator Calibration           | 133  |

| OSCICN   | 0xB2    | Internal Oscillator Control               | 132  |

| OSCLCN   | 0x86    | Internal Low-Frequency Oscillator Control | 134  |

| OSCXCN   | 0xB1    | External Oscillator Control               | 137  |

| P0       | 0x80    | Port 0 Latch                              | 150  |

| POMDIN   | 0xF1    | Port 0 Input Mode Configuration           | 150  |

| POMDOUT  | 0xA4    | Port 0 Output Mode Configuration          | 151  |

| POSKIP   | 0xD4    | Port 0 Skip                               | 151  |

| P1       | 0x90    | Port 1 Latch                              | 152  |

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

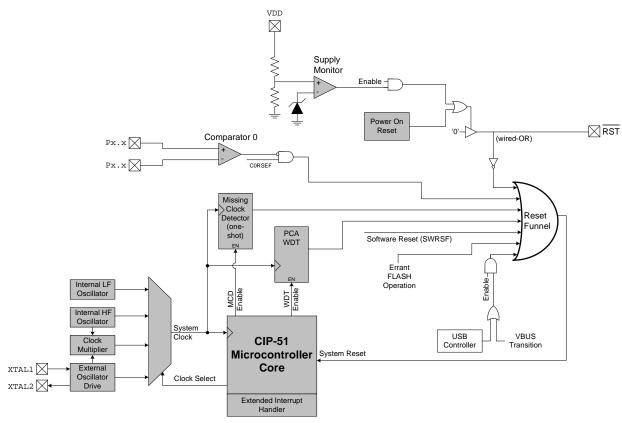

### 11. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pull-ups are enabled during and after the reset. For  $V_{DD}$  Monitor and Power-On Resets, the RST pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. Refer to **Section "14. Oscillators" on page 131** for information on selecting and configuring the system clock source. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source (**Section "22.3. Watchdog Timer Mode" on page 264** details the use of the Watchdog Timer). Program execution begins at location 0x0000.

Figure 11.1. Reset Sources

| Parameter        | Conditions             | Min    | Тур  | Max | Units       |

|------------------|------------------------|--------|------|-----|-------------|

| Flash Size       | C8051F340/2/4/6/A/C/D* | 65536* |      |     | Bytes       |

|                  | C8051F341/3/5/7/8/9/B  | 32768  |      |     | Bytes       |

| Endurance        |                        | 20k    | 100k |     | Erase/Write |

| Erase Cycle Time | 25 MHz System Clock    | 10     | 15   | 20  | ms          |

| Write Cycle Time | 25 MHz System Clock    | 40     | 55   | 70  | μs          |

#### Table 12.1. Flash Electrical Characteristics

\*Note: 1024 bytes at location 0xFC00 to 0xFFFF are reserved.

#### 12.2. Non-Volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note: MOVX read instructions always target XRAM.

#### 12.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to '1' before software can modify the Flash memory; both PSWE and PSEE must be set to '1' before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. The Flash security mechanism allows the user to lock n 512-byte Flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where n is the 1's complement number represented by the Security Lock Byte. Note that the page containing the Flash Security Lock Byte is also locked when any other Flash pages are locked. See example below.

| Security Lock Byte: | 1111101b                                                                                   |

|---------------------|--------------------------------------------------------------------------------------------|

| 1's Complement:     | 0000010b                                                                                   |

| Flash pages locked: | 3 (2 + Flash Lock Byte Page)                                                               |

|                     | First two pages of Flash: 0x0000 to 0x03FF                                                 |

| Addresses locked:   | Flash Lock Byte Page: (0xFA00 to 0xFBFF for 64k devices; 0x7E00 to 0x7FFF for 32k devices) |

| R/W                        | R/W                                                                                                                                                                                                                            | R/W                                                                                                                                                                                         | R/W                                                                                                                                                                  | R/W                                                                                                                                                   | R/W                                                                         | R/W                                                                   | R/W                                                                | Reset Value                                   |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------|

| -                          | -                                                                                                                                                                                                                              | -                                                                                                                                                                                           | -                                                                                                                                                                    | -                                                                                                                                                     | Reserved                                                                    | PSEE                                                                  | PSWE                                                               | 00000000                                      |

| Bit7                       | Bit6                                                                                                                                                                                                                           | Bit5                                                                                                                                                                                        | Bit4                                                                                                                                                                 | Bit3                                                                                                                                                  | Bit2                                                                        | Bit1                                                                  | Bit0                                                               | SFR Address:                                  |

|                            |                                                                                                                                                                                                                                |                                                                                                                                                                                             |                                                                                                                                                                      |                                                                                                                                                       |                                                                             |                                                                       |                                                                    | 0x8F                                          |

| Bits7–3:<br>Bit2:<br>Bit1: | Unused: Rea<br>Reserved. R<br>PSEE: Progr<br>Setting this b<br>to be erased<br>Flash memo<br>tion address<br>0: Flash prog<br>1: Flash prog<br>Setting this b<br>write instruct<br>0: Writes to F<br>1: Writes to F<br>memory. | ead = 0b. N<br>ram Store E<br>bit (in combi<br>. If this bit is<br>ry using the<br>ed by the N<br>gram memo<br>gram memo<br>gram Store N<br>bit allows we<br>cion. The Fla<br>Flash program | Aust Write =<br>rase Enabl<br>nation with<br>s logic 1 an<br>MOVX instru-<br>ory erasure<br>ory erasure<br>Vrite Enabl<br>riting a byte<br>ash locatior<br>am memory | = 0b.<br>e<br>PSWE) allo<br>d Flash writ<br>truction will<br>ction. The v<br>disabled.<br>enabled.<br>e<br>of data to f<br>a should be<br>v disabled. | tes are enab<br>erase the e<br>value of the<br>the Flash pro<br>erased befo | oled (PSWE<br>ntire page<br>data byte w<br>ogram men<br>ore writing o | is logic 1)<br>that contair<br>vritten does<br>nory using<br>data. | , a write to<br>as the loca-<br>a not matter. |

### SFR Definition 12.2. FLKEY: Flash Lock and Key

| R/W     | R/W                                                                                                                                                                                                                          | R/W                                                                                                                                                 | R/W                                                                                                                                                       | R/W                                                                                                                | R/W                                                                              | R/W                                            | R/W                                 | Reset Value                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------|---------------------------------------------|

| Bit7    | Bit6                                                                                                                                                                                                                         | Bit5                                                                                                                                                | Bit4                                                                                                                                                      | Bit3                                                                                                               | Bit2                                                                             | Bit1                                           | Bit0                                | SFR Address:<br>0xB7                        |

| Bits-0: | FLKEY: Flas<br>Write:<br>This register<br>remains lock<br>timing of the<br>must be writt<br>system reset<br>codes have b<br>Read:<br>When read, b<br>00: Flash is w<br>01: The first<br>10: Flash is with<br>11: Flash write | must be w<br>ed until this<br>writes does<br>en for each<br>if the wron<br>been written<br>bits 1-0 ind<br>write/erase<br>key code h<br>unlocked (v | ritten to before<br>seregister is<br>a not matter,<br>a Flash write<br>and codes are<br>an correctly.<br>acate the cu<br>locked.<br>as been writes/erases | ore Flash w<br>written to w<br>as long as<br>or erase c<br>written or<br>rrent Flash<br>tten (0xA5)<br>s allowed). | vith the follow<br>the codes a<br>operation. Fla<br>if a Flash op<br>lock state. | wing key coo<br>re written in<br>ash will be l | des: 0xA5<br>order. Th<br>locked un | 5, 0xF1. The<br>e key codes<br>til the next |

| R/W      | R/W                                      | R/W         | R/W       | R/W       | R/W   | R/W  | R/W         | Reset Value |  |  |  |

|----------|------------------------------------------|-------------|-----------|-----------|-------|------|-------------|-------------|--|--|--|

| EAS1     | EAS0                                     | EWR3        | EWR2      | EWR1      | EWR0  | EAH1 | EAH0        | 11111111    |  |  |  |

| Bit7     | Bit6                                     | Bit5        | Bit4      | Bit3      | Bit2  | Bit1 | Bit0        | 3           |  |  |  |

|          |                                          |             |           |           |       |      | SFR Address | 0x84        |  |  |  |

|          |                                          |             |           |           |       |      |             |             |  |  |  |

| Bits7–6: | EAS1-0: EN                               | IIF Address | Setup Tim | e Bits.   |       |      |             |             |  |  |  |

|          | 00: Address                              | setup time  | = 0 SYSCL | K cycles. |       |      |             |             |  |  |  |

|          | 01: Address setup time = 1 SYSCLK cycle. |             |           |           |       |      |             |             |  |  |  |

|          | 10: Address                              |             |           |           |       |      |             |             |  |  |  |

|          | 11: Address                              |             |           |           |       |      |             |             |  |  |  |

| Bits5–2: | EWR3 <u>–0:</u> EN                       |             |           |           |       |      |             |             |  |  |  |

|          | 0000: <u>WR</u> ar                       |             |           |           |       |      |             |             |  |  |  |

|          | 0001: <u>WR</u> ar                       |             |           |           |       |      |             |             |  |  |  |

|          | 0010: <u>WR</u> ar                       |             |           |           |       |      |             |             |  |  |  |

|          | 0011: <u>WR</u> ar                       | ·           |           |           |       |      |             |             |  |  |  |

|          | 0100: WR ar                              |             |           |           |       |      |             |             |  |  |  |

|          | 0101: WR ar                              |             |           |           |       |      |             |             |  |  |  |

|          | 0110: <u>WR</u> ar                       |             |           |           |       |      |             |             |  |  |  |

|          | 0111: <u>WR</u> ar<br>1000: WR ar        |             |           |           |       |      |             |             |  |  |  |

|          | 1000. <u>WR</u> an<br>1001: WR ar        |             |           |           |       |      |             |             |  |  |  |

|          | 1001: <u>WR</u> an<br>1010: WR ar        |             |           |           |       |      |             |             |  |  |  |

|          | 1010: <u>WR</u> an                       |             |           |           |       |      |             |             |  |  |  |

|          | 1100: WR ar                              |             |           |           |       |      |             |             |  |  |  |

|          | 1100: <u>WR</u> an                       |             |           |           |       |      |             |             |  |  |  |

|          | 1110: WR ar                              |             |           |           |       |      |             |             |  |  |  |

|          | 1111:WR and                              |             |           |           |       |      |             |             |  |  |  |

| Bits1-0: | EAH1–0: EM                               |             |           |           | 0.001 |      |             |             |  |  |  |

| 2.10. 01 | 00: Address                              |             |           |           |       |      |             |             |  |  |  |

|          | 01: Address                              |             |           |           |       |      |             |             |  |  |  |

|          | 10: Address                              |             |           |           |       |      |             |             |  |  |  |

|          | 11: Address                              |             |           |           |       |      |             |             |  |  |  |

|          |                                          |             |           | -         |       |      |             |             |  |  |  |

#### SFR Definition 13.3. EMI0TC: External Memory Timing Control

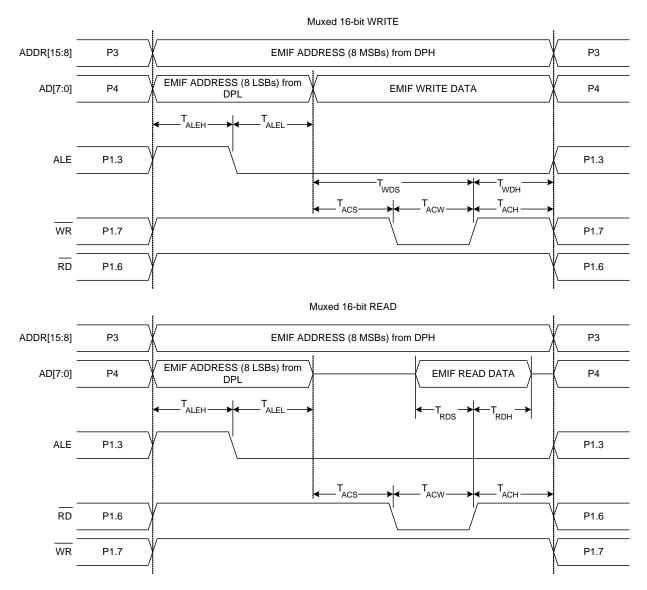

#### 13.7.2. Multiplexed Mode

#### 13.7.2.1.16-bit MOVX: EMI0CF[4:2] = '001', '010', or '011'.

Figure 13.8. Multiplexed 16-bit MOVX Timing

#### 14.4. 4x Clock Multiplier

The 4x Clock Multiplier allows a 12 MHz oscillator to generate the 48 MHz clock required for Full Speed USB communication (see **Section "16.4. USB Clock Configuration" on page 166**). A divided version of the Multiplier output can also be used as the system clock. C8051F340/1/2/3 devices can use the 48 MHz Clock Multiplier output as system clock. See Table 3.1, "Global DC Electrical Characteristics," on page 25 for system clock frequency specifications. See **Section 14.5** for details on system clock and USB clock source selection.

The 4x Clock Multiplier is configured via the CLKMUL register. The procedure for configuring and enabling the 4x Clock Multiplier is as follows:

- 1. Reset the Multiplier by writing 0x00 to register CLKMUL.

- 2. Select the Multiplier input source via the MULSEL bits.

- 3. Enable the Multiplier with the MULEN bit (CLKMUL | = 0x80).

- 4. Delay for  $>5 \ \mu s$ .

- 5. Initialize the Multiplier with the MULINIT bit (CLKMUL | = 0xC0).

- 6. Poll for MULRDY = '1'.

Important Note: When using an external oscillator as the input to the 4x Clock Multiplier, the external source must be enabled and stable before the Multiplier is initialized. See Section 14.5 for details on selecting an external oscillator source.

#### SFR Definition 14.5. CLKMUL: Clock Multiplier Control

| R/W      | R/W                                                             | R            | R/W       | R/W           | R/W          | R/W         | R/W        | Reset Value   |  |

|----------|-----------------------------------------------------------------|--------------|-----------|---------------|--------------|-------------|------------|---------------|--|

| MULEN    |                                                                 | MULRDY       | -         | -             | -            | MUL         |            | 00000000      |  |

| Bit7     | Bit6                                                            | Bit5         | -<br>Bit4 | -<br>Bit3     | -<br>Bit2    | Bit1        | Bit0       | SFR Address   |  |

| DIL7     | DILO                                                            | DIID         | DIL4      | DIIJ          | DILZ         | DILI        | BIIU       |               |  |

|          |                                                                 |              |           |               |              |             |            | 0xB9          |  |

| Bit7:    | MULEN: Clo                                                      | ck Multinlie | r Enable  |               |              |             |            |               |  |

| Ditr.    | MULEN: Clock Multiplier Enable<br>0: Clock Multiplier disabled. |              |           |               |              |             |            |               |  |

|          | 1: Clock Mul                                                    |              |           |               |              |             |            |               |  |

| Bit6:    | MULINIT: CI                                                     | •            |           |               |              |             |            |               |  |

| Ditto    | This bit shou                                                   |              |           | ock Multipli  | er is enable | ed. Once en | abled, wri | ting a '1' to |  |

|          | this bit will in                                                |              |           |               |              |             |            |               |  |

|          | is stabilized.                                                  |              |           |               |              |             |            |               |  |

| Bit5:    | MULRDY: C                                                       | lock Multipl | ier Readv |               |              |             |            |               |  |

|          | This read-on                                                    |              |           | us of the Cl  | ock Multipli | er.         |            |               |  |

|          | 0: Clock Mul                                                    |              |           |               |              |             |            |               |  |

|          | 1: Clock Mul                                                    | •            | •         |               |              |             |            |               |  |

| Bits4–2: | Unused. Rea                                                     |              |           | 't care.      |              |             |            |               |  |

|          | MULSEL: CI                                                      |              |           |               |              |             |            |               |  |

|          | These bits se                                                   |              |           |               | k Multiplie  | r.          |            |               |  |

|          |                                                                 |              |           |               |              |             |            |               |  |

|          | MU                                                              | LSEL         | S         | elected Clo   | ock          |             |            |               |  |

|          | (                                                               | 00           | In        | ternal Oscil  | ator         |             |            |               |  |

|          | (                                                               | 01           | Ex        | ternal Oscil  | lator        |             |            |               |  |

|          |                                                                 | 10           | Exte      | ernal Oscilla | tor / 2      |             |            |               |  |

|          |                                                                 | 11           |           | RESERVE       | D            |             |            |               |  |

|          |                                                                 |              |           |               |              |             |            |               |  |

| R/W       | R/W  | R/W        | R/W   | R/W  | R/W  | R/W  | R/W  | Reset Value         |

|-----------|------|------------|-------|------|------|------|------|---------------------|

| D:47      | Dito | D:+C       | Dit 4 | D:#2 | D:+0 | Ditt | Dito |                     |

| Bit7      | Bit6 | Bit5       | Bit4  | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address<br>0xF5 |

| its7–0: A |      | Configurat |       |      |      |      |      |                     |

### SFR Definition 15.21. P4MDIN: Port4 Input Mode

### SFR Definition 15.22. P4MDOUT: Port4 Output Mode

| R/W      | R/W                                           | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value          |  |  |  |

|----------|-----------------------------------------------|------|------|------|------|------|------|----------------------|--|--|--|

| Bit7     | Bit6                                          | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xAE |  |  |  |

| Bits7–0: |                                               |      |      |      |      |      |      |                      |  |  |  |

| Note: P4 | Note: P4 is only available on 48-pin devices. |      |      |      |      |      |      |                      |  |  |  |

| USB Register<br>Name | USB Register<br>Address | Description                                     | Page Number |

|----------------------|-------------------------|-------------------------------------------------|-------------|

| Name                 | Address                 | Interrupt Registers                             |             |

|                      | 0.00                    |                                                 | 470         |

| IN1INT               | 0x02                    | Endpoint0 and Endpoints1-3 IN Interrupt Flags   | 173         |

| OUT1INT              | 0x04                    | Endpoints1-3 OUT Interrupt Flags                | 173         |

| CMINT                | 0x06                    | Common USB Interrupt Flags                      | 174         |

| IN1IE                | 0x07                    | Endpoint0 and Endpoints1-3 IN Interrupt Enables | 175         |

| OUT1IE               | 0x09                    | Endpoints1-3 OUT Interrupt Enables              | 175         |

| CMIE                 | 0x0B                    | Common USB Interrupt Enables                    | 176         |

|                      |                         | Common Registers                                |             |

| FADDR                | 0x00                    | Function Address                                | 169         |

| POWER                | 0x01                    | Power Management                                | 171         |

| FRAMEL               | 0x0C                    | Frame Number Low Byte                           | 172         |

| FRAMEH               | 0x0D                    | Frame Number High Byte                          | 172         |

| INDEX                | 0x0E                    | Endpoint Index Selection                        | 165         |

| CLKREC               | 0x0F                    | Clock Recovery Control                          | 166         |

| FIFOn                | 0x20-0x23               | Endpoints0-3 FIFOs                              | 168         |

|                      |                         | Indexed Registers                               |             |

| E0CSR                | 0x11                    | Endpoint0 Control / Status                      | 179         |

| EINCSRL              | 0.00                    | Endpoint IN Control / Status Low Byte           | 182         |

| EINCSRH              | 0x12                    | Endpoint IN Control / Status High Byte          | 183         |

| EOUTCSRL             | 0x14                    | Endpoint OUT Control / Status Low Byte          | 185         |

| EOUTCSRH             | 0x15                    | Endpoint OUT Control / Status High Byte         | 186         |

| E0CNT                | 0x16                    | Number of Received Bytes in Endpoint0 FIFO      | 180         |

| EOUTCNTL             | 01X0                    | Endpoint OUT Packet Count Low Byte              | 186         |

| EOUTCNTH             | 0x17                    | Endpoint OUT Packet Count High Byte             | 186         |

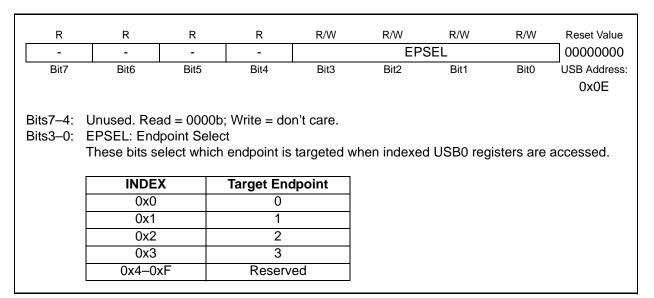

#### Table 16.2. USB0 Controller Registers

#### USB Register Definition 16.4. INDEX: USB0 Endpoint Index

| SFR Definition 17.2 | SMB0CN: SMBus Control |

|---------------------|-----------------------|

|---------------------|-----------------------|

| R     | R                                                                                                                    | R/W         | R/W          | R                         | R                | R/W         | R/W          | Reset Value        |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------|-------------|--------------|---------------------------|------------------|-------------|--------------|--------------------|--|--|--|--|

| MASTE | R TXMODE                                                                                                             | STA         | STO          | ACKRQ                     | ARBLOST          | ACK         | SI           | 00000000           |  |  |  |  |

| Bit7  | Bit6                                                                                                                 | Bit5        | Bit4         | Bit3                      | Bit2             | Bit1        | Bit0         | Bit<br>Addressable |  |  |  |  |

|       | SFR Address: 0xC0                                                                                                    |             |              |                           |                  |             |              |                    |  |  |  |  |

|       |                                                                                                                      |             |              |                           |                  |             |              |                    |  |  |  |  |

| Bit7: | MASTER: SM                                                                                                           |             |              |                           |                  |             |              |                    |  |  |  |  |

|       | This read-only                                                                                                       | •           |              |                           | s operating a    | s a maste   | r.           |                    |  |  |  |  |

|       | 0: SMBus ope                                                                                                         |             |              |                           |                  |             |              |                    |  |  |  |  |

| Bit6: |                                                                                                                      |             |              |                           |                  |             |              |                    |  |  |  |  |

| Dito. | TXMODE: SMBus Transmit Mode Indicator.<br>This read-only bit indicates when the SMBus is operating as a transmitter. |             |              |                           |                  |             |              |                    |  |  |  |  |

|       | 0: SMBus in F                                                                                                        |             |              |                           | o oporating a    | o a tranon  |              |                    |  |  |  |  |

|       | 1: SMBus in T                                                                                                        |             |              |                           |                  |             |              |                    |  |  |  |  |

| Bit5: | STA: SMBus                                                                                                           | Start Flag. |              |                           |                  |             |              |                    |  |  |  |  |

|       | Write:                                                                                                               |             |              |                           |                  |             |              |                    |  |  |  |  |

|       | 0: No Start ge                                                                                                       |             |              |                           |                  |             |              |                    |  |  |  |  |

|       | 1: When oper                                                                                                         |             |              |                           |                  |             |              |                    |  |  |  |  |

|       | is not free, the                                                                                                     |             |              |                           |                  |             |              | ,                  |  |  |  |  |

|       | STA is set by<br>next ACK cyc                                                                                        |             | as an active | e iviaster, a             | repeated STA     |             | generated    |                    |  |  |  |  |

|       | Read:                                                                                                                | 10.         |              |                           |                  |             |              |                    |  |  |  |  |

|       | 0: No Start or                                                                                                       | repeated    | Start detec  | ted.                      |                  |             |              |                    |  |  |  |  |

|       | 1: Start or rep                                                                                                      |             |              |                           |                  |             |              |                    |  |  |  |  |

| Bit4: | STO: SMBus                                                                                                           | Stop Flag   |              |                           |                  |             |              |                    |  |  |  |  |

|       | Write:                                                                                                               |             |              |                           |                  |             |              |                    |  |  |  |  |

|       | 0: No STOP o                                                                                                         |             |              |                           |                  | •••         | <i>6</i> 1   |                    |  |  |  |  |

|       | 1: Setting ST                                                                                                        | -           |              |                           |                  |             |              |                    |  |  |  |  |

|       | cycle. When t<br>and STO are                                                                                         |             |              | -                         |                  |             | -            |                    |  |  |  |  |

|       | Read:                                                                                                                | sei, a sic  |              | 115 (13115)111            |                  | by a STAI   |              | <i>л</i> п.        |  |  |  |  |

|       | 0: No Stop co                                                                                                        | ndition de  | tected.      |                           |                  |             |              |                    |  |  |  |  |

|       | 1: Stop condit                                                                                                       |             |              | ve Mode) o                | or pending (if i | in Master   | Mode).       |                    |  |  |  |  |

| Bit3: | ACKRQ: SME                                                                                                           | Bus Ackno   | wledge Re    | quest                     |                  |             | ,            |                    |  |  |  |  |

|       | This read-only                                                                                                       |             | •            |                           |                  | eived a by  | te and nee   | eds the ACK        |  |  |  |  |

| DVA   | bit to be writte                                                                                                     |             |              |                           | e value.         |             |              |                    |  |  |  |  |

| Bit2: | ARBLOST: SI                                                                                                          |             |              |                           |                  |             |              |                    |  |  |  |  |

|       | This read-only transmitter. A                                                                                        |             | •            |                           |                  |             |              | iting as a         |  |  |  |  |

| Bit1: | ACK: SMBus                                                                                                           |             |              | a slave inui              | cales a bus e    |             | uon.         |                    |  |  |  |  |

| Ditt. | This bit define                                                                                                      |             | 0 0          | level and r               | ecords incom     | ina ACK le  | evels. It sh | ould be writ       |  |  |  |  |

|       | ten each time                                                                                                        |             |              |                           |                  |             |              |                    |  |  |  |  |

|       | 0: A "not ackr                                                                                                       |             | •            |                           | ,                |             |              |                    |  |  |  |  |

|       | in Receiver M                                                                                                        | lode).      |              |                           |                  |             |              |                    |  |  |  |  |

|       | 1: An "acknow                                                                                                        | -           | s been rec   | eived (if in <sup>-</sup> | Fransmitter M    | ode) OR v   | vill be tran | smitted (if in     |  |  |  |  |

| Bito  | Receiver Mod                                                                                                         | ,           |              |                           |                  |             |              |                    |  |  |  |  |

| Bit0: | SI: SMBus Int                                                                                                        | •           | -            |                           |                  |             |              | aloored by         |  |  |  |  |

|       | This bit is set                                                                                                      | by nardwa   | are under th | ie condition              | is listed in Tal | ole 17.3. S | M MUST DE    | cleared by         |  |  |  |  |

#### 17.5.4. Slave Transmitter Mode

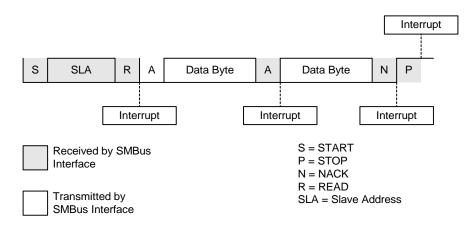

Serial data is transmitted on SDA and the clock is received on SCL. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. Upon entering Slave Transmitter Mode, an interrupt is generated and the ACKRQ bit is set. Software responds to the received slave address with an ACK, or ignores the received slave address with a NACK. If the received slave address is ignored, slave interrupts will be inhibited until a START is detected. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters Slave Transmitter Mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (Note: an error condition may be generated if SMB0DAT is written following a received NACK while in Slave Transmitter Mode). The interface exits Slave Transmitter Mode after receiving a STOP. Note that the interface will switch to Slave Receiver Mode if SMB0DAT is not written following a Slave Transmitter interrupt. Figure 17.8 shows a typical Slave Transmitter sequence. Two transmitted data bytes are shown, though any number of bytes may be transmitted. Notice that the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode.

### Figure 17.8. Typical Slave Transmitter Sequence

#### 17.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. In the table below, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. Note that the shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed but do not conform to the SMBus specification.

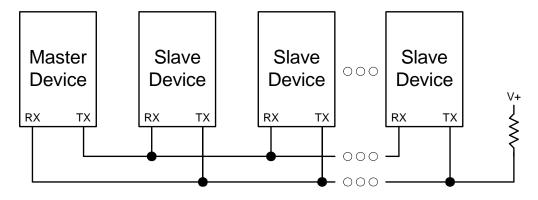

Figure 18.6. UART Multi-Processor Mode Interconnect Diagram

| R/W    | R                                                                                         | R/W            | R/W           | R/W           | R/W            | R/W         | R/W          | Reset Value        |  |  |  |  |

|--------|-------------------------------------------------------------------------------------------|----------------|---------------|---------------|----------------|-------------|--------------|--------------------|--|--|--|--|

| SOMODE | -                                                                                         | MCE0           | REN0          | TB80          | RB80           | TI0         | RI0          | 0100000            |  |  |  |  |

| Bit7   | Bit6                                                                                      | Bit5           | Bit4          | Bit3          | Bit2           | Bit1        | Bit0         | Bit<br>Addressable |  |  |  |  |

|        | SFR Address: 0x98                                                                         |                |               |               |                |             |              |                    |  |  |  |  |

| Bit7:  | SOMODE: S                                                                                 | erial Port 0   | Operation I   | Mode          |                |             |              |                    |  |  |  |  |

| Bitr.  | S0MODE: Serial Port 0 Operation Mode.<br>This bit selects the UART0 Operation Mode.       |                |               |               |                |             |              |                    |  |  |  |  |

|        | 0: 8-bit UART with Variable Baud Rate.                                                    |                |               |               |                |             |              |                    |  |  |  |  |

|        | 1: 9-bit UAR                                                                              | T with Varia   | ble Baud R    | ate.          |                |             |              |                    |  |  |  |  |

| Bit6:  | UNUSED. R                                                                                 |                |               |               |                |             |              |                    |  |  |  |  |

| Bit5:  | MCE0: Multi                                                                               | iprocessor (   | Communica     | tion Enable   | -              |             |              |                    |  |  |  |  |

|        | The function                                                                              | of this bit is | s dependen    | t on the Se   | rial Port 0 O  | peration M  | lode.        |                    |  |  |  |  |

|        | S0MODE =                                                                                  | 0: Checks f    | or valid stop | o bit.        |                |             |              |                    |  |  |  |  |

|        | 0: L                                                                                      | ogic level of  | stop bit is i | gnored.       |                |             |              |                    |  |  |  |  |

|        | 1: R                                                                                      | I0 will only   | be activated  | l if stop bit | is logic level | 1.          |              |                    |  |  |  |  |

|        | S0MODE =                                                                                  | 1: Multiproc   | essor Com     | munication    | s Enable.      |             |              |                    |  |  |  |  |

|        | 0: L                                                                                      | ogic level of  | ninth bit is  | ignored.      |                |             |              |                    |  |  |  |  |

|        | 1: R                                                                                      | I0 is set and  | d an interru  | ot is genera  | ated only whe  | en the nint | h bit is log | ic 1.              |  |  |  |  |

| Bit4:  | REN0: Rece                                                                                |                |               |               |                |             |              |                    |  |  |  |  |

|        | This bit enal                                                                             |                |               | receiver.     |                |             |              |                    |  |  |  |  |

|        | 0: UART0 re                                                                               |                |               |               |                |             |              |                    |  |  |  |  |

|        | 1: UART0 re                                                                               |                |               |               |                |             |              |                    |  |  |  |  |

|        | TB80: Ninth                                                                               |                |               |               |                |             |              |                    |  |  |  |  |

|        | The logic lev                                                                             |                |               | -             |                |             |              | ART Mode. It       |  |  |  |  |

|        | is not used i                                                                             |                |               | Set or cleare | ed by softwa   | re as requi | ired.        |                    |  |  |  |  |

| Bit2:  | RB80: Ninth                                                                               |                |               |               |                |             |              |                    |  |  |  |  |

|        | RB80 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 9th |                |               |               |                |             |              |                    |  |  |  |  |

| D'44   | data bit in M                                                                             |                | -,            |               |                |             |              |                    |  |  |  |  |

| Bit1:  | TIO: Transm                                                                               |                | 0             |               |                |             |              |                    |  |  |  |  |

|        | Set by hard                                                                               |                |               |               |                |             |              |                    |  |  |  |  |

|        | 8-bit UART I                                                                              |                | •             | •             |                |             | ,            |                    |  |  |  |  |

|        | UART0 inter                                                                               |                |               |               |                |             | to the UAP   | R I O Interrup     |  |  |  |  |

|        | service routi                                                                             |                |               | eared manu    | ally by softw  | are.        |              |                    |  |  |  |  |

| Bit0:  | RI0: Receive<br>Set to '1' by                                                             | •              | •             | of data hac   | hoon rocoiv    |             | TO (cot at t | the STOP hi        |  |  |  |  |

|        | sampling tim                                                                              |                |               |               |                |             | •            |                    |  |  |  |  |

|        | to vector to f                                                                            |                |               |               |                |             |              |                    |  |  |  |  |

|        | ware.                                                                                     |                | interrupt se  |               |                |             |              | any by soll-       |  |  |  |  |

|        | ware.                                                                                     |                |               |               |                |             |              |                    |  |  |  |  |

### SFR Definition 18.1. SCON0: Serial Port 0 Control

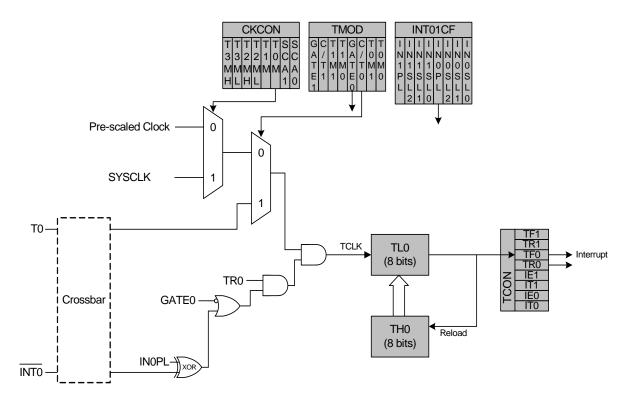

#### 21.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register INT01CF (see Section "9.3.2. External Interrupts" on page 88 for details on the external input signals INT0 and INT1).

Figure 21.2. T0 Mode 2 Block Diagram

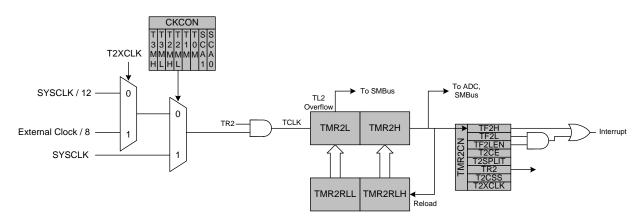

#### 21.2. Timer 2

Timer 2 is a 16-bit timer formed by two 8-bit SFRs: TMR2L (low byte) and TMR2H (high byte). Timer 2 may operate in 16-bit auto-reload mode, (split) 8-bit auto-reload mode, USB Start-of-Frame (SOF) capture mode, or Low-Frequency Oscillator (LFO) Falling Edge capture mode. The Timer 2 operation mode is defined by the T2SPLIT (TMR2CN.3), T2CE (TMR2CN.4) bits, and T2CSS (TMR2CN.1) bits.

Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 2 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 21.2.1. 16-bit Timer with Auto-Reload

When T2SPLIT = '0' and T2CE = '0', Timer 2 operates as a 16-bit timer with auto-reload. Timer 2 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 2 reload registers (TMR2RLH and TMR2RLL) is loaded into the Timer 2 register as shown in Figure 21.4, and the Timer 2 High Byte Overflow Flag (TMR2CN.7) is set. If Timer 2 interrupts are enabled, an interrupt will be generated on each Timer 2 overflow. Additionally, if Timer 2 interrupts are enabled and the TF2LEN bit is set (TMR2CN.5), an interrupt will be generated each time the lower 8 bits (TMR2L) overflow from 0xFF to 0x000.

Figure 21.4. Timer 2 16-Bit Mode Block Diagram

#### 22.2.2. Software Timer (Compare) Mode

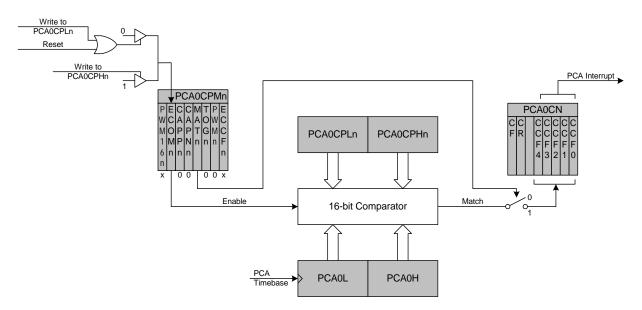

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 22.5. PCA Software Timer Mode Diagram

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**