# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 48MHz                                                           |

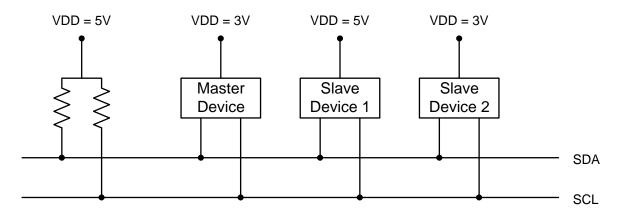

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                           |

| Number of I/O              | 40                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                    |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f34c-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1        | System Overview                                                             | 17 |

|----------|-----------------------------------------------------------------------------|----|

|          | Absolute Maximum Ratings                                                    |    |

| 3.       |                                                                             |    |

| 4.       | Pinout and Package Definitions                                              |    |

| <br>5.   | 10-Bit ADC (ADC0, C8051F340/1/2/3/4/5/6/7/A/B Only)                         |    |

| 0.       | 5.1. Analog Multiplexer                                                     |    |

|          | 5.2. Temperature Sensor                                                     |    |

|          | 5.3. Modes of Operation                                                     |    |

|          | 5.3.1. Starting a Conversion                                                |    |

|          | 5.3.2. Tracking Modes                                                       |    |

|          | 5.3.3. Settling Time Requirements                                           |    |

|          | 5.4. Programmable Window Detector                                           |    |

|          | 5.4.1. Window Detector In Single-Ended Mode                                 |    |

|          | 5.4.2. Window Detector In Differential Mode                                 |    |

| 6        | Voltage Reference (C8051F340/1/2/3/4/5/6/7/A/B Only)                        |    |

| о.<br>7. | Comparators                                                                 | 57 |

|          | Comparators<br>Voltage Regulator (REG0)                                     | 59 |

| 0.       |                                                                             |    |

|          | <ul><li>8.1. Regulator Mode Selection</li><li>8.2. VBUS Detection</li></ul> |    |

| •        |                                                                             |    |

| 9.       | CIP-51 Microcontroller                                                      |    |

|          | 9.1. Instruction Set                                                        |    |

|          | 9.1.1. Instruction and CPU Timing                                           |    |

|          | 9.1.2. MOVX Instruction and Program Memory                                  |    |

|          | 9.2. Memory Organization.                                                   |    |

|          | 9.2.1. Program Memory                                                       |    |

|          | 9.2.2. Data Memory                                                          |    |

|          | 9.2.3. General Purpose Registers                                            |    |

|          | 9.2.4. Bit Addressable Locations                                            |    |

|          | 9.2.5. Stack                                                                |    |

|          | 9.2.6. Special Function Registers                                           |    |

|          | 9.2.7. Register Descriptions                                                |    |

|          | 9.3. Interrupt Handler                                                      |    |

|          | 9.3.1. MCU Interrupt Sources and Vectors                                    |    |

|          | 9.3.2. External Interrupts                                                  |    |

|          | 9.3.3. Interrupt Priorities                                                 |    |

|          | 9.3.4. Interrupt Latency                                                    |    |

|          | 9.3.5. Interrupt Register Descriptions                                      |    |

|          | 9.4. Power Management Modes                                                 |    |

|          | 9.4.1. Idle Mode                                                            |    |

|          | 9.4.2. Stop Mode                                                            |    |

|          | Prefetch Engine                                                             |    |

| 11.      | Reset Sources1                                                              |    |

|          | 11.1.Power-On Reset 1                                                       | 01 |

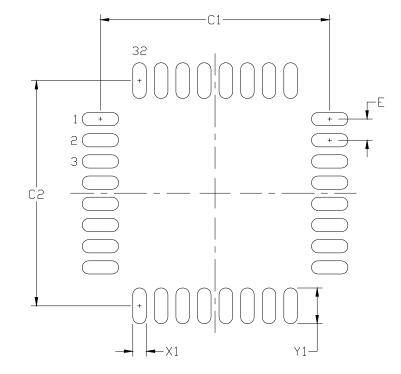

#### Figure 4.6. LQFP-32 Recommended PCB Land Pattern

#### Table 4.5. LQFP-32 PCB Land Pattern Dimensions

|       |                              |                                       | Dimensions                 |

|-------|------------------------------|---------------------------------------|----------------------------|

|       | Dimension                    | Min                                   | Max                        |

|       | C1                           | 8.40                                  | 8.50                       |

|       | C2                           | 8.40                                  | 8.50                       |

|       | E                            | 0.80                                  | BSC                        |

|       | X1                           | 0.40                                  | 0.50                       |

|       | Y1                           | 1.25                                  | 1.35                       |

| Notes | :                            |                                       |                            |

| Gener | ral:                         |                                       |                            |

| 1.    | All dimensions shown are     | in millimeters (mm) unless            | otherwise noted.           |

| 2.    | This Land Pattern Design     | is based on the IPC-7351              | guidelines.                |

| Solde | r Mask Design:               |                                       |                            |

| 3.    | All metal pads are to be no  | on-solder mask defined (N             | SMD). Clearance between    |

|       | the solder mask and the m    | ietal pad is to be 60 µm mi           | nimum, all the way around  |

|       | the pad.                     |                                       |                            |

| Stenc | il Design:                   |                                       |                            |

| 4.    | A stainless steel, laser-cut | and electro-polished sten             | cil with trapezoidal walls |

|       | should be used to assure     | •                                     | •                          |

| 5.    | The stencil thickness shou   |                                       |                            |

|       | The ratio of stencil apertur | · · ·                                 | pe 1:1 for all pads.       |

|       | Assembly:                    | •                                     |                            |

|       | A No-Clean, Type-3 solde     | r paste is recommended.               |                            |

|       | The recommended card re      | •                                     | EC/IPC J-STD-020           |

| 51    | specification for Small Boo  |                                       |                            |

|       |                              | · · · · · · · · · · · · · · · · · · · |                            |

#### SFR Definition 5.2. AMX0N: AMUX0 Negative Channel Select

| R        | R              | R              | R/W           | R/W          | R/W     | R/W               | R/W           | Reset Value |  |

|----------|----------------|----------------|---------------|--------------|---------|-------------------|---------------|-------------|--|

| -        | -              | -              | AMX0N4        | AMX0N3       | AMX0N2  | AMX0N1            | AMX0N0        | 00000000    |  |

| Bit7     | Bit7 Bit6 Bit5 |                | Bit4          | Bit3         | Bit2    | Bit1              | Bit0          | SFR Address |  |

|          |                |                |               |              |         |                   |               | 0xBA        |  |

| Bito7 5. | UNUSED. R      | ood - 000      | h: Mrito – de | n't coro     |         |                   |               |             |  |

|          | AMX0N4-0:      |                | ,             |              |         |                   |               |             |  |

| Dito+ 0. | Note that wh   |                |               |              |         | DC0 operate       | es in Sinale  | -ended      |  |

|          | mode. For al   |                |               |              |         |                   |               |             |  |

|          |                |                | 5 1           | ,            | •       |                   |               |             |  |

|          | AMX0           | N4-0           |               | Negative I   |         |                   | gative Inpu   | t           |  |

|          |                |                | (32-          | pin Packag   | je)     |                   | Package)      |             |  |

|          | 000            |                |               | P1.0         |         |                   | 2.0           |             |  |

|          | 000            |                |               | P1.1         |         |                   | 2.1           |             |  |

|          | 000            |                |               | P1.2         |         |                   | 2.2           |             |  |

|          | 000            |                |               | P1.3         |         |                   | 2.3           |             |  |

|          | 001            |                |               | P1.4         |         |                   | 2.5           |             |  |

|          | 001            |                |               | P1.5         |         |                   | 2.6           |             |  |

|          | 001            |                |               | P1.6         |         |                   | 3.0           |             |  |

|          | 001            |                |               | P1.7         |         |                   | 3.1           |             |  |

|          | 010            |                |               | P2.0         |         |                   | 3.4           |             |  |

|          | 010            |                |               | P2.1         |         |                   | 3.5           |             |  |

|          | 010            |                |               | P2.2         |         |                   | 3.7           |             |  |

|          | 010            |                |               | P2.3         |         |                   | 4.0           |             |  |

|          | 011            |                |               | P2.4         |         |                   | 4.3           |             |  |

|          | 011            |                |               | P2.5         |         |                   | 4.4           |             |  |

|          | 011            |                |               | P2.6         |         |                   | 4.5           |             |  |

|          | 011            |                |               | P2.7         |         |                   | 4.6           |             |  |

|          |                | 10000<br>10001 |               | P3.0         |         |                   | RESERVED      |             |  |

|          | 100            |                |               | P0.0         |         |                   | P0.3          |             |  |

|          | 100            |                |               | P0.1         |         |                   | P0.4<br>P1.1  |             |  |

|          | 100            |                |               | P0.4<br>P0.5 |         |                   | 1.1           |             |  |

|          | 10101 -        |                |               | ESERVED      |         |                   | T.Z<br>ERVED  |             |  |

|          | 111            |                | K             | VREF         |         |                   | REF           |             |  |

|          | 111            |                |               | ngle-Ended   | Mode) ( | or<br>SND (Single |               | de)         |  |

|          |                |                |               |              |         | שוווטו סווועופ    | -டப்பு பிலும் |             |  |

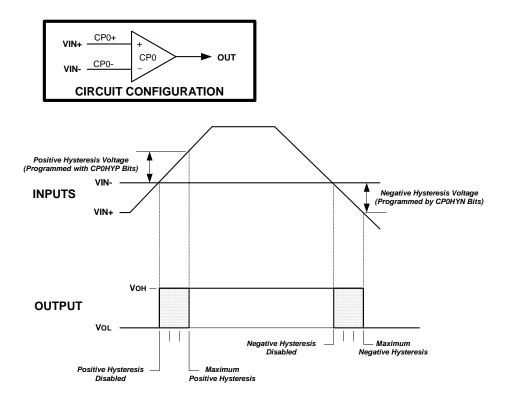

Figure 7.2. Comparator Hysteresis Plot

Comparator hysteresis is programmed using Bits3-0 in the Comparator Control Register CPTnCN (shown in SFR Definition 7.1 and SFR Definition 7.4). The amount of negative hysteresis voltage is determined by the settings of the CPnHYN bits. As shown in Figure 7.2, various levels of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPnHYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see **Section "9.3. Interrupt Handler" on page 88**.) The CPnFIF flag is set to '1' upon a Comparator falling-edge, and the CPnRIF flag is set to '1' upon the Comparator rising-edge. Once set, these bits remain set until cleared by software. The output state of the Comparator can be obtained at any time by reading the CPnOUT bit. The Comparator is enabled by setting the CPnEN bit to '1', and is disabled by clearing this bit to '0'.

| R/W       | R                            | R/W         | R/W        | R/W           | R/W            | R/W         | R/W        | Reset Value  |

|-----------|------------------------------|-------------|------------|---------------|----------------|-------------|------------|--------------|

| CP1EN     | CP1OUT                       | CP1RIF      | CP1FIF     | CP1HYP1       | CP1HYP0        | CP1HYN1     | CP1HYN0    | 00000000     |

| Bit7      | Bit6                         | Bit5        | Bit4       | Bit3          | Bit2           | Bit1        | Bit0       | SFR Address: |

|           |                              |             |            |               |                |             |            | 0x9A         |

|           |                              |             |            |               |                |             |            |              |

| Bit7:     | CP1EN: Cor                   | nparator1 E | nable Bit. |               |                |             |            |              |

|           | 0: Comparat                  | or1 Disable | d.         |               |                |             |            |              |

|           | 1: Comparat                  | or1 Enable  | d.         |               |                |             |            |              |

| Bit6:     | CP1OUT: Co                   | •           |            | ite Flag.     |                |             |            |              |

|           | 0: Voltage or                |             |            |               |                |             |            |              |

|           | 1: Voltage or                |             |            |               |                |             |            |              |

| Bit5:     | CP1RIF: Co                   |             |            |               |                |             |            |              |

|           | 0: No Compa                  |             |            |               | since this fla | ag was last | cleared.   |              |

|           | 1: Comparat                  | -           | -          |               |                |             |            |              |

| Bit4:     | CP1FIF: Cor                  |             |            |               |                |             |            |              |

|           | 0: No Compa                  |             |            |               | since this fl  | ag was las  | t cleared. |              |

|           | 1: Comparat                  |             |            |               |                | -           |            |              |

| Bits3-2:  | CP1HYP1-0                    |             |            | e Hysteresi   | s Control Bit  | S.          |            |              |

|           | 00: Positive                 |             |            |               |                |             |            |              |

|           | 01: Positive<br>10: Positive |             |            |               |                |             |            |              |

|           | 10. Positive I               |             |            |               |                |             |            |              |

| Bits1–0:  | CP1HYN1–C                    |             |            | vo Hystoros   | is Control B   | ite         |            |              |

| Dits I=0. | 00: Negative                 |             |            | ive riysteres |                |             |            |              |

|           | 01: Negative                 |             |            |               |                |             |            |              |

|           | 10: Negative                 |             |            |               |                |             |            |              |

|           | 11: Negative                 | •           |            |               |                |             |            |              |

|           |                              | ,           | _0         |               |                |             |            |              |

| [         |                              |             |            |               |                |             |            |              |

#### SFR Definition 7.4. CPT1CN: Comparator1 Control

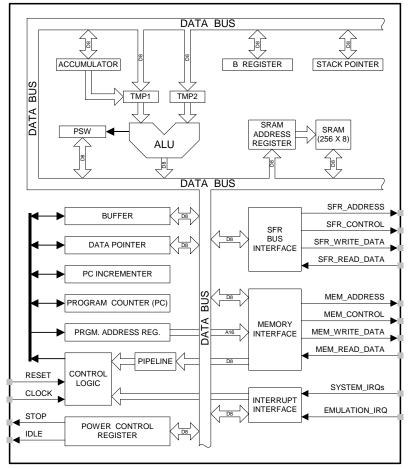

## 9. CIP-51 Microcontroller

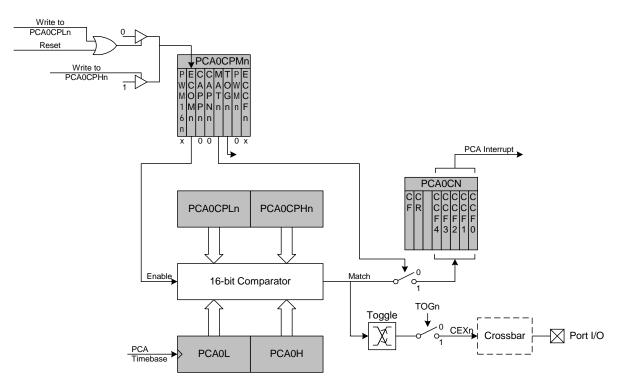

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. Included are four 16-bit counter/timers (see description in **Section 21**), an enhanced full-duplex UART (see description in **Section 18**), an Enhanced SPI (see description in **Section 20**), 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space (**Section 9.2.6**), and 25 Port I/O (see description in **Section 15**). The CIP-51 also includes on-chip debug hardware (see description in **Section 23**), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 9.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 0 to 48 MHz Clock Frequency

- 256 Bytes of Internal RAM

- 25 Port I/O

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### Figure 9.1. CIP-51 Block Diagram

| R/W   | R/W                                               | R/W           | R/W           | R/W           | R/W            | R/W           | R/W   | Reset Value         |  |  |

|-------|---------------------------------------------------|---------------|---------------|---------------|----------------|---------------|-------|---------------------|--|--|

| PT3   | PCP1                                              | PCP0          | PPCA0         | PADC0         | PWADC0         | PUSB0         | PSMB0 | 00000000            |  |  |

| Bit7  | Bit6                                              | Bit5          | Bit4          | Bit3          | Bit2           | Bit1          | Bit0  | SFR Address<br>0xF6 |  |  |

| Bit7: | PT3: Timer 3                                      |               |               |               |                |               |       |                     |  |  |

|       | This bit sets                                     |               |               |               | ot.            |               |       |                     |  |  |

|       | 0: Timer 3 in                                     | •             |               |               |                |               |       |                     |  |  |

|       | 1: Timer 3 in                                     | •             | • •           |               |                |               |       |                     |  |  |

| Bit6: | PCP1: Com                                         | · ·           | , i           |               | ontrol.        |               |       |                     |  |  |

|       | This bit sets                                     |               |               |               |                |               |       |                     |  |  |

|       | 0: CP1 inter                                      |               |               |               |                |               |       |                     |  |  |

|       | 1: CP1 inter                                      |               | • • •         |               |                |               |       |                     |  |  |

| Bit5: | PCP0: Com                                         | · ·           | , i           |               | ontrol.        |               |       |                     |  |  |

|       | This bit sets                                     | the priority  | of the CP0    | interrupt.    |                |               |       |                     |  |  |

|       | 0: CP0 interr                                     | upt set to I  | ow priority l | evel.         |                |               |       |                     |  |  |

|       | 1: CP0 inter                                      | upt set to h  | high priority | level.        |                |               |       |                     |  |  |

| Bit4: | PPCA0: Pro                                        | grammable     | Counter A     | ray (PCA0     | ) Interrupt Pr | riority Contr | ol.   |                     |  |  |

|       | This bit sets the priority of the PCA0 interrupt. |               |               |               |                |               |       |                     |  |  |

|       | 0: PCA0 inte                                      | errupt set to | low priority  | level.        |                |               |       |                     |  |  |

|       | 1: PCA0 inte                                      | errupt set to | high priorit  | y level.      |                |               |       |                     |  |  |

| Bit3: | PADC0 ADC                                         | 0 Convers     | ion Comple    | te Interrupt  | Priority Con   | trol.         |       |                     |  |  |

|       | This bit sets                                     | the priority  | of the ADC    | 0 Conversi    | on Complete    | e interrupt.  |       |                     |  |  |

|       | 0: ADC0 Co                                        | nversion Co   | omplete inte  | errupt set to | low priority   | level.        |       |                     |  |  |

|       | 1: ADC0 Co                                        | nversion Co   | omplete inte  | errupt set to | high priority  | / level.      |       |                     |  |  |

| Bit2: | PWADC0: A                                         | DC0 Windo     | ow Compara    | ator Interru  | ot Priority Co | ontrol.       |       |                     |  |  |

|       | This bit sets                                     | the priority  | of the ADC    | 0 Window      | interrupt.     |               |       |                     |  |  |

|       | 0: ADC0 Wir                                       | ndow interr   | upt set to lo | w priority le | evel.          |               |       |                     |  |  |

|       | 1: ADC0 Wir                                       | ndow interr   | upt set to hi | gh priority l | evel.          |               |       |                     |  |  |

| Bit1: | PUSB0: USE                                        | 30 Interrup   | t Priority Co | ntrol.        |                |               |       |                     |  |  |

|       | This bit sets                                     | the priority  | of the USB    | 0 interrupt.  |                |               |       |                     |  |  |

|       | 0: USB0 inte                                      | errupt set to | low priority  | level.        |                |               |       |                     |  |  |

|       | 1: USB0 inte                                      | •             |               |               |                |               |       |                     |  |  |

| Bit0: | PSMB0: SM                                         | •             | • •           |               | ntrol.         |               |       |                     |  |  |

|       | This bit sets                                     |               |               |               |                |               |       |                     |  |  |

|       | 0: SMB0 inte                                      |               |               |               |                |               |       |                     |  |  |

|       | 1: SMB0 inte                                      |               |               |               |                |               |       |                     |  |  |

#### SFR Definition 9.10. EIP1: Extended Interrupt Priority 1

#### 9.4. Power Management Modes

The CIP-51 core has two software programmable power management modes: Idle and Stop. Idle mode halts the CPU while leaving the peripherals and clocks active. In Stop mode, the CPU is halted, all interrupts, are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not affected). Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode consumes the least power. Figure 1.15 describes the Power Control Register (PCON) used to control the CIP-51's power management modes.

Although the CIP-51 has Idle and Stop modes built in (as with any standard 8051 architecture), power management of the entire MCU is better accomplished through system clock and individual peripheral management. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off the oscillators lowers power consumption considerably; however a reset is required to restart the MCU.

The internal oscillator can be placed in Suspend mode (see **Section "14. Oscillators" on page 131**). In Suspend mode, the internal oscillator is stopped until a non-idle USB event is detected, or the VBUS input signal matches the polarity selected by the VBPOL bit in register REGOCN (SFR Definition 8.1).

#### 9.4.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to **Section "11.6. PCA Watchdog Timer Reset" on page 103** for more information on the use and configuration of the WDT.

#### 9.4.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100 µsec.

## 10. Prefetch Engine

The 48 MHz versions of the C8051F34x family of devices incorporate a 2-byte prefetch engine. Because the access time of the FLASH memory is 40 ns, and the minimum instruction time is roughly 20 ns, the prefetch engine is necessary for full-speed code execution. Instructions are read from FLASH memory two bytes at a time by the prefetch engine, and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine allows instructions to be executed at full speed. When a code branch occurs, the processor may be stalled for up to two clock cycles while the next set of code bytes is retrieved from FLASH memory. The FLRT bit (FLSCL.4) determines how many clock cycles are used to read each set of two code bytes from FLASH. When operating from a system clock of 25 MHz or less, the FLRT bit should be set to '0' so that the prefetch engine takes only one clock cycle for each read. When operating with a system clock of greater than 25 MHz (up to 48 MHz), the FLRT bit should be set to '1', so that each prefetch code read lasts for two clock cycles.

| R         | R              | R/W           | R             | R          | R           | R    | R/W         | Reset Value |

|-----------|----------------|---------------|---------------|------------|-------------|------|-------------|-------------|

|           |                | PFEN          |               |            |             |      | FLBWE       | 00100000    |

| Bit7      | Bit6           | Bit5          | Bit4          | Bit3       | Bit2        | Bit1 | Bit0        | 3           |

|           |                |               |               |            |             |      | SFR Address | 0xAF        |

| Bits 7–6: | Unused. Rea    | ad = 00b; W   | /rite = Don'i | t Care     |             |      |             |             |

| Bit 5:    | PFEN: Prefe    | tch Enable    |               |            |             |      |             |             |

|           | This bit enab  | oles the pre  | fetch engine  | e.         |             |      |             |             |

|           | 0: Prefetch e  | engine is dis | abled.        |            |             |      |             |             |

|           | 1: Prefetch e  | engine is en  | abled.        |            |             |      |             |             |

| Bits 4–1: | Unused. Rea    | ad = 0000b:   | Write = Do    | on't Care  |             |      |             |             |

| Bit 0:    | FLBWE: FLA     |               |               |            |             |      |             |             |

|           | This bit allow | vs block wri  | tes to FLAS   | SH memory  | from softwa | are. |             |             |

|           | 0: Each byte   |               |               |            |             |      |             |             |

|           | 1: FLASH by    |               |               |            |             | any. |             |             |

|           | 1.1 2/(0110)   |               | ser in group  | 05 01 100. |             |      |             |             |

|           |                |               |               |            |             |      |             |             |

### SFR Definition 10.1. PFE0CN: Prefetch Engine Control

| SFR Definition 14.4 | . OSCXCN: External | <b>Oscillator Control</b> |

|---------------------|--------------------|---------------------------|

|---------------------|--------------------|---------------------------|

|                   |             | R/W                                            | R/W          | R             | R/W                     | R/W   | R/W        | Reset Value |

|-------------------|-------------|------------------------------------------------|--------------|---------------|-------------------------|-------|------------|-------------|

| XTLVLD            | XOSCM       | D2 XOSCMD1                                     | XOSCMD0      | -             | XFCN2                   | XFCN1 | XFCN0      | 00000000    |

| Bit7              | Bit6        | Bit5                                           | Bit4         | Bit3          | Bit2                    | Bit1  | Bit0       | SFR Address |

|                   |             |                                                |              |               |                         |       |            | 0xB1        |

| Bit7:             |             | Crystal Occillat                               | or Valid Ela |               |                         |       |            |             |

| DILT.             |             | Crystal Oscillat<br>Ily when XOSCI             |              | ıy.           |                         |       |            |             |

|                   |             | l Oscillator is ur                             |              | t vet stable. |                         |       |            |             |

|                   |             | l Oscillator is ru                             |              |               |                         |       |            |             |

| Bits6–4:          | •           | 02–0: External (                               | -            |               |                         |       |            |             |

|                   | 00x: Exte   | ernal Oscillator o                             | circuit off. |               |                         |       |            |             |

|                   | 010: Exte   | ernal CMOS Clo                                 | ck Mode.     |               |                         |       |            |             |

|                   |             | ernal CMOS Clo                                 |              | th divide by  | v 2 stage.              |       |            |             |

|                   |             | Oscillator Mode                                |              |               |                         |       |            |             |

|                   | •           | acitor Oscillator                              |              |               |                         |       |            |             |

|                   |             | stal Oscillator M                              |              |               |                         |       |            |             |

| D:+2.             |             | tal Oscillator M                               |              |               | age.                    |       |            |             |

| Bit3:<br>Bits2–0: |             | ED. Read = 0, <sup>v</sup><br>D: External Osci |              |               | ol Rite                 |       |            |             |

| DIISZ-U.          |             | See table belov                                | •            | iency Contr   | OI DIIS.                |       |            |             |

|                   |             |                                                |              |               |                         |       |            |             |

|                   |             | Crystal (XOSC                                  | ,            |               | CMD = 10x)              |       | CMD = 10   | <)          |

|                   | 000         | f ≤ 32 kł                                      |              | f ≤ 25        |                         |       | tor = 0.87 |             |

|                   | 001         | 32 kHz < f ≤                                   |              |               | f ≤ 50 kHz              |       | ctor = 2.6 |             |

|                   | 010         | 84 kHz < f ≤ 2                                 |              |               | ≤ 100 kHz               |       | ctor = 7.7 |             |

|                   | 011         | 225 kHz < f ≤                                  |              |               | f ≤ 200 kHz             |       | ctor = 22  |             |

|                   | 100         | 590 kHz < f ≤                                  |              |               | f ≤ 400 kHz             |       | ctor = 65  |             |

|                   | 101         | 1.5 MHz < f ≤                                  |              |               | f ≤ 800 kHz             |       | tor = 180  |             |

|                   | 110         | 4 MHz < f ≤ 1                                  |              |               | f ≤ 1.6 MHz             |       | ctor = 664 |             |

|                   | 111         | 10 MHz < f ≤                                   | 30 MHz       | 1.6 MHz <     | $f \le 3.2 \text{ MHz}$ | K Fac | tor = 1590 |             |

| CRYSTA            | L MODE (    | Circuit from Fig                               | ure 14.1, O  | ption 1; XO   | SCMD = 11               | x)    |            |             |

|                   | •           | KFCN value to r                                |              | •             |                         | ,     |            |             |

|                   |             |                                                |              |               |                         |       |            |             |

| RC MOD            | •           | from Figure 14.                                | •            |               | ,                       |       |            |             |

|                   |             | KFCN value to r                                | •            | ency range    | :                       |       |            |             |

|                   |             | 10 <sup>3</sup> ) / (R x C), w                 |              |               |                         |       |            |             |

|                   |             | ency of clock in                               |              |               |                         |       |            |             |

|                   | •           | citor value in pF                              |              |               |                         |       |            |             |

|                   | K = Pull-   | up resistor value                              | e in κΩ      |               |                         |       |            |             |

|                   | (Circuit fr | om Figure 14.1,                                | Ontion 2. V  | ( <u>)</u>    | 10v)                    |       |            |             |

|                   |             | K Factor (KF) fo                               |              |               |                         |       |            |             |

|                   |             | C x V <sub>DD</sub> ), where                   |              | aon neque     | ity uconeu.             |       |            |             |

|                   | -           | ency of clock in                               |              |               |                         |       |            |             |

|                   | •           | citor value the >                              |              | ηpF           |                         |       |            |             |

|                   |             | ower Supply on                                 |              |               |                         |       |            |             |

|                   |             |                                                |              |               |                         |       |            |             |

### Table 14.1. Oscillator Electrical Characteristics

#### $V_{DD}$ = 2.7 to 3.6 V; -40 to +85 °C unless otherwise specified

| Parameter                                            | Conditions                                      | Min      | Тур   | Max   | Units  |

|------------------------------------------------------|-------------------------------------------------|----------|-------|-------|--------|

| Internal High-Frequency Os                           | cillator (Using Factory-Calibrated              | Settings | 5)    |       |        |

| Oscillator Frequency                                 | IFCN = 11b                                      | 11.82    | 12.00 | 12.18 | MHz    |

| Oscillator Supply Current<br>(from V <sub>DD</sub> ) | 24 °C, V <sub>DD</sub> = 3.0 V,<br>OSCICN.7 = 1 | _        | 685   | —     | μA     |

| Internal Low-Frequency Os                            | cillator (Using Factory-Calibrated S            | Settings | )     |       |        |

| Oscillator Frequency                                 | OSCLD = 11b                                     | 72       | 80    | 99    | kHz    |

| Oscillator Supply Current<br>(from V <sub>DD</sub> ) | 24 °C, V <sub>DD</sub> = 3.0 V,<br>OSCLCN.7 = 1 | _        | 7.0   | _     | μA     |

| External USB Clock Require                           | ements                                          |          |       |       |        |

|                                                      | Full Speed Mode                                 | 47.88    | 48    | 48.12 | N 41 I |

| USB Clock Frequency*                                 | Low Speed Mode                                  | 5.91     | 6     | 6.09  | MHz    |

\*Note: Applies only to external oscillator sources.

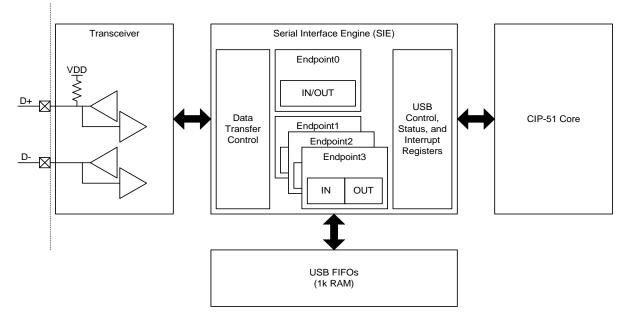

## 16. Universal Serial Bus Controller (USB0)

C8051F34x devices include a complete Full/Low Speed USB function for USB peripheral implementations\*. The USB Function Controller (USB0) consists of a Serial Interface Engine (SIE), USB Transceiver (including matching resistors and configurable pull-up resistors), 1k FIFO block, and clock recovery mechanism for crystal-less operation. No external components are required. The USB Function Controller and Transceiver is Universal Serial Bus Specification 2.0 compliant.

Figure 16.1. USB0 Block Diagram

*Important Note:* This document assumes a comprehensive understanding of the USB Protocol. Terms and abbreviations used in this document are defined in the USB Specification. We encourage you to review the latest version of the USB Specification before proceeding.

\*Note: The C8051F34x cannot be used as a USB Host device.

#### 16.5.2. FIFO Double Buffering

FIFO slots for Endpoints1-3 can be configured for double-buffered mode. In this mode, the maximum packet size is halved and the FIFO may contain two packets at a time. This mode is available for Endpoints1-3. When an endpoint is configured for Split Mode, double buffering may be enabled for the IN Endpoint and/or the OUT endpoint. When Split Mode is not enabled, double-buffering may be enabled for the entire endpoint FIFO. See Table 16.3 for a list of maximum packet sizes for each FIFO configuration.

| Endpoint<br>Number | Split Mode<br>Enabled? | Maximum IN Packet Size (Dou-<br>ble Buffer Disabled / Enabled) | Maximum OUT Packet Size<br>(Double Buffer Disabled /<br>Enabled) |

|--------------------|------------------------|----------------------------------------------------------------|------------------------------------------------------------------|

| 0                  | N/A                    | 64                                                             | 4                                                                |

| 1                  | N                      | 128                                                            | / 64                                                             |

| 1                  | Y                      | 64 / 32                                                        | 64 / 32                                                          |

| 2                  | N                      | 256 /                                                          | 128                                                              |

| 2                  | Y                      | 128 / 64                                                       | 128 / 64                                                         |

| 3                  | N                      | 512 /                                                          | 256                                                              |

| 3                  | Y                      | 256 / 128                                                      | 256 / 128                                                        |

#### Table 16.3. FIFO Configurations

#### 16.5.1. FIFO Access

Each endpoint FIFO is accessed through a corresponding FIFOn register. A read of an endpoint FIFOn register unloads one byte from the FIFO; a write of an endpoint FIFOn register loads one byte into the endpoint FIFO. When an endpoint FIFO is configured for Split Mode, a read of the endpoint FIFOn register unloads one byte from the OUT endpoint FIFO; a write of the endpoint FIFOn register loads one byte into the IN endpoint FIFO.

#### USB Register Definition 16.6. FIFOn: USB0 Endpoint FIFO Access

|                                                                                                                                                                                   |      | FIFODATA 00  |               |           |             |             |             |           |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|---------------|-----------|-------------|-------------|-------------|-----------|------------|

| USB Addresses 0x20–0x23 provide access to the 4 pairs of endpoint FIFOs:<br>IN/OUT Endpoint FIFO       USB Address         0       0x20         1       0x21         2       0x22 | Bit7 | Bit6         | Bit5          | Bit4      | Bit3        | Bit2        | Bit1        | Bit0      | USB Addres |

| IN/OUT Endpoint FIFOUSB Address00x2010x2120x22                                                                                                                                    |      |              |               |           |             |             |             |           | 0x20 - 0x  |

| 0         0x20           1         0x21           2         0x22                                                                                                                  |      | USB Addres   | sses 0x20–0x2 | 23 provid | e access to | the 4 pairs | of endpoint | t FIFOs:  |            |

| 0         0x20           1         0x21           2         0x22                                                                                                                  |      |              | desint EIEO   |           | Adroco      |             |             |           |            |

| 1 0x21<br>2 0x22                                                                                                                                                                  |      |              |               | 036       |             |             |             |           |            |

| 2 0x22                                                                                                                                                                            |      | U            |               |           |             |             |             |           |            |

|                                                                                                                                                                                   |      | 1            |               |           | 0x21        |             |             |           |            |

| 3 0x23                                                                                                                                                                            |      |              | 2             |           | 0x22        |             |             |           |            |

|                                                                                                                                                                                   |      | -            | 3             |           | 0x23        |             |             |           |            |

|                                                                                                                                                                                   |      |              |               |           | -           |             |             |           |            |

|                                                                                                                                                                                   |      | Reading from | m the FIFO ac | idress ur | noads data  | from the O  | JI FIFO for | the corre | sponding   |

#### USB Register Definition 16.16. CMIE: USB0 Common Interrupt Enable

| Bit7       Bit6       Bit5       Bit4       Bit3       Bit2       Bit1       Bit0       U         Bits7-4:       Unused. Read = 0000b; Write = don't care.       Bit3:       SOFE: Start of Frame Interrupt Enable       0: SOF interrupt disabled.       1: SOF interrupt disabled.       1: SOF interrupt enabled.         Bit2:       RSTINTE: Reset Interrupt Enable       0: Reset interrupt disabled.       1: Reset interrupt disabled.         Bit1:       RSUINTE: Resume Interrupt Enable       0: Resume interrupt disabled.       1: Resume Interrupt enabled.         Bit1:       RSUINTE: Resume Interrupt Enable       0: Resume interrupt disabled.       1: Resume interrupt disabled.         Bit1:       RSUINTE: Resume Interrupt Enable       0: Resume interrupt disabled.       1: Resume interrupt disabled. | Reset Value                           |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|--|--|--|

| <ul> <li>Bits7-4: Unused. Read = 0000b; Write = don't care.</li> <li>Bit3: SOFE: Start of Frame Interrupt Enable</li> <li>0: SOF interrupt disabled.</li> <li>1: SOF interrupt enabled.</li> <li>Bit2: RSTINTE: Reset Interrupt Enable</li> <li>0: Reset interrupt disabled.</li> <li>1: Reset interrupt enabled.</li> <li>Bit1: RSUINTE: Resume Interrupt Enable</li> <li>0: Resume interrupt disabled.</li> <li>1: Resume interrupt disabled.</li> <li>1: Resume interrupt disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                    | 00000110                              |  |  |  |  |  |  |  |

| Bit3:       SOFE: Start of Frame Interrupt Enable         0: SOF interrupt disabled.         1: SOF interrupt enabled.         Bit2:       RSTINTE: Reset Interrupt Enable         0: Reset interrupt disabled.         1: Reset interrupt enabled.         Bit1:       RSUINTE: Resume Interrupt Enable         0: Resume interrupt disabled.         1: Resume interrupt disabled.         1: Resume interrupt disabled.         1: Resume interrupt disabled.         1: Resume interrupt disabled.                                                                                                                                                                                                                                                                                                                               | USB Addres                            |  |  |  |  |  |  |  |

| 0: SOF interrupt disabled.<br>1: SOF interrupt enabled.<br>Bit2: RSTINTE: Reset Interrupt Enable<br>0: Reset interrupt disabled.<br>1: Reset interrupt enabled.<br>Bit1: RSUINTE: Resume Interrupt Enable<br>0: Resume interrupt disabled.<br>1: Resume interrupt disabled.<br>1: Resume interrupt enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x0B                                  |  |  |  |  |  |  |  |

| 0: SOF interrupt disabled.<br>1: SOF interrupt enabled.<br>Bit2: RSTINTE: Reset Interrupt Enable<br>0: Reset interrupt disabled.<br>1: Reset interrupt enabled.<br>Bit1: RSUINTE: Resume Interrupt Enable<br>0: Resume interrupt disabled.<br>1: Resume interrupt disabled.<br>1: Resume interrupt enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |  |  |  |  |  |  |  |

| 1: SOF interrupt enabled.<br>Bit2: RSTINTE: Reset Interrupt Enable<br>0: Reset interrupt disabled.<br>1: Reset interrupt enabled.<br>Bit1: RSUINTE: Resume Interrupt Enable<br>0: Resume interrupt disabled.<br>1: Resume interrupt enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |  |  |  |  |  |  |  |

| Bit2:       RSTINTE: Reset Interrupt Enable         0: Reset interrupt disabled.         1: Reset interrupt enabled.         Bit1:       RSUINTE: Resume Interrupt Enable         0: Resume interrupt disabled.         1: Resume interrupt enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |  |  |  |  |  |  |  |

| 0: Reset interrupt disabled.<br>1: Reset interrupt enabled.<br>Bit1: RSUINTE: Resume Interrupt Enable<br>0: Resume interrupt disabled.<br>1: Resume interrupt enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |  |  |  |  |  |  |  |

| 1: Reset interrupt enabled. Bit1: RSUINTE: Resume Interrupt Enable     0: Resume interrupt disabled.     1: Resume interrupt enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |  |  |  |  |  |  |  |

| Bit1: RSUINTE: Resume Interrupt Enable<br>0: Resume interrupt disabled.<br>1: Resume interrupt enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | · · · · · · · · · · · · · · · · · · · |  |  |  |  |  |  |  |

| 0: Resume interrupt disabled.<br>1: Resume interrupt enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                     |  |  |  |  |  |  |  |

| 1: Resume interrupt enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RSUINTE: Resume Interrupt Enable      |  |  |  |  |  |  |  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0: Resume interrupt disabled.         |  |  |  |  |  |  |  |

| Bit0: SUSINTE: Suspend Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1: Resume interrupt enabled.          |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SUSINTE: Suspend Interrupt Enable     |  |  |  |  |  |  |  |

| 0: Suspend interrupt disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       |  |  |  |  |  |  |  |

| 1: Suspend interrupt enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |  |  |  |  |  |  |  |

#### 16.9. The Serial Interface Engine

The Serial Interface Engine (SIE) performs all low level USB protocol tasks, interrupting the processor when data has successfully been transmitted or received. When receiving data, the SIE will interrupt the processor when a complete data packet has been received; appropriate handshaking signals are automatically generated by the SIE. When transmitting data, the SIE will interrupt the processor when a complete data packet has been received; appropriate handshaking signals are automatically generated by the SIE. When transmitting data, the SIE will interrupt the processor when a complete data packet has been transmitted and the appropriate handshake signal has been received.

The SIE will not interrupt the processor when corrupted/erroneous packets are received.

#### 16.10. Endpoint0

Endpoint0 is managed through the USB register E0CSR (USB Register Definition 16.17). The INDEX register must be loaded with 0x00 to access the E0CSR register.

An Endpoint0 interrupt is generated when:

- 1. A data packet (OUT or SETUP) has been received and loaded into the Endpoint0 FIFO. The OPRDY bit (E0CSR.0) is set to '1' by hardware.

- 2. An IN data packet has successfully been unloaded from the Endpoint0 FIFO and transmitted to the host; INPRDY is reset to '0' by hardware.

- 3. An IN transaction is completed (this interrupt generated during the status stage of the transaction).

- 4. Hardware sets the STSTL bit (E0CSR.2) after a control transaction ended due to a protocol violation.

- 5. Hardware sets the SUEND bit (E0CSR.4) because a control transfer ended before firmware sets the DATAEND bit (E0CSR.3).

#### USB Register Definition 16.19. EINCSRL: USB0 IN Endpoint Control Low Byte

| R     | W                                                                                                                                                                                                                                                                              | R/W                                                                                                                                                     | R/W           | R/W          | R/W           | R/W           | R/W         | Reset Value          |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|---------------|---------------|-------------|----------------------|--|

| -     | CLRDT                                                                                                                                                                                                                                                                          | STSTL                                                                                                                                                   | SDSTL         | FLUSH        | UNDRUN        | FIFONE        | INPRDY      | 00000000             |  |

| Bit7  | Bit6                                                                                                                                                                                                                                                                           | Bit5                                                                                                                                                    | Bit4          | Bit3         | Bit2          | Bit1          | Bit0        | USB Address:<br>0x11 |  |

| Bit7: | Unused. Read = 0; Write = don't care.                                                                                                                                                                                                                                          |                                                                                                                                                         |               |              |               |               |             |                      |  |

| Bit6: | CLRDT: Clear Data Toggle.                                                                                                                                                                                                                                                      |                                                                                                                                                         |               |              |               |               |             |                      |  |

|       | Write: Software should write '1' to this bit to reset the IN Endpoint data toggle to '0'.                                                                                                                                                                                      |                                                                                                                                                         |               |              |               |               |             |                      |  |

|       | Read: This bit always reads '0'.                                                                                                                                                                                                                                               |                                                                                                                                                         |               |              |               |               |             |                      |  |

| Bit5: | STSTL: Sen                                                                                                                                                                                                                                                                     |                                                                                                                                                         |               | 07411        |               |               |             |                      |  |

|       | Hardware sets this bit to '1' when a STALL handshake signal is transmitted. The FIFO is                                                                                                                                                                                        |                                                                                                                                                         |               |              |               |               |             | FIFOIS               |  |

| Bit4: |                                                                                                                                                                                                                                                                                | flushed, and the INPRDY bit cleared. This flag must be cleared by software.<br>SDSTL: Send Stall.                                                       |               |              |               |               |             |                      |  |

| DIL4. | Software sho                                                                                                                                                                                                                                                                   |                                                                                                                                                         | ' to this bit | to generate  | a STALL ha    | andshake ii   | n response  | to an IN             |  |