Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                          |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                   |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f34d-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

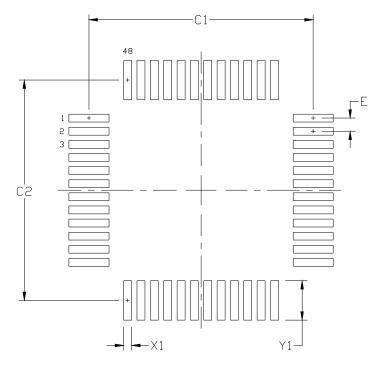

Figure 4.3. TQFP-48 Recommended PCB Land Pattern

| Table 4.3. TQFP-48 PCB Land Pattern Dimensions |                                |                           |  |  |  |  |  |  |

|------------------------------------------------|--------------------------------|---------------------------|--|--|--|--|--|--|

| Dimension                                      | Min                            | Max                       |  |  |  |  |  |  |

| C1                                             | 8.30                           | 8.40                      |  |  |  |  |  |  |

| C2                                             | 8.30                           | 8.40                      |  |  |  |  |  |  |

| E                                              | 0.50                           | BSC                       |  |  |  |  |  |  |

| X1                                             | 0.20                           | 0.30                      |  |  |  |  |  |  |

| Y1                                             | 1.40                           | 1.50                      |  |  |  |  |  |  |

| Notes:                                         |                                |                           |  |  |  |  |  |  |

| General:                                       |                                |                           |  |  |  |  |  |  |

| <ol> <li>All dimensions shown ar</li> </ol>    | e in millimeters (mm) unless   | otherwise noted.          |  |  |  |  |  |  |

| 2. This Land Pattern Desig                     | n is based on the IPC-7351 g   | juidelines.               |  |  |  |  |  |  |

| Solder Mask Design:                            |                                |                           |  |  |  |  |  |  |

| 3. All metal pads are to be                    | non-solder mask defined (NS    | MD). Clearance between    |  |  |  |  |  |  |

| the solder mask and the                        | metal pad is to be 60 µm min   | imum, all the way around  |  |  |  |  |  |  |

| the pad.                                       |                                |                           |  |  |  |  |  |  |

| Stencil Design:                                |                                |                           |  |  |  |  |  |  |

| 4. A stainless steel, laser-c                  | ut and electro-polished stend  | il with trapezoidal walls |  |  |  |  |  |  |

| should be used to assure                       | e good solder paste release.   | ·                         |  |  |  |  |  |  |

| 5. The stencil thickness sho                   | ould be 0.125 mm (5 mils).     |                           |  |  |  |  |  |  |

| 6. The ratio of stencil apert                  | ure to land pad size should b  | e 1:1 for all pads.       |  |  |  |  |  |  |

| Card Assembly:                                 | ·                              | ·                         |  |  |  |  |  |  |

| 7. A No-Clean, Type-3 sold                     | er paste is recommended.       |                           |  |  |  |  |  |  |

|                                                | reflow profile is per the JEDE | EC/IPC J-STD-020          |  |  |  |  |  |  |

| specification for Small B                      |                                |                           |  |  |  |  |  |  |

Table 4.3. TQFP-48 PCB Land Pattern Dimensions

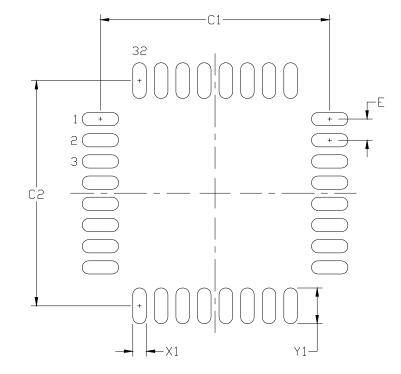

# Figure 4.6. LQFP-32 Recommended PCB Land Pattern

### Table 4.5. LQFP-32 PCB Land Pattern Dimensions

|       |                              |                                       | Dimensions                 |  |  |

|-------|------------------------------|---------------------------------------|----------------------------|--|--|

|       | Dimension                    | Min                                   | Max                        |  |  |

|       | C1                           | 8.40                                  | 8.50                       |  |  |

|       | C2                           | 8.40                                  | 8.50                       |  |  |

|       | E                            | 0.80 BSC                              |                            |  |  |

|       | X1                           | 0.40                                  | 0.50                       |  |  |

|       | Y1                           | 1.25                                  | 1.35                       |  |  |

| Notes | :                            |                                       |                            |  |  |

| Gener | ral:                         |                                       |                            |  |  |

| 1.    | All dimensions shown are     | in millimeters (mm) unless            | otherwise noted.           |  |  |

| 2.    | This Land Pattern Design     | is based on the IPC-7351              | guidelines.                |  |  |

| Solde | r Mask Design:               |                                       |                            |  |  |

| 3.    | All metal pads are to be no  | on-solder mask defined (N             | SMD). Clearance between    |  |  |

|       | the solder mask and the m    | ietal pad is to be 60 μm mi           | nimum, all the way around  |  |  |

|       | the pad.                     |                                       |                            |  |  |

| Stenc | il Design:                   |                                       |                            |  |  |

| 4.    | A stainless steel, laser-cut | and electro-polished sten             | cil with trapezoidal walls |  |  |

|       | should be used to assure     | •                                     | •                          |  |  |

| 5.    | The stencil thickness shou   |                                       |                            |  |  |

|       | The ratio of stencil apertur | · · ·                                 | pe 1:1 for all pads.       |  |  |

|       | Assembly:                    | •                                     |                            |  |  |

|       | A No-Clean, Type-3 solde     | r paste is recommended.               |                            |  |  |

|       | The recommended card re      | •                                     | EC/IPC J-STD-020           |  |  |

| 51    | specification for Small Boo  |                                       |                            |  |  |

|       |                              | · · · · · · · · · · · · · · · · · · · |                            |  |  |

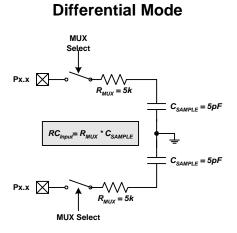

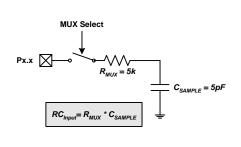

### 5.3.3. Settling Time Requirements

When the ADC0 input configuration is changed (i.e., a different AMUX0 selection is made), a minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the minimum tracking time requirements.

Figure 5.5 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 5.1. When measuring the Temperature Sensor output or  $V_{DD}$  with respect to GND,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 5.1 for ADC0 minimum settling time requirements.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

# Equation 5.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

*n* is the ADC resolution in bits (10).

Single-Ended Mode

# Figure 5.5. ADC0 Equivalent Input Circuits

# 7. Comparators

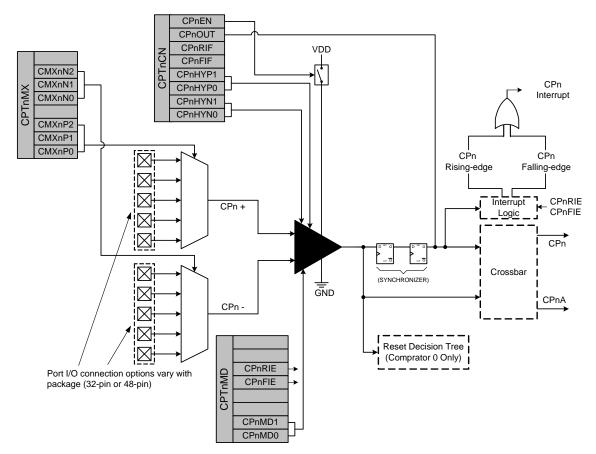

C8051F34x devices include two on-chip programmable voltage Comparators. A block diagram of the comparators is shown in Figure 7.1, where "n" is the comparator number (0 or 1). The two Comparators operate identically with the following exceptions: (1) Their input selections differ, and (2) Comparator0 can be used as a reset source. For input selection details, refer to SFR Definition 7.2 and SFR Definition 7.5.

Each Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0, CP1), or an asynchronous "raw" output (CP0A, CP1A). The asynchronous signal is available even when the system clock is not active. This allows the Comparators to operate and generate an output with the device in STOP mode. When assigned to a Port pin, the Comparator outputs may be configured as open drain or push-pull (see Section "15.2. Port I/O Initialization" on page 147). Comparator0 may also be used as a reset source (see Section "11.5. Comparator0 Reset" on page 103).

The Comparator0 inputs are selected in the CPT0MX register (SFR Definition 7.2). The CMX0P1-CMX0P0 bits select the Comparator0 positive input; the CMX0N1-CMX0N0 bits select the Comparator0 negative input. The Comparator1 inputs are selected in the CPT1MX register (SFR Definition 7.5). The CMX-1P1-CMX1P0 bits select the Comparator1 positive input; the CMX1N1-CMX1N0 bits select the Comparator1 negative input.

**Important Note About Comparator Inputs:** The Port pins selected as Comparator inputs should be configured as analog inputs in their associated Port configuration register, and configured to be skipped by the Crossbar (for details on Port configuration, see **Section "15.3. General Purpose Port I/O" on page 150**).

Figure 7.1. Comparator Functional Block Diagram

Comparator outputs can be polled in software, used as an interrupt source, and/or routed to a Port pin. When routed to a Port pin, Comparator outputs are available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP mode (with no system clock active). When disabled, the Comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and supply current falls to less than 100 nA. See **Section "15.1. Priority Crossbar Decoder" on page 144** for details on configuring Comparator outputs via the digital Crossbar. Comparator inputs can be externally driven from -0.25 V to (V<sub>DD</sub>) + 0.25 V without damage or upset. The complete Comparator electrical specifications are given in Table 7.1.

Comparator response time may be configured in software via the CPTnMD registers (see SFR Definition 7.3 and SFR Definition 7.6). Selecting a longer response time reduces the Comparator supply current. See Table 7.1 for complete timing and supply current specifications.

#### Notes on Registers, Operands and Addressing Modes:

Rn - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8K-byte program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

| R/W   | R/W                                                                                                   | R/W           | R/W           | R/W           | R/W            | R/W          | R/W   | Reset Value         |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|----------------|--------------|-------|---------------------|--|--|--|

| PT3   | PCP1                                                                                                  | PCP0          | PPCA0         | PADC0         | PWADC0         | PUSB0        | PSMB0 | 00000000            |  |  |  |

| Bit7  | Bit6                                                                                                  | Bit5          | Bit4          | Bit3          | Bit2           | Bit1         | Bit0  | SFR Address<br>0xF6 |  |  |  |

| Bit7: | PT3: Timer 3                                                                                          |               |               |               |                |              |       |                     |  |  |  |

|       | This bit sets                                                                                         |               |               |               | ot.            |              |       |                     |  |  |  |

|       | 0: Timer 3 interrupts set to low priority level.<br>1: Timer 3 interrupts set to high priority level. |               |               |               |                |              |       |                     |  |  |  |

|       |                                                                                                       | •             | • •           |               |                |              |       |                     |  |  |  |

| Bit6: | PCP1: Comparator1 (CP1) Interrupt Priority Control.                                                   |               |               |               |                |              |       |                     |  |  |  |

|       | This bit sets the priority of the CP1 interrupt.                                                      |               |               |               |                |              |       |                     |  |  |  |

|       | 0: CP1 interrupt set to low priority level.                                                           |               |               |               |                |              |       |                     |  |  |  |

|       | 1: CP1 inter                                                                                          |               | • • •         |               |                |              |       |                     |  |  |  |

| Bit5: | PCP0: Com                                                                                             | · ·           | , i           |               | ontrol.        |              |       |                     |  |  |  |

|       | This bit sets                                                                                         | the priority  | of the CP0    | interrupt.    |                |              |       |                     |  |  |  |

|       | 0: CP0 interrupt set to low priority level.                                                           |               |               |               |                |              |       |                     |  |  |  |

|       | 1: CP0 interrupt set to high priority level.                                                          |               |               |               |                |              |       |                     |  |  |  |

| Bit4: | PPCA0: Programmable Counter Array (PCA0) Interrupt Priority Control.                                  |               |               |               |                |              |       |                     |  |  |  |

|       | This bit sets the priority of the PCA0 interrupt.                                                     |               |               |               |                |              |       |                     |  |  |  |

|       | 0: PCA0 interrupt set to low priority level.                                                          |               |               |               |                |              |       |                     |  |  |  |

|       | 1: PCA0 inte                                                                                          | errupt set to | high priorit  | y level.      |                |              |       |                     |  |  |  |

| Bit3: | PADC0 ADC                                                                                             | 0 Convers     | ion Comple    | te Interrupt  | Priority Con   | trol.        |       |                     |  |  |  |

|       | This bit sets                                                                                         | the priority  | of the ADC    | 0 Conversi    | on Complete    | e interrupt. |       |                     |  |  |  |

|       | 0: ADC0 Co                                                                                            | nversion Co   | omplete inte  | errupt set to | low priority   | level.       |       |                     |  |  |  |

|       | 1: ADC0 Co                                                                                            | nversion Co   | omplete inte  | errupt set to | high priority  | / level.     |       |                     |  |  |  |

| Bit2: | PWADC0: A                                                                                             | DC0 Windo     | ow Compara    | ator Interru  | ot Priority Co | ontrol.      |       |                     |  |  |  |

|       | This bit sets                                                                                         | the priority  | of the ADC    | 0 Window      | interrupt.     |              |       |                     |  |  |  |

|       | 0: ADC0 Wir                                                                                           | ndow interr   | upt set to lo | w priority le | evel.          |              |       |                     |  |  |  |

|       | 1: ADC0 Wir                                                                                           | ndow interr   | upt set to hi | gh priority l | evel.          |              |       |                     |  |  |  |

| Bit1: | PUSB0: USE                                                                                            | 30 Interrup   | t Priority Co | ntrol.        |                |              |       |                     |  |  |  |

|       | This bit sets                                                                                         | the priority  | of the USB    | 0 interrupt.  |                |              |       |                     |  |  |  |

|       | 0: USB0 inte                                                                                          | errupt set to | low priority  | level.        |                |              |       |                     |  |  |  |

|       | 1: USB0 inte                                                                                          | •             |               |               |                |              |       |                     |  |  |  |

| Bit0: | PSMB0: SM                                                                                             | •             | • •           |               | ntrol.         |              |       |                     |  |  |  |

|       | This bit sets                                                                                         |               |               |               |                |              |       |                     |  |  |  |

|       | 0: SMB0 inte                                                                                          |               |               |               |                |              |       |                     |  |  |  |

|       | 1: SMB0 inte                                                                                          |               |               |               |                |              |       |                     |  |  |  |

# SFR Definition 9.10. EIP1: Extended Interrupt Priority 1

### 9.4. Power Management Modes

The CIP-51 core has two software programmable power management modes: Idle and Stop. Idle mode halts the CPU while leaving the peripherals and clocks active. In Stop mode, the CPU is halted, all interrupts, are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not affected). Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode consumes the least power. Figure 1.15 describes the Power Control Register (PCON) used to control the CIP-51's power management modes.

Although the CIP-51 has Idle and Stop modes built in (as with any standard 8051 architecture), power management of the entire MCU is better accomplished through system clock and individual peripheral management. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off the oscillators lowers power consumption considerably; however a reset is required to restart the MCU.

The internal oscillator can be placed in Suspend mode (see **Section "14. Oscillators" on page 131**). In Suspend mode, the internal oscillator is stopped until a non-idle USB event is detected, or the VBUS input signal matches the polarity selected by the VBPOL bit in register REGOCN (SFR Definition 8.1).

#### 9.4.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to **Section "11.6. PCA Watchdog Timer Reset" on page 103** for more information on the use and configuration of the WDT.

#### 9.4.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100 µsec.

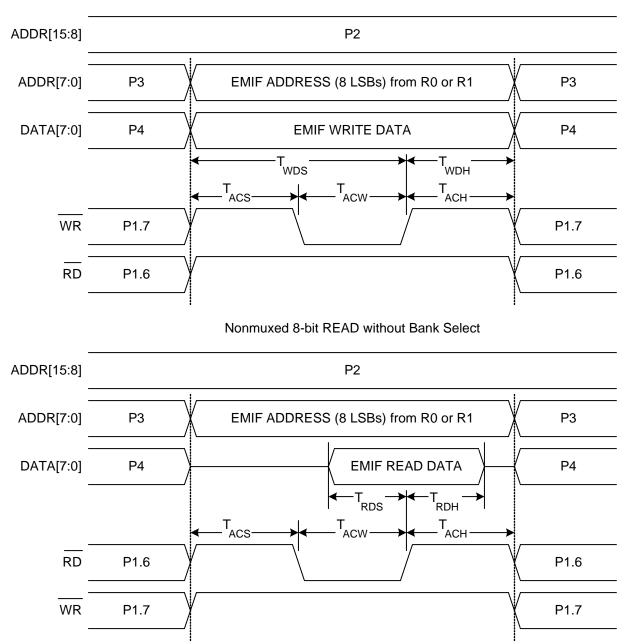

## 13.7.1.2.8-bit MOVX without Bank Select: EMI0CF[4:2] = '101' or '111'.

Nonmuxed 8-bit WRITE without Bank Select

Figure 13.6. Non-multiplexed 8-bit MOVX without Bank Select Timing

| SFR Definition 14.4 | . OSCXCN: External | <b>Oscillator Control</b> |

|---------------------|--------------------|---------------------------|

|---------------------|--------------------|---------------------------|

|                   |                                                       | R/W                                                                                       | R/W          | R             | R/W                     | R/W   | R/W        | Reset Value |  |  |  |

|-------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------|---------------|-------------------------|-------|------------|-------------|--|--|--|

| XTLVLD            | XOSCM                                                 | D2 XOSCMD1                                                                                | XOSCMD0      | -             | XFCN2                   | XFCN1 | XFCN0      | 00000000    |  |  |  |

| Bit7              | Bit6                                                  | Bit5                                                                                      | Bit4         | Bit3          | Bit2                    | Bit1  | Bit0       | SFR Address |  |  |  |

|                   |                                                       |                                                                                           |              |               |                         |       |            | 0xB1        |  |  |  |

| Bit7:             |                                                       | Crystal Occillat                                                                          | or Valid Ela |               |                         |       |            |             |  |  |  |

| DILT.             |                                                       | Crystal Oscillat<br>Ily when XOSCI                                                        |              | ıy.           |                         |       |            |             |  |  |  |

|                   |                                                       | l Oscillator is ur                                                                        |              | t vet stable. |                         |       |            |             |  |  |  |

|                   |                                                       |                                                                                           |              |               |                         |       |            |             |  |  |  |

| Bits6–4:          | •                                                     | 1: Crystal Oscillator is running and stable.<br>XOSCMD2–0: External Oscillator Mode Bits. |              |               |                         |       |            |             |  |  |  |

|                   | 00x: External Oscillator circuit off.                 |                                                                                           |              |               |                         |       |            |             |  |  |  |

|                   | 010: External CMOS Clock Mode.                        |                                                                                           |              |               |                         |       |            |             |  |  |  |

|                   | 011: External CMOS Clock Mode with divide by 2 stage. |                                                                                           |              |               |                         |       |            |             |  |  |  |

|                   |                                                       | Oscillator Mode                                                                           |              |               |                         |       |            |             |  |  |  |

|                   | •                                                     | acitor Oscillator                                                                         |              |               |                         |       |            |             |  |  |  |

|                   |                                                       | stal Oscillator M                                                                         |              |               |                         |       |            |             |  |  |  |

| D:+2.             |                                                       | tal Oscillator M                                                                          |              |               | age.                    |       |            |             |  |  |  |

| Bit3:<br>Bits2–0: |                                                       | ED. Read = 0, <sup>v</sup><br>D: External Osci                                            |              |               | ol Rite                 |       |            |             |  |  |  |

| DIISZ-U.          |                                                       | See table belov                                                                           | •            | iency Contr   | OI DIIS.                |       |            |             |  |  |  |

|                   |                                                       |                                                                                           |              |               |                         |       |            |             |  |  |  |

|                   |                                                       | Crystal (XOSC                                                                             | ,            |               | CMD = 10x)              |       | CMD = 10   | <)          |  |  |  |

|                   | 000                                                   | f ≤ 32 kł                                                                                 |              | f ≤ 25        |                         |       | tor = 0.87 |             |  |  |  |

|                   | 001                                                   | 32 kHz < f ≤                                                                              |              |               | f ≤ 50 kHz              |       | ctor = 2.6 |             |  |  |  |

|                   | 010                                                   | 84 kHz < f ≤ 2                                                                            |              |               | ≤ 100 kHz               |       | ctor = 7.7 |             |  |  |  |

|                   | 011                                                   | 225 kHz < f ≤                                                                             |              |               | f ≤ 200 kHz             |       | ctor = 22  |             |  |  |  |

|                   | 100                                                   | 590 kHz < f ≤                                                                             |              |               | f ≤ 400 kHz             |       | ctor = 65  |             |  |  |  |

|                   | 101                                                   | 1.5 MHz < f ≤                                                                             |              |               | f ≤ 800 kHz             |       | tor = 180  |             |  |  |  |

|                   | 110                                                   | 4 MHz < f ≤ 1                                                                             |              |               | f ≤ 1.6 MHz             |       | ctor = 664 |             |  |  |  |

|                   | 111                                                   | 10 MHz < f ≤                                                                              | 30 MHz       | 1.6 MHz <     | $f \le 3.2 \text{ MHz}$ | K Fac | tor = 1590 |             |  |  |  |

| CRYSTA            | L MODE (                                              | Circuit from Fig                                                                          | ure 14.1, O  | ption 1; XO   | SCMD = 11               | x)    |            |             |  |  |  |

|                   | •                                                     | KFCN value to r                                                                           |              | •             |                         | ,     |            |             |  |  |  |

|                   |                                                       |                                                                                           |              |               |                         |       |            |             |  |  |  |

| RC MOD            | •                                                     | from Figure 14.                                                                           | •            |               | •                       |       |            |             |  |  |  |

|                   |                                                       | KFCN value to r                                                                           | •            | ency range    | :                       |       |            |             |  |  |  |

|                   |                                                       | 10 <sup>3</sup> ) / (R x C), w                                                            |              |               |                         |       |            |             |  |  |  |

|                   |                                                       | ency of clock in                                                                          |              |               |                         |       |            |             |  |  |  |

|                   | •                                                     | citor value in pF                                                                         |              |               |                         |       |            |             |  |  |  |

|                   | K = Pull-                                             | up resistor value                                                                         | e in κΩ      |               |                         |       |            |             |  |  |  |

|                   | (Circuit fr                                           | om Figure 14.1,                                                                           | Ontion 2. V  | ( <u>)</u>    | 10v)                    |       |            |             |  |  |  |

|                   |                                                       | K Factor (KF) fo                                                                          |              |               |                         |       |            |             |  |  |  |

|                   |                                                       | C x V <sub>DD</sub> ), where                                                              |              | aon neque     | ity uconeu.             |       |            |             |  |  |  |

|                   | -                                                     | ency of clock in                                                                          |              |               |                         |       |            |             |  |  |  |

|                   | •                                                     | citor value the >                                                                         |              | ηpF           |                         |       |            |             |  |  |  |

|                   |                                                       | ower Supply on                                                                            |              |               |                         |       |            |             |  |  |  |

|                   |                                                       |                                                                                           |              |               |                         |       |            |             |  |  |  |

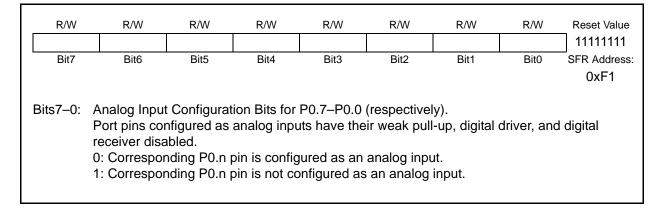

# 15.3. General Purpose Port I/O

Port pins that remain unassigned by the Crossbar and are not used by analog peripherals can be used for general purpose I/O. Ports 3-0 are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. Port 4 (48-pin packages only) uses an SFR which is byte-addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the register (not the pin) is read, modified, and written back to the SFR.

| R/W                    | R/W                                                                                                                         | R/W                                                                      | R/W                                        | R/W                           | R/W        | R/W        | R/W       | Reset Value  |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------|-------------------------------|------------|------------|-----------|--------------|--|--|

| P0.7                   | P0.6                                                                                                                        | P0.5                                                                     | P0.4                                       | P0.3                          | P0.2       | P0.1       | P0.0      | 111111111    |  |  |

|                        |                                                                                                                             |                                                                          |                                            |                               |            |            |           |              |  |  |

| Bit7                   | Bit6                                                                                                                        | Bit5                                                                     | Bit4                                       | Bit3                          | Bit2       | Bit1       | Bit0      | SFR Address: |  |  |

| (bit addressable) 0x80 |                                                                                                                             |                                                                          |                                            |                               |            |            |           |              |  |  |

| Bits7–0:               | P0.[7:0]<br>Write - Outp<br>0: Logic Low<br>1: Logic Higl<br>Read - Alwa<br>pin when co<br>0: P0.n pin is<br>1: P0.n pin is | / Output.<br>h Output (hi<br>ys reads '0'<br>nfigured as<br>s logic low. | gh impedar<br>if selected<br>digital input | nce if corres<br>as analog ir | ponding P0 | )MDOUT.n l | bit = 0). |              |  |  |

## SFR Definition 15.4. P0: Port0 Latch

# SFR Definition 15.5. P0MDIN: Port0 Input Mode

| Bit7       Bit6       Bit5       Bit4       Bit3       Bit2       Bit1       Bit0       SFF         This SFR is used to indirectly read and write USB0 registers.         Write Procedure:         1. Poll for BUSY (USB 0ADR.7) => '0'.                                                                                                                                                                                                                                                                                                                                                                                                                       |                            | R/W                                                                                                        | R/W                                                                              | R/W                                                               | R/W                                           | R/W                      | R/W                       | R/W                      | Reset Value |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------|--------------------------|---------------------------|--------------------------|-------------|--|

| <ul> <li>This SFR is used to indirectly read and write USB0 registers.</li> <li>Write Procedure: <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write data to USB0DAT.</li> <li>Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> </ol> </li> <li>Read Procedure: <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ul> |                            |                                                                                                            |                                                                                  | USB                                                               | DAT                                           |                          |                           |                          | 0000000     |  |

| <ul> <li>This SFR is used to indirectly read and write USB0 registers.</li> <li>Write Procedure: <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write data to USB0DAT.</li> <li>Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> </ol> </li> <li>Read Procedure: <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ul> | Bit7                       | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0                                                                         |                                                                                  |                                                                   |                                               |                          |                           |                          |             |  |

| <ul> <li>Write Procedure:</li> <li>1. Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>2. Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>3. Write data to USB0DAT.</li> <li>4. Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> <li>Read Procedure:</li> <li>1. Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>2. Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>3. Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ul>                                                                           |                            |                                                                                                            |                                                                                  |                                                                   |                                               |                          |                           |                          | 0x97        |  |

| <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write data to USB0DAT.</li> <li>Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> <li>Read Procedure:         <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ol>                                                                                                      | Т                          | This SFR is                                                                                                | used to indi                                                                     | rectly read                                                       | and write U                                   | SB0 registe              | ers.                      |                          |             |  |

| <ol> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write data to USB0DAT.</li> <li>Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> <li>Read Procedure:         <ol> <li>Poll for BUSY (USB_0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ol>                                                                                                                                                     | ٧                          |                                                                                                            |                                                                                  |                                                                   |                                               |                          |                           |                          |             |  |

| <ol> <li>Write data to USB0DAT.</li> <li>Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> <li>Read Procedure:         <ol> <li>Poll for BUSY (USB_0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ol>                                                                                                                                                                                                                                            |                            |                                                                                                            |                                                                                  |                                                                   |                                               |                          |                           |                          |             |  |

| <ul> <li>4. Repeat (Step 2 may be skipped when writing to the same USB0 register).</li> <li>Read Procedure: <ol> <li>Poll for BUSY (USB_0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                 |                            |                                                                                                            |                                                                                  |                                                                   |                                               |                          |                           |                          |             |  |

| <ul> <li>Read Procedure:</li> <li>1. Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>2. Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>3. Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       |                            |                                                                                                            |                                                                                  |                                                                   |                                               |                          |                           |                          |             |  |

| <ol> <li>Poll for BUSY (USB 0ADR.7) =&gt; '0'.</li> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                         |                            | 4. Repeat (Step 2 may be skipped when writing to the same USB0 register).                                  |                                                                                  |                                                                   |                                               |                          |                           |                          |             |  |

| <ol> <li>Load the target USB0 register address into the USBADDR bits in register USB0A</li> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i same write).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                          | 4. Repeat (S                                                                                               | Step 2 may                                                                       | ве ѕкірреа                                                        | when writin                                   | g to the sar             | ne usbu re                | egister).                |             |  |

| <ol> <li>Write '1' to the BUSY bit in register USB0ADR (steps 2 and 3 can be performed i<br/>same write).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |                                                                                                            |                                                                                  | ре скірреа                                                        | when writin                                   | g to the sar             | ne usbu re                | egister).                |             |  |

| same write).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F                          | Read Proced                                                                                                | dure:                                                                            |                                                                   |                                               | g to the sar             |                           | egister).                |             |  |

| 4. Poll for BUSY (USB 0ADR.7) => '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | F<br>1                     | Read Proced                                                                                                | dure:<br>USY (USB                                                                | 0ADR.7) =                                                         | > '0'.                                        | -                        |                           |                          | SB0ADR.     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | F<br>1<br>2                | Read Proced<br>1. Poll for B<br>2. Load the<br>3. Write '1' t                                              | dure:<br>USY (USB<br>target USB<br>to the BUSY                                   | 0ADR.7) =<br>0 register a                                         | > '0'.<br>ddress into                         | the USBAD                | DR bits in I              | register U               |             |  |

| 5. Read data from USB0DAT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | F<br>1<br>2<br>3           | Read Proced<br>1. Poll for B<br>2. Load the<br>3. Write '1' t<br>same writ                                 | dure:<br>USY (USB<br>target USB<br>to the BUSN<br>te).                           | 0ADR.7) =<br>0 register a<br>′ bit in regis                       | > '0'.<br>ddress into<br>ter USB0AI           | the USBAD                | DR bits in I              | register U               |             |  |

| <ol> <li>Repeat from Step 2 (Step 2 may be skipped when reading the same USB0 register<br/>may be skipped when the AUTORD bit (USB0ADR.6) is logic 1).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | F<br>1<br>2<br>3<br>4<br>5 | Read Proced<br>1. Poll for B<br>2. Load the<br>3. Write '1' t<br>same writ<br>4. Poll for B<br>5. Read dat | dure:<br>USY (USB<br>target USB<br>to the BUSY<br>te).<br>USY (USB<br>a from USB | 0ADR.7) =<br>0 register a<br>′ bit in regis<br>0ADR.7) =<br>0DAT. | > '0'.<br>ddress into<br>ter USB0AI<br>> '0'. | the USBAD<br>DR (steps 2 | DR bits in i<br>and 3 can | register U<br>be perfori | med in the  |  |

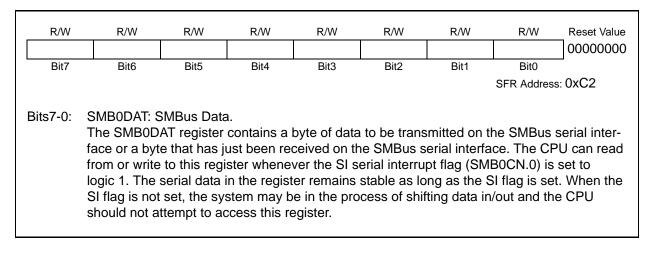

## SFR Definition 16.3. USB0DAT: USB0 Data

. . .

.. . .

| R                         | R    | R    | R    | R    | R    | R    | R    | Reset Value |  |

|---------------------------|------|------|------|------|------|------|------|-------------|--|

| Frame Number Low          |      |      |      |      |      |      |      |             |  |

| Bit7                      | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | USB Address |  |

|                           |      |      |      |      |      |      |      | 0x0C        |  |

| Bits7-0: Frame Number Low |      |      |      |      |      |      |      |             |  |

\_\_\_\_\_

- -

-

.

# USB Register Definition 16.10. FRAMEH: USB0 Frame Number High

| R<br>-   | R<br>-                                     | R<br>-      | R<br>- | R<br>- | R<br>Fran   | R<br>ne Number | R<br>High | Reset Value          |  |  |  |  |  |

|----------|--------------------------------------------|-------------|--------|--------|-------------|----------------|-----------|----------------------|--|--|--|--|--|

| Bit7     | Bit6                                       | Bit5        | Bit4   | Bit3   | Bit2        | Bit1           | Bit0      | USB Address:<br>0x0D |  |  |  |  |  |

| Bits2-0: | Unused. Rea<br>Frame Numb<br>This register | oer High By | te     |        | ved frame r | number.        |           |                      |  |  |  |  |  |

## 16.8. Interrupts

.....

The read-only USB0 interrupt flags are located in the USB registers shown in USB Register Definition 16.11 through USB Register Definition 16.13. The associated interrupt enable bits are located in the USB registers shown in USB Register Definition 16.14 through USB Register Definition 16.16. A USB0 interrupt is generated when any of the USB interrupt flags is set to '1'. The USB0 interrupt is enabled via the EIE1 SFR (see Section "9.3. Interrupt Handler" on page 88).

Important Note: Reading a USB interrupt flag register resets all flags in that register to '0'.

| <b>USB</b> Register | r Definition 16.11 | . IN1INT: USB0 IN | Endpoint Interrupt |

|---------------------|--------------------|-------------------|--------------------|

|---------------------|--------------------|-------------------|--------------------|

|    | R                       | R                                                                                                                                                                                                                                                                                                                  | R                                                                                                                                                                                                                          | R                                                                                                                                                                                                                                                                    | R                                                                                                                        | R            | R          | R    | Reset Value  |

|----|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------|------------|------|--------------|

| Ιſ | -                       | -                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                    | IN3                                                                                                                      | IN2          | IN1        | EP0  | 00000000     |

|    | Bit7                    | Bit6                                                                                                                                                                                                                                                                                                               | Bit5                                                                                                                                                                                                                       | Bit4                                                                                                                                                                                                                                                                 | Bit3                                                                                                                     | Bit2         | Bit1       | Bit0 | USB Address: |

|    |                         |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                      |                                                                                                                          |              |            |      | 0x02         |

| E  | Bit2:<br>Bit1:<br>Bit0: | Unused. Rea<br>IN3: IN Endp<br>This bit is cle<br>0: IN Endpoi<br>1: IN Endpoi<br>IN2: IN Endpoi<br>1: IN Endpoi<br>1: IN Endpoi<br>1: IN Endpoi<br>1: IN Endpoi<br>2: IN Endpoi<br>1: IN Endpoi<br>2: IN Endpoi<br>1: IN Endpoi<br>2: IN Endpoi<br>2: IN Endpoi<br>1: IN Endpoi<br>2: Endpoint (<br>1: Endpoint ( | point 3 Inter<br>pared when<br>nt 3 interrup<br>nt 3 interrup<br>ooint 2 Inter<br>point 2 Interrup<br>nt 2 interrup<br>ooint 1 Interrup<br>nt 1 interrup<br>nt 1 interrup<br>nt 0 Interrup<br>pared when<br>0 interrupt in | rupt-pendin<br>software re<br>ot inactive.<br>rupt-pendin<br>software re<br>ot inactive.<br>ot active.<br>rupt-pendin<br>software re<br>ot inactive.<br>ot active.<br>ot active.<br>ot active.<br>ot active.<br>ot active.<br>ot active.<br>ot active.<br>ot active. | ig Flag<br>eads the IN <sup>7</sup><br>g Flag<br>eads the IN <sup>7</sup><br>ig Flag<br>eads the IN <sup>7</sup><br>Flag | IINT registe | er.<br>er. |      |              |

## USB Register Definition 16.12. OUT1INT: USB0 Out Endpoint Interrupt

| R     | R                                                                                                                                                                                                                                                                      | R    | R    | R    | R    | R    | R    | Reset Value |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------------|

| -     | -                                                                                                                                                                                                                                                                      | -    | -    | OUT3 | OUT2 | OUT1 | -    | 00000000    |

| Bit7  | Bit6                                                                                                                                                                                                                                                                   | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | USB Address |

|       |                                                                                                                                                                                                                                                                        |      |      |      |      |      |      | 0x04        |

|       |                                                                                                                                                                                                                                                                        |      |      |      |      |      |      |             |

|       | s7–4: Unused. Read = 0000b. Write = don't care.                                                                                                                                                                                                                        |      |      |      |      |      |      |             |

| Bit3: | OUT3: OUT Endpoint 3 Interrupt-pending Flag                                                                                                                                                                                                                            |      |      |      |      |      |      |             |

|       | This bit is cleared when software reads the OUT1INT register.                                                                                                                                                                                                          |      |      |      |      |      |      |             |

|       | 0: OUT Endpoint 3 interrupt inactive.                                                                                                                                                                                                                                  |      |      |      |      |      |      |             |

|       | 1: OUT Endpoint 3 interrupt active.                                                                                                                                                                                                                                    |      |      |      |      |      |      |             |

| Bit2: | OUT2: OUT Endpoint 2 Interrupt-pending Flag                                                                                                                                                                                                                            |      |      |      |      |      |      |             |

|       | This bit is cleared when software reads the OUT1INT register.<br>0: OUT Endpoint 2 interrupt inactive.                                                                                                                                                                 |      |      |      |      |      |      |             |

|       |                                                                                                                                                                                                                                                                        |      |      |      |      |      |      |             |

|       | <ol> <li>OUT Endpoint 2 interrupt active.</li> <li>OUT1: OUT Endpoint 1 Interrupt-pending Flag</li> <li>This bit is cleared when software reads the OUT1INT register.</li> <li>OUT Endpoint 1 interrupt inactive.</li> <li>OUT Endpoint 1 interrupt active.</li> </ol> |      |      |      |      |      |      |             |

| Bit1: |                                                                                                                                                                                                                                                                        |      |      |      |      |      |      |             |

|       |                                                                                                                                                                                                                                                                        |      |      |      |      |      |      |             |

|       |                                                                                                                                                                                                                                                                        |      |      |      |      |      |      |             |

|       |                                                                                                                                                                                                                                                                        |      |      |      |      |      |      |             |

| Bit0: | Unused. Read = 0; Write = don't care.                                                                                                                                                                                                                                  |      |      |      |      |      |      |             |

|       |                                                                                                                                                                                                                                                                        |      |      |      |      |      |      |             |

### 17.3.2. Clock Low Extension