#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 48MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                           |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                    |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-LQFP                                                         |

| Supplier Device Package    | 32-LQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f34d-gqr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 11.2 Dower Foil Deast ()/DD Manitar                             | 100   |

|-----------------------------------------------------------------|-------|

| 11.2.Power-Fail Reset / VDD Monitor                             |       |

| 11.3.External Reset                                             |       |

| 11.4.Missing Clock Detector Reset                               |       |

| 11.5.Comparator0 Reset                                          |       |

| 11.6.PCA Watchdog Timer Reset                                   |       |

| 11.7.Flash Error Reset                                          |       |

| 11.8.Software Reset                                             |       |

| 11.9.USB Reset                                                  |       |

| 12. Flash Memory                                                |       |

| 12.1.Programming The Flash Memory                               |       |

| 12.1.1.Flash Lock and Key Functions                             |       |

| 12.1.2.Flash Erase Procedure                                    |       |

| 12.1.3.Flash Write Procedure                                    |       |

| 12.2.Non-Volatile Data Storage                                  |       |

| 12.3.Security Options                                           |       |

| 13. External Data Memory Interface and On-Chip XRAM             |       |

| 13.1.Accessing XRAM                                             |       |

| 13.1.1.16-Bit MOVX Example                                      |       |

| 13.1.2.8-Bit MOVX Example                                       |       |

| 13.2.Accessing USB FIFO Space                                   |       |

| 13.3.Configuring the External Memory Interface                  | . 116 |

| 13.4.Port Configuration                                         | . 116 |

| 13.5.Multiplexed and Non-multiplexed Selection                  |       |

| 13.5.1.Multiplexed Configuration                                | . 119 |

| 13.5.2.Non-multiplexed Configuration                            | . 120 |

| 13.6.Memory Mode Selection                                      |       |

| 13.6.1.Internal XRAM Only                                       | . 121 |

| 13.6.2.Split Mode without Bank Select                           | . 121 |

| 13.6.3.Split Mode with Bank Select                              | . 122 |

| 13.6.4.External Only                                            |       |

| 13.7.Timing                                                     | . 122 |

| 13.7.1.Non-multiplexed Mode                                     | . 124 |

| 13.7.2.Multiplexed Mode                                         | . 127 |

| 14. Oscillators                                                 |       |

| 14.1.Programmable Internal High-Frequency (H-F) Oscillator      | . 132 |

| 14.1.1.Internal H-F Oscillator Suspend Mode                     |       |

| 14.2.Programmable Internal Low-Frequency (L-F) Oscillator       |       |

| 14.2.1.Calibrating the Internal L-F Oscillator                  |       |

| 14.3.External Oscillator Drive Circuit                          |       |

| 14.3.1.Clocking Timers Directly Through the External Oscillator |       |

| 14.3.2.External Crystal Example                                 |       |

| 14.3.3.External RC Example                                      |       |

| 14.3.4.External Capacitor Example                               |       |

| 14.4.4x Clock Multiplier                                        |       |

| 14.5.System and USB Clock Selection                             |       |

|                                                                 | 00    |

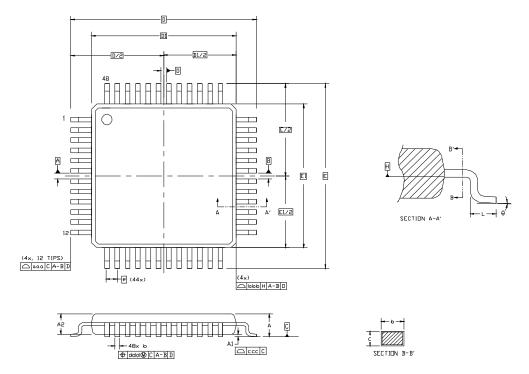

| Table 4.2. TWFF-40 Fackage Dimensions |                                                         |                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|---------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Min                                   | Nom                                                     | Max                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| —                                     | —                                                       | 1.20                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 0.05                                  | —                                                       | 0.15                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 0.95                                  | 1.00                                                    | 1.05                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 0.17                                  | 0.22                                                    | 0.27                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 0.09                                  | —                                                       | 0.20                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                                       | 9.00 BSC                                                |                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                                       | 7.00 BSC                                                |                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                                       | 0.50 BSC                                                |                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                                       | 9.00 BSC                                                |                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                                       | 7.00 BSC                                                |                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0.45                                  | 0.60                                                    | 0.75                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                                       | 0.20                                                    |                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                                       | 0.20                                                    |                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                                       | 0.08                                                    |                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                                       | 0.08                                                    |                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0°                                    | 3.5°                                                    | 7°                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                                       | Min<br><br>0.05<br>0.95<br>0.17<br>0.09<br><br>0.45<br> | Min         Nom               0.05            0.95         1.00           0.17         0.22           0.09            9.00 BSC         7.00 BSC           0.50 BSC         9.00 BSC           0.45         0.60           0.20         0.20           0.08         0.08 |  |  |  |  |  |

### Table 4.2. TQFP-48 Package Dimensions

#### Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MS-026, variation ABC.

**4.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

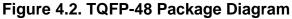

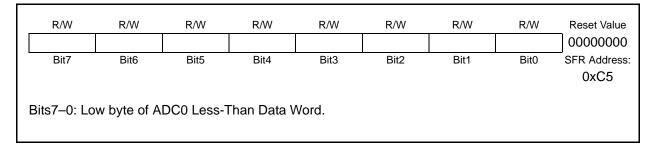

## SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte

## SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte

| R/W      | R/W        | R/W            | R/W          | R/W           | R/W        | R/W        | R/W    | Reset Value  |

|----------|------------|----------------|--------------|---------------|------------|------------|--------|--------------|

| -        | -          | CP0RIE         | CP0FIE       | -             | -          | CP0MD1     | CP0MD0 | 00000010     |

| Bit7     | Bit6       | Bit5           | Bit4         | Bit3          | Bit2       | Bit1       | Bit0   | SFR Address: |

|          |            |                |              |               |            |            |        | 0x9D         |

| Bits7–6: | UNUSED     | Read = 00b.    | Write = dor  | i't care      |            |            |        |              |

| Bit5:    | CPORIE: C  | omparator0     | Risina-Edae  | e Interrupt E | nable.     |            |        |              |

|          |            | ator0 rising-e |              | •             |            |            |        |              |

|          |            | ator0 rising-e | • •          |               |            |            |        |              |

| Bit4:    |            | omparator0     | • •          |               | nable.     |            |        |              |

|          | 0: Compara | ator0 falling- | edge interru | pt disabled.  |            |            |        |              |

|          | 1: Compara | ator0 falling- | edge interru | pt enabled.   |            |            |        |              |

| Bits3–2: | UNUSED.    | Read = 00b.    | Write = dor  | i't care.     |            |            |        |              |

| Bits1–0: | CP0MD1-0   | CP0MD0: Co     | omparator0 l | Mode Selec    | t          |            |        |              |

|          | These bits | select the re  | sponse time  | e for Compa   | rator0.    |            |        |              |

|          | Mode       | CP0MD1         | CP0MD0       | CP0 Res       | oonse Time | <b>e</b> * |        |              |

|          | 0          | 0              | 0            |               | Response   |            |        |              |

|          | 1          | 0              | 1            |               |            |            |        |              |

|          | 2          | 1              | 0            |               |            |            |        |              |

|          | 3          | 1              | 1            | Lowe          | st Power   |            |        |              |

|          | L          |                |              |               |            | I          |        |              |

|          |            |                |              |               |            |            |        |              |

### SFR Definition 7.3. CPT0MD: Comparator0 Mode Selection

| Table 9.1. CIP-51 | Instruction | Set Summary | (Continued) |

|-------------------|-------------|-------------|-------------|

|                   |             |             |             |

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

|                      | Boolean Manipulation                                |       | 1               |

| CLR C                | Clear Carry                                         | 1     | 1               |

| CLR bit              | Clear direct bit                                    | 2     | 2               |

| SETB C               | Set Carry                                           | 1     | 1               |

| SETB bit             | Set direct bit                                      | 2     | 2               |

| CPL C                | Complement Carry                                    | 1     | 1               |

| CPL bit              | Complement direct bit                               | 2     | 2               |

| ANL C, bit           | AND direct bit to Carry                             | 2     | 2               |

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |

| JC rel               | Jump if Carry is set                                | 2     | 2/4             |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/4             |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/5             |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/5             |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3     | 3/5             |

|                      | Program Branching                                   |       |                 |

| ACALL addr11         | Absolute subroutine call                            | 2     | 4               |

| LCALL addr16         | Long subroutine call                                | 3     | 5               |

| RET                  | Return from subroutine                              | 1     | 6               |

| RETI                 | Return from interrupt                               | 1     | 6               |

| AJMP addr11          | Absolute jump                                       | 2     | 4               |

| LJMP addr16          | Long jump                                           | 3     | 5               |

| SJMP rel             | Short jump (relative address)                       | 2     | 4               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 4               |

| JZ rel               | Jump if A equals zero                               | 2     | 2/4             |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/4             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 3/5             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/5             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/5             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/6             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/4             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/5             |

| NOP                  | No operation                                        | 1     | 1               |

## 10. Prefetch Engine

The 48 MHz versions of the C8051F34x family of devices incorporate a 2-byte prefetch engine. Because the access time of the FLASH memory is 40 ns, and the minimum instruction time is roughly 20 ns, the prefetch engine is necessary for full-speed code execution. Instructions are read from FLASH memory two bytes at a time by the prefetch engine, and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine allows instructions to be executed at full speed. When a code branch occurs, the processor may be stalled for up to two clock cycles while the next set of code bytes is retrieved from FLASH memory. The FLRT bit (FLSCL.4) determines how many clock cycles are used to read each set of two code bytes from FLASH. When operating from a system clock of 25 MHz or less, the FLRT bit should be set to '0' so that the prefetch engine takes only one clock cycle for each read. When operating with a system clock of greater than 25 MHz (up to 48 MHz), the FLRT bit should be set to '1', so that each prefetch code read lasts for two clock cycles.

| R         | R              | R/W           | R             | R          | R           | R    | R/W         | Reset Value |

|-----------|----------------|---------------|---------------|------------|-------------|------|-------------|-------------|

|           |                | PFEN          |               |            |             |      | FLBWE       | 00100000    |

| Bit7      | Bit6           | Bit5          | Bit4          | Bit3       | Bit2        | Bit1 | Bit0        | 3           |

|           |                |               |               |            |             |      | SFR Address | 0xAF        |

| Bits 7–6: | Unused. Rea    | ad = 00b; W   | /rite = Don'i | t Care     |             |      |             |             |

| Bit 5:    | PFEN: Prefe    | tch Enable    |               |            |             |      |             |             |

|           | This bit enab  | oles the pre  | fetch engine  | e.         |             |      |             |             |

|           | 0: Prefetch e  | engine is dis | abled.        |            |             |      |             |             |

|           | 1: Prefetch e  | engine is en  | abled.        |            |             |      |             |             |

| Bits 4–1: | Unused. Rea    | ad = 0000b:   | Write = Do    | on't Care  |             |      |             |             |

| Bit 0:    | FLBWE: FLA     |               |               |            |             |      |             |             |

|           | This bit allow | vs block wri  | tes to FLAS   | SH memory  | from softwa | are. |             |             |

|           | 0: Each byte   |               |               |            |             |      |             |             |

|           | 1: FLASH by    |               |               |            |             | any. |             |             |

|           | 1.1 2/(0110)   |               | ser in group  | 05 01 100. |             |      |             |             |

|           |                |               |               |            |             |      |             |             |

## SFR Definition 10.1. PFE0CN: Prefetch Engine Control

| R/W                        | R/W                                                                                                                                                                                                                            | R/W                                                                                                                                                                                         | R/W                                                                                                                                                                  | R/W                                                                                                                                                   | R/W                                                                         | R/W                                                                   | R/W                                                                | Reset Value                                   |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------|

| -                          | -                                                                                                                                                                                                                              | -                                                                                                                                                                                           | -                                                                                                                                                                    | -                                                                                                                                                     | Reserved                                                                    | PSEE                                                                  | PSWE                                                               | 00000000                                      |

| Bit7                       | Bit6                                                                                                                                                                                                                           | Bit5                                                                                                                                                                                        | Bit4                                                                                                                                                                 | Bit3                                                                                                                                                  | Bit2                                                                        | Bit1                                                                  | Bit0                                                               | SFR Address:                                  |

|                            |                                                                                                                                                                                                                                |                                                                                                                                                                                             |                                                                                                                                                                      |                                                                                                                                                       |                                                                             |                                                                       |                                                                    | 0x8F                                          |

| Bits7–3:<br>Bit2:<br>Bit1: | Unused: Rea<br>Reserved. R<br>PSEE: Progr<br>Setting this b<br>to be erased<br>Flash memo<br>tion address<br>0: Flash prog<br>1: Flash prog<br>Setting this b<br>write instruct<br>0: Writes to F<br>1: Writes to F<br>memory. | ead = 0b. N<br>ram Store E<br>bit (in combi<br>. If this bit is<br>ry using the<br>ed by the N<br>gram memo<br>gram memo<br>gram Store N<br>bit allows we<br>cion. The Fla<br>Flash program | Aust Write =<br>rase Enabl<br>nation with<br>s logic 1 an<br>MOVX instru-<br>ory erasure<br>ory erasure<br>Vrite Enabl<br>riting a byte<br>ash locatior<br>am memory | = 0b.<br>e<br>PSWE) allo<br>d Flash writ<br>truction will<br>ction. The v<br>disabled.<br>enabled.<br>e<br>of data to f<br>a should be<br>v disabled. | tes are enab<br>erase the e<br>value of the<br>the Flash pro<br>erased befo | oled (PSWE<br>ntire page<br>data byte w<br>ogram men<br>ore writing o | is logic 1)<br>that contair<br>vritten does<br>nory using<br>data. | , a write to<br>as the loca-<br>a not matter. |

## SFR Definition 12.2. FLKEY: Flash Lock and Key

| R/W     | R/W                                                                                                                                                                                                                          | R/W                                                                                                                                                 | R/W                                                                                                                                                       | R/W                                                                                                                | R/W                                                                              | R/W                                            | R/W                                 | Reset Value                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------|---------------------------------------------|

| Bit7    | Bit6                                                                                                                                                                                                                         | Bit5                                                                                                                                                | Bit4                                                                                                                                                      | Bit3                                                                                                               | Bit2                                                                             | Bit1                                           | Bit0                                | SFR Address:<br>0xB7                        |

| Bits-0: | FLKEY: Flas<br>Write:<br>This register<br>remains lock<br>timing of the<br>must be writt<br>system reset<br>codes have b<br>Read:<br>When read, b<br>00: Flash is w<br>01: The first<br>10: Flash is with<br>11: Flash write | must be w<br>ed until this<br>writes does<br>en for each<br>if the wron<br>been written<br>bits 1-0 ind<br>write/erase<br>key code h<br>unlocked (v | ritten to before<br>seregister is<br>a not matter,<br>a Flash write<br>and codes are<br>an correctly.<br>acate the cu<br>locked.<br>as been writes/erases | ore Flash w<br>written to w<br>as long as<br>or erase c<br>written or<br>rrent Flash<br>tten (0xA5)<br>s allowed). | vith the follow<br>the codes a<br>operation. Fla<br>if a Flash op<br>lock state. | wing key coo<br>re written in<br>ash will be l | des: 0xA5<br>order. Th<br>locked un | 5, 0xF1. The<br>e key codes<br>til the next |

| SFR Definition 14.2. OSCICL: Internal H-F Oscillator C | Calibration |

|--------------------------------------------------------|-------------|

|--------------------------------------------------------|-------------|

| R/W<br>- | R/W                                                                             | R/W<br>-                                    | R/W                         | R/W                           | R/W<br>OSCCAL | R/W          | R/W        | Reset Value         |

|----------|---------------------------------------------------------------------------------|---------------------------------------------|-----------------------------|-------------------------------|---------------|--------------|------------|---------------------|

| Bit7     | Bit6                                                                            | Bit5                                        | Bit4                        | Bit3                          | Bit2          | Bit1         | Bit0       | SFR Address<br>0xB3 |

| Bits4–0: | OSCCAL: OF<br>These bits de<br>operates at it<br>ting. The cor<br>tor frequency | etermine th<br>ts fastest s<br>ntents of th | e internal H<br>etting. Whe | I-F oscillato<br>n set to 111 | 11b, the osc  | illator oper | ates at is | slowest set-        |

|          |                                                                                 |                                             |                             |                               |               |              |            |                     |

## 14.2. Programmable Internal Low-Frequency (L-F) Oscillator

The C8051F340/1/2/3/4/5/8/9/C/D devices include a programmable internal oscillator which operates at a nominal frequency of 80 kHz. The low-frequency oscillator circuit includes a divider that can be changed to divide the clock by 1, 2, 4, or 8, using the OSCLD bits in the OSCLCN register (see SFR Definition 14.3). Additionally, the OSCLF bits (OSCLCN5:2) can be used to adjust the oscillator's output frequency.

### 14.2.1. Calibrating the Internal L-F Oscillator

Timers 2 and 3 include capture functions that can be used to capture the oscillator frequency, when running from a known time base. When either Timer 2 or Timer 3 is configured for L-F Oscillator Capture Mode, a falling edge (Timer 2) or rising edge (Timer 3) of the low-frequency oscillator's output will cause a capture event on the corresponding timer. As a capture event occurs, the current timer value (TMRnH:TMRnL) is copied into the timer reload registers (TMRnRLH:TMRnRLL). By recording the difference between two successive timer capture values, the low-frequency oscillator's period can be calculated. The OSCLF bits can then be adjusted to produce the desired oscillator period.

| R/W      | R/W                                                                                                                                                                                                                                                                                                                                                                                      | R/W                                                                                                 | R/W  | R/W  | R/W  | R/W    | R/W  | Reset Value          |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|--------|------|----------------------|--|--|

| WEAKP    | UD XBARE                                                                                                                                                                                                                                                                                                                                                                                 | T1E                                                                                                 | T0E  | ECIE |      | PCA0ME |      | 00000000             |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                                                                                                                                                                                     | Bit5                                                                                                | Bit4 | Bit3 | Bit2 | Bit1   | Bit0 | SFR Address:<br>0xE2 |  |  |

| Bit7:    | WEAKPUD: Port I/O Weak Pull-up Disable.<br>0: Weak Pull-ups enabled (except for Ports whose I/O are configured as analog input or<br>push-pull output).<br>1: Weak Pull-ups disabled.                                                                                                                                                                                                    |                                                                                                     |      |      |      |        |      |                      |  |  |

| Bit6:    | 0: Crossbar o                                                                                                                                                                                                                                                                                                                                                                            | XBARE: Crossbar Enable.<br>0: Crossbar disabled; all Port drivers disabled.<br>1: Crossbar enabled. |      |      |      |        |      |                      |  |  |

| Bit5:    | T1E: T1 Ena<br>0: T1 unavail<br>1: T1 routed                                                                                                                                                                                                                                                                                                                                             | able at Port                                                                                        | pin. |      |      |        |      |                      |  |  |

| Bit4:    | T0E: T0 Ena<br>0: T0 unavail<br>1: T0 routed                                                                                                                                                                                                                                                                                                                                             | able at Port                                                                                        | pin. |      |      |        |      |                      |  |  |

| Bit3:    | ECIE: PCA0 External Counter Input Enable<br>0: ECI unavailable at Port pin.                                                                                                                                                                                                                                                                                                              |                                                                                                     |      |      |      |        |      |                      |  |  |

| Bits2–0: | 1: ECI routed to Port pin.<br>PCA0ME: PCA Module I/O Enable Bits.<br>000: All PCA I/O unavailable at Port pins.<br>001: CEX0 routed to Port pin.<br>010: CEX0, CEX1 routed to Port pins.<br>011: CEX0, CEX1, CEX2 routed to Port pins.<br>100: CEX0, CEX1, CEX2, CEX3 routed to Port pins.<br>101: CEX0, CEX1, CEX2, CEX3, CEX4 routed to Port pins.<br>110: Reserved.<br>111: Reserved. |                                                                                                     |      |      |      |        |      |                      |  |  |

## SFR Definition 15.3. XBR2: Port I/O Crossbar Register 2

## SFR Definition 15.11. P1SKIP: Port1 Skip

| R/W          | R/W                                                                                              | R/W                                                     | R/W                                                        | R/W                                                      | R/W                                                     | R/W                   | R/W  | Reset Value 00000000          |

|--------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|-----------------------|------|-------------------------------|

| Bit7         | Bit6                                                                                             | Bit5                                                    | Bit4                                                       | Bit3                                                     | Bit2                                                    | Bit1                  | Bit0 | SFR Address:<br>0xD5          |

| ר<br>וג<br>נ | P1SKIP[7:0]:<br>These bits se<br>og inputs (fo<br>ator circuit, (<br>): Correspon<br>: Correspon | elect Port p<br>r ADC or C<br>CNVSTR in<br>iding P1.n p | ins to be sk<br>omparator)<br>put) should<br>pin is not sk | ipped by the<br>or used as<br>be skipped<br>ipped by the | e Crossbar<br>special fund<br>by the Cro<br>e Crossbar. | ctions (VRE<br>ssbar. |      | sed as ana-<br>xternal oscil- |

## SFR Definition 15.12. P2: Port2 Latch

| R/W<br>P2.7 | R/W<br>P2.6                                                                                                                   | R/W<br>P2.5                                                                 | R/W<br>P2.4                               | R/W<br>P2.3                  | R/W<br>P2.2 | R/W<br>P2.1 | R/W<br>P2.0 | Reset Value<br>11111111 |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------|------------------------------|-------------|-------------|-------------|-------------------------|--|

| Bit7        | Bit6                                                                                                                          | Bit5                                                                        | Bit4                                      | Bit3                         | Bit2        | Bit1        | Bit0        | SFR Address:            |  |

|             | (bit addressable) 0xA0                                                                                                        |                                                                             |                                           |                              |             |             |             |                         |  |

| Bits7–0:    | P2.[7:0]<br>Write - Outpu<br>0: Logic Low<br>1: Logic High<br>Read - Alwa<br>pin when cou<br>0: P2.n pin is<br>1: P2.n pin is | o Output.<br>In Output (hi<br>ys reads '0'<br>Infigured as<br>Is logic low. | gh impedar<br>if selected<br>digital inpu | nce if corres<br>as analog i | ponding P2  | 2MDOUT.n l  | bit = 0).   |                         |  |

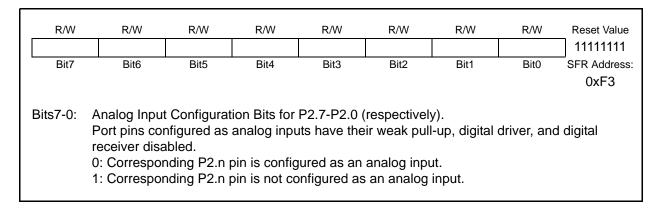

## SFR Definition 15.13. P2MDIN: Port2 Input Mode

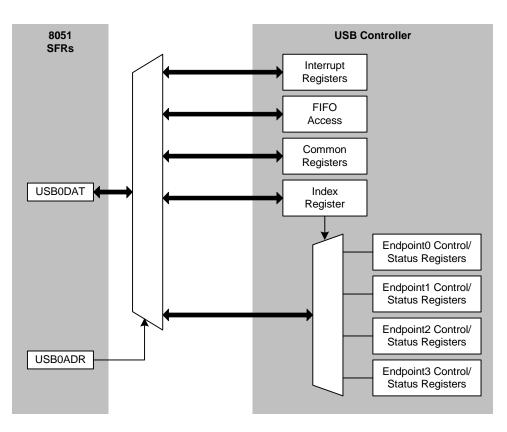

by reads/writes of the USB0DAT register. See Figure 16.2.

Endpoint control/status registers are accessed by first writing the USB register INDEX with the target endpoint number. Once the target endpoint number is written to the INDEX register, the control/status registers associated with the target endpoint may be accessed. See the "Indexed Registers" section of Table 16.2 for a list of endpoint control/status registers.

Important Note: The USB clock must be active when accessing USB registers.

Figure 16.2. USB0 Register Access Scheme

The E0CNT register (USB Register Definition 16.18) holds the number of received data bytes in the Endpoint0 FIFO.

Hardware will automatically detect protocol errors and send a STALL condition in response. Firmware may force a STALL condition to abort the current transfer. When a STALL condition is generated, the STSTL bit will be set to '1' and an interrupt generated. The following conditions will cause hardware to generate a STALL condition:

- 1. The host sends an OUT token during a OUT data phase after the DATAEND bit has been set to '1'.

- 2. The host sends an IN token during an IN data phase after the DATAEND bit has been set to '1'.

- 3. The host sends a packet that exceeds the maximum packet size for Endpoint0.

- 4. The host sends a non-zero length DATA1 packet during the status phase of an IN transaction.

- 5. Firmware sets the SDSTL bit (E0CSR.5) to '1'.

#### 16.10.1.Endpoint0 SETUP Transactions

All control transfers must begin with a SETUP packet. SETUP packets are similar to OUT packets, containing an 8-byte data field sent by the host. Any SETUP packet containing a command field of anything other than 8 bytes will be automatically rejected by USB0. An Endpoint0 interrupt is generated when the data from a SETUP packet is loaded into the Endpoint0 FIFO. Software should unload the command from the Endpoint0 FIFO, decode the command, perform any necessary tasks, and set the SOPRDY bit to indicate that it has serviced the OUT packet.

#### 16.10.2.Endpoint0 IN Transactions

When a SETUP request is received that requires USB0 to transmit data to the host, one or more IN requests will be sent by the host. For the first IN transaction, firmware should load an IN packet into the Endpoint0 FIFO, and set the INPRDY bit (E0CSR.1). An interrupt will be generated when an IN packet is transmitted successfully. Note that no interrupt will be generated if an IN request is received before firmware has loaded a packet into the Endpoint0 FIFO. If the requested data exceeds the maximum packet size for Endpoint0 (as reported to the host), the data should be split into multiple packets; each packet should be of the maximum packet size excluding the last (residual) packet. If the requested data is an integer multiple of the maximum packet size for Endpoint0, the last data packet should be a zero-length packet signaling the end of the transfer. Firmware should set the DATAEND bit to '1' after loading into the Endpoint0 FIFO the last data packet for a transfer.

Upon reception of the first IN token for a particular control transfer, Endpoint0 is said to be in Transmit Mode. In this mode, only IN tokens should be sent by the host to Endpoint0. The SUEND bit (E0CSR.4) is set to '1' if a SETUP or OUT token is received while Endpoint0 is in Transmit Mode.

Endpoint0 will remain in Transmit Mode until any of the following occur:

- 1. USB0 receives an Endpoint0 SETUP or OUT token.

- 2. Firmware sends a packet less than the maximum Endpoint0 packet size.

- 3. Firmware sends a zero-length packet.

Firmware should set the DATAEND bit (E0CSR.3) to '1' when performing (2) and (3) above.

The SIE will transmit a NAK in response to an IN token if there is no packet ready in the IN FIFO (INPRDY = '0').

Writing '1' to INPRDY without writing any data to the endpoint FIFO will cause a zero-length packet to be transmitted upon reception of the next IN token.

A Bulk or Interrupt pipe can be shut down (or Halted) by writing '1' to the SDSTL bit (EINCSRL.4). While SDSTL = '1', hardware will respond to all IN requests with a STALL condition. Each time hardware generates a STALL condition, an interrupt will be generated and the STSTL bit (EINCSRL.5) set to '1'. The STSTL bit must be reset to '0' by firmware.

Hardware will automatically reset INPRDY to '0' when a packet slot is open in the endpoint FIFO. Note that if double buffering is enabled for the target endpoint, it is possible for firmware to load two packets into the IN FIFO at a time. In this case, hardware will reset INPRDY to '0' immediately after firmware loads the first packet into the FIFO and sets INPRDY to '1'. An interrupt will not be generated in this case; an interrupt will only be generated when a data packet is transmitted.

When firmware writes '1' to the FCDT bit (EINCSRH.3), the data toggle for each IN packet will be toggled continuously, regardless of the handshake received from the host. This feature is typically used by Interrupt endpoints functioning as rate feedback communication for Isochronous endpoints. When FCDT = '0', the data toggle bit will only be toggled when an ACK is sent from the host in response to an IN packet.

#### 16.12.2.Endpoints1-3 IN Isochronous Mode

When the ISO bit (EINCSRH.6) is set to '1', the target endpoint operates in Isochronous (ISO) mode. Once an endpoint has been configured for ISO IN mode, the host will send one IN token (data request) per frame; the location of data within each frame may vary. Because of this, it is recommended that double buffering be enabled for ISO IN endpoints.

Hardware will automatically reset INPRDY (EINCSRL.0) to '0' when a packet slot is open in the endpoint FIFO. Note that if double buffering is enabled for the target endpoint, it is possible for firmware to load two packets into the IN FIFO at a time. In this case, hardware will reset INPRDY to '0' immediately after firmware loads the first packet into the FIFO and sets INPRDY to '1'. An interrupt will not be generated in this case; an interrupt will only be generated when a data packet is transmitted.

If there is not a data packet ready in the endpoint FIFO when USB0 receives an IN token from the host, USB0 will transmit a zero-length data packet and set the UNDRUN bit (EINCSRL.2) to '1'.

The ISO Update feature (see **Section 16.7**) can be useful in starting a double buffered ISO IN endpoint. If the host has already set up the ISO IN pipe (has begun transmitting IN tokens) when firmware writes the first data packet to the endpoint FIFO, the next IN token may arrive and the first data packet sent before firmware has written the second (double buffered) data packet to the FIFO. The ISO Update feature ensures that any data packet written to the endpoint FIFO will not be transmitted during the current frame; the packet will only be sent after a SOF signal has been received.

#### 17.3.2. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 17.3.3. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMB0CF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 17.3.4. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50 µs, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods. If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. Note that a clock source is required for free timeout detection, even in a slave-only implementation.

### 17.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

SMBus interrupts are generated for each data byte or slave address that is transferred. When transmitting, this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data, this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. See **Section "17.5. SMBus Transfer Modes" on page 198** for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in **Section "17.4.2. SMB0CN Control Register" on page 195**; Table 17.4 provides a quick SMB0CN decoding reference.

### 20.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 20.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 20.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

## 20.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

Note that all of the following bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- 2. The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- 3. The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

### 20.5. Serial Clock Timing

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 20.5. For slave mode, the clock and data relationships are shown in Figure 20.6 and Figure 20.7.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 20.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 20.5. Master Mode Data/Clock Timing

### SFR Definition 20.2. SPI0CN: SPI0 Control

| R/W<br>SPIF | R/W<br>WCOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W<br>MODF          | R/W         | R/W<br>NSSMD1 | R/W  | R<br>TXBMT | R/W<br>SPIEN | Reset Value 00000110 |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|---------------|------|------------|--------------|----------------------|--|--|--|

| Bit7        | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit5                 | Bit4        | Bit3          | Bit2 | Bit1       | Bit0         | Bit<br>Addressable   |  |  |  |

|             | SFR Address: 0xF8                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |             |               |      |            |              |                      |  |  |  |

| Bit 7:      | This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enabled, setting this bit causes the CPU to vector to the SPI0 interrupt service routine. This bit is not                                                                                                                                                                                                                                                                                               |                      |             |               |      |            |              |                      |  |  |  |

| Bit 6:      | automatically cleared by hardware. It must be cleared by software.<br>WCOL: Write Collision Flag.<br>This bit is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not<br>been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be<br>ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes. It                                                                                                |                      |             |               |      |            |              |                      |  |  |  |

| Bit 5:      | must be cleared by software.<br>MODF: Mode Fault Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when a master mode<br>collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01). This bit is not auto-<br>matically cleared by hardware. It must be cleared by software.                                                                                                                                                                             |                      |             |               |      |            |              |                      |  |  |  |

| Bit 4:      | RXOVRN: Receive Overrun Flag (Slave Mode only).<br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when the receive buf-<br>fer still holds unread data from a previous transfer and the last bit of the current transfer is<br>shifted into the SPI0 shift register. This bit is not automatically cleared by hardware. It must<br>be cleared by software.                                                                                                             |                      |             |               |      |            |              |                      |  |  |  |

| Bits 3–2:   | NSSMD1–NSSMD0: Slave Select Mode.<br>Selects between the following NSS operation modes:<br>(See Section "20.2. SPI0 Master Mode Operation" on page 224 and Section "20.3. SPI0<br>Slave Mode Operation" on page 226).<br>00: 3-Wire Slave or 3-wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is always an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the device and will |                      |             |               |      |            |              |                      |  |  |  |

| Bit 1:      | assume the value of NSSMD0.<br>TXBMT: Transmit Buffer Empty.<br>This bit will be set to logic 0 when new data has been written to the transmit buffer. When<br>data in the transmit buffer is transferred to the SPI shift register, this bit will be set to logic 1,<br>indicating that it is safe to write a new byte to the transmit buffer.                                                                                                                                                 |                      |             |               |      |            |              |                      |  |  |  |

| Bit 0:      | SPIEN: SPIC<br>This bit enab<br>0: SPI disab<br>1: SPI enabl                                                                                                                                                                                                                                                                                                                                                                                                                                    | oles/disable<br>led. | es the SPI. |               |      |            |              |                      |  |  |  |

## SFR Definition 21.9. TMR2RLL: Timer 2 Reload Register Low Byte

|   | R/W                                                                                                                                                                                                                    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--------------|--|

|   |                                                                                                                                                                                                                        |      |      |      |      |      |      |      | 0000000      |  |

|   | Bit7                                                                                                                                                                                                                   | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |  |

|   |                                                                                                                                                                                                                        |      |      |      |      |      |      |      | 0xCA         |  |

| E | Bits 7–0: TMR2RLL: Timer 2 Reload Register Low Byte.<br>TMR2RLL holds the low byte of the reload value for Timer 2 when operating in auto-reload<br>mode, or the captured value of the TMR2L register in capture mode. |      |      |      |      |      |      |      |              |  |

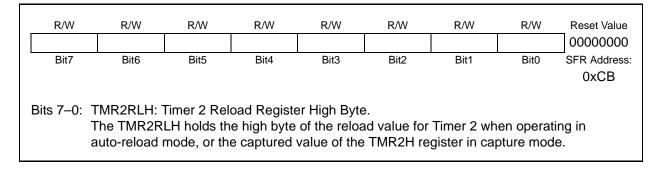

## SFR Definition 21.10. TMR2RLH: Timer 2 Reload Register High Byte

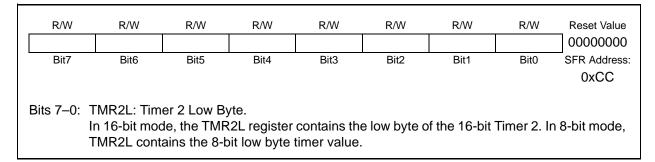

## SFR Definition 21.11. TMR2L: Timer 2 Low Byte

## SFR Definition 21.12. TMR2H Timer 2 High Byte

| R/W  | R/W                                                                                                                                                                                       | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value          |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|----------------------|--|--|--|

| Bit7 | Bit6                                                                                                                                                                                      | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xCD |  |  |  |

|      | Bits 7–0: TMR2H: Timer 2 High Byte.<br>In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8-bit<br>mode, TMR2H contains the 8-bit high byte timer value. |      |      |      |      |      |      |                      |  |  |  |

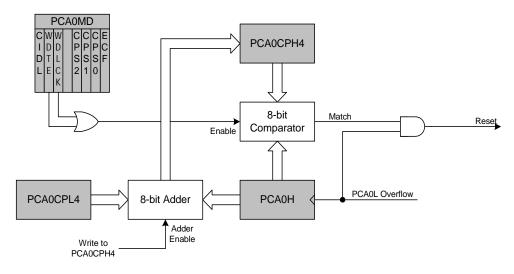

### 22.3. Watchdog Timer Mode

A programmable watchdog timer (WDT) function is available through the PCA Module 4. The WDT is used to generate a reset if the time between writes to the WDT update register (PCA0CPH4) exceed a specified limit. The WDT can be configured and enabled/disabled as needed by software.

With the WDTE and/or WDLCK bits set to '1' in the PCA0MD register, Module 4 operates as a watchdog timer (WDT). The Module 4 high byte is compared to the PCA counter high byte; the Module 4 low byte holds the offset to be used when WDT updates are performed. **The Watchdog Timer is enabled on reset. Writes to some PCA registers are restricted while the Watchdog Timer is enabled.**

#### 22.3.1. Watchdog Timer Operation

While the WDT is enabled:

- PCA counter is forced on.

- Writes to PCA0L and PCA0H are not allowed.

- PCA clock source bits (CPS2-CPS0) are frozen.

- PCA Idle control bit (CIDL) is frozen.

- Module 4 is forced into Watchdog Timer mode.

- Writes to the Module 4 mode register (PCA0CPM4) are disabled.

While the WDT is enabled, writes to the CR bit will not change the PCA counter state; the counter will run until the WDT is disabled. The PCA counter run control (CR) will read zero if the WDT is enabled but user software has not enabled the PCA counter. If a match occurs between PCA0CPH4 and PCA0H while the WDT is enabled, a reset will be generated. To prevent a WDT reset, the WDT may be updated with a write of any value to PCA0CPH4. Upon a PCA0CPH4 write, PCA0H plus the offset held in PCA0CPL4 is loaded into PCA0CPH4 (See Figure 22.10).

## Figure 22.10. PCA Module 4 with Watchdog Timer Enabled

Note that the 8-bit offset held in PCA0CPH4 is compared to the upper byte of the 16-bit PCA counter. This offset value is the number of PCA0L overflows before a reset. Up to 256 PCA clocks may pass before the first PCA0L overflow occurs, depending on the value of the PCA0L when the update is performed. The total offset is then given (in PCA clocks) by Equation 22.4, where PCA0L is the value of the PCA0L register at the time of the update.

| R/W    | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W                       | R/W                 | R/W          | R/W                  | R/W        | R/W   | Reset Value                                        |  |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------|--------------|----------------------|------------|-------|----------------------------------------------------|--|--|--|--|

| PWM16  |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CAPPn                     | CAPNn               | MATn         | TOGn                 | PWMn       | ECCFn | 00000000                                           |  |  |  |  |

| Bit7   | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit5                      | Bit4                | Bit3         | Bit2                 | Bit1       | Bit0  | SFR Address:<br>0xDA, 0xDB,<br>0xDC, 0xDD,<br>0xDE |  |  |  |  |

| PCA0CP | Mn Address:                                                                                                                                                                                                                                                                                                                                                                                                                                     | PCA0C                     | PM2 = 0xD           | C (n = 2), F | PCA0CPM1<br>PCA0CPM3 | · ·        |       |                                                    |  |  |  |  |