Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 232 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-16e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### 4.1.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (1024Tosc) delay after  $\overline{\text{MCLR}}$  is detected high or a wake-up from SLEEP event occurs.

The OST time-out is invoked only for XT and LF oscillator modes on a Power-on Reset or a Wake-up from SLEEP.

The OST counts the oscillator pulses on the OSC1/CLKIN pin. The counter only starts incrementing after the amplitude of the signal reaches the oscillator input thresholds. This delay allows the crystal oscillator or resonator to stabilize before the device exits reset. The length of time-out is a function of the crystal/resonator frequency.

#### 4.1.4 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First the internal POR signal goes high when the POR trip point is reached. If MCLR is high, then both the OST and PWRT timers start. In general the PWRT time-out is longer, except with low frequency crystals/resonators. The total time-out also varies based on oscillator configuration. Table 4-1 shows the times that are associated with the oscillator configuration. Figure 4-2 and Figure 4-3 display these time-out sequences.

If the device voltage is not within electrical specification at the end of a time-out, the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be held low until the voltage is within the device specification. The use of an external RC delay is sufficient for many of these applications.

## TABLE 4-1:TIME-OUT IN VARIOUSSITUATIONS

| Oscillator<br>Configuration | Power-up                            | Wake up<br>from<br>SLEEP | MCLR<br>Reset |

|-----------------------------|-------------------------------------|--------------------------|---------------|

| XT, LF                      | Greater of:<br>96 ms or<br>1024Tosc | 1024Tosc                 | —             |

| EC, RC                      | Greater of:<br>96 ms or<br>1024Tosc |                          | —             |

The time-out sequence begins from the first rising edge of  $\overline{\text{MCLR}}$ .

Table 4-3 shows the reset conditions for some special registers, while Table 4-4 shows the initialization conditions for all the registers. The shaded registers (in Table 4-4) are for all devices except the PIC17C42. In the PIC17C42, the PRODH and PRODL registers are general purpose RAM.

# TABLE 4-2:STATUS BITS AND THEIR<br/>SIGNIFICANCE

| TO | PD | Event                                                                              |

|----|----|------------------------------------------------------------------------------------|

| 1  | 1  | Power-on Reset, MCLR Reset during normal operation, or CLRWDT instruction executed |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP                            |

| 0  | 1  | WDT Reset during normal operation                                                  |

| 0  | 0  | WDT Reset during SLEEP                                                             |

In Figure 4-2, Figure 4-3 and Figure 4-4, TPWRT > TOST, as would be the case in higher frequency crystals. For lower frequency crystals, (i.e., 32 kHz) TOST would be greater.

#### TABLE 4-3: RESET CONDITION FOR THE PROGRAM COUNTER AND THE CPUSTA REGISTER

| Event                                      |                 | PCH:PCL               | CPUSTA | OST Active |

|--------------------------------------------|-----------------|-----------------------|--------|------------|

| Power-on Reset                             |                 | 0000h                 | 11 11  | Yes        |

| MCLR Reset during normal ope               | ration          | 0000h                 | 11 11  | No         |

| MCLR Reset during SLEEP                    |                 | 0000h                 | 11 10  | Yes (2)    |

| WDT Reset during normal operation          | ation           | 0000h                 | 11 01  | No         |

| WDT Reset during SLEEP (3)                 |                 | 0000h                 | 11 00  | Yes (2)    |

| Interrupt wake-up from SLEEP GLINTD is set |                 | PC + 1                | 11 10  | Yes (2)    |

|                                            | GLINTD is clear | PC + 1 <sup>(1)</sup> | 10 10  | Yes (2)    |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0'.

Note 1: On wake-up, this instruction is executed. The instruction at the appropriate interrupt vector is fetched and then executed.

2: The OST is only active when the Oscillator is configured for XT or LF modes.

3: The Program Counter = 0, that is the device branches to the reset vector. This is different from the mid-range devices.

NOTES:

#### 6.2.2.3 TMR0 STATUS/CONTROL REGISTER (T0STA)

This register contains various control bits. Bit7 (INTEDG) is used to control the edge upon which a signal on the RA0/INT pin will set the RB0/INT interrupt flag. The other bits configure the Timer0 prescaler and clock source. (Figure 11-1).

#### FIGURE 6-9: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

| R/W - 0        | R/W - 0                                                                                                                                                                                                                       | R/W - 0                                          | R/W - 0                                                            | R/W - 0    | R/W - 0    | R/W - 0     | U - 0 |                                                                                                       |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------|------------|------------|-------------|-------|-------------------------------------------------------------------------------------------------------|

| INTEDG<br>bit7 | TOSE                                                                                                                                                                                                                          | TOCS                                             | PS3                                                                | PS2        | PS1        | PS0         | bit0  | R = Readable bit<br>W = Writable bit<br>U = Unimplemented,<br>reads as '0'<br>-n = Value at POR reset |

| bit 7:         | INTEDG: RA0/INT Pin Interrupt Edge Select bit<br>This bit selects the edge upon which the interrupt is detected.<br>1 = Rising edge of RA0/INT pin generates interrupt<br>0 = Falling edge of RA0/INT pin generates interrupt |                                                  |                                                                    |            |            |             |       |                                                                                                       |

| bit 6:         |                                                                                                                                                                                                                               | ects the ed<br>S = 0<br>edge of RA<br>edge of RA | ge upon w<br>1/T0CKI pi                                            | hich TMRC  | nts TMR0 a | and/or gene |       | CKIF interrupt<br>CKIF interrupt                                                                      |

| bit 5:         | <b>TOCS</b> : Time<br>This bit sele<br>1 = Internal<br>0 = TOCKI                                                                                                                                                              | ects the clo<br>instruction                      | ock source                                                         | for Timer0 |            |             |       |                                                                                                       |

| bit 4-1:       | PS3:PS0: 7<br>These bits                                                                                                                                                                                                      |                                                  |                                                                    |            | ner0.      |             |       |                                                                                                       |

|                | PS3:PS0                                                                                                                                                                                                                       | Pre                                              | scale Valu                                                         | е          |            |             |       |                                                                                                       |

|                | 0000<br>001<br>0010<br>010<br>0100<br>0101<br>0110<br>0111<br>1xxx                                                                                                                                                            |                                                  | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 |            |            |             |       |                                                                                                       |

| bit 0:         | Unimplem                                                                                                                                                                                                                      | <b>ented</b> : Rea                               | id as '0'                                                          |            |            |             |       |                                                                                                       |

### 9.0 I/O PORTS

The PIC17C4X devices have five I/O ports, PORTA through PORTE. PORTB through PORTE have a corresponding Data Direction Register (DDR), which is used to configure the port pins as inputs or outputs. These five ports are made up of 33 I/O pins. Some of these ports pins are multiplexed with alternate functions.

PORTC, PORTD, and PORTE are multiplexed with the system bus. These pins are configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, these pins are general purpose I/O.

PORTA and PORTB are multiplexed with the peripheral features of the device. These peripheral features are:

- Timer modules

- Capture module

- PWM module

- USART/SCI module

- External Interrupt pin

When some of these peripheral modules are turned on, the port pin will automatically configure to the alternate function. The modules that do this are:

- PWM module

- USART/SCI module

When a pin is automatically configured as an output by a peripheral module, the pins data direction (DDR) bit is unknown. After disabling the peripheral module, the user should re-initialize the DDR bit to the desired configuration.

The other peripheral modules (which require an input) must have their data direction bit configured appropriately.

**Note:** A pin that is a peripheral input, can be configured as an output (DDRx<y> is cleared). The peripheral events will be determined by the action output on the port pin.

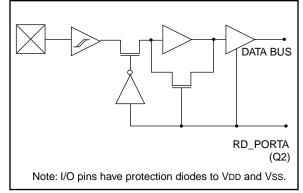

#### 9.1 PORTA Register

PORTA is a 6-bit wide latch. PORTA does not have a corresponding Data Direction Register (DDR).

Reading PORTA reads the status of the pins.

The RA1 pin is multiplexed with TMR0 clock input, and RA4 and RA5 are multiplexed with the USART functions. The control of RA4 and RA5 as outputs is automatically configured by the USART module.

9.1.1 USING RA2, RA3 AS OUTPUTS

The RA2 and RA3 pins are open drain outputs. To use the RA2 or the RA3 pin(s) as output(s), simply write to the PORTA register the desired value. A '0' will cause the pin to drive low, while a '1' will cause the pin to float (hi-impedance). An external pull-up resistor should be used to pull the pin high. Writes to PORTA will not affect the other pins.

| Note: | When using the RA2 or RA3 pin(s) as out-<br>put(s), read-modify-write instructions (such<br>as BCF, BSF, BTG) on PORTA are not rec-<br>ommended.<br>Such operations read the port pins, do the<br>desired operation, and then write this value<br>to the data latch. This may inadvertently<br>cause the RA2 or RA3 pins to switch from<br>input to output (or vice-versa).<br>It is recommended to use a shadow regis-<br>ter for PORTA. Do the bit operations on this<br>shadow register and then move it to<br>PORTA. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### FIGURE 9-1: RA0 AND RA1 BLOCK DIAGRAM

### FIGURE 13-2: RCSTA REGISTER (ADDRESS: 13h, BANK 0)

| SPEN   | N.W0         R/W - 0         R/W - 0         U - 0         R - 0         R - 0         R - x           RX9         SREN         CREN         —         FERR         OERR         RX9D         R = Readable bit                                                                                                                                             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit7   | bit 0<br>W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)                                                                                                                                                                                                                                                                                      |

| bit 7: | <b>SPEN</b> : Serial Port Enable bit<br>1 = Configures RA5/RX/DT and RA4/TX/CK pins as serial port pins<br>0 = Serial port disabled                                                                                                                                                                                                                        |

| bit 6: | <b>RX9</b> : 9-bit Receive Enable bit<br>1 = Selects 9-bit reception<br>0 = Selects 8-bit reception                                                                                                                                                                                                                                                        |

| bit 5: | SREN: Single Receive Enable bit         This bit enables the reception of a single byte. After receiving the byte, this bit is automatically cleared.         Synchronous mode:         1 = Enable reception         0 = Disable reception         Note: This bit is ignored in synchronous slave reception.         Asynchronous mode:         Don't care |

| bit 4: | CREN: Continuous Receive Enable bit<br>This bit enables the continuous reception of serial data.<br><u>Asynchronous mode:</u><br>1 = Enable reception<br>0 = Disables reception<br><u>Synchronous mode:</u><br>1 = Enables continuous reception until CREN is cleared (CREN overrides SREN)<br>0 = Disables continuous reception                           |

| bit 3: | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                 |

| bit 2: | FERR: Framing Error bit<br>1 = Framing error (Updated by reading RCREG)<br>0 = No framing error                                                                                                                                                                                                                                                            |

| bit 1: | OERR: Overrun Error bit<br>1 = Overrun (Cleared by clearing CREN)<br>0 = No overrun error                                                                                                                                                                                                                                                                  |

| bit 0: | <b>RX9D</b> : 9th bit of receive data (can be the software calculated parity bit)                                                                                                                                                                                                                                                                          |

#### 13.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. Table 13-1 shows the formula for computation of the baud rate for different USART modes. These only apply when the USART is in synchronous master mode (internal clock) and asynchronous mode.

Given the desired baud rate and Fosc, the nearest integer value between 0 and 255 can be calculated using the formula below. The error in baud rate can then be determined.

#### TABLE 13-1: BAUD RATE FORMULA

| SYNC | Mode         | Baud Rate      |

|------|--------------|----------------|

| 0    | Asynchronous | Fosc/(64(X+1)) |

| 1    | Synchronous  | Fosc/(4(X+1))  |

X = value in SPBRG (0 to 255)

Example 13-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 SYNC = 0

#### EXAMPLE 13-1: CALCULATING BAUD RATE ERROR

Desired Baud rate=Fosc / (64 (X + 1))

$9600 = \frac{16000000}{(64 (X + 1))}$

X = 25.042 = 25

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

- Error = <u>(Calculated Baud Rate Desired Baud Rate)</u> Desired Baud Rate

- = (9615 9600) / 9600

- = 0.16%

Writing a new value to the SPBRG, causes the BRG timer to be reset (or cleared), this ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

#### TABLE 13-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address                                        | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------|-------------------------------|-----------------------------------------|

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9   | SREN  | CREN  | _     | FERR  | OERR  | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9   | TXEN  | SYNC  | —     | —     | TRMT  | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |       |       |       |       |       |       | xxxx xxxx | uuuu uuuu                     |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used by the Baud Rate Generator. $Note 1: Other (non power-up) resets include: external reset through <math>\overline{MCLR}$  and Watchdog Timer Reset.

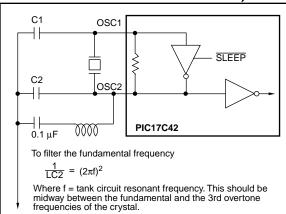

#### FIGURE 14-3: CRYSTAL OPERATION, OVERTONE CRYSTALS (XT OSC CONFIGURATION)

#### TABLE 14-2: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Oscillator<br>Type | Resonator<br>Frequency         | Capacitor Range<br>C1 = C2               |

|--------------------|--------------------------------|------------------------------------------|

| LF                 | 455 kHz<br>2.0 MHz             | 15 - 68 pF<br>10 - 33 pF                 |

| ХТ                 | 4.0 MHz<br>8.0 MHz<br>16.0 MHz | 22 - 68 pF<br>33 - 100 pF<br>33 - 100 pF |

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### **Resonators Used:**

| 455 kHz  | Panasonic EFO-A455K04B                            | ± 0.3% |  |  |  |

|----------|---------------------------------------------------|--------|--|--|--|

| 2.0 MHz  | Murata Erie CSA2.00MG                             | ± 0.5% |  |  |  |

| 4.0 MHz  | Murata Erie CSA4.00MG                             | ± 0.5% |  |  |  |

| 8.0 MHz  | Murata Erie CSA8.00MT                             | ± 0.5% |  |  |  |

| 16.0 MHz | Murata Erie CSA16.00MX                            | ± 0.5% |  |  |  |

| Resona   | Resonators used did not have built-in capacitors. |        |  |  |  |

# TABLE 14-3:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR

| Osc<br>Type | Freq                  | C1               | C2             |

|-------------|-----------------------|------------------|----------------|

| LF          | 32 kHz <sup>(1)</sup> | 100-150 pF       | 100-150 pF     |

|             | 1 MHz                 | 10-33 pF         | 10-33 pF       |

|             | 2 MHz                 | 10-33 pF         | 10-33 pF       |

| XT          | 2 MHz                 | 47-100 pF        | 47-100 pF      |

|             | 4 MHz                 | 15-68 pF         | 15-68 pF       |

|             | 8 MHz <sup>(2)</sup>  | 15-47 pF         | 15-47 pF       |

|             | 16 MHz                | TBD              | TBD            |

|             | 25 MHz                | 15-47 pF         | 15-47 pF       |

|             | 32 MHz <sup>(3)</sup> | <sub>0</sub> (3) | <sub>(3)</sub> |

Higher capacitance increases the stability of the oscillator but also increases the start-up time and the oscillator current. These values are for design guidance only. Rs may be required in XT mode to avoid overdriving the crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values for external components.

- Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

- 2: Rs of 330Ω is required for a capacitor combination of 15/15 pF.

- 3: Only the capacitance of the board was present.

#### **Crystals Used:**

| 32.768 kHz | Epson C-001R32.768K-A | ± 20 PPM     |

|------------|-----------------------|--------------|

| 1.0 MHz    | ECS-10-13-1           | $\pm$ 50 PPM |

| 2.0 MHz    | ECS-20-20-1           | $\pm$ 50 PPM |

| 4.0 MHz    | ECS-40-20-1           | ± 50 PPM     |

| 8.0 MHz    | ECS ECS-80-S-4        | ± 50 PPM     |

|            | ECS-80-18-1           |              |

| 16.0 MHz   | ECS-160-20-1          | TBD          |

| 25 MHz     | CTS CTS25M            | $\pm$ 50 PPM |

| 32 MHz     | CRYSTEK HF-2          | $\pm$ 50 PPM |

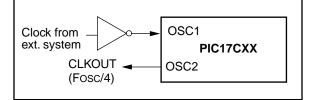

#### 14.2.3 EXTERNAL CLOCK OSCILLATOR

In the EC oscillator mode, the OSC1 input can be driven by CMOS drivers. In this mode, the OSC1/CLKIN pin is hi-impedance and the OSC2/CLK-OUT pin is the CLKOUT output (4 Tosc).

#### FIGURE 14-4: EXTERNAL CLOCK INPUT OPERATION (EC OSC CONFIGURATION)

| Mnemonic,  |        | Description                                   |       | cles 16-bit Opcode |      |      |      | Status    | Notes |

|------------|--------|-----------------------------------------------|-------|--------------------|------|------|------|-----------|-------|

| Operands   |        |                                               |       | MSb                |      |      | LSb  | Affected  |       |

| TABLWT     | t,i,f  | Table Write                                   | 2     | 1010               | 11ti | ffff | ffff | None      | 5     |

| TLRD       | t,f    | Table Latch Read                              | 1     | 1010               | 00tx | ffff | ffff | None      |       |

| TLWT       | t,f    | Table Latch Write                             | 1     | 1010               | 01tx | ffff | ffff | None      |       |

| TSTFSZ     | f      | Test f, skip if 0                             | 1 (2) | 0011               | 0011 | ffff | ffff | None      | 6,8   |

| XORWF      | f,d    | Exclusive OR WREG with f                      | 1     | 0000               | 110d | ffff | ffff | Z         |       |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS                         | 1     |                    |      |      |      |           |       |

| BCF        | f,b    | Bit Clear f                                   | 1     | 1000               | 1bbb | ffff | ffff | None      |       |

| BSF        | f,b    | Bit Set f                                     | 1     | 1000               | 0bbb | ffff | ffff | None      |       |

| BTFSC      | f,b    | Bit test, skip if clear                       | 1 (2) | 1001               | 1bbb | ffff | ffff | None      | 6,8   |

| BTFSS      | f,b    | Bit test, skip if set                         | 1 (2) | 1001               | 0bbb | ffff | ffff | None      | 6,8   |

| BTG        | f,b    | Bit Toggle f                                  | 1     | 0011               | 1bbb | ffff | ffff | None      |       |

| LITERAL AN | ID CO  | NTROL OPERATIONS                              |       |                    |      |      |      |           |       |

| ADDLW      | k      | ADD literal to WREG                           | 1     | 1011               | 0001 | kkkk | kkkk | OV,C,DC,Z |       |

| ANDLW      | k      | AND literal with WREG                         | 1     | 1011               | 0101 | kkkk | kkkk | Z         |       |

| CALL       | k      | Subroutine Call                               | 2     | 111k               | kkkk | kkkk | kkkk | None      | 7     |

| CLRWDT     | _      | Clear Watchdog Timer                          | 1     | 0000               | 0000 | 0000 | 0100 | TO,PD     |       |

| GOTO       | k      | Unconditional Branch                          | 2     | 110k               | kkkk | kkkk | kkkk | None      | 7     |

| IORLW      | k      | Inclusive OR literal with WREG                | 1     | 1011               | 0011 | kkkk | kkkk | Z         |       |

| LCALL      | k      | Long Call                                     | 2     | 1011               | 0111 | kkkk | kkkk | None      | 4,7   |

| MOVLB      | k      | Move literal to low nibble in BSR             | 1     | 1011               | 1000 | uuuu | kkkk | None      |       |

| MOVLR      | k      | Move literal to high nibble in BSR            | 1     | 1011               | 101x | kkkk | uuuu | None      | 9     |

| MOVLW      | k      | Move literal to WREG                          | 1     | 1011               | 0000 | kkkk | kkkk | None      |       |

| MULLW      | k      | Multiply literal with WREG                    | 1     | 1011               | 1100 | kkkk | kkkk | None      | 9     |

| RETFIE     | _      | Return from interrupt (and enable interrupts) | 2     | 0000               | 0000 | 0000 | 0101 | GLINTD    | 7     |

| RETLW      | k      | Return literal to WREG                        | 2     | 1011               | 0110 | kkkk | kkkk | None      | 7     |

| RETURN     | _      | Return from subroutine                        | 2     | 0000               | 0000 | 0000 | 0010 | None      | 7     |

| SLEEP      | _      | Enter SLEEP Mode                              | 1     | 0000               | 0000 | 0000 | 0011 | TO, PD    |       |

| SUBLW      | k      | Subtract WREG from literal                    | 1     | 1011               | 0010 | kkkk | kkkk | OV,C,DC,Z |       |

| XORLW      | k      | Exclusive OR literal with WREG                | 1     | 1011               | 0100 | kkkk | kkkk | Z         |       |

### TABLE 15-2: PIC17CXX INSTRUCTION SET (Cont.'d)

Legend: Refer to Table 15-1 for opcode field descriptions.

Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

- 3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

| ADDLW                             | ADD Literal to WREG                                                                       |                      |       |                  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------|----------------------|-------|------------------|--|

| Syntax:                           | [label] A                                                                                 | DLW                  | k     |                  |  |

| Operands:                         | $0 \le k \le 25$                                                                          | 55                   |       |                  |  |

| Operation:                        | (WREG) -                                                                                  | + k $\rightarrow$ (V | VREG) |                  |  |

| Status Affected:                  | OV, C, DC                                                                                 | C, Z                 |       |                  |  |

| Encoding:                         | 1011                                                                                      | 0001                 | kkkk  | kkkk             |  |

| Description:                      | The contents of WREG are added to the 8-bit literal 'k' and the result is placed in WREG. |                      |       |                  |  |

| Words:                            | 1                                                                                         |                      |       |                  |  |

| Cycles:                           | 1                                                                                         |                      |       |                  |  |

| Q Cycle Activity:                 |                                                                                           |                      |       |                  |  |

| Q1                                | Q2                                                                                        | Q3                   | 3     | Q4               |  |

| Decode                            | Read<br>literal 'k'                                                                       | Execu                |       | Vrite to<br>WREG |  |

| Example:                          | ADDLW                                                                                     | 0x15                 |       |                  |  |

| Before Instruction<br>WREG = 0x10 |                                                                                           |                      |       |                  |  |

| ADDWF                         | ADD WRE                                    | EG to f                                                           |            |                       |  |  |

|-------------------------------|--------------------------------------------|-------------------------------------------------------------------|------------|-----------------------|--|--|

| Syntax:                       | [ <i>label</i> ] A[                        | DDWF 1                                                            | f,d        |                       |  |  |

| Operands:                     | $0 \le f \le 255$ $d \in [0,1]$            | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |            |                       |  |  |

| Operation:                    | (WREG) +                                   | - (f) $\rightarrow$ (de                                           | est)       |                       |  |  |

| Status Affected:              | OV, C, DC                                  | , Z                                                               |            |                       |  |  |

| Encoding:                     | 0000                                       | 111d                                                              | ffff       | ffff                  |  |  |

| Description:                  | Add WREG<br>result is sto<br>result is sto | red in WRE                                                        | EG. If 'd' | is 1 the              |  |  |

| Words:                        | 1                                          |                                                                   |            |                       |  |  |

| Cycles:                       | 1                                          |                                                                   |            |                       |  |  |

| Q Cycle Activity:             |                                            |                                                                   |            |                       |  |  |

| Q1                            | Q2                                         | Q3                                                                |            | Q4                    |  |  |

| Decode                        | Read<br>register 'f'                       | Execute                                                           | ·   ·      | /rite to<br>stination |  |  |

| Example:                      | ADDWF                                      | REG, 0                                                            |            |                       |  |  |

| Before Instru<br>WREG<br>REG  | iction<br>= 0x17<br>= 0xC2                 |                                                                   |            |                       |  |  |

| After Instruct<br>WREG<br>REG | tion<br>= 0xD9<br>= 0xC2                   |                                                                   |            |                       |  |  |

After Instruction WREG = 0x25

| CPFSEQ                                         | Compare<br>skip if f =                                                                                                                                                                                                                                             | f with WREC<br>WREG                            | Э,     | CPF        | SGT                                                                                    | Compare<br>skip if f >                                                                   | f with WRE<br>WREG                             | G,      |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------|------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------|---------|

| Syntax:                                        | [label]                                                                                                                                                                                                                                                            | CPFSEQ f                                       |        | Syn        | tax:                                                                                   | [label]                                                                                  | CPFSGT f                                       |         |

| Operands:                                      | $0 \le f \le 255$                                                                                                                                                                                                                                                  | 5                                              |        | Ope        | rands:                                                                                 | $0 \le f \le 255$                                                                        | 5                                              |         |

| Operation:                                     | (f) – (WRE)<br>skip if (f) =<br>(unsigned o                                                                                                                                                                                                                        |                                                |        | Ope        | ration:                                                                                | (f) – (WRE0<br>skip if (f) ><br>(unsigned o                                              |                                                |         |

| Status Affected:                               | None                                                                                                                                                                                                                                                               |                                                |        | Stat       | us Affected:                                                                           | None                                                                                     |                                                |         |

| Encoding:                                      | 0011                                                                                                                                                                                                                                                               | 0001 fff                                       | f ffff | Enc        | oding:                                                                                 | 0011                                                                                     | 0010 ff:                                       | ff ffff |

| Description:                                   | Compares the contents of data memory<br>location 'f' to the contents of WREG by<br>performing an unsigned subtraction.<br>If 'f' = WREG then the fetched instruc-<br>tion is discarded and an NOP is exe-<br>cuted instead making this a two-cycle<br>instruction. |                                                | Des    | cription:  | location 'f' t<br>by performi<br>If the conte<br>WREG the<br>discarded a<br>instead ma | o the contents<br>ng an unsigne<br>nts of 'f' > the<br>n the fetched in<br>and an NOP is | nstruction is                                  |         |

| Words:                                         | 1                                                                                                                                                                                                                                                                  |                                                |        | 14/0 -     | de .                                                                                   | tion.<br>1                                                                               |                                                |         |

| Cycles:                                        | 1 (2)                                                                                                                                                                                                                                                              |                                                |        | Wor        |                                                                                        | -                                                                                        |                                                |         |

| Q Cycle Activity:                              |                                                                                                                                                                                                                                                                    |                                                |        | Cyc        |                                                                                        | 1 (2)                                                                                    |                                                |         |

| Q1                                             | Q2                                                                                                                                                                                                                                                                 | Q3                                             | Q4     | QC         | ycle Activity:<br>Q1                                                                   | Q2                                                                                       | Q3                                             | Q4      |

| Decode                                         | Read<br>register 'f'                                                                                                                                                                                                                                               | Execute                                        | NOP    |            | Decode                                                                                 | Read                                                                                     | Execute                                        | NOP     |

| If skip:                                       |                                                                                                                                                                                                                                                                    |                                                |        | lf sk      | in:                                                                                    | register 'f'                                                                             |                                                |         |

| Q1                                             | Q2                                                                                                                                                                                                                                                                 | Q3                                             | Q4     |            | Q1                                                                                     | Q2                                                                                       | Q3                                             | Q4      |

| Forced NOP                                     | NOP                                                                                                                                                                                                                                                                | Execute                                        | NOP    |            | Forced NOP                                                                             | NOP                                                                                      | Execute                                        | NOP     |

| <u>Example</u> :                               | NEQUAL                                                                                                                                                                                                                                                             | CPFSEQ REG<br>:<br>:                           |        | <u>Exa</u> | mple:                                                                                  | HERE<br>NGREATER<br>GREATER                                                              | CPFSGT RE<br>:<br>:                            | G       |

| Before Instru<br>PC Addre                      |                                                                                                                                                                                                                                                                    |                                                |        |            | Before Instru                                                                          | -                                                                                        | ·                                              |         |

| WREG<br>REG                                    | ess = HE<br>= ?<br>= ?                                                                                                                                                                                                                                             | RE                                             |        |            | PC<br>WREG                                                                             |                                                                                          | dress (HERE)                                   |         |

| After Instruct<br>If REG<br>PC<br>If REG<br>PC | = W<br>= Ac<br>≠ W                                                                                                                                                                                                                                                 | REG;<br>Idress (EQUAL<br>REG;<br>Idress (NEQUA |        |            | After Instruc<br>If REG<br>PC<br>If REG<br>PC                                          | > Wi<br>= Ad<br>≤ Wi                                                                     | REG;<br>Idress (GREAT<br>REG;<br>Idress (NGREZ |         |

| DECF              | Decreme                  | nt f               |                      | DECFSZ          | Decrement f,                                                      | skip if 0  |                 |

|-------------------|--------------------------|--------------------|----------------------|-----------------|-------------------------------------------------------------------|------------|-----------------|

| Syntax:           | [label]                  | DECF f,d           |                      | Syntax:         | [label] DEC                                                       | FSZ f,d    |                 |

| Operands:         | 0 ≤ f ≤ 258<br>d ∈ [0,1] | 5                  |                      | Operands:       | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |            |                 |

| Operation:        | (f) – 1 $\rightarrow$ (  | dest)              |                      | Operation:      | (f) – 1 $\rightarrow$ (dest                                       |            |                 |

| Status Affected:  | OV, C, DC                | ;, Z               |                      |                 | skip if result =                                                  | 0          |                 |

| Encoding:         | 0000                     | 011d ff            | ff ffff              | Status Affected | l: None                                                           |            |                 |

| Description:      | Decrement                | register 'f'. If ' | d' is 0 the          | Encoding:       | 0001 011                                                          | Ld fff     | f ffff          |

|                   |                          | ored in WREG       |                      | Description:    | The contents of mented. If 'd' is                                 | 0 the resu | It is placed in |

| Words:            | 1                        |                    |                      |                 | WREG. If 'd' is 1<br>back in register                             |            | t is placed     |

| Cycles:           | 1                        |                    |                      |                 | If the result is 0,                                               |            | instruction.    |

| Q Cycle Activity: |                          |                    |                      |                 | which is already                                                  | / fetched, | is discarded,   |

| Q1                | Q2                       | Q3                 | Q4                   |                 | and an NOP is e<br>ing it a two-cycle                             |            |                 |

| Decode            | Read<br>register 'f'     | Execute            | Write to destination | Words:          | 1                                                                 |            |                 |

| Example:          | DECF                     | CNT, 1             |                      | Cycles:         | 1(2)                                                              |            |                 |

| Before Instru     |                          | - ,                |                      | Q Cycle Activit | y:                                                                |            |                 |

| CNT               | = 0x01                   |                    |                      | Q1              | Q2                                                                | Q3         | Q4              |

| Z                 | = 0                      |                    |                      | Decode          |                                                                   | xecute     | Write to        |

| After Instruc     | tion                     |                    |                      |                 | register 'f'                                                      |            | destination     |

| CNT               | = 0x00                   |                    |                      | Example:        |                                                                   |            | CNT, 1          |

| Z                 | = 1                      |                    |                      |                 | GC<br>CONTINUE                                                    | OTO        | LOOP            |

|                   |                          |                    |                      | Defers inc      |                                                                   |            |                 |

|                   |                          |                    |                      | Before Ins      | liucion                                                           |            |                 |

| PC             | =    | Address (HERE)     |

|----------------|------|--------------------|

| After Instruct | tion |                    |

| CNT            | =    | CNT - 1            |

| If CNT         | =    | 0;                 |

| PC             | =    | Address (CONTINUE) |

| If CNT         | ≠    | 0;                 |

| PC             | =    | Address (HERE+1)   |

| IORWF                    | Inclusive            |                                                   | with f               | LCALL          | Long Cal                                  | I                                            |                               |

|--------------------------|----------------------|---------------------------------------------------|----------------------|----------------|-------------------------------------------|----------------------------------------------|-------------------------------|

| Syntax:                  | [ label ]            | ORWF f,d                                          |                      | Syntax:        | [ label ]                                 | LCALL k                                      |                               |

| Operands:                | $0 \le f \le 255$    | 5                                                 |                      | Operands:      | $0 \le k \le 25$                          | 5                                            |                               |

|                          | d ∈ [0,1]            |                                                   |                      | Operation:     | PC + 1 $\rightarrow$                      | TOS;                                         |                               |

| Operation:               | (WREG) .             | $OR.\left(f ight) ightarrow\left(de ight)$        | est)                 |                | $k \rightarrow PCL$ ,                     | (PCLATH) -                                   | $\rightarrow$ PCH             |

| Status Affected:         | Z                    |                                                   |                      | Status Affecte | d: None                                   |                                              |                               |

| Encoding:                | 0000                 | 100d ff:                                          | ff ffff              | Encoding:      | 1011                                      | 0111 kk                                      | kk kkkk                       |

| Description:             | 'd' is 0 the r       | R WREG with<br>esult is placed<br>esult is placed | 0                    | Description:   | tine call to<br>gram mem<br>First, the re | anywhere with<br>ory space.<br>eturn address | · · ·                         |

| Words:                   | 1                    |                                                   |                      |                | •                                         | to the stack. A<br>ress is then lo           |                               |

| Cycles:                  | 1                    |                                                   |                      |                |                                           | ounter. The lo                               |                               |

| Q Cycle Activity:        |                      |                                                   |                      |                |                                           |                                              | s embedded in                 |

| Q1                       | Q2                   | Q3                                                | Q4                   |                |                                           | om PC high h                                 | er 8-bits of PC olding latch, |

| Decode                   | Read<br>register 'f' | Execute                                           | Write to destination |                | PCLATH.                                   | Ū                                            | 0                             |

|                          | 0                    |                                                   | uestination          | Words:         | 1                                         |                                              |                               |

| Example:                 |                      | ESULT, O                                          |                      | Cycles:        | 2                                         |                                              |                               |

| Before Instru<br>RESULT  |                      |                                                   |                      | Q Cycle Activi | ty:                                       |                                              |                               |

| WREG                     | = 0x13<br>= 0x91     |                                                   |                      | Q1             | Q2                                        | Q3                                           | Q4                            |

| After Instruct<br>RESULT |                      |                                                   |                      | Decode         | Read<br>literal 'k'                       | Execute                                      | Write<br>register PCL         |

| WREG                     | = 0x13<br>= 0x93     |                                                   |                      | Forced NC      | DP NOP                                    | Execute                                      | NOP                           |

|                          |                      |                                                   |                      | Example:       | MOVPF W                                   | IGH(SUBROU<br>REG, PCLAT<br>OW(SUBROUT       | Н                             |

**Before Instruction**

| SUBROUTINE        | = | 16-bit Address |

|-------------------|---|----------------|

| PC                | = | ?              |

| After Instruction |   |                |

| PC = Address (S | UBROUTINE) |

|-----------------|------------|

|-----------------|------------|

| TABLWT            | Table Wr    | ite      |         |                |

|-------------------|-------------|----------|---------|----------------|

| Example1:         | TABLWT      | 0, 1,    | REG     |                |

| Before Instruc    | tion        |          |         |                |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA356  |                |

| MEMORY            | (TBLPTR)    | =        | 0xFFFI  | F              |

| After Instruction | on (table v | vrite co | mpletio | n)             |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0x53    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA357  | 7              |

| MEMORY            | (TBLPTR -   | 1) =     | 0x5355  | 5              |

| Example 2:        | TABLWT      | 1, 0,    | REG     |                |

| Before Instruc    | tion        |          |         |                |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA356  | 6              |

| MEMORY            | (TBLPTR)    | =        | 0xFFFI  | F              |

| After Instruction | on (table v | vrite co | mpletio | n)             |

| REG               | ,           | =        | 0x53    | ,              |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x53    |                |

| TBLPTR            |             | =        | 0xA356  | 6              |

| MEMORY            | (TBLPTR)    | =        | 0xAA5   | 3              |

|                   |             |          |         |                |

|                   | 1           |          | г       |                |

| Program<br>Memory | 15          |          | 0       | Data<br>Momory |

| Wiethory          |             |          |         | Memory         |

|                   | ( 🖳         | TBLPTR   |         |                |

|                                       | TBLPTR       |

|---------------------------------------|--------------|

| · · · · · · · · · · · · · · · · · · · |              |

| 16 bits                               | TBLAT 8 bits |

| TLR               | D                                                               | Table Late                                     | ch Read                                                                                                                                                               |                       |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|

| Syntax:           |                                                                 | [ <i>label</i> ] T                             | LRD t,f                                                                                                                                                               |                       |  |  |  |  |  |

| Operands:         |                                                                 | 0 ≤ f ≤ 255<br>t ∈ [0,1]                       | $0 \le f \le 255$<br>t $\in [0,1]$                                                                                                                                    |                       |  |  |  |  |  |

| Ope               | ration:                                                         | lf t = 0,<br>TBLAT                             |                                                                                                                                                                       |                       |  |  |  |  |  |

|                   |                                                                 | lf t = 1,<br>TBLAT                             | ,                                                                                                                                                                     |                       |  |  |  |  |  |

| State             | us Affected:                                                    | None                                           | None                                                                                                                                                                  |                       |  |  |  |  |  |

| Enco              | oding:                                                          | 1010                                           | 1010 00tx ffff ffff                                                                                                                                                   |                       |  |  |  |  |  |

| Deso              | cription:                                                       | (TBLAT) into<br>is unaffecte<br>If t = 1; high | Read data from 16-bit table latch<br>(TBLAT) into file register 'f'. Table Latch<br>is unaffected.<br>If $t = 1$ ; high byte is read<br>If $t = 0$ ; low byte is read |                       |  |  |  |  |  |

|                   |                                                                 | with TABLR                                     | This instruction is used in conjunction<br>with TABLRD to transfer data from pro-<br>gram memory to data memory.                                                      |                       |  |  |  |  |  |

| Word              | ds:                                                             | 1                                              |                                                                                                                                                                       |                       |  |  |  |  |  |

| Cycl              | es:                                                             | 1                                              |                                                                                                                                                                       |                       |  |  |  |  |  |

| QC                | cle Activity:                                                   |                                                |                                                                                                                                                                       |                       |  |  |  |  |  |

|                   | Q1                                                              | Q2                                             | Q3                                                                                                                                                                    | Q4                    |  |  |  |  |  |

|                   | Decode                                                          | Read<br>register<br>TBLATH or<br>TBLATL        | Execute                                                                                                                                                               | Write<br>register 'f' |  |  |  |  |  |

| <u>Exar</u>       | <u>mple</u> :                                                   | TLRD t                                         | , RAM                                                                                                                                                                 |                       |  |  |  |  |  |

|                   | Before Instru                                                   | iction                                         |                                                                                                                                                                       |                       |  |  |  |  |  |

|                   | t<br>RAM                                                        | = 0<br>= ?                                     |                                                                                                                                                                       |                       |  |  |  |  |  |

|                   | TBLAT                                                           | •                                              |                                                                                                                                                                       |                       |  |  |  |  |  |

|                   | After Instruct                                                  | tion                                           |                                                                                                                                                                       |                       |  |  |  |  |  |

|                   | RAM = 0xAF<br>TBLAT = 0x00AF (TBLATH = 0x00)<br>(TBLATL = 0xAF) |                                                |                                                                                                                                                                       |                       |  |  |  |  |  |

|                   | Before Instru                                                   | iction                                         |                                                                                                                                                                       |                       |  |  |  |  |  |

|                   | t<br>RAM                                                        | = 1<br>= ?                                     |                                                                                                                                                                       |                       |  |  |  |  |  |

|                   | TBLAT                                                           | = ?<br>= 0x00AF                                | (TBLATH =<br>(TBLATL =                                                                                                                                                | ,                     |  |  |  |  |  |

| After Instruction |                                                                 |                                                |                                                                                                                                                                       |                       |  |  |  |  |  |

|                   | RAM<br>TBLAT                                                    | = 0x00<br>= 0x00AF                             | (TBLATH =<br>(TBLATL =                                                                                                                                                | ,                     |  |  |  |  |  |

|                   | Program<br>Memory                                               | 15                                             | 0                                                                                                                                                                     | Data<br>Memory        |  |  |  |  |  |

|                   |                                                                 |                                                |                                                                                                                                                                       |                       |  |  |  |  |  |

| • - •             |                                                                 |                                                | . (                                                                                                                                                                   | ÷                     |  |  |  |  |  |

|                   | 16 bits                                                         |                                                | BLAT                                                                                                                                                                  | 8 bits                |  |  |  |  |  |

### Applicable Devices 42 R42 42A 43 R43 44

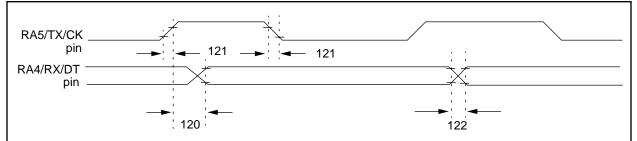

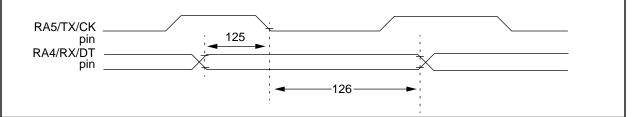

#### FIGURE 17-9: USART MODULE: SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 17-9: SERIAL PORT SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                             | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|------------------------------------------------------------|-----|------|-----|-------|------------|

| 120              | TckH2dtV | SYNC XMIT (MASTER & SLAVE)<br>Clock high to data out valid | _   | _    | 65  | ns    |            |

| 121              | TckRF    | Clock out rise time and fall time (Master Mode)            | _   | 10   | 35  | ns    |            |

| 122              | TdtRF    | Data out rise time and fall time                           |     | 10   | 35  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 17-10: USART MODULE: SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 17-10: SERIAL PORT SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data hold before CK↓ (DT hold time) | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                   | 15  | —    | _   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## Applicable Devices 42 R42 42A 43 R43 44

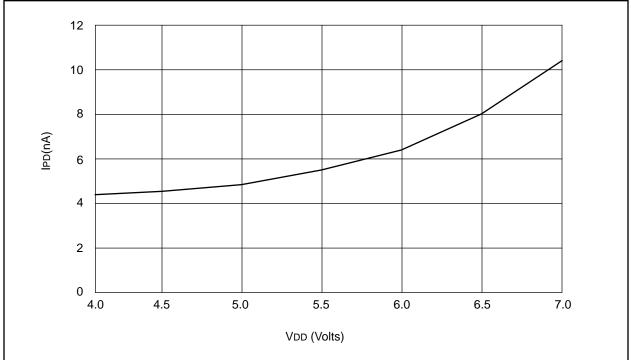

### FIGURE 18-9: TYPICAL IPD vs. VDD WATCHDOG DISABLED 25°C