Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 232 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

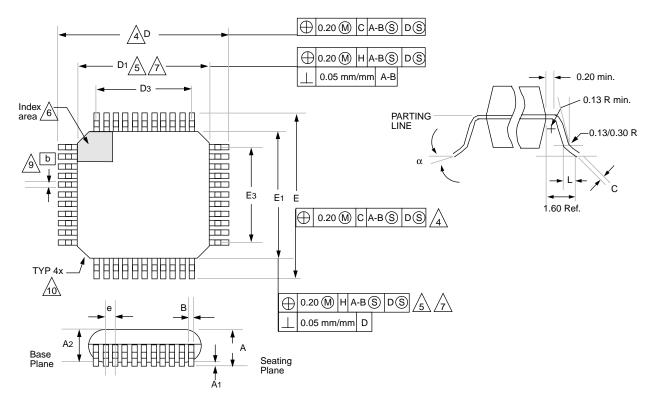

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-16i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABLE 3-1:  | FINU       | UT DES      |            |               |                |                                                                                                                                                                                                                                     |

|-------------|------------|-------------|------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name        | DIP<br>No. | PLCC<br>No. | QFP<br>No. | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                         |

| OSC1/CLKIN  | 19         | 21          | 37         | I             | ST             | Oscillator input in crystal/resonator or RC oscillator mode.<br>External clock input in external clock mode.                                                                                                                        |

| OSC2/CLKOUT | 20         | 22          | 38         | 0             |                | Oscillator output. Connects to crystal or resonator in crystal oscillator mode. In RC oscillator or external clock modes OSC2 pin outputs CLKOUT which has one fourth the frequency of OSC1 and denotes the instruction cycle rate. |

| MCLR/VPP    | 32         | 35          | 7          | I/P           | ST             | Master clear (reset) input/Programming Voltage (VPP) input.<br>This is the active low reset input to the chip.                                                                                                                      |

|             |            |             |            |               |                | PORTA is a bi-directional I/O Port except for RA0 and RA1 which are input only.                                                                                                                                                     |

| RA0/INT     | 26         | 28          | 44         | I             | ST             | RA0/INT can also be selected as an external interrupt<br>input. Interrupt can be configured to be on positive or<br>negative edge.                                                                                                  |

| RA1/T0CKI   | 25         | 27          | 43         | I             | ST             | RA1/T0CKI can also be selected as an external interrupt<br>input, and the interrupt can be configured to be on posi-<br>tive or negative edge. RA1/T0CKI can also be selected<br>to be the clock input to the Timer0 timer/counter. |

| RA2         | 24         | 26          | 42         | I/O           | ST             | High voltage, high current, open drain input/output port pins.                                                                                                                                                                      |

| RA3         | 23         | 25          | 41         | I/O           | ST             | High voltage, high current, open drain input/output port pins.                                                                                                                                                                      |

| RA4/RX/DT   | 22         | 24          | 40         | I/O           | ST             | RA4/RX/DT can also be selected as the USART (SCI)<br>Asynchronous Receive or USART (SCI) Synchronous<br>Data.                                                                                                                       |

| RA5/TX/CK   | 21         | 23          | 39         | I/O           | ST             | RA5/TX/CK can also be selected as the USART (SCI)<br>Asynchronous Transmit or USART (SCI) Synchronous<br>Clock.                                                                                                                     |

|             |            |             |            |               |                | PORTB is a bi-directional I/O Port with software configurable weak pull-ups.                                                                                                                                                        |

| RB0/CAP1    | 11         | 13          | 29         | I/O           | ST             | RB0/CAP1 can also be the CAP1 input pin.                                                                                                                                                                                            |

| RB1/CAP2    | 12         | 14          | 30         | I/O           | ST             | RB1/CAP2 can also be the CAP2 input pin.                                                                                                                                                                                            |

| RB2/PWM1    | 13         | 15          | 31         | I/O           | ST             | RB2/PWM1 can also be the PWM1 output pin.                                                                                                                                                                                           |

| RB3/PWM2    | 14         | 16          | 32         | I/O           | ST             | RB3/PWM2 can also be the PWM2 output pin.                                                                                                                                                                                           |

| RB4/TCLK12  | 15         | 17          | 33         | I/O           | ST             | RB4/TCLK12 can also be the external clock input to<br>Timer1 and Timer2.                                                                                                                                                            |

| RB5/TCLK3   | 16         | 18          | 34         | I/O           | ST             | RB5/TCLK3 can also be the external clock input to<br>Timer3.                                                                                                                                                                        |

| RB6         | 17         | 19          | 35         | I/O           | ST             |                                                                                                                                                                                                                                     |

| RB7         | 18         | 20          | 36         | I/O           | ST             |                                                                                                                                                                                                                                     |

|             |            |             |            |               |                | PORTC is a bi-directional I/O Port.                                                                                                                                                                                                 |

| RC0/AD0     | 2          | 3           | 19         | I/O           | TTL            | This is also the lower half of the 16-bit wide system bus                                                                                                                                                                           |

| RC1/AD1     | 3          | 4           | 20         | I/O           | TTL            | in microprocessor mode or extended microcontroller                                                                                                                                                                                  |

| RC2/AD2     | 4          | 5           | 21         | I/O           | TTL            | mode. In multiplexed system bus configuration, these pins are address output as well as data input or output.                                                                                                                       |

| RC3/AD3     | 5          | 6           | 22         | I/O           | TTL            |                                                                                                                                                                                                                                     |

| RC4/AD4     | 6          | 7           | 23         | I/O           | TTL            |                                                                                                                                                                                                                                     |

| RC5/AD5     | 7          | 8           | 24         | I/O           | TTL            |                                                                                                                                                                                                                                     |

| RC6/AD6     | 8          | 9           | 25         | I/O           | TTL            |                                                                                                                                                                                                                                     |

| RC7/AD7     | 9          | 10          | 26         | I/O           | TTL            |                                                                                                                                                                                                                                     |

TABLE 3-1:PINOUT DESCRIPTIONS

Legend: I = Input only; O = Output only; I/O = Input/Output; P = Power; — = Not Used; TTL = TTL input; ST = Schmitt Trigger input.

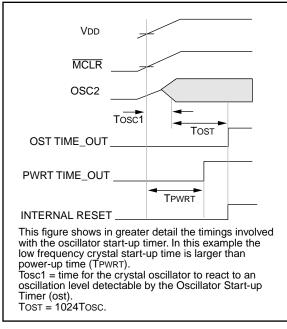

## FIGURE 4-5: OSCILLATOR START-UPTIME

#### FIGURE 4-6: USING ON-CHIP POR

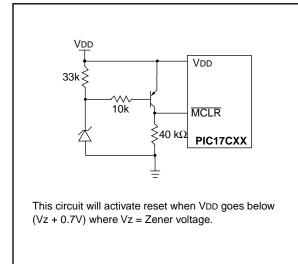

#### FIGURE 4-7: BROWN-OUT PROTECTION CIRCUIT 1

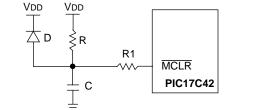

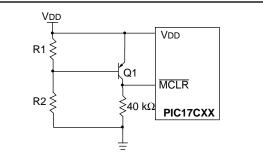

# FIGURE 4-8: PIC17C42 EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: An external Power-on Reset circuit is required only if VDD power-up time is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R < 40 k $\Omega$  is recommended to ensure that the voltage drop across R does not exceed 0.2V (max. leakage current spec. on the  $\overline{MCLR}/VPP$  pin is 5  $\mu$ A). A larger voltage drop will degrade VIH level on the  $\overline{MCLR}/VPP$  pin.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or (Electrical Overstress) EOS.

FIGURE 4-9: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

## 6.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC17C4X; program memory and data memory. Each block has its own bus, so that access to each block can occur during the same oscillator cycle.

The data memory can further be broken down into General Purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

#### 6.1 Program Memory Organization

PIC17C4X devices have a 16-bit program counter capable of addressing a 64K x 16 program memory space. The reset vector is at 0000h and the interrupt vectors are at 0008h, 0010h, 0018h, and 0020h (Figure 6-1).

#### 6.1.1 PROGRAM MEMORY OPERATION

The PIC17C4X can operate in one of four possible program memory configurations. The configuration is selected by two configuration bits. The possible modes are:

- Microprocessor

- Microcontroller

- Extended Microcontroller

- Protected Microcontroller

The microcontroller and protected microcontroller modes only allow internal execution. Any access beyond the program memory reads unknown data. The protected microcontroller mode also enables the code protection feature.

The extended microcontroller mode accesses both the internal program memory as well as external program memory. Execution automatically switches between internal and external memory. The 16-bits of address allow a program memory range of 64K-words.

The microprocessor mode only accesses the external program memory. The on-chip program memory is ignored. The 16-bits of address allow a program memory range of 64K-words. Microprocessor mode is the default mode of an unprogrammed device.

The different modes allow different access to the configuration bits, test memory, and boot ROM. Table 6-1 lists which modes can access which areas in memory. Test Memory and Boot Memory are not required for normal operation of the device. Care should be taken to ensure that no unintended branches occur to these areas.

#### FIGURE 6-1: PROGRAM MEMORY MAP AND STACK

| AND STACK                     |                                   |                     |  |  |  |

|-------------------------------|-----------------------------------|---------------------|--|--|--|

|                               | PC<15:0>                          | ]                   |  |  |  |

| CALL,                         | RETURN 1 16                       | 1                   |  |  |  |

| RETFI                         |                                   |                     |  |  |  |

|                               | Stack Level 1                     | 1                   |  |  |  |

|                               | :                                 | 1                   |  |  |  |

|                               | •<br>Stack Level 16               | -                   |  |  |  |

|                               | Stack Level 10                    | ]                   |  |  |  |

| T T                           | Reset Vector                      | ] 0000h             |  |  |  |

|                               |                                   |                     |  |  |  |

|                               | INT Pin Interrupt Vector          | 0008h               |  |  |  |

|                               | Timer0 Interrupt Vector           | 0010h               |  |  |  |

|                               | T0CKI Pin Interrupt Vector        | 0018h               |  |  |  |

|                               | Peripheral Interrupt Vector       | 0020h               |  |  |  |

|                               |                                   | 0021h               |  |  |  |

|                               |                                   |                     |  |  |  |

|                               |                                   | 7FFh<br>(PIC17C42,  |  |  |  |

| <u>&gt;</u>                   |                                   | PIC17CR42,          |  |  |  |

| User Memory<br>Space (1)      |                                   | PIC17C42A)          |  |  |  |

| ace                           |                                   | FFFh                |  |  |  |

| Spe                           |                                   | (PIC17C43           |  |  |  |

| n ∣                           |                                   | PIC17CR43)          |  |  |  |

|                               |                                   |                     |  |  |  |

|                               |                                   |                     |  |  |  |

|                               |                                   | 1FFFh<br>(PIC17C44) |  |  |  |

|                               |                                   | (FIC17C44)          |  |  |  |

|                               |                                   |                     |  |  |  |

|                               |                                   | l                   |  |  |  |

| <u>+</u>                      | FOSC0                             | FDFFh               |  |  |  |

| > [                           | FOSC0                             | FE00h<br>FE01h      |  |  |  |

| Jor                           | WDTPS0                            | FE02h               |  |  |  |

| len                           | WDTPS1                            | FE03h               |  |  |  |

| ≥ e                           | PM0                               | FE04h               |  |  |  |

| pac                           | Reserved                          | FE05h               |  |  |  |

| S IB                          | PM1                               | FE06h               |  |  |  |

| figu                          | Reserved                          | FE07h               |  |  |  |

| Configuration Memory<br>Space | Reserved                          | FE08h               |  |  |  |

|                               |                                   | FE0Eh               |  |  |  |

| 📕                             | PM2 <sup>(2)</sup>                | FE0Fh               |  |  |  |

|                               | Test EPROM                        | FE10h<br>FF5Fh      |  |  |  |

|                               |                                   | FF60h               |  |  |  |

|                               | Boot ROM                          |                     |  |  |  |

|                               |                                   | FFFFh               |  |  |  |

| Note 1: U                     | ser memory space may be inter     | nal, external, or   |  |  |  |

|                               | oth. The memory configuration of  |                     |  |  |  |

|                               | rocessor mode.                    | ,                   |  |  |  |

|                               | his location is reserved on the F | PIC17C42.           |  |  |  |

| 1                             |                                   |                     |  |  |  |

| Addr                                                        | Unbanked                                                                                  |                                                        |                                                           |                                                               |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|

| 00h                                                         | INDF0                                                                                     |                                                        |                                                           |                                                               |

| 01h                                                         | FSR0                                                                                      |                                                        |                                                           |                                                               |

| 02h                                                         | PCL                                                                                       |                                                        |                                                           |                                                               |

| 03h                                                         | PCLATH                                                                                    |                                                        |                                                           |                                                               |

| 04h                                                         | ALUSTA                                                                                    |                                                        |                                                           |                                                               |

| 05h                                                         | TOSTA                                                                                     |                                                        |                                                           |                                                               |

| 06h                                                         | CPUSTA                                                                                    |                                                        |                                                           |                                                               |

| 07h                                                         | INTSTA                                                                                    |                                                        |                                                           |                                                               |

| 08h                                                         | INDF1                                                                                     |                                                        |                                                           |                                                               |

| 09h                                                         | FSR1                                                                                      |                                                        |                                                           |                                                               |

| 0Ah                                                         | WREG                                                                                      |                                                        |                                                           |                                                               |

| 0Bh                                                         | TMR0L                                                                                     |                                                        |                                                           |                                                               |

| 0Ch                                                         | TMR0H                                                                                     |                                                        |                                                           |                                                               |

| 0Dh                                                         | TBLPTRL                                                                                   |                                                        |                                                           |                                                               |

| 0Eh                                                         | TBLPTRH                                                                                   |                                                        |                                                           |                                                               |

| 0Fh                                                         | BSR                                                                                       |                                                        |                                                           |                                                               |

| 1                                                           |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | Bank 0                                                                                    | Bank 1 <sup>(1)</sup>                                  | Bank 2 <sup>(1)</sup>                                     | Bank 3 <sup>(1)</sup>                                         |

| 10h                                                         | Bank 0<br>PORTA                                                                           | Bank 1 <sup>(1)</sup><br>DDRC                          | Bank 2 <sup>(1)</sup><br>TMR1                             | Bank 3 <sup>(1)</sup><br>PW1DCL                               |

| 10h<br>11h                                                  |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | PORTA                                                                                     | DDRC                                                   | TMR1                                                      | PW1DCL                                                        |

| 11h                                                         | PORTA<br>DDRB                                                                             | DDRC<br>PORTC                                          | TMR1<br>TMR2                                              | PW1DCL<br>PW2DCL                                              |

| 11h<br>12h                                                  | PORTA<br>DDRB<br>PORTB                                                                    | DDRC<br>PORTC<br>DDRD                                  | TMR1<br>TMR2<br>TMR3L                                     | PW1DCL<br>PW2DCL<br>PW1DCH                                    |

| 11h<br>12h<br>13h                                           | PORTA<br>DDRB<br>PORTB<br>RCSTA                                                           | DDRC<br>PORTC<br>DDRD<br>PORTD                         | TMR1<br>TMR2<br>TMR3L<br>TMR3H                            | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH                          |

| 11h<br>12h<br>13h<br>14h                                    | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG                                                  | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE                 | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1                     | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L                  |

| 11h<br>12h<br>13h<br>14h<br>15h                             | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA                                         | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE        | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2              | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H          |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h                      | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h               | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h        | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

# FIGURE 6-5: PIC17C42 REGISTER FILE MAP

Note 1: SFR file locations 10h - 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

## FIGURE 6-6: PIC17CR42/42A/43/R43/44 REGISTER FILE MAP

| Addr | Unbanked           |                       |                       |                       |

|------|--------------------|-----------------------|-----------------------|-----------------------|

| 00h  | INDF0              |                       |                       |                       |

| 01h  | FSR0               |                       |                       |                       |

| 02h  | PCL                |                       |                       |                       |

| 03h  | PCLATH             |                       |                       |                       |

| 04h  | ALUSTA             |                       |                       |                       |

| 05h  | TOSTA              |                       |                       |                       |

| 06h  | CPUSTA             |                       |                       |                       |

| 07h  | INTSTA             |                       |                       |                       |

| 08h  | INDF1              |                       |                       |                       |

| 09h  | FSR1               |                       |                       |                       |

| 0Ah  | WREG               |                       |                       |                       |

| 0Bh  | TMR0L              |                       |                       |                       |

| 0Ch  | TMR0H              |                       |                       |                       |

| 0Dh  | TBLPTRL            |                       |                       |                       |

| 0Eh  | TBLPTRH            |                       |                       |                       |

| 0Fh  | BSR                |                       |                       |                       |

|      | Bank 0             | Bank 1 <sup>(1)</sup> | Bank 2 <sup>(1)</sup> | Bank 3 <sup>(1)</sup> |

| 10h  | PORTA              | DDRC                  | TMR1                  | PW1DCL                |

| 11h  | DDRB               | PORTC                 | TMR2                  | PW2DCL                |

| 12h  | PORTB              | DDRD                  | TMR3L                 | PW1DCH                |

| 13h  | RCSTA              | PORTD                 | TMR3H                 | PW2DCH                |

| 14h  | RCREG              | DDRE                  | PR1                   | CA2L                  |

| 15h  | TXSTA              | PORTE                 | PR2                   | CA2H                  |

| 16h  | TXREG              | PIR                   | PR3L/CA1L             | TCON1                 |

| 17h  | SPBRG              | PIE                   | PR3H/CA1H             | TCON2                 |

| 18h  | PRODL              |                       |                       |                       |

| 19h  | PRODH              |                       |                       |                       |

| 1Ah  |                    |                       |                       |                       |

|      |                    |                       |                       |                       |

| 1Fh  |                    |                       | 1                     |                       |

| 20h  | General            | General               |                       |                       |

|      | Purpose            | Purpose               |                       |                       |

|      | RAM <sup>(2)</sup> | RAM (2)               |                       |                       |

|      |                    |                       |                       |                       |

| FFh  |                    |                       |                       |                       |

- Note 1: SFR file locations 10h 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

- 2: General Purpose Registers (GPR) locations 20h - FFh and 120h - 1FFh are banked. All other GPRs ignore the Bank Select Register (BSR) bits.

### 7.1 <u>Table Writes to Internal Memory</u>

A table write operation to internal memory causes a long write operation. The long write is necessary for programming the internal EPROM. Instruction execution is halted while in a long write cycle. The long write will be terminated by any enabled interrupt. To ensure that the EPROM location has been well programmed, a minimum programming time is required (see specification #D114). Having only one interrupt enabled to terminate the long write ensures that no unintentional interrupts will prematurely terminate the long write.

The sequence of events for programming an internal program memory location should be:

- 1. Disable all interrupt sources, except the source to terminate EPROM program write.

- 2. Raise MCLR/VPP pin to the programming voltage.

- 3. Clear the WDT.

- 4. Do the table write. The interrupt will terminate the long write.

- 5. Verify the memory location (table read).

- **Note:** Programming requirements must be met. See timing specification in electrical specifications for the desired device. Violating these specifications (including temperature) may result in EPROM locations that are not fully programmed and may lose their state over time.

#### 7.1.1 TERMINATING LONG WRITES

An interrupt source or reset are the only events that terminate a long write operation. Terminating the long write from an interrupt source requires that the interrupt enable and flag bits are set. The GLINTD bit only enables the vectoring to the interrupt address.

If the TOCKI, RA0/INT, or TMR0 interrupt source is used to terminate the long write; the interrupt flag, of the highest priority enabled interrupt, will terminate the long write and automatically be cleared.

- **Note 1:** If an interrupt is pending, the TABLWT is aborted (an NOP is executed). The highest priority pending interrupt, from the TOCKI, RA0/INT, or TMR0 sources that is enabled, has its flag cleared.

- **Note 2:** If the interrupt is not being used for the program write timing, the interrupt should be disabled. This will ensure that the interrupt is not lost, nor will it terminate the long write prematurely.

If a peripheral interrupt source is used to terminate the long write, the interrupt enable and flag bits must be set. The interrupt flag will not be automatically cleared upon the vectoring to the interrupt vector address.

If the GLINTD bit is cleared prior to the long write, when the long write is terminated, the program will branch to the interrupt vector.

If the GLINTD bit is set prior to the long write, when the long write is terminated, the program will not vector to the interrupt address.

| Interrupt<br>Source     | GLINTD | Enable<br>Bit | Flag<br>Bit | Action                                                                                                              |

|-------------------------|--------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------|

| RA0/INT, TMR0,<br>T0CKI | 0      | 1             | 1           | Terminate long table write (to internal program<br>memory), branch to interrupt vector (branch clears<br>flag bit). |

|                         | 0      | 1             | 0           | None                                                                                                                |

|                         | 1      | 0             | x           | None                                                                                                                |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is automatically cleared).                           |

| Peripheral              | 0      | 1             | 1           | Terminate table write, branch to interrupt vector.                                                                  |

|                         | 0      | 1             | 0           | None                                                                                                                |

|                         | 1      | 0             | x           | None                                                                                                                |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is set).                                             |

## TABLE 7-1: INTERRUPT - TABLE WRITE INTERACTION

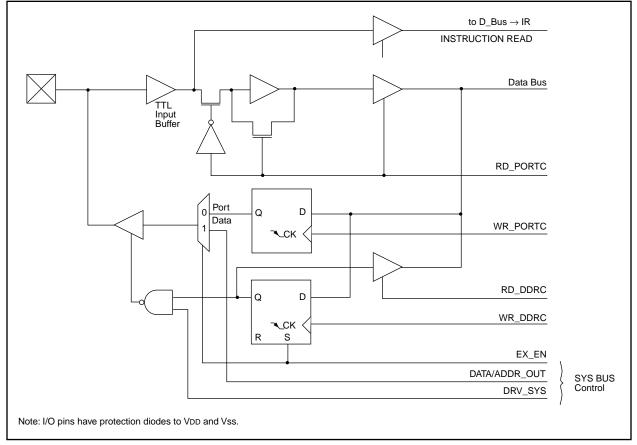

## 9.3 PORTC and DDRC Registers

PORTC is an 8-bit bi-directional port. The corresponding data direction register is DDRC. A '1' in DDRC configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTC reads the status of the pins, whereas writing to it will write to the port latch. PORTC is multiplexed with the system bus. When operating as the system bus, PORTC is the low order byte of the address/data bus (AD7:AD0). The timing for the system bus is shown in the Electrical Characteristics section.

**Note:** This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-2 shows the instruction sequence to initialize PORTC. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-2: INITIALIZING PORTC

| 1     | ;             | Select Bank 1                                        |

|-------|---------------|------------------------------------------------------|

| PORTC | ;             | Initialize PORTC data                                |

|       | ;             | latches before setting                               |

|       | ;             | the data direction                                   |

|       | ;             | register                                             |

| 0xCF  | ;             | Value used to initialize                             |

|       | ;             | data direction                                       |

| DDRC  | ;             | Set RC<3:0> as inputs                                |

|       | ;             | RC<5:4> as outputs                                   |

|       | ;             | RC<7:6> as inputs                                    |

|       | PORTC<br>0xCF | PORTC ;<br>;<br>;<br>;<br>;<br>0xCF ;<br>DDRC ;<br>; |

## FIGURE 9-6: BLOCK DIAGRAM OF RC<7:0> PORT PINS

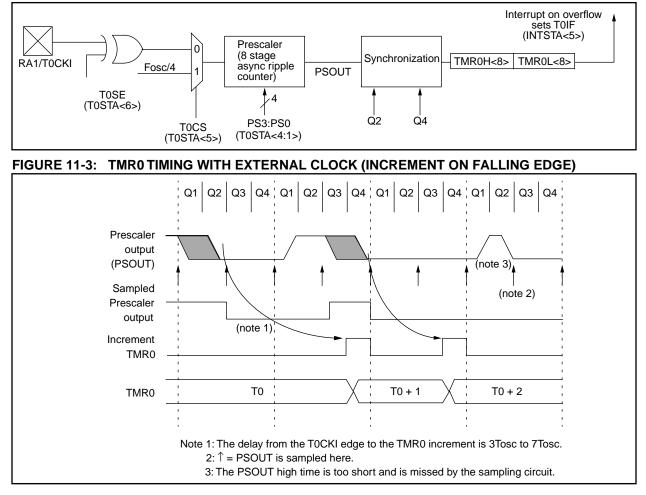

## 11.1 <u>Timer0 Operation</u>

When the TOCS (TOSTA<5>) bit is set, TMR0 increments on the internal clock. When TOCS is clear, TMR0 increments on the external clock (RA1/T0CKI pin). The external clock edge can be configured in software. When the TOSE (TOSTA<6>) bit is set, the timer will increment on the rising edge of the RA1/T0CKI pin. When T0SE is clear, the timer will increment on the falling edge of the RA1/T0CKI pin. The prescaler can be programmed to introduce a prescale of 1:1 to 1:256. The timer increments from 0000h to FFFFh and rolls over to 0000h. On overflow, the TMR0 Interrupt Flag bit (T0IF) is set. The TMR0 interrupt can be masked by clearing the corresponding TMR0 Interrupt Enable bit (T0IE). The TMR0 Interrupt Flag bit (T0IF) is automatically cleared when vectoring to the TMR0 interrupt vector.

## 11.2 Using Timer0 with External Clock

When the external clock input is used for Timer0, it is synchronized with the internal phase clocks. Figure 11-3 shows the synchronization of the external clock. This synchronization is done after the prescaler. The output of the prescaler (PSOUT) is sampled twice in every instruction cycle to detect a rising or a falling edge. The timing requirements for the external clock are detailed in the electrical specification section for the desired device.

#### 11.2.1 DELAY FROM EXTERNAL CLOCK EDGE

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time TMR0 is actually incremented. Figure 11-3 shows that this delay is between 3Tosc and 7Tosc. Thus, for example, measuring the interval between two edges (e.g. period) will be accurate within  $\pm$ 4Tosc ( $\pm$ 121 ns @ 33 MHz).

#### FIGURE 11-2: TIMER0 MODULE BLOCK DIAGRAM

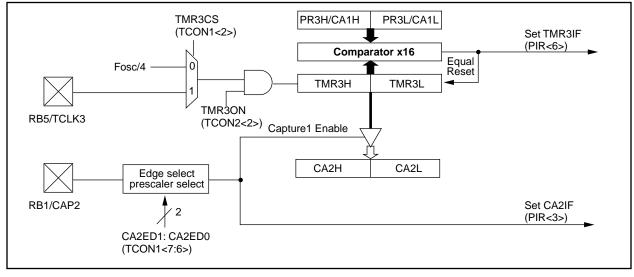

#### 12.2.1 ONE CAPTURE AND ONE PERIOD REGISTER MODE

In this mode registers PR3H/CA1H and PR3L/CA1L constitute a 16-bit period register. A block diagram is shown in Figure 12-7. The timer increments until it equals the period register and then resets to 0000h. TMR3 Interrupt Flag bit (TMR3IF) is set at this point. This interrupt can be disabled by clearing the TMR3 Interrupt Enable bit (TMR3IE). TMR3IF must be cleared in software.

This mode is selected if control bit CA1/PR3 is clear. In this mode, the Capture1 register, consisting of high byte (PR3H/CA1H) and low byte (PR3L/CA1L), is configured as the period control register for TMR3. Capture1 is disabled in this mode, and the corresponding Interrupt bit CA1IF is never set. TMR3 increments until it equals the value in the period register and then resets to 0000h.

Capture2 is active in this mode. The CA2ED1 and CA2ED0 bits determine the event on which capture will occur. The possible events are:

- · Capture on every falling edge

- Capture on every rising edge

- · Capture every 4th rising edge

- · Capture every 16th rising edge

When a capture takes place, an interrupt flag is latched into the CA2IF bit. This interrupt can be enabled by setting the corresponding mask bit CA2IE. The Peripheral Interrupt Enable bit (PEIE) must be set and the Global Interrupt Disable bit (GLINTD) must be cleared for the interrupt to be acknowledged. The CA2IF interrupt flag bit must be cleared in software.

When the capture prescale select is changed, the prescaler is not reset and an event may be generated. Therefore, the first capture after such a change will be ambiguous. However, it sets the time-base for the next capture. The prescaler is reset upon chip reset. Capture pin RB1/CAP2 is a multiplexed pin. When used as a port pin, Capture2 is not disabled. However, the user can simply disable the Capture2 interrupt by clearing CA2IE. If RB1/CAP2 is used as an output pin, the user can activate a capture by writing to the port pin. This may be useful during development phase to emulate a capture interrupt.

The input on capture pin RB1/CAP2 is synchronized internally to internal phase clocks. This imposes certain restrictions on the input waveform (see the Electrical Specification section for timing).

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the Timer3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The recommended sequence to read capture registers and capture overflow flag bits is shown in Example 12-1.

#### EXAMPLE 12-1: SEQUENCE TO READ CAPTURE REGISTERS

| MOVLB 3              | ;Select Bank 3          |

|----------------------|-------------------------|

| MOVPF CA2L,LO_BYTE   | ;Read Capture2 low      |

|                      | ;byte, store in LO_BYTE |

| MOVPF CA2H, HI_BYTE  | ;Read Capture2 high     |

|                      | ;byte, store in HI_BYTE |

| MOVPF TCON2,STAT_VAL | ;Read TCON2 into file   |

|                      | ;STAT_VAL               |

#### FIGURE 12-7: TIMER3 WITH ONE CAPTURE AND ONE PERIOD REGISTER BLOCK DIAGRAM

#### 14.4 Power-down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction. This clears the Watchdog Timer and postscaler (if enabled). The  $\overrightarrow{PD}$  bit is cleared and the  $\overrightarrow{TO}$  bit is set (in the CPUSTA register). In SLEEP mode, the oscillator driver is turned off. The I/O ports maintain their status (driving high, low, or hi-impedance).

The  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level (VIHMC). A WDT time-out RESET does not drive the  $\overline{\text{MCLR}}/\text{VPP}$  pin low.

#### 14.4.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- A POR reset

- External reset input on MCLR/VPP pin

- WDT Reset (if WDT was enabled)

- Interrupt from RA0/INT pin, RB port change, T0CKI interrupt, or some Peripheral Interrupts

The following peripheral interrupts can wake-up from SLEEP:

- · Capture1 interrupt

- Capture2 interrupt

- · USART synchronous slave transmit interrupt

- · USART synchronous slave receive interrupt

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

Any reset event will cause a device reset. Any interrupt event is considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the CPUSTA register can be used to determine the cause of device reset. The

$\overline{PD}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{TO}$  bit is cleared if WDT time-out occurred (and caused wake-up).

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GLINTD bit. If the GLINTD bit is set (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GLINTD bit is clear (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt vector address. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

Note: If the global interrupts are disabled (GLINTD is set), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from sleep. The TO bit is set, and the PD bit is cleared.

The WDT is cleared when the device wake from SLEEP, regardless of the source of wake-up.

14.4.1.1 WAKE-UP DELAY

When the oscillator type is configured in XT or LF mode, the Oscillator Start-up Timer (OST) is activated on wake-up. The OST will keep the device in reset for 1024Tosc. This needs to be taken into account when considering the interrupt response time when coming out of SLEEP.

## FIGURE 14-9: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                              | Q1   Q2   Q3   Q4                                                                                     | Q1   Q2   Q3   Q4                                  | Q1   Q2      | Q3   Q4      | Q1   Q2       | Q3  Q4                 | Q1   Q2   Q3   Q4                            |

|------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|--------------|---------------|------------------------|----------------------------------------------|

| OSC1                         |                                                                                                       |                                                    |              |              |               | $\frown \frown \frown$ |                                              |

| CLKOUT(4)                    |                                                                                                       | /                                                  |              | Tost(2)      | \/<br>\/      |                        |                                              |

| INT                          |                                                                                                       |                                                    |              |              | I<br>I        |                        |                                              |

| (RA0/INT pin)                | ı ı                                                                                                   |                                                    | : (          |              | 1             |                        | <u>1                                    </u> |

| INTF flag                    |                                                                                                       |                                                    | <u>`</u>     |              | I             |                        | Interrupt Latency (2)                        |

| GLINTD bit                   | 1<br>11                                                                                               |                                                    | · ·          |              | I             |                        | ·                                            |

|                              | i i                                                                                                   |                                                    | Processor    |              | 1             |                        | 1 I                                          |

| INSTRUCTION                  | FLOW                                                                                                  |                                                    | in SLEEP     |              | 1<br>1        |                        | I I<br>I I                                   |

| PC                           | C PC                                                                                                  | PC+1                                               |              | +2           | × 0004        | h                      | × <u>0005h</u>                               |

| Instruction (<br>fetched     | Inst (PC) = SLEEP                                                                                     | Inst (PC+1)                                        |              |              | Inst (PC      | +2)                    |                                              |

| Instruction {                | Inst (PC-1)                                                                                           | SLEEP                                              |              |              | Inst (PC      | +1)                    | Dummy Cycle                                  |

| 2: Tost = 102<br>3: When GLI | scillator mode assume<br>4Tosc (drawing not to s<br>NTD = 0 processor jum<br>s not available in these | scale). This delay will<br>ps to interrupt routing | e after wake | -up. If GLIN | ITD = 1, exec | ution will             | continue in line.                            |

# PIC17C4X

| CALL                                               | Subroutir                                                  | ne Call                                                                                                                         |                                                                              | CLF  | RF                                                 | Clear f                                                                                                                                                             |                           |       |                       |  |

|----------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|-----------------------|--|

| Syntax:                                            | [label] C                                                  | CALL k                                                                                                                          |                                                                              | Syn  | tax:                                               | [ <i>label</i> ] CL                                                                                                                                                 | [ <i>label</i> ] CLRF f,s |       |                       |  |

| Operands:                                          | $0 \le k \le 40$                                           | $0 \leq k \leq 4095$                                                                                                            |                                                                              |      | rands:                                             | $0 \le f \le 25$                                                                                                                                                    | $0 \leq f \leq 255$       |       |                       |  |

| Operation:                                         | k<12:8> –                                                  | PC+ 1 $\rightarrow$ TOS, k $\rightarrow$ PC<12:0>,<br>k<12:8> $\rightarrow$ PCLATH<4:0>;<br>PC<15:13> $\rightarrow$ PCLATH<7:5> |                                                                              |      | ration:                                            | $00h \rightarrow f, s$<br>$00h \rightarrow de$                                                                                                                      |                           |       |                       |  |

| Status Affected:                                   | None                                                       |                                                                                                                                 | 1<1.02                                                                       | Stat | us Affected:                                       | None                                                                                                                                                                |                           |       |                       |  |

|                                                    |                                                            |                                                                                                                                 |                                                                              | Enc  | oding:                                             | 0010                                                                                                                                                                | 100s                      | ffff  | ffff                  |  |

| Encoding:<br>Description:                          | return addr<br>the stack. T<br>PC bits<12<br>bits of the F | :0>. Then the uPC are copied                                                                                                    | page. First,<br>pushed onto<br>is loaded into<br>upper-eight<br>into PCLATH. |      | cription:                                          | Clears the contents of the specified reg<br>ister(s).<br>s = 0: Data memory location 'f' and<br>WREG are cleared.<br>s = 1: Data memory location 'f' is<br>cleared. |                           |       | 'f' and               |  |

|                                                    |                                                            | wo-cycle instru                                                                                                                 |                                                                              |      | Words:                                             |                                                                                                                                                                     | 1                         |       |                       |  |

|                                                    | See LCALL<br>space.                                        | for calls outsic                                                                                                                | de 8K memory                                                                 | Cyc  | les:                                               | 1                                                                                                                                                                   |                           |       |                       |  |

| Words:                                             | 1                                                          |                                                                                                                                 |                                                                              | QC   | ycle Activity:                                     |                                                                                                                                                                     |                           |       |                       |  |

| Cycles:                                            | 2                                                          |                                                                                                                                 |                                                                              |      | Q1                                                 | Q2                                                                                                                                                                  | Q                         |       | Q4                    |  |

| Q Cycle Activity:                                  |                                                            |                                                                                                                                 |                                                                              |      | Decode                                             | Read<br>register 'f'                                                                                                                                                | Exect                     |       | Write<br>egister 'f'  |  |

| Q1                                                 | Q2                                                         | Q3                                                                                                                              | Q4                                                                           |      |                                                    | iegister i                                                                                                                                                          |                           |       | and other             |  |

| Decode                                             | Read literal<br>'k'<7:0>                                   | Execute                                                                                                                         | NOP                                                                          |      |                                                    |                                                                                                                                                                     |                           |       | specified<br>register |  |

| Forced NOP                                         | NOP                                                        | Execute                                                                                                                         | NOP                                                                          | Exa  | <u>mple</u> :                                      | CLRF                                                                                                                                                                | FLAG                      | G_REG |                       |  |

| Example:<br>Before Instr<br>PC =<br>After Instruct | Address(HERE)                                              |                                                                                                                                 |                                                                              |      | Before Instru<br>FLAG_R<br>After Instruc<br>FLAG_R | EG = 0x<br>tion                                                                                                                                                     | 5A<br>00                  |       |                       |  |

| PC =                                               | Address (THI                                               | ERE)                                                                                                                            |                                                                              |      |                                                    |                                                                                                                                                                     |                           |       |                       |  |

TOS = Address(HERE + 1)

# PIC17C4X

| IORWF                    | Inclusive            |                                                   | with f               | LCALL             | Long Cal                                      | I                                            |                                  |

|--------------------------|----------------------|---------------------------------------------------|----------------------|-------------------|-----------------------------------------------|----------------------------------------------|----------------------------------|

| Syntax:                  | [label]              | ORWF f,d                                          |                      | Syntax:           | [ label ]                                     | LCALL k                                      |                                  |

| Operands:                | 0 ≤ f ≤ 255          | 5                                                 |                      | Operands:         | $0 \le k \le 25$                              | 5                                            |                                  |

|                          | d ∈ [0,1]            |                                                   |                      | Operation:        | PC + 1 $\rightarrow$                          | TOS;                                         |                                  |

| Operation:               | (WREG) .             | $OR.\left(f ight) ightarrow\left(de ight)$        | est)                 |                   | $k \rightarrow PCL$ ,                         | (PCLATH) -                                   | → PCH                            |

| Status Affected:         | Z                    |                                                   |                      | Status Affected:  | None                                          |                                              |                                  |

| Encoding:                | 0000                 | 100d ff                                           | ff ffff              | Encoding:         | 1011                                          | 0111 kk                                      | kk kkkk                          |

| Description:             | 'd' is 0 the r       | R WREG with<br>esult is placed<br>esult is placed | 0                    | Description:      | tine call to a<br>gram memor<br>First, the re | anywhere with<br>ory space.<br>eturn address | · /                              |

| Words:                   | 1                    |                                                   |                      |                   | •                                             | to the stack. A ress is then lo              |                                  |

| Cycles:                  | 1                    |                                                   |                      |                   | program co                                    | ounter. The lo                               | wer 8-bits of                    |

| Q Cycle Activity:        |                      |                                                   |                      |                   |                                               |                                              | s embedded in<br>er 8-bits of PC |

| Q1                       | Q2                   | Q3                                                | Q4                   |                   |                                               | om PC high h                                 |                                  |

| Decode                   | Read<br>register 'f' | Execute                                           | Write to destination |                   | PCLATH.                                       |                                              |                                  |

| Evemple:                 |                      |                                                   | uccundulori          | Words:            | 1                                             |                                              |                                  |

| Example:                 |                      | ESULT, O                                          |                      | Cycles:           | 2                                             |                                              |                                  |

| Before Instru<br>RESULT  |                      |                                                   |                      | Q Cycle Activity: |                                               |                                              |                                  |

| WREG                     | = 0x13<br>= 0x91     |                                                   |                      | Q1                | Q2                                            | Q3                                           | Q4                               |

| After Instruct<br>RESULT |                      |                                                   |                      | Decode            | Read<br>literal 'k'                           | Execute                                      | Write<br>register PCL            |

| WREG                     | = 0x13<br>= 0x93     |                                                   |                      | Forced NOP        | NOP                                           | Execute                                      | NOP                              |

|                          |                      |                                                   |                      | Example:          | MOVPF W                                       | IGH(SUBROU<br>REG, PCLAT<br>OW(SUBROUT       | Н                                |

**Before Instruction**

| Boloro modución   |        |                     |  |  |  |  |

|-------------------|--------|---------------------|--|--|--|--|

| SUBROUTINE<br>PC  | =<br>= | 16-bit Address<br>? |  |  |  |  |

| After Instruction |        |                     |  |  |  |  |

| PC = Address | (SUBROUTINE) |

|--------------|--------------|

|--------------|--------------|

# PIC17C4X

| MOVLR                                                      | Move Literal to high nibble in BSR                                                                                                                                                                                                                                          |   |  |  |  |  |  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|

| Syntax:                                                    | [ <i>label</i> ] MOVLR k                                                                                                                                                                                                                                                    |   |  |  |  |  |  |

| Operands:                                                  | $0 \le k \le 15$                                                                                                                                                                                                                                                            |   |  |  |  |  |  |

| Operation:                                                 | $k \rightarrow (BSR < 7:4>)$                                                                                                                                                                                                                                                |   |  |  |  |  |  |

| Status Affected:                                           | None                                                                                                                                                                                                                                                                        |   |  |  |  |  |  |

| Encoding:                                                  | 1011 101x kkkk uuuu                                                                                                                                                                                                                                                         |   |  |  |  |  |  |

| Description:                                               | The 4-bit literal 'k' is loaded into the<br>most significant 4-bits of the Bank<br>Select Register (BSR). Only the high<br>4-bits of the Bank Select Register<br>are affected. The lower half of the<br>BSR is unchanged. The assembler<br>will encode the "u" fields as 0. |   |  |  |  |  |  |

| Words:                                                     | 1                                                                                                                                                                                                                                                                           |   |  |  |  |  |  |

| Cycles: 1                                                  |                                                                                                                                                                                                                                                                             |   |  |  |  |  |  |

| Q Cycle Activity:                                          |                                                                                                                                                                                                                                                                             |   |  |  |  |  |  |

| Q1                                                         | Q2 Q3 Q4                                                                                                                                                                                                                                                                    |   |  |  |  |  |  |