Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 232 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-25-pq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

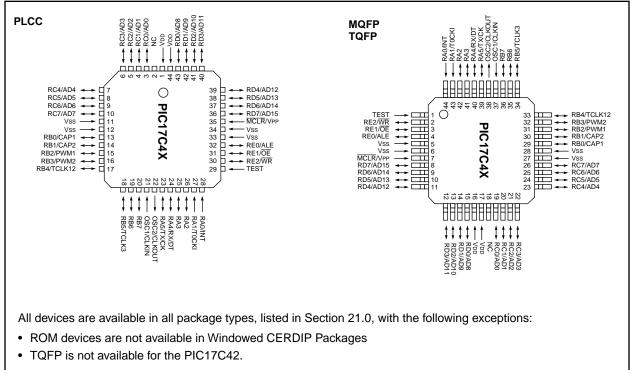

#### Pin Diagrams Cont.'d

#### 4.1.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (1024Tosc) delay after  $\overline{\text{MCLR}}$  is detected high or a wake-up from SLEEP event occurs.

The OST time-out is invoked only for XT and LF oscillator modes on a Power-on Reset or a Wake-up from SLEEP.

The OST counts the oscillator pulses on the OSC1/CLKIN pin. The counter only starts incrementing after the amplitude of the signal reaches the oscillator input thresholds. This delay allows the crystal oscillator or resonator to stabilize before the device exits reset. The length of time-out is a function of the crystal/resonator frequency.

#### 4.1.4 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First the internal POR signal goes high when the POR trip point is reached. If MCLR is high, then both the OST and PWRT timers start. In general the PWRT time-out is longer, except with low frequency crystals/resonators. The total time-out also varies based on oscillator configuration. Table 4-1 shows the times that are associated with the oscillator configuration. Figure 4-2 and Figure 4-3 display these time-out sequences.

If the device voltage is not within electrical specification at the end of a time-out, the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be held low until the voltage is within the device specification. The use of an external RC delay is sufficient for many of these applications.

# TABLE 4-1:TIME-OUT IN VARIOUSSITUATIONS

| Oscillator<br>Configuration | Power-up                            | Wake up<br>from<br>SLEEP | MCLR<br>Reset |

|-----------------------------|-------------------------------------|--------------------------|---------------|

| XT, LF                      | Greater of:<br>96 ms or<br>1024Tosc | 1024Tosc                 | —             |

| EC, RC                      | Greater of:<br>96 ms or<br>1024Tosc |                          | —             |

The time-out sequence begins from the first rising edge of  $\overline{\text{MCLR}}$ .

Table 4-3 shows the reset conditions for some special registers, while Table 4-4 shows the initialization conditions for all the registers. The shaded registers (in Table 4-4) are for all devices except the PIC17C42. In the PIC17C42, the PRODH and PRODL registers are general purpose RAM.

# TABLE 4-2:STATUS BITS AND THEIR<br/>SIGNIFICANCE

| TO | PD | Event                                                                              |  |  |  |  |

|----|----|------------------------------------------------------------------------------------|--|--|--|--|

| 1  | 1  | Power-on Reset, MCLR Reset during normal operation, or CLRWDT instruction executed |  |  |  |  |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP                            |  |  |  |  |

| 0  | 1  | WDT Reset during normal operation                                                  |  |  |  |  |

| 0  | 0  | WDT Reset during SLEEP                                                             |  |  |  |  |

In Figure 4-2, Figure 4-3 and Figure 4-4, TPWRT > TOST, as would be the case in higher frequency crystals. For lower frequency crystals, (i.e., 32 kHz) TOST would be greater.

#### TABLE 4-3: RESET CONDITION FOR THE PROGRAM COUNTER AND THE CPUSTA REGISTER

| Event                                      |                 | PCH:PCL               | CPUSTA | OST Active |

|--------------------------------------------|-----------------|-----------------------|--------|------------|

| Power-on Reset                             |                 | 0000h                 | 11 11  | Yes        |

| MCLR Reset during normal ope               | ration          | 0000h                 | 11 11  | No         |

| MCLR Reset during SLEEP                    |                 | 0000h                 | 11 10  | Yes (2)    |

| WDT Reset during normal operation          | ation           | 0000h                 | 11 01  | No         |

| WDT Reset during SLEEP <sup>(3)</sup>      |                 | 0000h                 | 11 00  | Yes (2)    |

| Interrupt wake-up from SLEEP GLINTD is set |                 | PC + 1                | 11 10  | Yes (2)    |

|                                            | GLINTD is clear | PC + 1 <sup>(1)</sup> | 10 10  | Yes (2)    |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0'.

Note 1: On wake-up, this instruction is executed. The instruction at the appropriate interrupt vector is fetched and then executed.

2: The OST is only active when the Oscillator is configured for XT or LF modes.

3: The Program Counter = 0, that is the device branches to the reset vector. This is different from the mid-range devices.

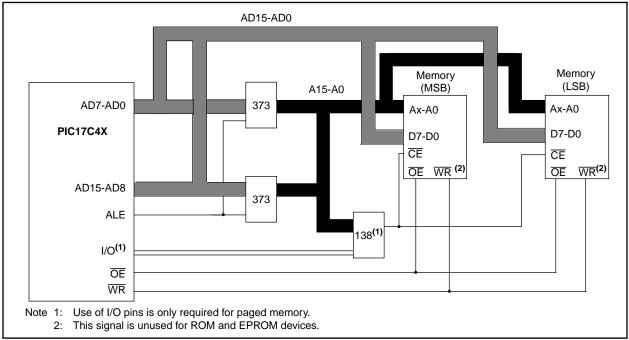

#### 6.1.2 EXTERNAL MEMORY INTERFACE

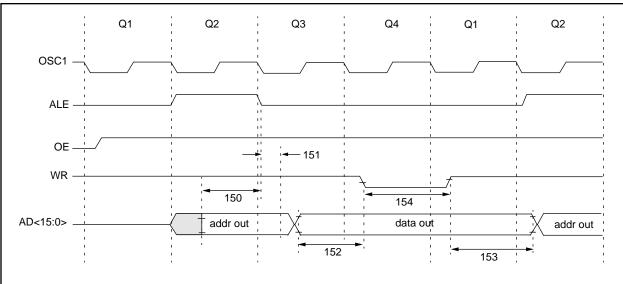

When either microprocessor or extended microcontroller mode is selected, PORTC, PORTD and PORTE are configured as the system bus. PORTC and PORTD are the multiplexed address/data bus and PORTE is for the control signals. External components are needed to demultiplex the address and data. This can be done as shown in Figure 6-4. The waveforms of address and data are shown in Figure 6-3. For complete timings, please refer to the electrical specification section.

#### FIGURE 6-3: EXTERNAL PROGRAM MEMORY ACCESS WAVEFORMS

| :      | Q1   Q2   Q3   Q4   | Q1   Q2   Q3   Q4   Q1 |

|--------|---------------------|------------------------|

| AD     | X                   |                        |

| <15:0> | Address out Data in | Address out Data out   |

| ALE    |                     |                        |

| OE;    | '4'                 | · · · ·                |

| WR     | '1'                 | <u> </u>               |

|        | Read cycle          | Write cycle            |

|        |                     | , white cycle          |

The system bus requires that there is no bus conflict (minimal leakage), so the output value (address) will be capacitively held at the desired value.

As the speed of the processor increases, external EPROM memory with faster access time must be used. Table 6-2 lists external memory speed requirements for a given PIC17C4X device frequency.

In extended microcontroller mode, when the device is executing out of internal memory, the control signals will continue to be active. That is, they indicate the action that is occurring in the internal memory. The external memory access is ignored.

This following selection is for use with Microchip EPROMs. For interfacing to other manufacturers memory, please refer to the electrical specifications of the desired PIC17C4X device, as well as the desired memory device to ensure compatibility.

| TABLE 6-2: | EPROM MEMORY ACCESS  |  |  |  |  |

|------------|----------------------|--|--|--|--|

|            | TIME ORDERING SUFFIX |  |  |  |  |

| BIC17CAY                | PIC17C4X Instruction |          | EPROM Suffix         |  |  |  |

|-------------------------|----------------------|----------|----------------------|--|--|--|

| Oscillator<br>Frequency | Cycle<br>Time (Tcy)  | PIC17C42 | PIC17C43<br>PIC17C44 |  |  |  |

| 8 MHz                   | 500 ns               | -25      | -25                  |  |  |  |

| 16 MHz                  | 250 ns               | -12      | -15                  |  |  |  |

| 20 MHz                  | 200 ns               | -90      | -10                  |  |  |  |

| 25 MHz                  | 160 ns               | N.A.     | -70                  |  |  |  |

| 33 MHz                  | 121 ns               | N.A.     | (1)                  |  |  |  |

Note 1: The access times for this requires the use of fast SRAMS.

**Note:** The external memory interface is not supported for the LC devices.

FIGURE 6-4: TYPICAL EXTERNAL PROGRAM MEMORY CONNECTION DIAGRAM

© 1996 Microchip Technology Inc.

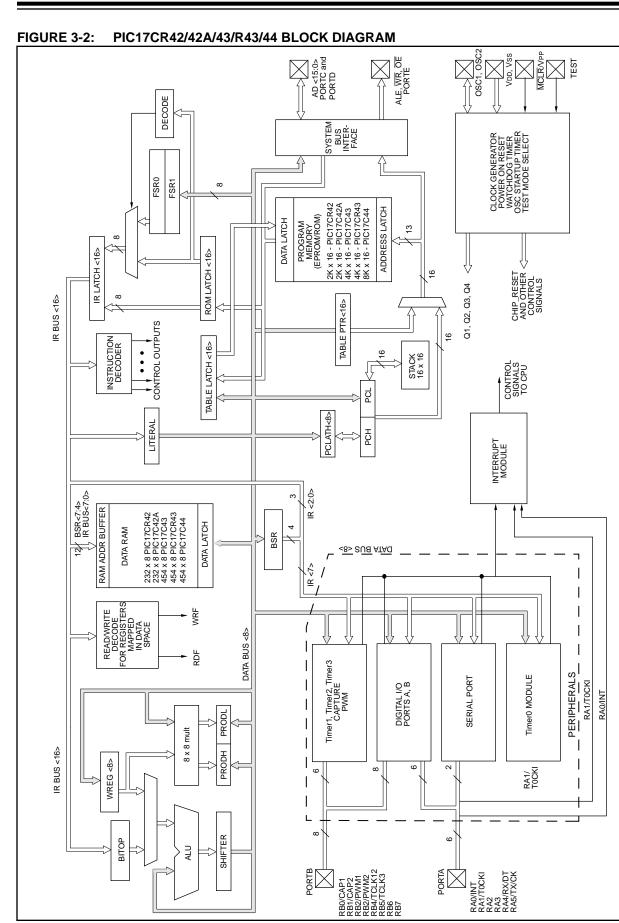

#### 6.2 Data Memory Organization

Data memory is partitioned into two areas. The first is the General Purpose Registers (GPR) area, while the second is the Special Function Registers (SFR) area. The SFRs control the operation of the device.

Portions of data memory are banked, this is for both areas. The GPR area is banked to allow greater than 232 bytes of general purpose RAM. SFRs are for the registers that control the peripheral functions. Banking requires the use of control bits for bank selection. These control bits are located in the Bank Select Register (BSR). If an access is made to a location outside this banked region, the BSR bits are ignored. Figure 6-5 shows the data memory map organization for the PIC17C42 and Figure 6-6 for all of the other PIC17C4X devices.

Instructions MOVPF and MOVFP provide the means to move values from the peripheral area ("P") to any location in the register file ("F"), and vice-versa. The definition of the "P" range is from 0h to 1Fh, while the "F" range is 0h to FFh. The "P" range has six more locations than peripheral registers (eight locations for the PIC17C42 device) which can be used as General Purpose Registers. This can be useful in some applications where variables need to be copied to other locations in the general purpose RAM (such as saving status information during an interrupt).

The entire data memory can be accessed either directly or indirectly through file select registers FSR0 and FSR1 (Section 6.4). Indirect addressing uses the appropriate control bits of the BSR for accesses into the banked areas of data memory. The BSR is explained in greater detail in Section 6.8.

#### 6.2.1 GENERAL PURPOSE REGISTER (GPR)

All devices have some amount of GPR area. The GPRs are 8-bits wide. When the GPR area is greater than 232, it must be banked to allow access to the additional memory space.

Only the PIC17C43 and PIC17C44 devices have banked memory in the GPR area. To facilitate switching between these banks, the MOVLR bank instruction has been added to the instruction set. GPRs are not initialized by a Power-on Reset and are unchanged on all other resets.

#### 6.2.2 SPECIAL FUNCTION REGISTERS (SFR)

The SFRs are used by the CPU and peripheral functions to control the operation of the device (Figure 6-5 and Figure 6-6). These registers are static RAM.

The SFRs can be classified into two sets, those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described here, while those related to a peripheral feature are described in the section for each peripheral feature.

The peripheral registers are in the banked portion of memory, while the core registers are in the unbanked region. To facilitate switching between the peripheral banks, the MOVLB bank instruction has been provided.

#### 6.3 <u>Stack Operation</u>

The PIC17C4X devices have a 16 x 16-bit wide hardware stack (Figure 6-1). The stack is not part of either the program or data memory space, and the stack pointer is neither readable nor writable. The PC is "PUSHed" onto the stack when a CALL instruction is executed or an interrupt is acknowledged. The stack is "POPed" in the event of a RETURN, RETLW, or a RETFIE instruction execution. PCLATH is not affected by a "PUSH" or a "POP" operation.

The stack operates as a circular buffer, with the stack pointer initialized to '0' after all resets. There is a stack available bit (STKAV) to allow software to ensure that the stack has not overflowed. The STKAV bit is set after a device reset. When the stack pointer equals Fh, STKAV is cleared. When the stack pointer rolls over from Fh to 0h, the STKAV bit will be held clear until a device reset.

- **Note 1:** There is not a status bit for stack underflow. The STKAV bit can be used to detect the underflow which results in the stack pointer being at the top of stack.

- Note 2: There are no instruction mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt vector.

- Note 3: After a reset, if a "POP" operation occurs before a "PUSH" operation, the STKAV bit will be cleared. This will appear as if the stack is full (underflow has occurred). If a "PUSH" operation occurs next (before another "POP"), the STKAV bit will be locked clear. Only a device reset will cause this bit to set.

After the device is "PUSHed" sixteen times (without a "POP"), the seventeenth push overwrites the value from the first push. The eighteenth push overwrites the second push (and so on).

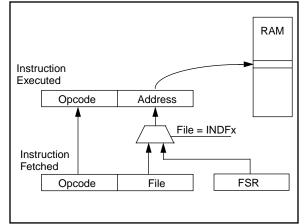

#### 6.4 Indirect Addressing

Indirect addressing is a mode of addressing data memory where the data memory address in the instruction is not fixed. That is, the register that is to be read or written can be modified by the program. This can be useful for data tables in the data memory. Figure 6-10 shows the operation of indirect addressing. This shows the moving of the value to the data memory address specified by the value of the FSR register.

Example 6-1 shows the use of indirect addressing to clear RAM in a minimum number of instructions. A similar concept could be used to move a defined number of bytes (block) of data to the USART transmit register (TXREG). The starting address of the block of data to be transmitted could easily be modified by the program.

#### FIGURE 6-10: INDIRECT ADDRESSING

NOTES:

### 13.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART) MODULE

The USART module is a serial I/O module. The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

The SPEN (RCSTA<7>) bit has to be set in order to configure RA4 and RA5 as the Serial Communication Interface.

The USART module will control the direction of the RA4/RX/DT and RA5/TX/CK pins, depending on the states of the USART configuration bits in the RCSTA and TXSTA registers. The bits that control I/O direction are:

- SPEN

- TXEN

- SREN

- CREN

- CSRC

The Transmit Status And Control Register is shown in Figure 13-1, while the Receive Status And Control Register is shown in Figure 13-2.

| <b>D</b> 4 4 4  |                                                                                  |                                                 |                  |             |                       | <b>D</b> (           | <b>D</b> 4 4 4  |                                                      |

|-----------------|----------------------------------------------------------------------------------|-------------------------------------------------|------------------|-------------|-----------------------|----------------------|-----------------|------------------------------------------------------|

| R/W - 0<br>CSRC | R/W - 0<br>TX9                                                                   | R/W - 0<br>TXEN                                 | R/W - 0<br>SYNC  | <u>U-0</u>  | <u>U-0</u>            | <u>R - 1</u><br>TRMT | R/W - x<br>TX9D | R = Readable bit                                     |

| bit7            | 17.9                                                                             | TALM                                            | 51110            |             |                       |                      | bit0            | W = Writable bit-n = Value at POR reset(x = unknown) |

| bit 7:          | <b>CSRC</b> : C<br>Synchron<br>1 = Maste<br>0 = Slave<br>Asynchron<br>Don't care | ous mode<br>r Mode (C<br>mode (Clo<br>nous mode | lock gene        | rated inter | mally from I<br>urce) | BRG)                 |                 |                                                      |

| bit 6:          | <b>TX9</b> : 9-bit<br>1 = Select<br>0 = Select                                   | s 9-bit tra                                     | nsmission        |             |                       |                      |                 |                                                      |

| bit 5:          | <b>TXEN</b> : Tra<br>1 = Transr<br>0 = Transr<br>SREN/CR                         | nit enable<br>nit disable                       | d<br>ed          | in SYNC     | mode                  |                      |                 |                                                      |

| bit 4:          | SYNC: US<br>(Synchror<br>1 = Synch<br>0 = Async                                  | nous/Asyn<br>Ironous m                          | chronous)<br>ode |             |                       |                      |                 |                                                      |

| bit 3-2:        | Unimpler                                                                         | nented: R                                       | ead as '0'       |             |                       |                      |                 |                                                      |

| bit 1:          | <b>TRMT</b> : Tra<br>1 = TSR e<br>0 = TSR fr                                     | empty                                           | ft Registe       | r (TSR) Er  | npty bit              |                      |                 |                                                      |

| bit 0:          | <b>TX9D</b> : 9th                                                                | bit of trar                                     | emit data        | (can be u   | and to only           | مطلا امملمان         | nority in on    | ft                                                   |

#### FIGURE 13-1: TXSTA REGISTER (ADDRESS: 15h, BANK 0)

© 1996 Microchip Technology Inc.

#### 13.2 USART Asynchronous Mode

In this mode, the USART uses standard nonreturn-to-zero (NRZ) format (one start bit, eight or nine data bits, and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock x64 of the bit shift rate. Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

The asynchronous mode is selected by clearing the SYNC bit (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

#### 13.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 13-3. The heart of the transmitter is the transmit shift register (TSR). The shift register obtains its data from the read/write transmit buffer (TXREG). TXREG is loaded with data in software. The TSR is not loaded until the stop bit has been transmitted from the previous load. As soon as the stop bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one TCY at the end of the current BRG cycle), the TXREG is empty and an interrupt bit, TXIF (PIR<1>) is set. This interrupt can be enabled or disabled by the TXIE bit (PIE<1>). TXIF will be set regardless of TXIE and cannot be reset in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of the TXREG, the TRMT (TXSTA<1>) bit shows the status of the TSR. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty.

| Note: | The TSR is not mapped in data memory, |

|-------|---------------------------------------|

|       | so it is not available to the user.   |

Transmission enabled setting is by the TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 13-5). The transmission can also be started by first loading TXREG and then setting TXEN. Normally when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to TSR resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 13-6). Clearing TXEN during a transmission will cause the transmission to be aborted. This will reset the transmitter and the RA5/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty).

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. Load data to the TXREG register.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 7. Enable the transmission by setting TXEN (starts transmission).

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the opposite order.

Note: To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

#### 14.1 Configuration Bits

The PIC17CXX has up to seven configuration locations (Table 14-1). These locations can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. Any write to a configuration location, regardless of the data, will program that configuration bit. A TABLWT instruction is required to write to program memory locations. The configuration bits can be read by using the TABLRD instructions. Reading any configuration location between FE00h and FE07h will read the low byte of the configuration word (Figure 14-1) into the TABLATL register. The TABLATH register will be FFh. Reading a configuration location between FE08h and FE0Fh will read the high byte of the configuration word into the TABLATL register. The TABLATH register will be FFh.

Addresses FE00h thorough FE0Fh are only in the program memory space for microcontroller and code protected microcontroller modes. A device programmer will be able to read the configuration word in any processor mode. See programming specifications for more detail.

#### TABLE 14-1: CONFIGURATION LOCATIONS

| Bit                | Address              |

|--------------------|----------------------|

| FOSC0              | FE00h                |

| FOSC1              | FE01h                |

| WDTPS0             | FE02h                |

| WDTPS1             | FE03h                |

| PM0                | FE04h                |

| PM1                | FE06h                |

| PM2 <sup>(1)</sup> | FE0Fh <sup>(1)</sup> |

Note 1: This location does not exist on the PIC17C42.

| Note: | When programming the desired configura-    |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|

|       | tion locations, they must be programmed in |  |  |  |  |  |  |

|       | ascending order. Starting with address     |  |  |  |  |  |  |

|       | FE00h.                                     |  |  |  |  |  |  |

#### 14.2 Oscillator Configurations

#### 14.2.1 OSCILLATOR TYPES

The PIC17CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LF: Low Power Crystal

- XT: Crystal/Resonator

- EC: External Clock Input

- RC: Resistor/Capacitor

## 14.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

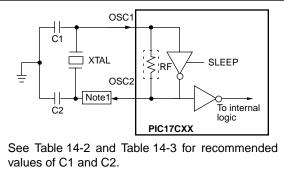

In XT or LF modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 14-2). The PIC17CXX Oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications.

For frequencies above 20 MHz, it is common for the crystal to be an overtone mode crystal. Use of overtone mode crystals require a tank circuit to attenuate the gain at the fundamental frequency. Figure 14-3 shows an example of this.

#### FIGURE 14-2: CRYSTAL OR CERAMIC RESONATOR OPERATION (XT OR LF OSC CONFIGURATION)

Note 1: A series resistor may be required for AT strip cut crystals.

| DCF                                                                | SNZ            | Decreme                                                  | ent f, skij                                                                             | o if no                                            | ot O                                                                    |  |  |

|--------------------------------------------------------------------|----------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------|--|--|

| Synt                                                               | tax:           | [ <i>label</i> ] D                                       | CFSNZ                                                                                   | f,d                                                |                                                                         |  |  |

| Ope                                                                | rands:         | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]                                                                |                                                    |                                                                         |  |  |

| Ope                                                                | ration:        | (f) – 1 $\rightarrow$ skip if not                        | • • •                                                                                   |                                                    |                                                                         |  |  |

| Stat                                                               | us Affected:   | None                                                     |                                                                                         |                                                    |                                                                         |  |  |

| Enc                                                                | oding:         | 0010                                                     | 011d                                                                                    | ffff                                               | ffff                                                                    |  |  |

| Des                                                                | cription:      | WREG. If '<br>back in reg<br>If the resul<br>which is al | 'd' is 0 the<br>d' is 1 the<br>gister 'f'.<br>t is not 0, t<br>ready fetc<br>DP is exec | e result<br>result<br>he nex<br>hed, is<br>uted in | is placed in<br>is placed<br>t instruction,<br>discarded,<br>stead mak- |  |  |

| Wor                                                                | ds:            | 1                                                        |                                                                                         |                                                    |                                                                         |  |  |

| Cycl                                                               | es:            | 1(2)                                                     |                                                                                         |                                                    |                                                                         |  |  |

| QC                                                                 | ycle Activity: |                                                          |                                                                                         |                                                    |                                                                         |  |  |

|                                                                    | Q1             | Q2                                                       | Q3                                                                                      |                                                    | Q4                                                                      |  |  |

|                                                                    | Decode         | Read<br>register 'f'                                     | Execu                                                                                   | ıte                                                | Write to destination                                                    |  |  |

| lf sk                                                              | ip:            |                                                          |                                                                                         |                                                    |                                                                         |  |  |

|                                                                    | Q1             | Q2                                                       | Q3                                                                                      |                                                    | Q4                                                                      |  |  |

|                                                                    | Forced NOP     | NOP                                                      | Execu                                                                                   | ute                                                | NOP                                                                     |  |  |

| <u>Exa</u>                                                         | <u>mple</u> :  | HERE<br>ZERO<br>NZERO                                    | DCFSNZ<br>:<br>:                                                                        | TEMP                                               | P, 1                                                                    |  |  |

| Before Instruction<br>TEMP_VALUE =                                 |                |                                                          |                                                                                         |                                                    |                                                                         |  |  |

| After Instructic<br>TEMP_VAI<br>If TEMP_V<br>PC<br>If TEMP_V<br>PC |                | ALUE =<br>VALUE =<br>=                                   | 0;<br>Addre:<br>0;                                                                      | _VALU<br>ss (ze<br>ss (nz                          | RO)                                                                     |  |  |

| Syntax:<br>Operand   | ds:         | [ label ]                                           | 0010                                                                                                                                                                                                                | N    |      |  |  |  |

|----------------------|-------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--|--|--|

| Operand              | IS'         | 0 / 1/ / 04                                         | 04                                                                                                                                                                                                                  |      |      |  |  |  |

|                      |             | 0 ≤ k ≤ 81                                          | •                                                                                                                                                                                                                   |      |      |  |  |  |

| Operation:           |             | k<12:8> -                                           | $k \rightarrow PC<12:0>;$<br>$k<12:8> \rightarrow PCLATH<4:0>,$<br>$PC<15:13> \rightarrow PCLATH<7:5>$                                                                                                              |      |      |  |  |  |

| Status A             | Affected:   | None                                                |                                                                                                                                                                                                                     |      |      |  |  |  |

| Encodin              | ig:         | 110k                                                | kkkk                                                                                                                                                                                                                | kkkk | kkkl |  |  |  |

| Description:         |             | The thirtee<br>loaded into<br>upper eigh<br>PCLATH. | anywhere within an 8K page boundary.<br>The thirteen bit immediate value is<br>loaded into PC bits <12:0>. Then the<br>upper eight bits of PC are loaded into<br>PCLATH. GOTO is always a two-cycle<br>instruction. |      |      |  |  |  |

| Words:               |             | 1                                                   |                                                                                                                                                                                                                     |      |      |  |  |  |

| Cycles:              |             | 2                                                   |                                                                                                                                                                                                                     |      |      |  |  |  |

| Q Cycle              | Activity:   |                                                     |                                                                                                                                                                                                                     |      |      |  |  |  |

|                      | Q1          | Q2                                                  | Q3                                                                                                                                                                                                                  | 5    | Q4   |  |  |  |

| E                    | Decode      | Read literal<br>'k'<7:0>                            | Execu                                                                                                                                                                                                               | ute  | NOP  |  |  |  |

| For                  | ced NOP     | NOP                                                 | Execu                                                                                                                                                                                                               | ute  | NOP  |  |  |  |

| Example              | <u>e</u> :  | GOTO THE                                            | RE                                                                                                                                                                                                                  |      |      |  |  |  |

| Afte                 | er Instruct | tion                                                |                                                                                                                                                                                                                     |      |      |  |  |  |

| PC = Address (THERE) |             |                                                     |                                                                                                                                                                                                                     |      |      |  |  |  |

| TLWT                                   | -                                            | Table Lat                            | ch Write                            |                       | TSTFSZ                                    | Test f, sk            | ip if 0                                                                     |        |  |

|----------------------------------------|----------------------------------------------|--------------------------------------|-------------------------------------|-----------------------|-------------------------------------------|-----------------------|-----------------------------------------------------------------------------|--------|--|

| Synta                                  | x:                                           | [ label ]                            | TLWT t,f                            |                       | Syntax:                                   | [ label ]             | TSTFSZ f                                                                    |        |  |

| Opera                                  | ands:                                        | 0 ≤ f ≤ 25                           | $0 \le f \le 255$                   |                       | Operands:                                 | $0 \le f \le 255$     |                                                                             |        |  |

|                                        |                                              | t ∈ [0,1]                            |                                     | Operation:            | skip if f = 0                             |                       |                                                                             |        |  |

| Operation:                             |                                              | If $t = 0$ ,                         |                                     | Status Affected: None |                                           |                       |                                                                             |        |  |

|                                        |                                              | $f \rightarrow TBLATL;$<br>If t = 1, |                                     |                       | Encoding:                                 | 0011                  | 0011 fff                                                                    | f ffff |  |

|                                        |                                              | $f \rightarrow TBLATH$               |                                     | Description:          | If 'f' = 0, the next instruction, fetched |                       |                                                                             |        |  |

| Status                                 | s Affected:                                  | None                                 |                                     |                       | ·                                         | -                     | during the current instruction execution                                    |        |  |

| Encod                                  | ding:                                        | 1010                                 | 01tx ff:                            | ff ffff               |                                           |                       | is discarded and an NOP is executed<br>making this a two-cycle instruction. |        |  |

| Descr                                  | ription:                                     | Data from                            | file register 'f' i                 | s written into        | Words:                                    | 1                     |                                                                             |        |  |

|                                        |                                              |                                      | able latch (TBI                     |                       | Cycles:                                   | 1 (2)                 |                                                                             |        |  |

|                                        |                                              | -                                    | h byte is writte                    |                       | Q Cycle Activity:                         |                       |                                                                             |        |  |

|                                        |                                              |                                      | byte is written<br>ction is used in |                       | Q1                                        | Q2                    | Q3                                                                          | Q4     |  |

|                                        |                                              | with TABL                            | v⊤ to transfer d                    | lata from data        | Decode                                    | Read                  | Execute                                                                     | NOP    |  |

|                                        |                                              | •                                    | program mem                         | iory.                 |                                           | register 'f'          |                                                                             |        |  |

| Words                                  |                                              | 1                                    |                                     |                       | lf skip:<br>Q1                            | Q2                    | Q3                                                                          | Q4     |  |

| Cycle                                  |                                              | 1                                    |                                     |                       | Forced NOP                                | NOP                   | Execute                                                                     | NOP    |  |

| Q Cyc                                  | cle Activity:                                | 00                                   | 00                                  | 04                    | Example:                                  | HERE                  | I I I I I I I I I I I I I I I I I I I                                       |        |  |

| Q1 Q2<br>Decode Read E<br>register 'f' |                                              | Q3<br>Execute                        | Q4<br>Write                         | Example:              | NZERO :                                   |                       |                                                                             |        |  |

|                                        |                                              |                                      | register                            |                       | ZERO :                                    |                       |                                                                             |        |  |

|                                        |                                              |                                      |                                     | TBLATH or<br>TBLATL   | Before Instru<br>PC = Ado                 | lction<br>dress(HERE) |                                                                             |        |  |

| <u>Exam</u>                            | <u>ple</u> :                                 | TLWT                                 | t, RAM                              |                       | After Instruct                            |                       |                                                                             |        |  |

| В                                      | efore Instru                                 | uction                               |                                     |                       | If CNT<br>PC                              |                       | 00,<br>Idress (ZERO)                                                        |        |  |

|                                        | t                                            | = 0                                  |                                     |                       | If CNT                                    |                       | 00,                                                                         |        |  |

|                                        | RAM = 0xB7<br>TBLAT = 0x0000 (TBLATH = 0x00) |                                      | 0x00)                               | PC                    | = Ac                                      | dress (NZERO          | )                                                                           |        |  |

|                                        |                                              |                                      | (TBLATL =                           |                       |                                           |                       |                                                                             |        |  |

| A                                      | fter Instruc                                 |                                      |                                     |                       |                                           |                       |                                                                             |        |  |

|                                        | RAM<br>TBLAT                                 | = 0xB7<br>= 0x00B7                   | ′ (TBLATH =                         | 0×00)                 |                                           |                       |                                                                             |        |  |

|                                        | IDEAI                                        | - 00000                              | (TBLATL =                           | ,                     |                                           |                       |                                                                             |        |  |

| В                                      | efore Instru                                 | uction                               |                                     |                       |                                           |                       |                                                                             |        |  |

|                                        | t                                            | = 1                                  |                                     |                       |                                           |                       |                                                                             |        |  |

|                                        | RAM<br>TBLAT                                 | = 0xB7<br>= 0x0000                   | ) (TBLATH =                         | 0x00)                 |                                           |                       |                                                                             |        |  |

|                                        |                                              |                                      | (TBLATL =                           | ,                     |                                           |                       |                                                                             |        |  |

| A                                      | fter Instruc                                 |                                      |                                     |                       |                                           |                       |                                                                             |        |  |

|                                        | RAM<br>TBLAT                                 | = 0xB7<br>= 0xB700                   | ) (TBLATH =                         |                       |                                           |                       |                                                                             |        |  |

|                                        |                                              | $= 0 \times B700$                    |                                     |                       |                                           |                       |                                                                             |        |  |

### Applicable Devices 42 R42 42A 43 R43 44

| DC CHARACTERISTICS |             |                                                                   | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature<br>$-40^{\circ}C \le TA \le +40^{\circ}C$<br>Operating voltage VDD range as described in Section 17.1 |           |               |          |                                                            |  |  |

|--------------------|-------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|----------|------------------------------------------------------------|--|--|

| Parameter<br>No.   | Sym         | Characteristic                                                    | Min                                                                                                                                                                                    | Typ†      | Max           | Units    |                                                            |  |  |

|                    |             | Internal Program Memory<br>Programming Specs (Note 4)             |                                                                                                                                                                                        |           |               |          |                                                            |  |  |

| D110<br>D111       | Vpp<br>Vddp | Voltage on MCLR/VPP pin<br>Supply voltage during<br>programming   | 12.75<br>4.75                                                                                                                                                                          | _<br>5.0  | 13.25<br>5.25 | V<br>V   | Note 5                                                     |  |  |

| D112<br>D113       | Ipp<br>Iddp | Current into MCLR/VPP pin<br>Supply current during<br>programming |                                                                                                                                                                                        | 25 ‡<br>_ | 50 ‡<br>30 ‡  | mA<br>mA |                                                            |  |  |

| D114               |             | Programming pulse width                                           | 10                                                                                                                                                                                     | 100       | 1000          | μs       | Terminated via internal/exter-<br>nal interrupt or a reset |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

**Note:** When using the Table Write for internal programming, the device temperature must be less than 40°C.

### Applicable Devices 42 R42 42A 43 R43 44

#### FIGURE 17-11: MEMORY INTERFACE WRITE TIMING

#### TABLE 17-11: MEMORY INTERFACE WRITE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                | Min          | Тур†      | Max | Units | Conditions |

|------------------|----------|---------------------------------------------------------------|--------------|-----------|-----|-------|------------|

| 150              | TadV2alL | AD<15:0> (address) valid to ALE↓<br>(address setup time)      | 0.25Tcy - 30 |           |     | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)               | 0            | _         | _   | ns    |            |

| 152              | TadV2wrL | Data out valid to $\overline{WR}\downarrow$ (data setup time) | 0.25Tcy - 40 | —         | —   | ns    |            |

| 153              | TwrH2adI | WR↑ to data out invalid<br>(data hold time)                   | _            | 0.25Tcy § | —   | ns    |            |

| 154              | TwrL     | WR pulse width                                                | —            | 0.25Tcy § | _   | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification is guaranteed by design.

### Applicable Devices 42 R42 42A 43 R43 44

## 18.0 PIC17C42 DC AND AC CHARACTERISTICS

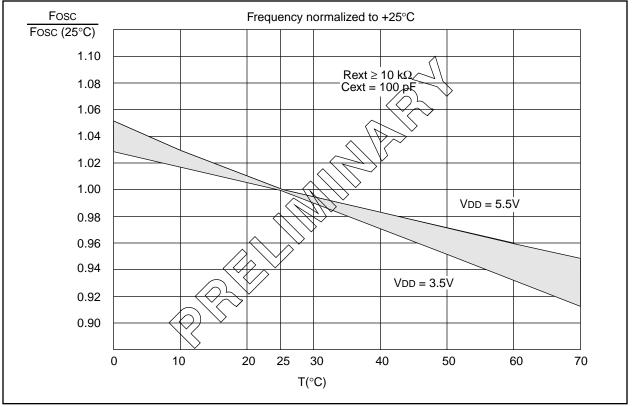

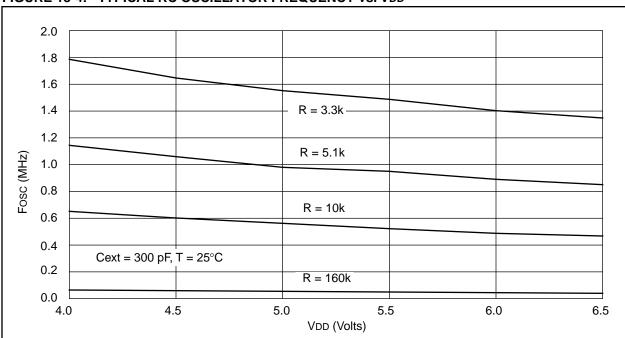

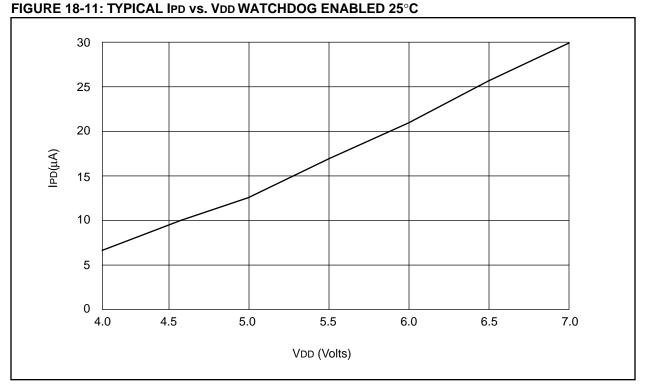

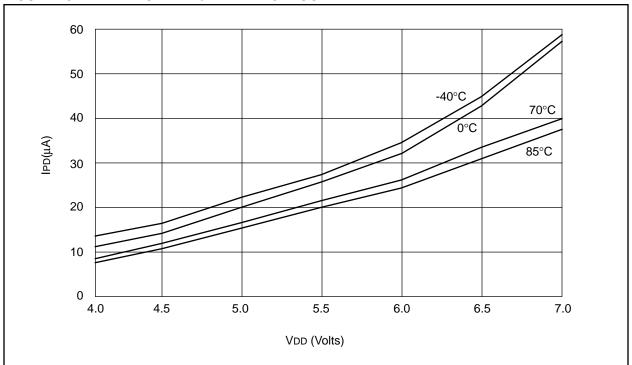

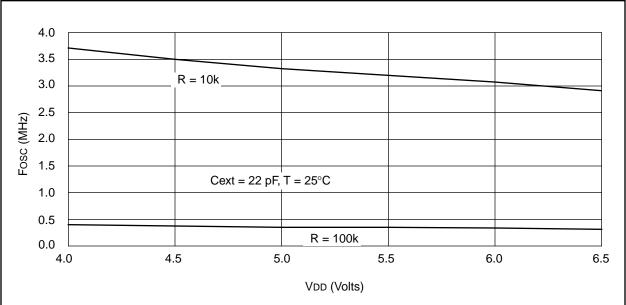

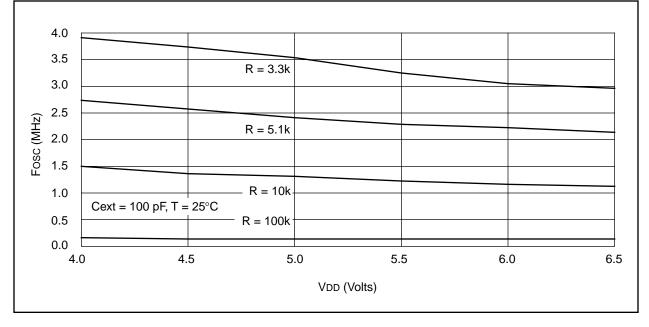

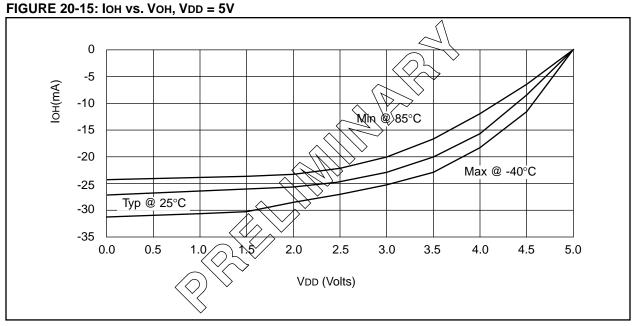

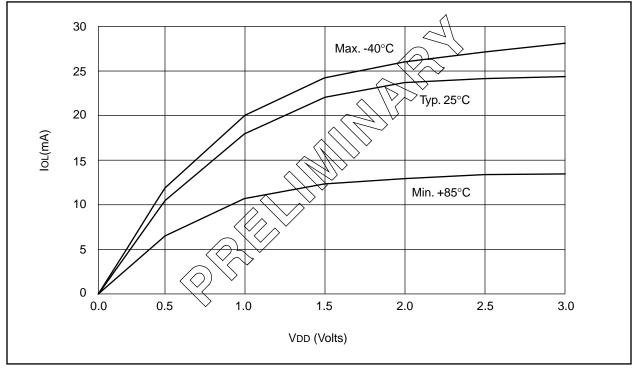

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed. In some graphs or tables the data presented are outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are ensured to operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

#### TABLE 18-1: PIN CAPACITANCE PER PACKAGE TYPE

| Pin Name                            | Typical Capacitance (pF) |             |             |             |  |  |  |  |

|-------------------------------------|--------------------------|-------------|-------------|-------------|--|--|--|--|

| Pin Name                            | 40-pin DIP               | 44-pin PLCC | 44-pin MQFP | 44-pin TQFP |  |  |  |  |

| All pins, except MCLR, VDD, and VSS | 10                       | 10          | 10          | 10          |  |  |  |  |

| MCLR pin                            | 20                       | 20          | 20          | 20          |  |  |  |  |

#### FIGURE 18-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

Applicable Devices 42 R42 42A 43 R43 44

### FIGURE 18-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

#### TABLE 18-2: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average<br>Fosc @ 5V, 25°C |       |  |

|--------|------|----------------------------|-------|--|

| 22 pF  | 10k  | 3.33 MHz                   | ± 12% |  |

|        | 100k | 353 kHz                    | ± 13% |  |

| 100 pF | 3.3k | 3.54 MHz                   | ± 10% |  |

|        | 5.1k | 2.43 MHz                   | ± 14% |  |

|        | 10k  | 1.30 MHz                   | ± 17% |  |

|        | 100k | 129 kHz                    | ± 10% |  |

| 300 pF | 3.3k | 1.54 MHz                   | ± 14% |  |

|        | 5.1k | 980 kHz                    | ± 12% |  |

|        | 10k  | 564 kHz                    | ± 16% |  |

|        | 160k | 35 kHz                     | ± 18% |  |

Applicable Devices 42 R42 42A 43 R43 44

FIGURE 18-12: MAXIMUM IPD vs. VDD WATCHDOG ENABLED

### Applicable Devices 42 R42 42A 43 R43 44

### FIGURE 20-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

#### FIGURE 20-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

## Applicable Devices 42 R42 42A 43 R43 44

FIGURE 20-16: IOL vs. VOL, VDD = 3V

NOTES: