Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

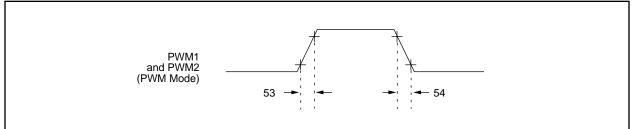

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 232 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-25-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register  | Address | Power-on Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEF<br>through interrupt |

|-----------|---------|----------------|-------------------------|-----------------------------------------|

| Bank 2    |         | -              |                         | ·                                       |

| TMR1      | 10h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| TMR2      | 11h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| TMR3L     | 12h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| TMR3H     | 13h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR1       | 14h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR2       | 15h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR3/CA1L  | 16h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| PR3/CA1H  | 17h     | XXXX XXXX      | սսսս սսսս               | սսսս սսսս                               |

| Bank 3    |         |                |                         |                                         |

| PW1DCL    | 10h     | xx             | uu                      | uu                                      |

| PW2DCL    | 11h     | xx             | uu                      | uu                                      |

| PW1DCH    | 12h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| PW2DCH    | 13h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| CA2L      | 14h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| CA2H      | 15h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| TCON1     | 16h     | 0000 0000      | 0000 0000               | uuuu uuuu                               |

| TCON2     | 17h     | 0000 0000      | 0000 0000               | uuuu uuuu                               |

| Unbanked  |         |                |                         |                                         |

| PRODL (5) | 18h     | XXXX XXXX      | นนนน นนนน               | นนนน นนนน                               |

| PRODH (5) | 19h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

## TABLE 4-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (Cont.'d)

Legend: u = unchanged, x = unknown, - = unimplemented read as '0', q = value depends on condition. Note 1: One or more bits in INTSTA, PIR will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

3: See Table 4-3 for reset value of specific condition.

4: Only applies to the PIC17C42.

5: Does not apply to the PIC17C42.

### 5.3 <u>Peripheral Interrupt Request Register</u> (PIR)

This register contains the individual flag bits for the peripheral interrupts.

**Note:** These bits will be set by the specified condition, even if the corresponding interrupt enable bit is cleared (interrupt disabled), or the GLINTD bit is set (all interrupts disabled). Before enabling an interrupt, the user may wish to clear the interrupt flag to ensure that the program does not immediately branch to the peripheral interrupt service routine.

# FIGURE 5-4: PIR REGISTER (ADDRESS: 16h, BANK 1)

|        | 0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 R-0                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| RBIF   |                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| bit7   | bit0 W = Writable bit<br>-n = Value at POR reset                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| bit 7: | <b>RBIF</b> : PORTB Interrupt on Change Flag bit<br>1 = One of the PORTB inputs changed (Software must end the mismatch condition)<br>0 = None of the PORTB inputs have changed                                                                                              |  |  |  |  |  |  |  |  |

| bit 6: | TMR3IF: Timer3 Interrupt Flag bit<br>If Capture1 is enabled (CA1/PR3 = 1)<br>1 = Timer3 overflowed<br>0 = Timer3 did not overflow                                                                                                                                            |  |  |  |  |  |  |  |  |

|        | If Capture1 is disabled (CA1/ $\overline{PR3}$ = 0)<br>1 = Timer3 value has rolled over to 0000h from equalling the period register (PR3H:PR3L) value<br>0 = Timer3 value has not rolled over to 0000h from equalling the period register (PR3H:PR3L) value                  |  |  |  |  |  |  |  |  |

| bit 5: | <b>TMR2IF</b> : Timer2 Interrupt Flag bit<br>1 = Timer2 value has rolled over to 0000h from equalling the period register (PR2) value<br>0 = Timer2 value has not rolled over to 0000h from equalling the period register (PR2) value                                        |  |  |  |  |  |  |  |  |

| bit 4: | <b>TMR1IF</b> : Timer1 Interrupt Flag bit<br>If Timer1 is in 8-bit mode (T16 = 0)<br>1 = Timer1 value has rolled over to 0000h from equalling the period register (PR) value<br>0 = Timer1 value has not rolled over to 0000h from equalling the period register (PR2) value |  |  |  |  |  |  |  |  |

|        | If Timer1 is in 16-bit mode (T16 = 1)<br>1 = TMR1:TMR2 value has rolled over to 0000h from equalling the period register (PR1:PR2) value<br>0 = TMR1:TMR2 value has not rolled over to 0000h from equalling the period register (PR1:PR2) value                              |  |  |  |  |  |  |  |  |

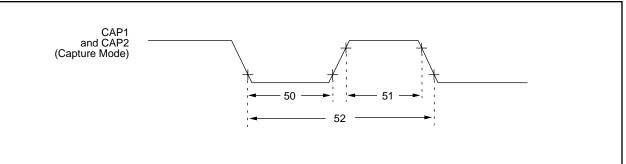

| bit 3: | <b>CA2IF</b> : Capture2 Interrupt Flag bit<br>1 = Capture event occurred on RB1/CAP2 pin<br>0 = Capture event did not occur on RB1/CAP2 pin                                                                                                                                  |  |  |  |  |  |  |  |  |

| bit 2: | <b>CA1IF</b> : Capture1 Interrupt Flag bit<br>1 = Capture event occurred on RB0/CAP1 pin<br>0 = Capture event did not occur on RB0/CAP1 pin                                                                                                                                  |  |  |  |  |  |  |  |  |

| bit 1: | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = Transmit buffer is empty<br>0 = Transmit buffer is full                                                                                                                                                               |  |  |  |  |  |  |  |  |

| bit 0: | RCIF: USART Receive Interrupt Flag bit<br>1 = Receive buffer is full<br>0 = Receive buffer is empty                                                                                                                                                                          |  |  |  |  |  |  |  |  |

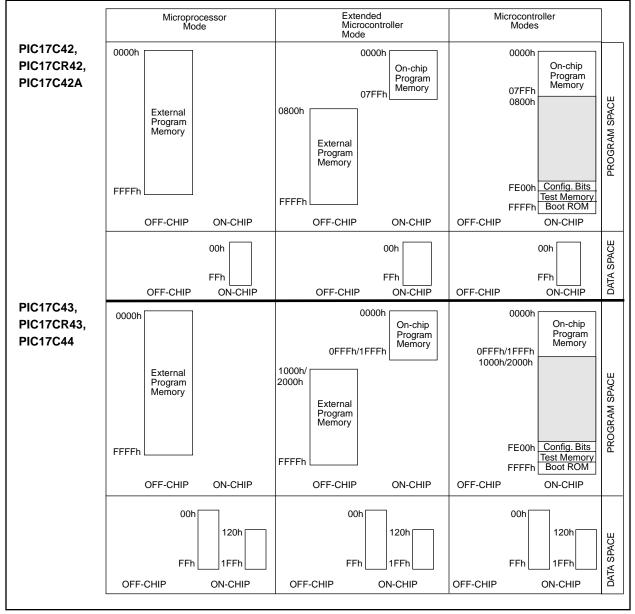

# TABLE 6-1: MODE MEMORY ACCESS

| Operating<br>Mode            | Internal<br>Program<br>Memory | Configuration Bits,<br>Test Memory,<br>Boot ROM |

|------------------------------|-------------------------------|-------------------------------------------------|

| Microprocessor               | No Access                     | No Access                                       |

| Microcontroller              | Access                        | Access                                          |

| Extended<br>Microcontroller  | Access                        | No Access                                       |

| Protected<br>Microcontroller | Access                        | Access                                          |

The PIC17C4X can operate in modes where the program memory is off-chip. They are the microprocessor and extended microcontroller modes. The microprocessor mode is the default for an unprogrammed device.

Regardless of the processor mode, data memory is always on-chip.

## FIGURE 6-2: MEMORY MAP IN DIFFERENT MODES

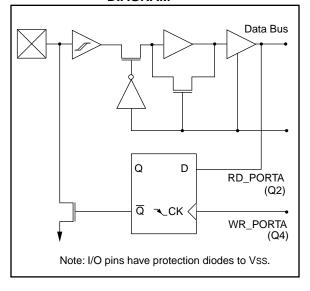

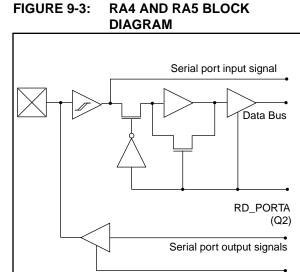

FIGURE 9-2: RA2 AND RA3 BLOCK DIAGRAM

$\overline{OE}$  = SPEN,SYNC,TXEN,  $\overline{CREN}$ ,  $\overline{SREN}$  for RA4  $\overline{OE}$  = SPEN ( $\overline{SYNC}$ +SYNC, $\overline{CSRC}$ ) for RA5

Note: I/O pins have protection diodes to VDD and VSS.

| TABLE 9-1: | PO | RTA FUNCTI | ONS |

|------------|----|------------|-----|

|            |    |            |     |

. . . . .

\_ \_ \_ \_ . . . . . . . . . . . . . . .

| Name      | Bit0 | Buffer Type | Function                                                                            |

|-----------|------|-------------|-------------------------------------------------------------------------------------|

| RA0/INT   | bit0 | ST          | Input or external interrupt input.                                                  |

| RA1/T0CKI | bit1 | ST          | Input or clock input to the TMR0 timer/counter, and/or an external interrupt input. |

| RA2       | bit2 | ST          | Input/Output. Output is open drain type.                                            |

| RA3       | bit3 | ST          | Input/Output. Output is open drain type.                                            |

| RA4/RX/DT | bit4 | ST          | Input or USART Asynchronous Receive or USART Synchronous Data.                      |

| RA5/TX/CK | bit5 | ST          | Input or USART Asynchronous Transmit or USART Synchronous Clock.                    |

| RBPU      | bit7 |             | Control bit for PORTB weak pull-ups.                                                |

Legend: ST = Schmitt Trigger input.

## TABLE 9-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address       | Name  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|-------|--------|-------|-------|-------|-------|-------|-----------|---------|-------------------------------|-----------------------------------------|

| 10h, Bank 0   | PORTA | RBPU   | _     | RA5   | RA4   | RA3   | RA2   | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                               |

| 05h, Unbanked | TOSTA | INTEDG | T0SE  | TOCS  | PS3   | PS2   | PS1   | PS0       | _       | 0000 000-                     | 0000 000-                               |

| 13h, Bank 0   | RCSTA | SPEN   | RC9   | SREN  | CREN  | —     | FERR  | OERR      | RC9D    | 0000 -00x                     | 0000 -00u                               |

| 15h, Bank 0   | TXSTA | CSRC   | TX9   | TXEN  | SYNC  | —     | —     | TRMT      | TX9D    | 00001x                        | 0000lu                                  |

Legend: x = unknown, u = unchanged, - = unimplemented reads as '0'. Shaded cells are not used by PORTA. Note 1: Other (non power-up) resets include: external reset through  $\overline{MCLR}$  and the Watchdog Timer Reset.

## 9.5 I/O Programming Considerations

#### 9.5.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. For example, the BCF and BSF instructions read the register into the CPU, execute the bit operation, and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g. bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading a port reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (BCF, BSF, BTG, etc.) on a port, the value of the port pins is read, the desired operation is performed with this value, and the value is then written to the port latch.

Example 9-5 shows the effect of two sequential read-modify-write instructions on an I/O port.

#### EXAMPLE 9-5: READ MODIFY WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORT settings: PORTB<7:4> Inputs PORTB<3:0> Outputs ; ; PORTB<7:6> have pull-ups and are ; not connected to other circuitry ; PORT latch PORT pins ; ; \_\_\_\_\_ \_\_\_\_\_ ; PORTB, 7 BCF 01pp pppp 11pp pppp BCF PORTB, 6 10pp pppp 11pp pppp ; BCF DDRB, 7 10pp pppp 11pp pppp BCF DDRB, 6 10pp pppp 10pp pppp ; ; Note that the user may have expected the ; pin values to be 00pp pppp. The 2nd BCF ; caused RB7 to be latched as the pin value ; (High).

Note: A pin actively outputting a Low or High should not be driven from external devices in order to change the level on this pin (i.e. "wired-or", "wired-and"). The resulting high output currents may damage the device.

#### 9.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 9-9). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before executing the instruction that reads the values on that I/O port. Otherwise, the previous state of that pin may be read into the CPU rather than the "new" state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

## FIGURE 9-9: SUCCESSIVE I/O OPERATION

| Instruction<br>fetched  | Q1  Q2  Q3  Q4<br>PC<br>MOVWF PORTB<br>write to<br>PORTB | PC + 1                           | Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4<br><u>PC+2</u> <u>PC+3</u><br>NOP NOP | Note:<br>This example shows a write to PORTB<br>followed by a read from PORTB.<br>Note that:<br>data setup time = (0.25 Tcy - TPD)<br>where TcY = instruction cycle.<br>TPD = propagation delay |

|-------------------------|----------------------------------------------------------|----------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB7:RB0                 |                                                          |                                  | X                                                             | Therefore, at higher clock<br>frequencies, a write followed by a                                                                                                                                |

|                         |                                                          |                                  | Port pin<br>sampled here                                      | read may be problematic.                                                                                                                                                                        |

| Instruction<br>executed |                                                          | MOVWF PORTB<br>write to<br>PORTB | MOVF PORTB,W NOP                                              |                                                                                                                                                                                                 |

|                         |                                                          |                                  | · · · · ·                                                     |                                                                                                                                                                                                 |

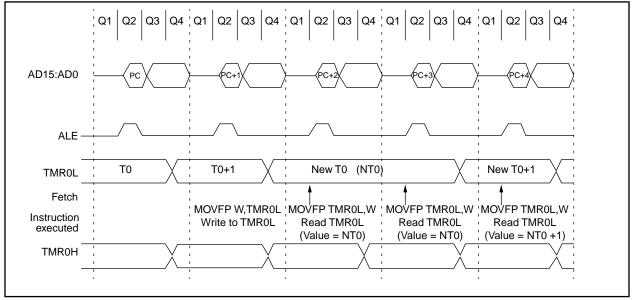

### 11.3 Read/Write Consideration for TMR0

Although TMR0 is a 16-bit timer/counter, only 8-bits at a time can be read or written during a single instruction cycle. Care must be taken during any read or write.

#### 11.3.1 READING 16-BIT VALUE

The problem in reading the entire 16-bit value is that after reading the low (or high) byte, its value may change from FFh to 00h.

Example 11-1 shows a 16-bit read. To ensure a proper read, interrupts must be disabled during this routine.

## EXAMPLE 11-1: 16-BIT READ

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

|--------|--------|-------|-----------------|

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| MOVFP  | TMPLO, | WREG  | ;tmplo -> wreg  |

| CPFSLT | TMR0L  |       | ;tmr0l < wreg?  |

| RETURN |        |       | ;no then return |

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| RETURN |        |       | ;return         |

#### 11.3.2 WRITING A 16-BIT VALUE TO TMR0

Since writing to either TMR0L or TMR0H will effectively inhibit increment of that half of the TMR0 in the next cycle (following write), but not inhibit increment of the other half, the user must write to TMR0L first and TMR0H next in two consecutive instructions, as shown in Example 11-2. The interrupt must be disabled. Any write to either TMR0L or TMR0H clears the prescaler.

#### EXAMPLE 11-2: 16-BIT WRITE

BSF CPUSTA, GLINTD ; Disable interrupt MOVFP RAM\_L, TMROL ; MOVFP RAM\_H, TMROH ; BCF CPUSTA, GLINTD ; Done, enable interrupt

#### 11.4 Prescaler Assignments

Timer0 has an 8-bit prescaler. The prescaler assignment is fully under software control; i.e., it can be changed "on the fly" during program execution. When changing the prescaler assignment, clearing the prescaler is recommended before changing assignment. The value of the prescaler is "unknown," and assigning a value that is less then the present value makes it difficult to take this unknown time into account.

#### FIGURE 11-4: TMR0 TIMING: WRITE HIGH OR LOW BYTE

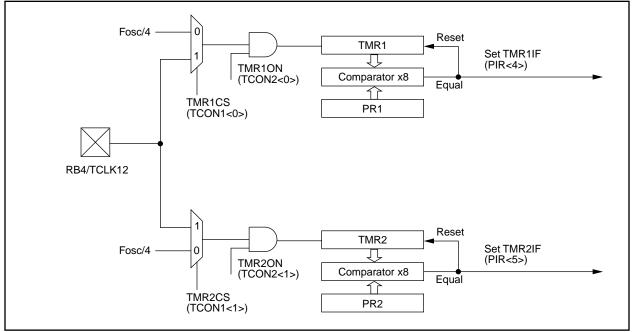

## 12.1 <u>Timer1 and Timer2</u>

#### 12.1.1 TIMER1, TIMER2 IN 8-BIT MODE

Both Timer1 and Timer2 will operate in 8-bit mode when the T16 bit is clear. These two timers can be independently configured to increment from the internal instruction cycle clock or from an external clock source on the RB4/TCLK12 pin. The timer clock source is configured by the TMRxCS bit (x = 1 for Timer1 or = 2 for Timer2). When TMRxCS is clear, the clock source is internal and increments once every instruction cycle (Fosc/4). When TMRxCS is set, the clock source is the RB4/TCLK12 pin, and the timer will increment on every falling edge of the RB4/TCLK12 pin.

The timer increments from 00h until it equals the Period register (PRx). It then resets to 00h at the next increment cycle. The timer interrupt flag is set when the timer is reset. TMR1 and TMR2 have individual interrupt flag bits. The TMR1 interrupt flag bit is latched into TMR1IF, and the TMR2 interrupt flag bit is latched into TMR2IF.

Each timer also has a corresponding interrupt enable bit (TMRxIE). The timer interrupt can be enabled by setting this bit and disabled by clearing this bit. For peripheral interrupts to be enabled, the Peripheral Interrupt Enable bit must be enabled (PEIE is set) and global interrupts must be enabled (GLINTD is cleared).

The timers can be turned on and off under software control. When the Timerx On control bit (TMRxON) is set, the timer increments from the clock source. When TMRxON is cleared, the timer is turned off and cannot cause the timer interrupt flag to be set.

#### 12.1.1.1 EXTERNAL CLOCK INPUT FOR TIMER1 OR TIMER2

When TMRxCS is set, the clock source is the RB4/TCLK12 pin, and the timer will increment on every falling edge on the RB4/TCLK12 pin. The TCLK12 input is synchronized with internal phase clocks. This causes a delay from the time a falling edge appears on TCLK12 to the time TMR1 or TMR2 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

## FIGURE 12-3: TIMER1 AND TIMER2 IN TWO 8-BIT TIMER/COUNTER MODE

## 13.3 USART Synchronous Master Mode

In Master Synchronous mode, the data is transmitted in a half-duplex manner; i.e. transmission and reception do not occur at the same time: when transmitting data, the reception is inhibited and vice versa. The synchronous mode is entered by setting the SYNC (TXSTA<4>) bit. In addition, the SPEN (RCSTA<7>) bit is set in order to configure the RA5 and RA4 I/O ports to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting the CSRC (TXSTA<7>) bit.

#### 13.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 13-3. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer TXREG. TXREG is loaded with data in software. The TSR is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one TCY at the end of the current BRG cycle), TXREG is empty and the TXIF (PIR<1>) bit is set. This interrupt can be enabled/disabled by setting/clearing the TXIE bit (PIE<1>). TXIF will be set regardless of the state of bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of TXREG, TRMT (TXSTA<1>) shows the status of the TSR. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting the TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the RA5/TX/CK pin. Data out is stable around the falling edge of the synchronous clock (Figure 13-10). The transmission can also be started by first loading TXREG and then setting TXEN. This is advantageous when slow baud rates are selected, since BRG is kept in RESET when the TXEN, CREN, and SREN bits are clear. Setting the TXEN bit will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to the TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The RA4/RX/DT and RA5/TX/CK pins will revert to hi-impedance. If either CREN or SREN are set during a transmission, the transmission is aborted and the

RA4/RX/DT pin reverts to a hi-impedance state (for a reception). The RA5/TX/CK pin will remain an output if the CSRC bit is set (internal clock). The transmitter logic is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear the TXEN bit. If the SREN bit is set (to interrupt an ongoing transmission and receive a single word), then after the single word is received, SREN will be cleared and the serial port will revert back to transmitting, since the TXEN bit is still set. The DT line will immediately switch from hi-impedance receive mode to transmit and start driving. To avoid this, TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty). If the TSR was empty and TXREG was written before writing the "new" TX9D, the "present" value of TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (see Baud Rate Generator Section for details).

- 2. Enable the synchronous master serial port by setting the SYNC, SPEN, and CSRC bits.

- 3. Ensure that the CREN and SREN bits are clear (these bits override transmission when set).

- 4. If interrupts are desired, then set the TXIE bit (the GLINTD bit must be clear and the PEIE bit must be set).

- 5. If 9-bit transmission is desired, then set the TX9 bit.

- 6. Start transmission by loading data to the TXREG register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 8. Enable the transmission by setting TXEN.

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the reverse order.

Note: To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

## 14.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLK-OUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation and SLEEP mode, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 14.1).

Under normal operation, the WDT must be cleared on a regular interval. This time is less the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

#### 14.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms, (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a postscaler with a division ratio of up to 1:256 can be assigned to the WDT. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

#### 14.3.2 CLEARING THE WDT AND POSTSCALER

The WDT and postscaler are cleared when:

- The device is in the reset state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the reset state.

#### 14.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT postscaler) it may take several seconds before a WDT time-out occurs.

The WDT and postscaler is the Power-up Timer during the Power-on Reset sequence.

#### 14.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the  $\overline{\text{TO}}$  bit is cleared (device is not reset). The CLRWDT instruction can be used to set the  $\overline{\text{TO}}$  bit. This allows the WDT to be a simple overflow timer. When in sleep, the WDT does not increment.

| ADDLW                             | ADD Literal to WREG                                                                                          |                   |      |                  |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------|------|------------------|--|--|--|--|

| Syntax:                           | [label] A                                                                                                    | DLW               | k    |                  |  |  |  |  |

| Operands:                         | $0 \le k \le 25$                                                                                             | $0 \le k \le 255$ |      |                  |  |  |  |  |

| Operation:                        | (WREG) + k $\rightarrow$ (WREG)                                                                              |                   |      |                  |  |  |  |  |

| Status Affected:                  | OV, C, DC                                                                                                    | C, Z              |      |                  |  |  |  |  |

| Encoding:                         | 1011                                                                                                         | 0001              | kkkk | kkkk             |  |  |  |  |

| Description:                      | Pescription: The contents of WREG are added to the<br>8-bit literal 'k' and the result is placed in<br>WREG. |                   |      |                  |  |  |  |  |

| Words:                            | 1                                                                                                            |                   |      |                  |  |  |  |  |

| Cycles:                           | 1                                                                                                            |                   |      |                  |  |  |  |  |

| Q Cycle Activity:                 |                                                                                                              |                   |      |                  |  |  |  |  |

| Q1                                | Q2                                                                                                           | Q3                | 3    | Q4               |  |  |  |  |

| Decode                            | Read<br>literal 'k'                                                                                          | Execu             |      | Vrite to<br>WREG |  |  |  |  |

| Example:                          | ADDLW                                                                                                        | 0x15              |      |                  |  |  |  |  |

| Before Instruction<br>WREG = 0x10 |                                                                                                              |                   |      |                  |  |  |  |  |

| ADDWF                         | ADD WRE                                    | EG to f                            |            |                       |  |  |  |  |

|-------------------------------|--------------------------------------------|------------------------------------|------------|-----------------------|--|--|--|--|

| Syntax:                       | [ <i>label</i> ] A[                        | [label]ADDWF f,d                   |            |                       |  |  |  |  |

| Operands:                     | $0 \le f \le 255$ $d \in [0,1]$            | $0 \le f \le 255$<br>$d \in [0,1]$ |            |                       |  |  |  |  |

| Operation:                    | (WREG) +                                   | - (f) $\rightarrow$ (de            | est)       |                       |  |  |  |  |

| Status Affected:              | OV, C, DC                                  | , Z                                |            |                       |  |  |  |  |

| Encoding:                     | 0000                                       | 111d                               | ffff       | ffff                  |  |  |  |  |

| Description:                  | Add WREG<br>result is sto<br>result is sto | red in WRE                         | EG. If 'd' | is 1 the              |  |  |  |  |

| Words:                        | 1                                          |                                    |            |                       |  |  |  |  |

| Cycles:                       | 1                                          |                                    |            |                       |  |  |  |  |

| Q Cycle Activity:             |                                            |                                    |            |                       |  |  |  |  |

| Q1                            | Q2                                         | Q3                                 |            | Q4                    |  |  |  |  |

| Decode                        | Read<br>register 'f'                       | Execute                            | ·   ·      | /rite to<br>stination |  |  |  |  |

| Example:                      | ADDWF                                      | REG, 0                             |            |                       |  |  |  |  |

| Before Instru<br>WREG<br>REG  | iction<br>= 0x17<br>= 0xC2                 |                                    |            |                       |  |  |  |  |

| After Instruct<br>WREG<br>REG | tion<br>= 0xD9<br>= 0xC2                   |                                    |            |                       |  |  |  |  |

After Instruction WREG = 0x25

| CPFSEQ                                         | Compare f with WREG, skip if f = WREG                                                                                                                                                                                                                              |                                                | CPF    | SGT        | -                                             | Compare f with WREG,<br>skip if f > WREG                                               |                                                                                          |               |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------|------------|-----------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------|--|

| Syntax:                                        | [label]                                                                                                                                                                                                                                                            | CPFSEQ f                                       |        | Syn        | tax:                                          | [label]                                                                                | CPFSGT f                                                                                 |               |  |

| Operands:                                      | $0 \le f \le 255$                                                                                                                                                                                                                                                  | 5                                              |        | Ope        | rands:                                        | $0 \le f \le 255$                                                                      | $0 \le f \le 255$                                                                        |               |  |

| Operation:                                     | (f) – (WREG),<br>skip if (f) = (WREG)<br>(unsigned comparison)                                                                                                                                                                                                     |                                                | Ope    | ration:    | skip if (f) >                                 | (f) – (WREG),<br>skip if (f) > (WREG)<br>(unsigned comparison)                         |                                                                                          |               |  |

| Status Affected:                               | None                                                                                                                                                                                                                                                               |                                                |        | Stat       | us Affected:                                  | None                                                                                   |                                                                                          |               |  |

| Encoding:                                      | 0011                                                                                                                                                                                                                                                               | 0001 fff                                       | f ffff | Enc        | oding:                                        | 0011                                                                                   | 0010 ff:                                                                                 | ff ffff       |  |

| Description:                                   | Compares the contents of data memory<br>location 'f' to the contents of WREG by<br>performing an unsigned subtraction.<br>If 'f' = WREG then the fetched instruc-<br>tion is discarded and an NOP is exe-<br>cuted instead making this a two-cycle<br>instruction. |                                                |        | Des        | cription:                                     | location 'f' t<br>by performi<br>If the conte<br>WREG the<br>discarded a<br>instead ma | o the contents<br>ng an unsigne<br>nts of 'f' > the<br>n the fetched in<br>and an NOP is | nstruction is |  |

| Words:                                         | 1                                                                                                                                                                                                                                                                  |                                                |        | 14/0 -     | de .                                          | tion.<br>1                                                                             |                                                                                          |               |  |

| Cycles:                                        | 1 (2)                                                                                                                                                                                                                                                              |                                                |        | Wor        |                                               | -                                                                                      |                                                                                          |               |  |

| Q Cycle Activity:                              |                                                                                                                                                                                                                                                                    |                                                |        | Cyc        |                                               | 1 (2)                                                                                  |                                                                                          |               |  |

| Q1                                             | Q2                                                                                                                                                                                                                                                                 | Q3                                             | Q4     | QC         | ycle Activity:<br>Q1                          | Q2                                                                                     | Q3                                                                                       | Q4            |  |

| Decode                                         | Read<br>register 'f'                                                                                                                                                                                                                                               | Execute                                        | NOP    |            | Decode                                        | Read                                                                                   | Execute                                                                                  | NOP           |  |

| If skip:                                       |                                                                                                                                                                                                                                                                    |                                                |        | lf sk      | in:                                           | register 'f'                                                                           |                                                                                          |               |  |

| Q1                                             | Q2                                                                                                                                                                                                                                                                 | Q3                                             | Q4     |            | Q1                                            | Q2                                                                                     | Q3                                                                                       | Q4            |  |

| Forced NOP                                     | NOP                                                                                                                                                                                                                                                                | Execute                                        | NOP    |            | Forced NOP                                    | NOP                                                                                    | Execute                                                                                  | NOP           |  |

| <u>Example</u> :                               | NEQUAL                                                                                                                                                                                                                                                             | CPFSEQ REG<br>:<br>:                           |        | <u>Exa</u> | mple:                                         | HERE<br>NGREATER<br>GREATER                                                            | CPFSGT RE<br>:<br>:                                                                      | G             |  |

| Before Instru<br>PC Addre                      |                                                                                                                                                                                                                                                                    |                                                |        |            | Before Instru                                 | -                                                                                      | ·                                                                                        |               |  |

| WREG<br>REG                                    | ess = HE<br>= ?<br>= ?                                                                                                                                                                                                                                             | RE                                             |        |            | PC<br>WREG                                    |                                                                                        | dress (HERE)                                                                             |               |  |

| After Instruct<br>If REG<br>PC<br>If REG<br>PC | = W<br>= Ac<br>≠ W                                                                                                                                                                                                                                                 | REG;<br>Idress (EQUAL<br>REG;<br>Idress (NEQUA |        |            | After Instruc<br>If REG<br>PC<br>If REG<br>PC | > Wi<br>= Ad<br>≤ Wi                                                                   | REG;<br>Idress (GREAT<br>REG;<br>Idress (NGREZ                                           |               |  |

| DCF               | SNZ                                                          | Decreme                                                                          | nt f, skip if                                                                                                                                | not (                                                  | 0                                              |

|-------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|

| Syn               | tax:                                                         | [ <i>label</i> ] D                                                               | CFSNZ f,c                                                                                                                                    | 1                                                      |                                                |

| Ope               | rands:                                                       | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                                          | 5                                                                                                                                            |                                                        |                                                |

| Ope               | ration:                                                      | (f) – 1 $\rightarrow$ skip if not                                                |                                                                                                                                              |                                                        |                                                |

| Stat              | us Affected:                                                 | None                                                                             |                                                                                                                                              |                                                        |                                                |

| Enc               | oding:                                                       | 0010                                                                             | 011d f:                                                                                                                                      | Eff                                                    | ffff                                           |

| Des               | cription:                                                    | mented. If<br>WREG. If back in reg<br>If the result<br>which is all<br>and an NO | hts of register<br>d' is 0 the res<br>d' is 1 the res<br>gister 'f'.<br>t is not 0, the<br>ready fetched<br>P is executed<br>-cycle instruct | sult is<br>sult is p<br>next ir<br>I, is di<br>d inste | placed in<br>placed<br>nstruction,<br>scarded, |

| Wor               | ds:                                                          | 1                                                                                |                                                                                                                                              |                                                        |                                                |

| Cyc               | les:                                                         | 1(2)                                                                             |                                                                                                                                              |                                                        |                                                |

| Q Cycle Activity: |                                                              |                                                                                  |                                                                                                                                              |                                                        |                                                |

| Q1<br>Decode      |                                                              | Q2                                                                               | Q3                                                                                                                                           |                                                        | Q4                                             |

|                   |                                                              | Read<br>register 'f'                                                             | Execute                                                                                                                                      |                                                        | Write to<br>estination                         |

| lf sk             | ip:                                                          |                                                                                  |                                                                                                                                              |                                                        |                                                |

|                   | Q1                                                           | Q2                                                                               | Q3                                                                                                                                           |                                                        | Q4                                             |

|                   | Forced NOP                                                   | NOP                                                                              | Execute                                                                                                                                      |                                                        | NOP                                            |

| <u>Example</u> :  |                                                              | HERE<br>ZERO<br>NZERO                                                            | DCFSNZ TI<br>:<br>:                                                                                                                          | EMP,                                                   | 1                                              |

|                   | Before Instru<br>TEMP_V                                      |                                                                                  | ?                                                                                                                                            |                                                        |                                                |

|                   | After Instruct<br>TEMP_V<br>If TEMP_<br>PC<br>If TEMP_<br>PC | ALUE =<br>VALUE =<br>=                                                           | TEMP_VA<br>0;<br>Address (<br>0;<br>Address (                                                                                                | ZERO                                                   | )                                              |

| Synta             | av.          | [ lahel ]                                  | [ <i>label</i> ] GOTO k                                                                                                                                                                                             |      |      |  |  |  |  |

|-------------------|--------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--|--|--|--|

| -                 | ands:        |                                            | $0 \le k \le 8191$                                                                                                                                                                                                  |      |      |  |  |  |  |

| •                 |              | $k \rightarrow PC < 12:0>;$                |                                                                                                                                                                                                                     |      |      |  |  |  |  |

| Oper              | ation:       | k<12:8> -                                  | $k < 12:8> \rightarrow PCLATH < 4:0>,$<br>$PC < 15:13> \rightarrow PCLATH < 7:5>$                                                                                                                                   |      |      |  |  |  |  |

| Statu             | is Affected: | None                                       |                                                                                                                                                                                                                     |      |      |  |  |  |  |

| Enco              | ding:        | 110k                                       | kkkk                                                                                                                                                                                                                | kkkk | kkkl |  |  |  |  |

|                   |              | The thirteen<br>loaded into<br>upper eight | anywhere within an 8K page boundary.<br>The thirteen bit immediate value is<br>loaded into PC bits <12:0>. Then the<br>upper eight bits of PC are loaded into<br>PCLATH. GOTO is always a two-cycle<br>instruction. |      |      |  |  |  |  |

| Word              | ls:          | 1                                          |                                                                                                                                                                                                                     |      |      |  |  |  |  |

| Cycles:           |              | 2                                          |                                                                                                                                                                                                                     |      |      |  |  |  |  |

| Q Cycle Activity: |              |                                            |                                                                                                                                                                                                                     |      |      |  |  |  |  |

| _                 | Q1           | Q2                                         | Q3                                                                                                                                                                                                                  | 3    | Q4   |  |  |  |  |

|                   | Decode       | Read literal<br>'k'<7:0>                   | Execu                                                                                                                                                                                                               | ute  | NOP  |  |  |  |  |

|                   |              |                                            |                                                                                                                                                                                                                     |      |      |  |  |  |  |

|                   | Forced NOP   | NOP                                        | Execu                                                                                                                                                                                                               | ute  | NOP  |  |  |  |  |

| Exan              |              | -                                          |                                                                                                                                                                                                                     | ute  | NOP  |  |  |  |  |

| IORWF                    | Inclusive            |                                                   | with f               | LCALL          | Long Cal                                  | I                                            |                               |

|--------------------------|----------------------|---------------------------------------------------|----------------------|----------------|-------------------------------------------|----------------------------------------------|-------------------------------|

| Syntax:                  | [ label ]            | ORWF f,d                                          |                      | Syntax:        | [ label ]                                 | LCALL k                                      |                               |

| Operands:                | $0 \le f \le 255$    | 5                                                 |                      | Operands:      | $0 \le k \le 25$                          | 5                                            |                               |

|                          | d ∈ [0,1]            |                                                   |                      | Operation:     | PC + 1 $\rightarrow$                      | TOS;                                         |                               |

| Operation:               | (WREG) .             | $OR.\left(f ight) ightarrow\left(de ight)$        | est)                 |                | $k \rightarrow PCL$ ,                     | (PCLATH) -                                   | $\rightarrow$ PCH             |

| Status Affected:         | Z                    |                                                   |                      | Status Affecte | d: None                                   |                                              |                               |

| Encoding:                | 0000                 | 100d ff:                                          | ff ffff              | Encoding:      | 1011                                      | 0111 kk                                      | kk kkkk                       |

| Description:             | 'd' is 0 the r       | R WREG with<br>esult is placed<br>esult is placed | 0                    | Description:   | tine call to<br>gram mem<br>First, the re | anywhere with<br>ory space.<br>eturn address | · · ·                         |

| Words:                   | 1                    |                                                   |                      |                | •                                         | to the stack. A<br>ress is then lo           |                               |

| Cycles:                  | 1                    |                                                   |                      |                |                                           | ounter. The lo                               |                               |

| Q Cycle Activity:        |                      |                                                   |                      |                |                                           |                                              | s embedded in                 |

| Q1                       | Q2                   | Q3                                                | Q4                   |                |                                           | om PC high h                                 | er 8-bits of PC olding latch, |

| Decode                   | Read<br>register 'f' | Execute                                           | Write to destination |                | PCLATH.                                   | Ū                                            | 0                             |

|                          | 0                    |                                                   | uestination          | Words:         | 1                                         |                                              |                               |

| Example:                 |                      | ESULT, O                                          |                      | Cycles:        | 2                                         |                                              |                               |

| Before Instru<br>RESULT  |                      |                                                   |                      | Q Cycle Activi | ty:                                       |                                              |                               |

| WREG                     | = 0x13<br>= 0x91     |                                                   |                      | Q1             | Q2                                        | Q3                                           | Q4                            |

| After Instruct<br>RESULT |                      |                                                   |                      | Decode         | Read<br>literal 'k'                       | Execute                                      | Write<br>register PCL         |

| WREG                     | = 0x13<br>= 0x93     |                                                   |                      | Forced NC      | DP NOP                                    | Execute                                      | NOP                           |

|                          |                      |                                                   |                      | Example:       | MOVPF W                                   | IGH(SUBROU<br>REG, PCLAT<br>OW(SUBROUT       | Н                             |

**Before Instruction**

| SUBROUTINE        | = | 16-bit Address |

|-------------------|---|----------------|

| PC                | = | ?              |

| After Instruction |   |                |

| PC = Address (S | UBROUTINE) |

|-----------------|------------|

|-----------------|------------|

| Droduct                                                                                                                                               | ** MDI ADTM                             |                                   | MD-Drivo/Mov      |                              | *** DICMACTED®/                                                                                                                                                                                                                     |                                                                |                                                                                                                                                                             |                                                                                                                                                                                                                                  | DIC CTADT® DI         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|-------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|                                                                                                                                                       | Integrated                              | Compiler                          | Applications      | Explorer/Edition             | PICMASTER-CE                                                                                                                                                                                                                        | Low-Cost                                                       | II Universal                                                                                                                                                                | Ultra Low-Cost                                                                                                                                                                                                                   | Low-Cost              |

|                                                                                                                                                       | Development<br>Environment              |                                   | Code<br>Generator | Fuzzy Logic<br>Dev. Tool     | In-Circuit<br>Emulator                                                                                                                                                                                                              | In-Circuit<br>Emulator                                         | Microchip<br>Programmer                                                                                                                                                     | Dev. Kit                                                                                                                                                                                                                         | Universal<br>Dev. Kit |

| PIC12C508, 509                                                                                                                                        | SW007002                                | SW006005                          | 1                 | I                            | EM167015/<br>EM167101                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | 1                                                                                                                                                                                                                                | DV003001              |

| PIC14000                                                                                                                                              | SW007002                                | SW006005                          | I                 | I                            | EM147001/<br>EM147101                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | I                                                                                                                                                                                                                                | DV003001              |

| PIC16C52, 54, 54A,<br>55, 56, 57, 58A                                                                                                                 | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167015/<br>EM167101                                                                                                                                                                                                               | EM167201                                                       | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                         | DV003001              |

| PIC16C554, 556, 558                                                                                                                                   | SW007002                                | SW006005                          | 1                 | DV005001/<br>DV005002        | EM167033/<br>EM167113                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | I                                                                                                                                                                                                                                | DV003001              |