Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product StatusObsoleteCore ProcessorPICCore Size8-BitSpeed25MHzConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O33Program Memory Size4KB (2K × 16)Program Memory TypeOTPEEPROM Size.32 × 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters.Orger ing Temperature.40°C ~ 125°C (TA)Mounting Type44-LCC (J-Lead)Supplier Device Package.4-LCC (Sps)16.59)Purchase URLhttps://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-25e-l | Details                    |                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------|

| Core Size8-BitSpeed25MHzConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O33Program Memory Size4KB (2K x 16)Program Memory TypeOTPEEPROM Size-RAM Size232 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Operating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-LCC (16.59x16.59)                                                                                       | Product Status             | Obsolete                                                                  |

| Speed25MHzConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O33Program Memory Size4KB (2K x 16)Program Memory TypeOTPEEPROM Size-RAM Size232 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                             | Core Processor             | PIC                                                                       |

| ConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O33Program Memory Size4KB (2K x 16)Program Memory TypeOTPEEPROM Size-RAM Size232 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (1-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                       | Core Size                  | 8-Bit                                                                     |

| PeripheralsPOR, PWM, WDTNumber of I/O33Program Memory Size4KB (2K x 16)Program Memory TypeOTPEEPROM Size-RAM Size232 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                                             | Speed                      | 25MHz                                                                     |

| Number of I/O33Program Memory Size4KB (2K x 16)Program Memory TypeOTPEEPROM Size-RAM Size232 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-PLCC (16.59x16.59)                                                                                                                                                                           | Connectivity               | UART/USART                                                                |

| Program Memory Size4KB (2K x 16)Program Memory TypeOTPEEPROM Size-RAM Size232 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                                                                                    | Peripherals                | POR, PWM, WDT                                                             |

| Program Memory TypeOTPEEPROM Size-RAM Size232 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                                                                                                                    | Number of I/O              | 33                                                                        |

| EEPROM Size-RAM Size232 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                                                                                                                                          | Program Memory Size        | 4KB (2K x 16)                                                             |

| RAM Size232 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                                                                                                                                                      | Program Memory Type        | OTP                                                                       |

| Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                                                                                                                                                                     | EEPROM Size                |                                                                           |

| Data Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                                                                                                                                                                                                        | RAM Size                   | 232 x 8                                                                   |

| Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                                                                                                                                                                                                                        | Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Operating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                                                                                                                                                                                                                                               | Data Converters            | ·                                                                         |

| Mounting TypeSurface MountPackage / Case44-LCC (J-Lead)Supplier Device Package44-PLCC (16.59x16.59)                                                                                                                                                                                                                                                                                                                                                      | Oscillator Type            | External                                                                  |

| Package / Case     44-LCC (J-Lead)       Supplier Device Package     44-PLCC (16.59x16.59)                                                                                                                                                                                                                                                                                                                                                               | Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Supplier Device Package     44-PLCC (16.59x16.59)                                                                                                                                                                                                                                                                                                                                                                                                        | Mounting Type              | Surface Mount                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Package / Case             | 44-LCC (J-Lead)                                                           |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-25e-l                                                                                                                                                                                                                                                                                                                                                                   | Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-25e-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Overview                                                               | 5   |

|-------|------------------------------------------------------------------------|-----|

| 2.0   | PIC17C4X Device Varieties                                              | 7   |

| 3.0   | Architectural Overview                                                 | 9   |

| 4.0   | Reset                                                                  | 15  |

| 5.0   | Interrupts                                                             | 21  |

| 6.0   | Memory Organization                                                    | 29  |

| 7.0   | Table Reads and Table Writes                                           | 43  |

| 8.0   | Hardware Multiplier                                                    | 49  |

| 9.0   | I/O Ports                                                              | 53  |

| 10.0  | Overview of Timer Resources                                            |     |

| 11.0  | Timer0                                                                 |     |

| 12.0  | Timer1, Timer2, Timer3, PWMs and Captures                              |     |

| 13.0  | Universal Synchronous Asynchronous Receiver Transmitter (USART) Module | 83  |

| 14.0  | Special Features of the CPU                                            | 99  |

| 15.0  | Instruction Set Summary                                                | 107 |

| 16.0  | Development Support                                                    | 143 |

| 17.0  | PIC17C42 Electrical Characteristics                                    |     |

| 18.0  | PIC17C42 DC and AC Characteristics                                     |     |

| 19.0  | PIC17CR42/42A/43/R43/44 Electrical Characteristics                     | 175 |

| 20.0  | PIC17CR42/42A/43/R43/44 DC and AC Characteristics                      |     |

| 21.0  | Packaging Information                                                  | 205 |

|       | dix A: Modifications                                                   |     |

|       | dix B: Compatibility                                                   |     |

| Appen | dix C: What's New                                                      | 212 |

| Appen | dix D: What's Changed                                                  | 212 |

|       | dix E: PIC16/17 Microcontrollers                                       |     |

|       | dix F: Errata for PIC17C42 Silicon                                     |     |

|       |                                                                        |     |

| PIC17 | C4X Product Identification System                                      | 237 |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. For example, the legend below shows that some features of only the PIC17C43, PIC17C43, PIC17C44 are described in this section.

### Applicable Devices 42 R42 42A 43 R43 44

# To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error from the previous version of the PIC17C4X Data Sheet (Literature Number DS30412B), please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

To assist you in the use of this document, Appendix C contains a list of new information in this data sheet, while Appendix D contains information that has changed

NOTES:

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC17C4X can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC17C4X uses a modified Harvard architecture. This architecture has the program and data accessed from separate memories. So the device has a program memory bus and a data memory bus. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory (accesses over the same bus). Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. PIC17C4X opcodes are 16-bits wide, enabling single word instructions. The full 16-bit wide program memory bus fetches a 16-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions. Consequently, all instructions execute in a single cycle (121 ns @ 33 MHz), except for program branches and two special instructions that transfer data between program and data memory.

The PIC17C4X can address up to 64K x 16 of program memory space.

The **PIC17C42** and **PIC17C42A** integrate 2K x 16 of EPROM program memory on-chip, while the **PIC17CR42** has 2K x 16 of ROM program memory on-chip.

The **PIC17C43** integrates 4K x 16 of EPROM program memory, while the **PIC17CR43** has 4K x 16 of ROM program memory.

The **PIC17C44** integrates 8K x 16 EPROM program memory.

Program execution can be internal only (microcontroller or protected microcontroller mode), external only (microprocessor mode) or both (extended microcontroller mode). Extended microcontroller mode does not allow code protection.

The PIC17CXX can directly or indirectly address its register files or data memory. All special function registers, including the Program Counter (PC) and Working Register (WREG), are mapped in the data memory. The PIC17CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC17CXX simple yet efficient. In addition, the learning curve is reduced significantly.

One of the PIC17CXX family architectural enhancements from the PIC16CXX family allows two file registers to be used in some two operand instructions. This allows data to be moved directly between two registers without going through the WREG register. This increases performance and decreases program memory usage. The PIC17CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift, and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature.

The WREG register is an 8-bit working register used for ALU operations.

All PIC17C4X devices (except the PIC17C42) have an 8 x 8 hardware multiplier. This multiplier generates a 16-bit result in a single cycle.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

Although the ALU does not perform signed arithmetic, the Overflow bit (OV) can be used to implement signed math. Signed arithmetic is comprised of a magnitude and a sign bit. The overflow bit indicates if the magnitude overflows and causes the sign bit to change state. Signed math can have greater than 7-bit values (magnitude), if more than one byte is used. The use of the overflow bit only operates on bit6 (MSb of magnitude) and bit7 (sign bit) of the value in the ALU. That is, the overflow bit is not useful if trying to implement signed math where the magnitude, for example, is 11-bits. If the signed math values are greater than 7-bits (15-, 24or 31-bit), the algorithm must ensure that the low order bytes ignore the overflow status bit.

Care should be taken when adding and subtracting signed numbers to ensure that the correct operation is executed. Example 3-1 shows an item that must be taken into account when doing signed arithmetic on an ALU which operates as an unsigned machine.

## EXAMPLE 3-1: SIGNED MATH

| Hex Value    | Signed Value<br>Math | Unsigned Value<br>Math      |

|--------------|----------------------|-----------------------------|

| FFh          | -127                 | 255                         |

| <u>+ 01h</u> | <u>+ 1</u>           | <u>+ 1</u>                  |

| = ?          | = -126 (FEh)         | = 0 (00h);<br>Carry bit = 1 |

|              |                      | curry pro - r               |

Signed math requires the result in REG to be FEh (-126). This would be accomplished by subtracting one as opposed to adding one.

Simplified block diagrams are shown in Figure 3-1 and Figure 3-2. The descriptions of the device pins are listed in Table 3-1.

© 1996 Microchip Technology Inc.

## 5.9 Context Saving During Interrupts

During an interrupt, only the returned PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt; e.g. WREG, ALUSTA and the BSR registers. This requires implementation in software. Example 5-1 shows the saving and restoring of information for an interrupt service routine. The PUSH and POP routines could either be in each interrupt service routine or could be subroutines that were called. Depending on the application, other registers may also need to be saved, such as PCLATH.

## EXAMPLE 5-1: SAVING STATUS AND WREG IN RAM

| ; must<br>; 8 loc<br>; the M<br>; bits,<br>; | be in th<br>ations c<br>NOVFP ins | e data memory address<br>an be saved and resto       | ction neither affects the status        |  |

|----------------------------------------------|-----------------------------------|------------------------------------------------------|-----------------------------------------|--|

| ;<br>PUSH                                    | MOVFP<br>MOVFP<br>MOVFP           | ,                                                    | ; Save ALUSTA                           |  |

| ISR                                          | :                                 |                                                      | ; This is the interrupt service routine |  |

| POP                                          | MOVFP<br>MOVFP<br>MOVFP<br>RETFIE | TEMP_W, WREG<br>TEMP_STATUS, ALUSTA<br>TEMP_BSR, BSR |                                         |  |

NOTES:

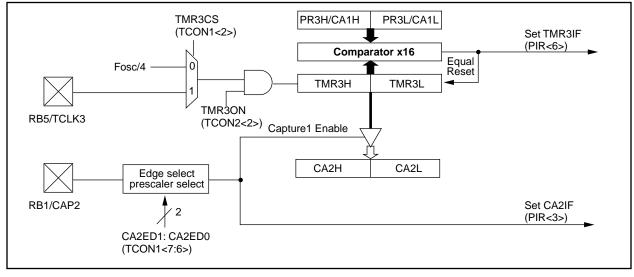

### 12.2.1 ONE CAPTURE AND ONE PERIOD REGISTER MODE

In this mode registers PR3H/CA1H and PR3L/CA1L constitute a 16-bit period register. A block diagram is shown in Figure 12-7. The timer increments until it equals the period register and then resets to 0000h. TMR3 Interrupt Flag bit (TMR3IF) is set at this point. This interrupt can be disabled by clearing the TMR3 Interrupt Enable bit (TMR3IE). TMR3IF must be cleared in software.

This mode is selected if control bit CA1/PR3 is clear. In this mode, the Capture1 register, consisting of high byte (PR3H/CA1H) and low byte (PR3L/CA1L), is configured as the period control register for TMR3. Capture1 is disabled in this mode, and the corresponding Interrupt bit CA1IF is never set. TMR3 increments until it equals the value in the period register and then resets to 0000h.

Capture2 is active in this mode. The CA2ED1 and CA2ED0 bits determine the event on which capture will occur. The possible events are:

- · Capture on every falling edge

- Capture on every rising edge

- · Capture every 4th rising edge

- · Capture every 16th rising edge

When a capture takes place, an interrupt flag is latched into the CA2IF bit. This interrupt can be enabled by setting the corresponding mask bit CA2IE. The Peripheral Interrupt Enable bit (PEIE) must be set and the Global Interrupt Disable bit (GLINTD) must be cleared for the interrupt to be acknowledged. The CA2IF interrupt flag bit must be cleared in software.

When the capture prescale select is changed, the prescaler is not reset and an event may be generated. Therefore, the first capture after such a change will be ambiguous. However, it sets the time-base for the next capture. The prescaler is reset upon chip reset. Capture pin RB1/CAP2 is a multiplexed pin. When used as a port pin, Capture2 is not disabled. However, the user can simply disable the Capture2 interrupt by clearing CA2IE. If RB1/CAP2 is used as an output pin, the user can activate a capture by writing to the port pin. This may be useful during development phase to emulate a capture interrupt.

The input on capture pin RB1/CAP2 is synchronized internally to internal phase clocks. This imposes certain restrictions on the input waveform (see the Electrical Specification section for timing).

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the Timer3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The recommended sequence to read capture registers and capture overflow flag bits is shown in Example 12-1.

## EXAMPLE 12-1: SEQUENCE TO READ CAPTURE REGISTERS

| MOVLB 3              | ;Select Bank 3          |

|----------------------|-------------------------|

| MOVPF CA2L,LO_BYTE   | ;Read Capture2 low      |

|                      | ;byte, store in LO_BYTE |

| MOVPF CA2H, HI_BYTE  | ;Read Capture2 high     |

|                      | ;byte, store in HI_BYTE |

| MOVPF TCON2,STAT_VAL | ;Read TCON2 into file   |

|                      | ;STAT_VAL               |

### FIGURE 12-7: TIMER3 WITH ONE CAPTURE AND ONE PERIOD REGISTER BLOCK DIAGRAM

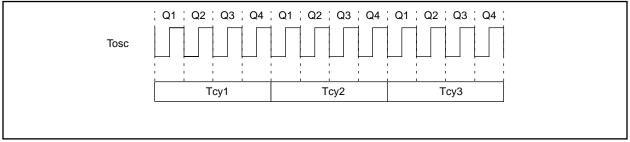

## 15.2 <u>Q Cycle Activity</u>

Each instruction cycle (Tcy) is comprised of four Q cycles (Q1-Q4). The Q cycles provide the timing/designation for the Decode, Read, Execute, Write etc., of each instruction cycle. The following diagram shows the relationship of the Q cycles to the instruction cycle.

The 4 Q cycles that make up an instruction cycle (Tcy) can be generalized as:

- Q1: Instruction Decode Cycle or forced NOP

- Q2: Instruction Read Cycle or NOP

- Q3: Instruction Execute

- Q4: Instruction Write Cycle or NOP

Each instruction will show the detailed Q cycle operation for the instruction.

# FIGURE 15-2: Q CYCLE ACTIVITY

| ADD         | WFC                                                                                     | ADD WRE                                                                                                                                                           | G and C     | Carry bit            | to f                     |

|-------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|--------------------------|

| Synt        | ax:                                                                                     | [ <i>label</i> ] A[                                                                                                                                               | DWFC        | f,d                  |                          |

| Ope         | rands:                                                                                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]                                                                                                                                          | 5           |                      |                          |

| Ope         | ration:                                                                                 | (WREG) +                                                                                                                                                          | - (f) + C - | $\rightarrow$ (dest) |                          |

| Statu       | us Affected:                                                                            | OV, C, DC                                                                                                                                                         | , Z         |                      |                          |

| Enco        | oding:                                                                                  | 0001                                                                                                                                                              | 000d        | ffff                 | ffff                     |

| Desc        | cription:                                                                               | Add WREG, the Carry Flag and data<br>memory location 'f'. If 'd' is 0, the resu<br>placed in WREG. If 'd' is 1, the result<br>placed in data memory location 'f'. |             |                      | e result is<br>result is |

| Word        | ds:                                                                                     | 1                                                                                                                                                                 |             |                      |                          |

| Cycl        | es:                                                                                     | 1                                                                                                                                                                 |             |                      |                          |

| QC          | cle Activity:                                                                           |                                                                                                                                                                   |             |                      |                          |

|             | Q1                                                                                      | Q2                                                                                                                                                                | Q3          |                      | Q4                       |

|             | Decode                                                                                  | Read<br>register 'f'                                                                                                                                              | Execut      |                      | rite to<br>tination      |

| <u>Exar</u> | <u>mple</u> :                                                                           | ADDWFC                                                                                                                                                            | REG         | 0                    |                          |

|             | Before Instru<br>Carry bit<br>REG<br>WREG<br>After Instruct<br>Carry bit<br>REG<br>WREG | = 1<br>= 0x02<br>= 0x4D                                                                                                                                           |             |                      |                          |

| ANDLW                 | And Lite                                                                                        | ral with WRI           | EG               |  |

|-----------------------|-------------------------------------------------------------------------------------------------|------------------------|------------------|--|

| Syntax:               | [label] A                                                                                       | ANDLW k                |                  |  |

| Operands:             | $0 \le k \le 25$                                                                                | 55                     |                  |  |

| Operation:            | (WREG)                                                                                          | .AND. (k) $ ightarrow$ | (WREG)           |  |

| Status Affected:      | Z                                                                                               |                        |                  |  |

| Encoding:             | 1011                                                                                            | 0101 kk                | kk kkkk          |  |

| Description:          | The contents of WREG are AND'ed with<br>the 8-bit literal 'k'. The result is placed in<br>WREG. |                        |                  |  |

| Words:                | 1                                                                                               |                        |                  |  |

| Cycles:               | 1                                                                                               |                        |                  |  |

| Q Cycle Activity:     |                                                                                                 |                        |                  |  |

| Q1                    | Q2                                                                                              | Q3                     | Q4               |  |

| Decode                | Read literal<br>'k'                                                                             | Execute                | Write to<br>WREG |  |

| Example:              | ANDLW                                                                                           | 0x5F                   |                  |  |

| Before Instru<br>WREG | uction<br>= 0xA3                                                                                |                        |                  |  |

| After Instruc<br>WREG | tion<br>= 0x03                                                                                  |                        |                  |  |

| ANDWF                                                  | AND WRE                         | EG with                                                                                                                                             | f                    |                       |  |  |

|--------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|--|--|

| Syntax:                                                | [ <i>label</i> ] A              | NDWF                                                                                                                                                | f,d                  |                       |  |  |

| Operands:                                              | $0 \le f \le 255$ $d \in [0,1]$ | 5                                                                                                                                                   |                      |                       |  |  |

| Operation:                                             | (WREG) .                        | AND. (f)                                                                                                                                            | $\rightarrow$ (dest) | )                     |  |  |

| Status Affected:                                       | Z                               |                                                                                                                                                     |                      |                       |  |  |

| Encoding:                                              | 0000                            | 101d                                                                                                                                                | ffff                 | ffff                  |  |  |

| Description:                                           | register 'f'.<br>in WREG. I     | The contents of WREG are AND'ed with register 'f'. If 'd' is 0 the result is stored in WREG. If 'd' is 1 the result is stored back in register 'f'. |                      |                       |  |  |

| Words:                                                 | 1                               |                                                                                                                                                     |                      |                       |  |  |

| Cycles:                                                | 1                               |                                                                                                                                                     |                      |                       |  |  |

| Q Cycle Activity:                                      |                                 |                                                                                                                                                     |                      |                       |  |  |

| Q1                                                     | Q2                              | Q3                                                                                                                                                  | 3                    | Q4                    |  |  |

| Decode                                                 | Read<br>register 'f'            | Execu                                                                                                                                               |                      | Vrite to<br>stination |  |  |

| Example:                                               | ANDWF                           | REG, 1                                                                                                                                              |                      |                       |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG | = 0x17<br>= 0xC2                |                                                                                                                                                     |                      |                       |  |  |

| BCF                                                                           |           | Bit Clear                        | f             |       |     |                     |

|-------------------------------------------------------------------------------|-----------|----------------------------------|---------------|-------|-----|---------------------|

| Syntax:                                                                       |           | [label] E                        | BCF f,I       | С     |     |                     |

| Operand                                                                       | s:        | $0 \le f \le 25$ $0 \le b \le 7$ | 5             |       |     |                     |

| Operatio                                                                      | n:        | $0 \rightarrow (f < b >$         | -)            |       |     |                     |

| Status A                                                                      | ffected:  | None                             |               |       |     |                     |

| Encoding                                                                      | g:        | 1000                             | 1bbb          | fff   | f   | ffff                |

| Descripti                                                                     | ion:      | Bit 'b' in re                    | gister 'f' is | clear | ed. |                     |

| Words:                                                                        |           | 1                                |               |       |     |                     |

| Cycles:                                                                       |           | 1                                |               |       |     |                     |

| Q Cycle                                                                       | Activity: |                                  |               |       |     |                     |

|                                                                               | Q1        | Q2                               | Q3            | 8     |     | Q4                  |

| D                                                                             | ecode     | Read<br>register 'f'             | Execu         | ute   |     | Write<br>gister 'f' |

| <u>Example</u>                                                                | :         | BCF                              | FLAG_R        | EG,   | 7   |                     |

| Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction<br>FLAG_REG = 0x47 |           |                                  |               |       |     |                     |

|                                                                               |           | 20 - 0,47                        |               |       |     |                     |

| INFSNZ                                               | NFSNZ Increment f, skip if not 0                                                      |                                                                                                                                                                                                                                                                                                                               |            |                       |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|--|--|

| Syntax:                                              | [ <i>label</i> ] II                                                                   | NFSNZ                                                                                                                                                                                                                                                                                                                         | f,d        |                       |  |  |

| Operands:                                            | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                                               | 5                                                                                                                                                                                                                                                                                                                             |            |                       |  |  |

| Operation:                                           | (f) + 1 $\rightarrow$                                                                 | (dest), s                                                                                                                                                                                                                                                                                                                     | kip if not | 0                     |  |  |

| Status Affected:                                     | None                                                                                  |                                                                                                                                                                                                                                                                                                                               |            |                       |  |  |

| Encoding:                                            | 0010                                                                                  | 010d                                                                                                                                                                                                                                                                                                                          | ffff       | ffff                  |  |  |

| Description:                                         | mented. If<br>WREG. If '<br>back in reg<br>If the result<br>which is all<br>and an NO | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'.<br>If the result is not 0, the next instruction,<br>which is already fetched, is discarded,<br>and an NOP is executed instead making<br>it a two-cycle instruction. |            |                       |  |  |

| Words:                                               | 1                                                                                     |                                                                                                                                                                                                                                                                                                                               |            |                       |  |  |

| Cycles:                                              | 1(2)                                                                                  |                                                                                                                                                                                                                                                                                                                               |            |                       |  |  |

| Q Cycle Activity:                                    |                                                                                       |                                                                                                                                                                                                                                                                                                                               |            |                       |  |  |

| Q1                                                   | Q2                                                                                    | Q                                                                                                                                                                                                                                                                                                                             | 3          | Q4                    |  |  |

| Decode                                               | Read<br>register 'f'                                                                  | Exect                                                                                                                                                                                                                                                                                                                         |            | Vrite to<br>stination |  |  |

| lf skip:                                             |                                                                                       |                                                                                                                                                                                                                                                                                                                               |            |                       |  |  |

| Q1                                                   | Q2                                                                                    | Q                                                                                                                                                                                                                                                                                                                             | 3          | Q4                    |  |  |

| Forced NOP                                           | NOP                                                                                   | Exect                                                                                                                                                                                                                                                                                                                         | ute        | NOP                   |  |  |

| Example: HERE INFSNZ REG, 1<br>ZERO<br>NZERO         |                                                                                       |                                                                                                                                                                                                                                                                                                                               |            |                       |  |  |

| Before Instru<br>REG                                 | uction<br>= REG                                                                       |                                                                                                                                                                                                                                                                                                                               |            |                       |  |  |

| After Instruc<br>REG<br>If REG<br>PC<br>If REG<br>PC | = REG +<br>= 1;<br>= Addres<br>= 0;                                                   | 1<br>s (zero<br>s (nzero                                                                                                                                                                                                                                                                                                      |            |                       |  |  |

| Current      |                        | [ lahal]                                |               |                   |                  |

|--------------|------------------------|-----------------------------------------|---------------|-------------------|------------------|

| Synt         | ax:                    | [ label ]                               | IORLW         | К                 |                  |

| Ope          | rands:                 | $0 \le k \le 25$                        | 55            |                   |                  |

| Ope          | ration:                | (WREG)                                  | .OR. (k)      | $\rightarrow$ (WR | EG)              |

| State        | us Affected:           | Z                                       |               |                   |                  |

| Enco         | oding:                 | 1011                                    | 0011          | kkkk              | kkkk             |

| Description: |                        | The conte<br>the eight b<br>placed in \ | it literal 'k |                   |                  |

| Wor          | ds:                    | 1                                       |               |                   |                  |

| Cycl         | es:                    | 1                                       |               |                   |                  |

| QC           | ycle Activity:         |                                         |               |                   |                  |

|              | Q1                     | Q2                                      | Q             | 3                 | Q4               |

|              | Decode                 | Read<br>literal 'k'                     | Exect         | ute               | Write to<br>WREG |

| <u>Exa</u>   | <u>mple</u> :          | IORLW                                   | 0x35          |                   |                  |

|              | Before Instru<br>WREG  | iction<br>= 0x9A                        |               |                   |                  |

|              | After Instruct<br>WREG | tion<br>= 0xBF                          |               |                   |                  |

Applicable Devices 42 R42 42A 43 R43 44

# TABLE 17-1:CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS<br/>AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| OSC | PIC17C42-16                              | PIC17C42-25                              |

|-----|------------------------------------------|------------------------------------------|

| RC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 6 mA max.                           | IDD: 6 mA max.                           |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 4 MHz max.                         | Freq: 4 MHz max.                         |

| XT  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| EC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| LF  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 150 μA max. at 32 kHz (WDT enabled) | IDD: 150 μA max. at 32 kHz (WDT enabled) |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 2 MHz max.                         | Freq: 2 MHz max.                         |

## Applicable Devices 42 R42 42A 43 R43 44

#### 17.2 DC CHARACTERISTICS:

### PIC17C42-16 (Commercial, Industrial) PIC17C42-25 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated) Operating temperature

### DC CHARACTERISTICS

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and  $0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

Operating voltage VDD range as described in Section 17.1 Parameter No. Sym Characteristic Min Typ† Max Units Conditions Input Low Voltage VIL I/O ports D030 with TTL buffer Vss 0.8 V D031 with Schmitt Trigger buffer Vss 0.2VDD V \_ D032 MCLR, OSC1 (in EC and RC Vss 0.2Vdd V Note1 \_ mode) D033 OSC1 (in XT, and LF mode) 0.5VDD V \_ Input High Voltage Vн I/O ports V D040 2.0 with TTL buffer \_ Vdd D041 with Schmitt Trigger buffer 0.8VDD Vdd V \_ D042 MCLR 0.8Vdd Vdd Note1 V D043 OSC1 (XT, and LF mode) 0.5VDD V D050 Hysteresis of 0.15VDD\* VHYS V \_ \_ Schmitt Trigger inputs Input Leakage Current (Notes 2, 3) D060 lı∟ I/O ports (except RA2, RA3)  $Vss \leq VPIN \leq VDD$ , ±1 μΑ I/O Pin at hi-impedance PORTB weak pull-ups disabled MCLR D061 <u>+2</u> μA VPIN = Vss or VPIN = VDD D062 **RA2, RA3** ±2 μΑ  $Vss \leq VRA2$ ,  $VRA3 \leq 12V$ D063 OSC1, TEST ±1 μΑ  $Vss \le VPIN \le VDD$

D070 IPURB PORTB weak pull-up current 60 These parameters are characterized but not tested.

MCLR

D064

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only t and are not tested.

200

10

400

μA

μΑ

These parameters are for design guidance only and are not tested, nor characterized. t

Design guidance to attain the AC timing specifications. These loads are not tested. ++

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/Vpp pin may be kept in this range at times other than programming, but this is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

VMCLR = VPP = 12V

(when not programming)

VPIN = Vss.  $\overline{RBPU} = 0$

# Applicable Devices 42 R42 42A 43 R43 44

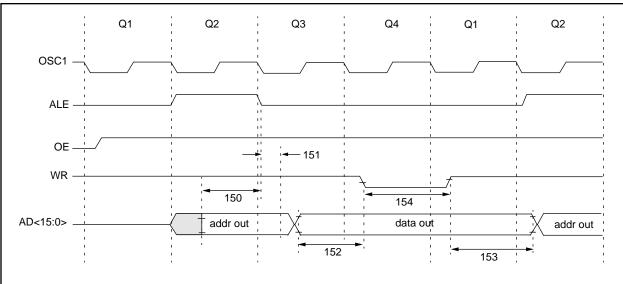

## FIGURE 17-11: MEMORY INTERFACE WRITE TIMING

## TABLE 17-11: MEMORY INTERFACE WRITE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                | Min          | Тур†      | Max | Units | Conditions |

|------------------|----------|---------------------------------------------------------------|--------------|-----------|-----|-------|------------|

| 150              | TadV2alL | AD<15:0> (address) valid to ALE↓<br>(address setup time)      | 0.25Tcy - 30 |           |     | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)               | 0            | _         | _   | ns    |            |

| 152              | TadV2wrL | Data out valid to $\overline{WR}\downarrow$ (data setup time) | 0.25Tcy - 40 | —         | —   | ns    |            |

| 153              | TwrH2adI | WR↑ to data out invalid<br>(data hold time)                   | _            | 0.25Tcy § | —   | ns    |            |

| 154              | TwrL     | WR pulse width                                                | —            | 0.25Tcy § | _   | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification is guaranteed by design.

# Applicable Devices 42 R42 42A 43 R43 44

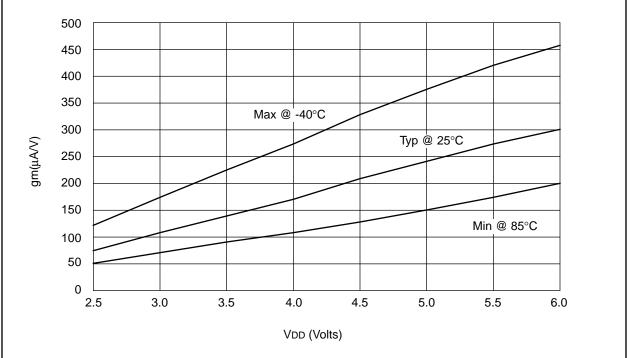

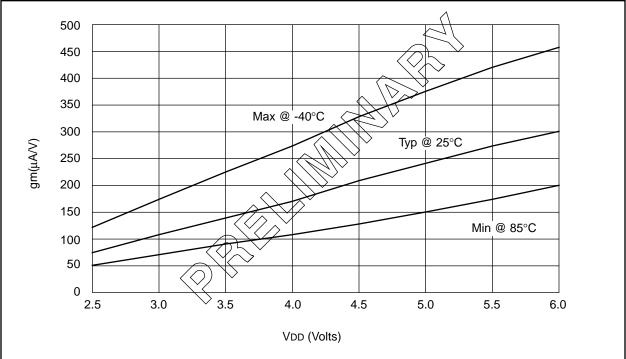

FIGURE 18-6: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

NOTES:

# Applicable Devices 42 R42 42A 43 R43 44

# 19.5 <u>Timing Diagrams and Specifications</u>

## FIGURE 19-2: EXTERNAL CLOCK TIMING

## TABLE 19-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                     | Min   | Тур†   | Max   | Units | Conditions                               |

|--------------|-------|------------------------------------|-------|--------|-------|-------|------------------------------------------|

|              | Fosc  | External CLKIN Frequency           | DC    | _      | 8     | MHz   | EC osc mode - 08 devices (8 MHz devices) |

|              |       | (Note 1)                           | DC    | _      | 16    | MHz   | - 16 devices (16 MHz devices)            |

|              |       | (                                  | DC    | _      | 25    | MHz   | - 25 devices (25 MHz devices)            |

|              |       |                                    | DC    | —      | 33    | MHz   | - 33 devices (33 MHz devices)            |

|              |       | Oscillator Frequency               | DC    | _      | 4     | MHz   | RC osc mode                              |

|              |       | (Note 1)                           | 1     | _      | 8     | MHz   | XT osc mode - 08 devices (8 MHz devices) |

|              |       |                                    | 1     | _      | 16    | MHz   | - 16 devices (16 MHz devices)            |

|              |       |                                    | 1     | _      | 25    | MHz   | - 25 devices (25 MHz devices)            |

|              |       |                                    | 1     | _      | 33    | MHz   | - 33 devices (33 MHz devices)            |

|              |       |                                    | DC    | —      | 2     | MHz   | LF osc mode                              |

| 1            | Tosc  | External CLKIN Period              | 125   | _      | —     | ns    | EC osc mode - 08 devices (8 MHz devices) |

|              |       | (Note 1)                           | 62.5  | _      | —     | ns    | - 16 devices (16 MHz devices)            |

|              |       |                                    | 40    | _      | —     | ns    | - 25 devices (25 MHz devices)            |

|              |       |                                    | 30.3  | —      | —     | ns    | - 33 devices (33 MHz devices)            |

|              |       | Oscillator Period                  | 250   | _      | —     | ns    | RC osc mode                              |

|              |       | (Note 1)                           | 125   | _      | 1,000 | ns    | XT osc mode - 08 devices (8 MHz devices) |

|              |       |                                    | 62.5  | _      | 1,000 | ns    | - 16 devices (16 MHz devices)            |

|              |       |                                    | 40    | —      | 1,000 | ns    | - 25 devices (25 MHz devices)            |

|              |       |                                    | 30.3  | —      | 1,000 | ns    | - 33 devices (33 MHz devices)            |

|              |       |                                    | 500   | —      | —     | ns    | LF osc mode                              |

| 2            | Тсү   | Instruction Cycle Time<br>(Note 1) | 121.2 | 4/Fosc | DC    | ns    |                                          |

| 3            | TosL, | Clock in (OSC1)                    | 10 ‡  | _      | _     | ns    | EC oscillator                            |

|              | TosH  | high or low time                   |       |        |       |       |                                          |

| 4            | TosR, | Clock in (OSC1)                    |       |        | 5‡    | ns    | EC oscillator                            |

|              | TosF  | rise or fall time                  |       |        |       |       |                                          |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

# Applicable Devices 42 R42 42A 43 R43 44

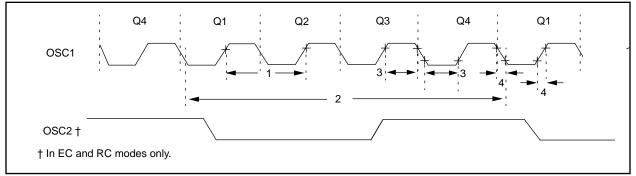

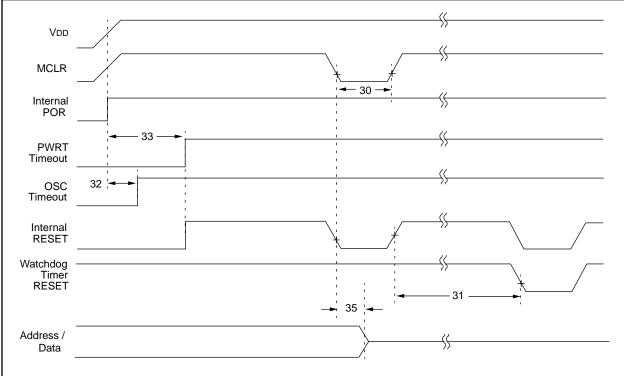

# TABLE 19-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                |                              | Min   | Тур†      | Max   | Units | Conditions         |

|------------------|----------|-----------------------------------------------|------------------------------|-------|-----------|-------|-------|--------------------|

| 30               | TmcL     | MCLR Pulse Width (low)                        |                              | 100 * | _         | _     | ns    | VDD = 5V           |

| 31               | Twdt     | Watchdog Timer Time-ou<br>(Prescale = 1)      | t Period                     | 5 *   | 12        | 25 *  | ms    | VDD = 5V           |

| 32               | Tost     | Oscillation Start-up Time                     | r Period                     | _     | 1024Tosc§ | _     | ms    | Tosc = OSC1 period |

| 33               | Tpwrt    | Power-up Timer Period                         |                              | 40 *  | 96        | 200 * | ms    | VDD = 5V           |

| 35               | TmcL2adl | MCLR to System Inter-<br>face bus (AD15:AD0>) | PIC17CR42/42A/<br>43/R43/44  | —     | _         | 100 * | ns    |                    |

|                  |          | invalid                                       | PIC17LCR42/<br>42A/43/R43/44 | —     | —         | 120 * | ns    |                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

§ This specification ensured by design.

# Applicable Devices 42 R42 42A 43 R43 44

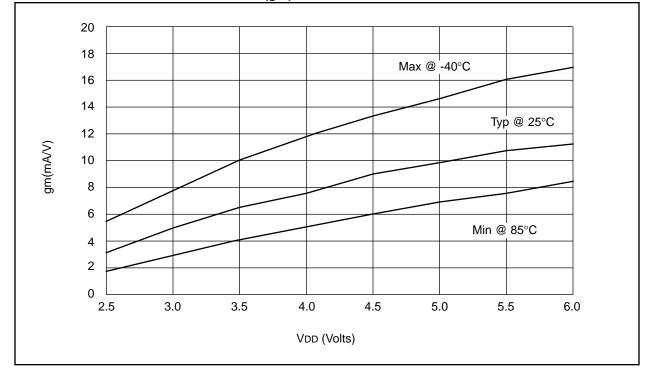

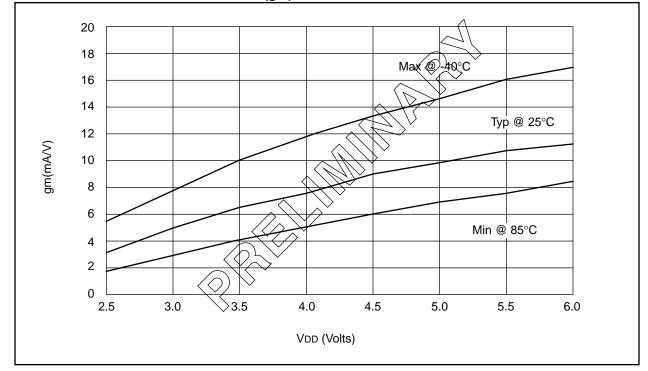

FIGURE 20-6: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

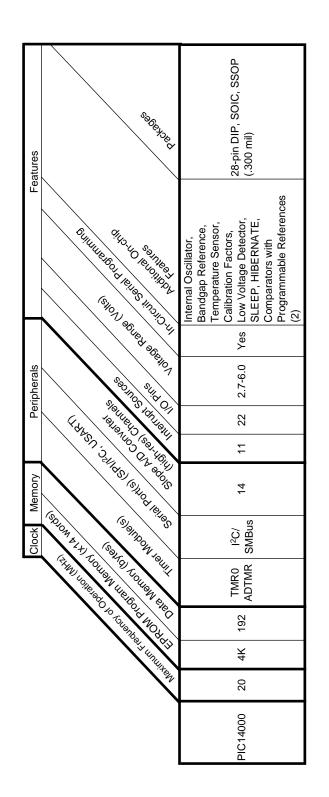

# **APPENDIX E: PIC16/17 MICROCONTROLLERS**

# E.1 PIC14000 Devices

© 1996 Microchip Technology Inc.

# E.2 PIC16C5X Family of Devices

|              |      |                 |           | 0           | Clock Mer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Memory  | Perip         | Peripherals | Features                                                                                                                |

|--------------|------|-----------------|-----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|-------------|-------------------------------------------------------------------------------------------------------------------------|

|              |      |                 |           | CAN USE     | Course will a course of the co |         |               |             |                                                                                                                         |

|              |      | 1081            | to TOUSDI |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (s)     |               | ., N SOL    | 454                                                                                                                     |

|              | Tely | UINUIN CONTRACT | MOL VY    | - MAA<br>MO | BOW SOUND SUNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         | SUID OI       | o sequent   | Sebersed                                                                                                                |