Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 232 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-25e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

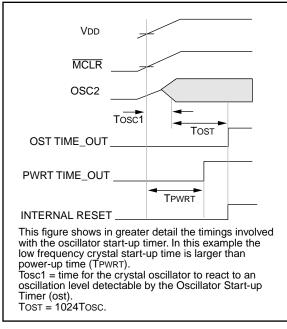

# FIGURE 4-5: OSCILLATOR START-UPTIME

# FIGURE 4-6: USING ON-CHIP POR

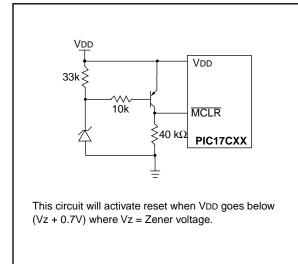

### FIGURE 4-7: BROWN-OUT PROTECTION CIRCUIT 1

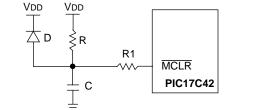

# FIGURE 4-8: PIC17C42 EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: An external Power-on Reset circuit is required only if VDD power-up time is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R < 40 k $\Omega$  is recommended to ensure that the voltage drop across R does not exceed 0.2V (max. leakage current spec. on the  $\overline{MCLR}/VPP$  pin is 5  $\mu$ A). A larger voltage drop will degrade VIH level on the  $\overline{MCLR}/VPP$  pin.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or (Electrical Overstress) EOS.

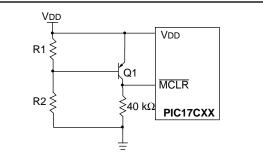

FIGURE 4-9: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

| TABLE 6-3: | SPECIAL FUNCTION REGISTERS |

|------------|----------------------------|

|------------|----------------------------|

| Address            | Name          | Bit 7        | Bit 6          | Bit 5         | Bit 4        | Bit 3        | Bit 2           | Bit 1          | Bit 0           | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|---------------|--------------|----------------|---------------|--------------|--------------|-----------------|----------------|-----------------|-------------------------------|-------------------------------------|

| Unbank             | ed            | •            |                |               |              | •            |                 |                | •               |                               |                                     |

| 00h                | INDF0         | Uses con     | tents of FSI   | R0 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 01h                | FSR0          | Indirect d   | ata memory     | address po    | inter 0      |              |                 |                |                 | XXXX XXXX                     | uuuu uuuu                           |

| 02h                | PCL           | Low orde     | r 8-bits of P  | С             |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | PCLATH        | Holding re   | egister for u  | pper 8-bits o | of PC        |              |                 |                |                 | 0000 0000                     | uuuu uuuu                           |

| 04h                | ALUSTA        | FS3          | FS2            | FS1           | FS0          | OV           | Z               | DC             | С               | 1111 xxxx                     | 1111 uuuu                           |

| 05h                | TOSTA         | INTEDG       | TOSE           | TOCS          | PS3          | PS2          | PS1             | PS0            | —               | 0000 000-                     | 0000 000-                           |

| 06h <b>(2)</b>     | CPUSTA        | _            | _              | STKAV         | GLINTD       | TO           | PD              | _              | _               | 11 11                         | 11 qq                               |

| 07h                | INTSTA        | PEIF         | TOCKIF         | T0IF          | INTF         | PEIE         | TOCKIE          | TOIE           | INTE            | 0000 0000                     | 0000 0000                           |

| 08h                | INDF1         | Uses con     | tents of FSI   | R1 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 09h                | FSR1          | Indirect d   | ata memory     | address po    | inter 1      |              | , ,             |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ah                | WREG          | Working r    | egister        |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Bh                | TMR0L         | TMR0 reg     | gister; low b  | yte           |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ch                | TMR0H         | TMR0 reg     | gister; high I | oyte          |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Dh                | TBLPTRL       | Low byte     | of program     | memory tab    | le pointer   |              |                 |                |                 | (4)                           | (4)                                 |

| 0Eh                | TBLPTRH       | High byte    | of program     | memory tal    | ole pointer  |              |                 |                |                 | (4)                           | (4)                                 |

| 0Fh                | BSR           | Bank sele    | ect register   |               |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| Bank 0             |               | 1            |                |               |              |              |                 |                |                 | I                             |                                     |

| 10h                | PORTA         | RBPU         | _              | RA5           | RA4          | RA3          | RA2             | RA1/T0CKI      | RA0/INT         | 0-xx xxxx                     | 0-uu uuuu                           |

| 11h                | DDRB          | Data dire    | ction registe  | er for PORTE  | 3            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 12h                | PORTB         | PORTB d      | ata latch      |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | RCSTA         | SPEN         | RX9            | SREN          | CREN         | —            | FERR            | OERR           | RX9D            | 0000 -00x                     | 0000 -00u                           |

| 14h                | RCREG         | Serial por   | t receive re   | gister        |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | TXSTA         | CSRC         | TX9            | TXEN          | SYNC         | —            | —               | TRMT           | TX9D            | 00001x                        | 00001u                              |

| 16h                | TXREG         | Serial por   | t transmit re  | egister       |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | SPBRG         | Baud rate    | generator      | register      |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| Bank 1             |               |              |                |               |              |              |                 |                |                 |                               |                                     |

| 10h                | DDRC          | Data dire    | ction registe  | er for PORT   | 2            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 11h                | PORTC         | RC7/<br>AD7  | RC6/<br>AD6    | RC5/<br>AD5   | RC4/<br>AD4  | RC3/<br>AD3  | RC2/<br>AD2     | RC1/<br>AD1    | RC0/<br>AD0     | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | DDRD          | Data dire    | ction registe  | er for PORTI  | )            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 4.01-              | PORTD         | RD7/<br>AD15 | RD6/<br>AD14   | RD5/<br>AD13  | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10    | RD1/<br>AD9    | RD0/<br>AD8     | xxxx xxxx                     | uuuu uuuu                           |

| 13h                |               | Data dira    | ction reaiste  | er for PORTE  | -            |              |                 | 1              |                 | 111                           | 111                                 |

| 13h<br>14h         | DDRE          | Data dire    |                |               |              |              |                 | -              |                 |                               |                                     |

|                    | DDRE<br>PORTE | Data dire    | _              | _             | _            | _            | RE2/WR          | RE1/OE         | RE0/ALE         | xxx                           | uuu                                 |

| 14h                |               | RBIF         | —<br>TMR3IF    | —<br>TMR2IF   | —<br>TMR1IF  | —<br>CA2IF   | RE2/WR<br>CA1IF | RE1/OE<br>TXIF | RE0/ALE<br>RCIF | xxx<br>0000 0010              | uuu<br>0000 0010                    |

x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated Legend: Note 1:

from or transferred to the upper byte of the program counter. The TO and PD status bits in CPUSTA are not affected by a MCLR reset. 2:

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

4:

The following values are for both TBLPTRL and TBLPTRH: All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000) except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu)

5: The PRODL and PRODH registers are not implemented on the PIC17C42.

#### 6.2.2.3 TMR0 STATUS/CONTROL REGISTER (T0STA)

This register contains various control bits. Bit7 (INTEDG) is used to control the edge upon which a signal on the RA0/INT pin will set the RB0/INT interrupt flag. The other bits configure the Timer0 prescaler and clock source. (Figure 11-1).

# FIGURE 6-9: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

| R/W - 0        | R/W - 0                                                            | R/W - 0                                          | R/W - 0                                                            | R/W - 0                    | R/W - 0                  | R/W - 0     | U - 0 |                                                                                                       |

|----------------|--------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------|----------------------------|--------------------------|-------------|-------|-------------------------------------------------------------------------------------------------------|

| INTEDG<br>bit7 | TOSE                                                               | TOCS                                             | PS3                                                                | PS2                        | PS1                      | PS0         | bit0  | R = Readable bit<br>W = Writable bit<br>U = Unimplemented,<br>reads as '0'<br>-n = Value at POR reset |

| bit 7:         | INTEDG: R<br>This bit sele<br>1 = Rising e<br>0 = Falling e        | ects the ed<br>edge of RA                        | ge upon w<br>0/INT pin g                                           | hich the in<br>generates i | terrupt is d<br>nterrupt | etected.    |       |                                                                                                       |

| bit 6:         |                                                                    | ects the ed<br>S = 0<br>edge of RA<br>edge of RA | ge upon w<br>1/T0CKI pi                                            | hich TMRC                  | nts TMR0 a               | and/or gene |       | CKIF interrupt<br>CKIF interrupt                                                                      |

| bit 5:         | <b>TOCS</b> : Time<br>This bit sele<br>1 = Internal<br>0 = TOCKI   | ects the clo<br>instruction                      | ock source                                                         | for Timer0                 |                          |             |       |                                                                                                       |

| bit 4-1:       | PS3:PS0: 7<br>These bits                                           |                                                  |                                                                    |                            | ner0.                    |             |       |                                                                                                       |

|                | PS3:PS0                                                            | Pre                                              | scale Valu                                                         | е                          |                          |             |       |                                                                                                       |

|                | 0000<br>001<br>0010<br>010<br>0100<br>0101<br>0110<br>0111<br>1xxx |                                                  | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 |                            |                          |             |       |                                                                                                       |

| bit 0:         | Unimplem                                                           | <b>ented</b> : Rea                               | id as '0'                                                          |                            |                          |             |       |                                                                                                       |

### 12.1.3.1 PWM PERIODS

The period of the PWM1 output is determined by Timer1 and its period register (PR1). The period of the PWM2 output can be software configured to use either Timer1 or Timer2 as the time-base. When TM2PW2 bit (PW2DCL<5>) is clear, the time-base is determined by TMR1 and PR1. When TM2PW2 is set, the time-base is determined by Timer2 and PR2.

Running two different PWM outputs on two different timers allows different PWM periods. Running both PWMs from Timer1 allows the best use of resources by freeing Timer2 to operate as an 8-bit timer. Timer1 and Timer2 can not be used as a 16-bit timer if either PWM is being used.

The PWM periods can be calculated as follows:

period of PWM1 =[(PR1) + 1] x 4Tosc

period of PWM2 =[(PR1) + 1] x 4Tosc or [(PR2) + 1] x 4Tosc

The duty cycle of PWMx is determined by the 10-bit value DCx<9:0>. The upper 8-bits are from register PWxDCH and the lower 2-bits are from PWxDCL<7:6> (PWxDCH:PWxDCL<7:6>). Table 12-3 shows the maximum PWM frequency (FPWM) given the value in the period register.

The number of bits of resolution that the PWM can achieve depends on the operation frequency of the device as well as the PWM frequency (FPWM).

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log\left(2\right)} \quad \text{bits}$$

The PWMx duty cycle is as follows:

PWMx Duty Cycle =  $(DCx) \times TOSC$

where DCx represents the 10-bit value from PWxDCH:PWxDCL.

If DCx = 0, then the duty cycle is zero. If PRx = PWxDCH, then the PWM output will be low for one to four Q-clock (depending on the state of the PWxDCL<7:6> bits). For a Duty Cycle to be 100%, the PWxDCH value must be greater then the PRx value.

The duty cycle registers for both PWM outputs are double buffered. When the user writes to these registers, they are stored in master latches. When TMR1 (or TMR2) overflows and a new PWM period begins, the master latch values are transferred to the slave latches and the PWMx pin is forced high.

| Note: | For PW1DCH, PW1DCL, PW2DCH and                |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | PW2DCL registers, a write operation           |  |  |  |  |  |

|       | writes to the "master latches" while a read   |  |  |  |  |  |

|       | operation reads the "slave latches". As a     |  |  |  |  |  |

|       | result, the user may not read back what       |  |  |  |  |  |

|       | was just written to the duty cycle registers. |  |  |  |  |  |

The user should also avoid any "read-modify-write" operations on the duty cycle registers, such as: ADDWF PW1DCH. This may cause duty cycle outputs that are unpredictable.

| TABLE 12-3: | PWM FREQUENCY vs.           |

|-------------|-----------------------------|

|             | <b>RESOLUTION AT 25 MHz</b> |

| PWM                    | Frequency (kHz) |       |         |       |       |  |  |  |  |

|------------------------|-----------------|-------|---------|-------|-------|--|--|--|--|

| Frequency              | 24.4            | 48.8  | 65.104  | 97.66 | 390.6 |  |  |  |  |

| PRx Value              | 0xFF            | 0x7F  | 0x5F    | 0x3F  | 0x0F  |  |  |  |  |

| High<br>Resolution     | 10-bit          | 9-bit | 8.5-bit | 8-bit | 6-bit |  |  |  |  |

| Standard<br>Resolution | 8-bit           | 7-bit | 6.5-bit | 6-bit | 4-bit |  |  |  |  |

### 12.1.3.2 PWM INTERRUPTS

The PWM module makes use of TMR1 or TMR2 interrupts. A timer interrupt is generated when TMR1 or TMR2 equals its period register and is cleared to zero. This interrupt also marks the beginning of a PWM cycle. The user can write new duty cycle values before the timer roll-over. The TMR1 interrupt is latched into the TMR1IF bit and the TMR2 interrupt is latched into the TMR2IF bit. These flags must be cleared in software.

### 12.1.3.3 EXTERNAL CLOCK SOURCE

The PWMs will operate regardless of the clock source of the timer. The use of an external clock has ramifications that must be understood. Because the external TCLK12 input is synchronized internally (sampled once per instruction cycle), the time TCLK12 changes to the time the timer increments will vary by as much as TCY (one instruction cycle). This will cause jitter in the duty cycle as well as the period of the PWM output.

This jitter will be  $\pm$ TCY, unless the external clock is synchronized with the processor clock. Use of one of the PWM outputs as the clock source to the TCLKx input, will supply a synchronized clock.

In general, when using an external clock source for PWM, its frequency should be much less than the device frequency (Fosc).

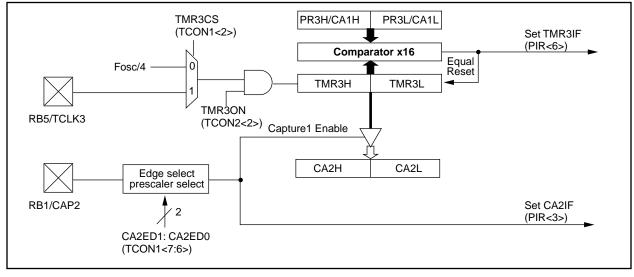

### 12.2.1 ONE CAPTURE AND ONE PERIOD REGISTER MODE

In this mode registers PR3H/CA1H and PR3L/CA1L constitute a 16-bit period register. A block diagram is shown in Figure 12-7. The timer increments until it equals the period register and then resets to 0000h. TMR3 Interrupt Flag bit (TMR3IF) is set at this point. This interrupt can be disabled by clearing the TMR3 Interrupt Enable bit (TMR3IE). TMR3IF must be cleared in software.

This mode is selected if control bit CA1/PR3 is clear. In this mode, the Capture1 register, consisting of high byte (PR3H/CA1H) and low byte (PR3L/CA1L), is configured as the period control register for TMR3. Capture1 is disabled in this mode, and the corresponding Interrupt bit CA1IF is never set. TMR3 increments until it equals the value in the period register and then resets to 0000h.

Capture2 is active in this mode. The CA2ED1 and CA2ED0 bits determine the event on which capture will occur. The possible events are:

- · Capture on every falling edge

- Capture on every rising edge

- · Capture every 4th rising edge

- · Capture every 16th rising edge

When a capture takes place, an interrupt flag is latched into the CA2IF bit. This interrupt can be enabled by setting the corresponding mask bit CA2IE. The Peripheral Interrupt Enable bit (PEIE) must be set and the Global Interrupt Disable bit (GLINTD) must be cleared for the interrupt to be acknowledged. The CA2IF interrupt flag bit must be cleared in software.

When the capture prescale select is changed, the prescaler is not reset and an event may be generated. Therefore, the first capture after such a change will be ambiguous. However, it sets the time-base for the next capture. The prescaler is reset upon chip reset. Capture pin RB1/CAP2 is a multiplexed pin. When used as a port pin, Capture2 is not disabled. However, the user can simply disable the Capture2 interrupt by clearing CA2IE. If RB1/CAP2 is used as an output pin, the user can activate a capture by writing to the port pin. This may be useful during development phase to emulate a capture interrupt.

The input on capture pin RB1/CAP2 is synchronized internally to internal phase clocks. This imposes certain restrictions on the input waveform (see the Electrical Specification section for timing).

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the Timer3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The recommended sequence to read capture registers and capture overflow flag bits is shown in Example 12-1.

## EXAMPLE 12-1: SEQUENCE TO READ CAPTURE REGISTERS

| MOVLB 3              | ;Select Bank 3          |

|----------------------|-------------------------|

| MOVPF CA2L,LO_BYTE   | ;Read Capture2 low      |

|                      | ;byte, store in LO_BYTE |

| MOVPF CA2H, HI_BYTE  | ;Read Capture2 high     |

|                      | ;byte, store in HI_BYTE |

| MOVPF TCON2,STAT_VAL | ;Read TCON2 into file   |

|                      | ;STAT_VAL               |

## FIGURE 12-7: TIMER3 WITH ONE CAPTURE AND ONE PERIOD REGISTER BLOCK DIAGRAM

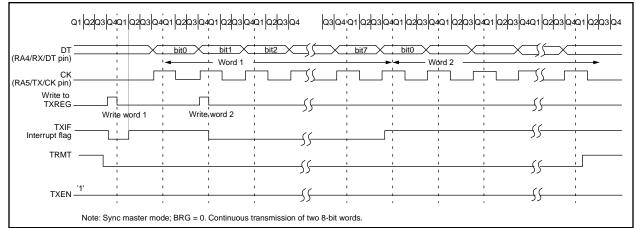

# TABLE 13-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                                        | Name  | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|--------|--------|--------|-------|-------|-------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 1                                    | PIR   | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF      | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9    | SREN   | CREN   | —     | FERR  | OERR  | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 16h, Bank 0                                    | TXREG | TX7   | TX6    | TX5    | TX4    | TX3   | TX2   | TX1   | TX0       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1                                    | PIE   | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE      | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9    | TXEN   | SYNC   | —     |       | TRMT  | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |        |        |        |       |       |       | xxxx xxxx | uuuu uuuu                     |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous master transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

## FIGURE 13-9: SYNCHRONOUS TRANSMISSION

## FIGURE 13-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

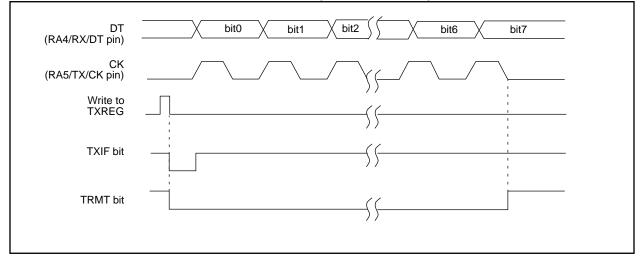

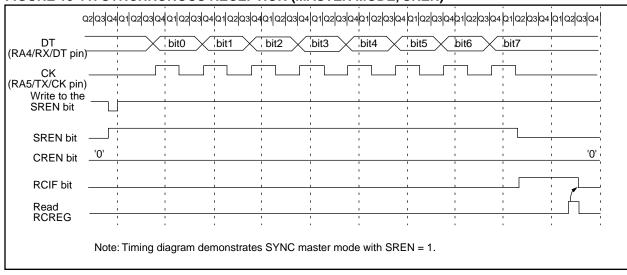

#### 13.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either the SREN (RCSTA<5>) bit or the CREN (RCSTA<4>) bit. Data is sampled on the RA4/RX/DT pin on the falling edge of the clock. If SREN is set, then only a single word is received. If CREN is set, the reception is continuous until CREN is reset. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to RCREG (if it is empty). If the transfer is complete, the interrupt bit RCIF (PIR<0>) is set. The actual interrupt can be enabled/disabled by setting/clearing the RCIE (PIE<0>) bit. RCIF is a read only bit which is RESET by the hardware. In this case it is reset when RCREG has been read and is empty. RCREG is a double buffered register; i.e., it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR. On the clocking of the last bit of the third byte, if RCREG is still full, then the overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. RCREG can be read twice to retrieve the two bytes in the FIFO. The OERR bit has to be cleared in software. This is done by clearing the CREN bit. If OERR bit is set, transfers from RSR to RCREG are inhibited, so it is essential to clear OERR bit if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register will allow the RX9D and FERR bits to be loaded with values for the next received data: therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old FERR and RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. See Section 13.1 for details.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- 6. The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- 7. Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading RCREG.

- 9. If any error occurred, clear the error by clearing CREN.

Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

# FIGURE 13-11: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

# 14.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLK-OUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation and SLEEP mode, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 14.1).

Under normal operation, the WDT must be cleared on a regular interval. This time is less the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

#### 14.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms, (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a postscaler with a division ratio of up to 1:256 can be assigned to the WDT. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

### 14.3.2 CLEARING THE WDT AND POSTSCALER

The WDT and postscaler are cleared when:

- The device is in the reset state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the reset state.

#### 14.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT postscaler) it may take several seconds before a WDT time-out occurs.

The WDT and postscaler is the Power-up Timer during the Power-on Reset sequence.

### 14.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the  $\overline{\text{TO}}$  bit is cleared (device is not reset). The CLRWDT instruction can be used to set the  $\overline{\text{TO}}$  bit. This allows the WDT to be a simple overflow timer. When in sleep, the WDT does not increment.

| DCF        | SNZ                                                                                                                                                                                                                                                                                                                                     | Decreme                           | ent f, skij                        | o if no                   | ot O                 |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------|---------------------------|----------------------|--|--|--|

| Synt       | tax:                                                                                                                                                                                                                                                                                                                                    | [ <i>label</i> ] D                | CFSNZ                              | f,d                       |                      |  |  |  |

| Ope        | rands:                                                                                                                                                                                                                                                                                                                                  | 0 ≤ f ≤ 25<br>d ∈ [0,1]           | $0 \le f \le 255$<br>$d \in [0,1]$ |                           |                      |  |  |  |

| Ope        | ration:                                                                                                                                                                                                                                                                                                                                 | (f) – 1 $\rightarrow$ skip if not | • • •                              |                           |                      |  |  |  |

| Stat       | us Affected:                                                                                                                                                                                                                                                                                                                            | None                              |                                    |                           |                      |  |  |  |

| Enc        | oding:                                                                                                                                                                                                                                                                                                                                  | 0010                              | 011d                               | ffff                      | ffff                 |  |  |  |

| Des        | Description:<br>The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed i<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'.<br>If the result is not 0, the next instruction<br>which is already fetched, is discarded<br>and an NOP is executed instead making it a two-cycle instruction. |                                   |                                    |                           |                      |  |  |  |

| Wor        | ds:                                                                                                                                                                                                                                                                                                                                     | 1                                 |                                    |                           |                      |  |  |  |

| Cycl       | es:                                                                                                                                                                                                                                                                                                                                     | 1(2)                              |                                    |                           |                      |  |  |  |

| QC         | ycle Activity:                                                                                                                                                                                                                                                                                                                          |                                   |                                    |                           |                      |  |  |  |

|            | Q1                                                                                                                                                                                                                                                                                                                                      | Q2                                | Q3                                 |                           | Q4                   |  |  |  |

|            | Decode                                                                                                                                                                                                                                                                                                                                  | Read<br>register 'f'              | Execu                              | ıte                       | Write to destination |  |  |  |

| lf sk      | ip:                                                                                                                                                                                                                                                                                                                                     |                                   |                                    |                           |                      |  |  |  |

|            | Q1                                                                                                                                                                                                                                                                                                                                      | Q2                                | Q3                                 |                           | Q4                   |  |  |  |

|            | Forced NOP                                                                                                                                                                                                                                                                                                                              | NOP                               | Execu                              | ute                       | NOP                  |  |  |  |

| <u>Exa</u> | <u>mple</u> :                                                                                                                                                                                                                                                                                                                           | HERE<br>ZERO<br>NZERO             | DCFSNZ<br>:<br>:                   | TEMP                      | P, 1                 |  |  |  |

|            | Before Instru<br>TEMP_V                                                                                                                                                                                                                                                                                                                 |                                   | ?                                  |                           |                      |  |  |  |

|            | After Instruct<br>TEMP_V<br>If TEMP_<br>PC<br>If TEMP_<br>PC                                                                                                                                                                                                                                                                            | ALUE =<br>VALUE =<br>=            | 0;<br>Addre:<br>0;                 | _VALU<br>ss (ze<br>ss (nz | RO)                  |  |  |  |

| Syntax:<br>Operand | de.         | [ label ]                                                                           | 0010                                             |                                     |                                  |

|--------------------|-------------|-------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------|----------------------------------|

| Operand            | 18.         | $0 \le k \le 81$                                                                    | ~                                                | i.                                  |                                  |

|                    |             |                                                                                     | •                                                |                                     |                                  |

| Operatio           | on:         | k → PC<1<br>k<12:8> -<br>PC<15:13                                                   | → PCLA                                           |                                     | ,                                |

| Status A           | Affected:   | None                                                                                |                                                  |                                     |                                  |

| Encodin            | ig:         | 110k                                                                                | kkkk                                             | kkkk                                | kkkl                             |

| Descript           |             | anywhere w<br>The thirtee<br>loaded into<br>upper eigh<br>PCLATH. o<br>instruction. | n bit imm<br>PC bits<br>t bits of P<br>30T0 is a | ediate va<br><12:0>. 1<br>C are loa | alue is<br>Then the<br>aded into |

| Words:             |             | 1                                                                                   |                                                  |                                     |                                  |

| Cycles:            |             | 2                                                                                   |                                                  |                                     |                                  |

| Q Cycle            | Activity:   |                                                                                     |                                                  |                                     |                                  |

|                    | Q1          | Q2                                                                                  | Q3                                               | 5                                   | Q4                               |

| E                  | Decode      | Read literal<br>'k'<7:0>                                                            | Execu                                            | ute                                 | NOP                              |

| For                | ced NOP     | NOP                                                                                 | Execu                                            | ute                                 | NOP                              |

| Example            | <u>e</u> :  | GOTO THE                                                                            | RE                                               |                                     |                                  |

| Afte               | er Instruct | tion                                                                                |                                                  |                                     |                                  |

|                    | PC =        | Address (TH                                                                         | HERE )                                           |                                     |                                  |

| MOVFP                        | Move f to                 | р                                 |                                                                         | MOVLB                    | Move Lite                                                                                                                                                                                      | eral to low i       | nibble in BSR                 |  |

|------------------------------|---------------------------|-----------------------------------|-------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------|--|

| Syntax:                      | [ <i>label</i> ] N        | IOVFP f,p                         |                                                                         | Syntax:                  | [ label ]                                                                                                                                                                                      | MOVLB k             |                               |  |

| Operands:                    | 0 ≤ f ≤ 255               | 5                                 |                                                                         | Operands:                | $0 \le k \le 15$                                                                                                                                                                               | 5                   |                               |  |

|                              | $0 \le p \le 31$          |                                   |                                                                         | Operation:               | k  ightarrow (BSR                                                                                                                                                                              | (<3:0>)             |                               |  |

| Operation:                   | $(f) \to (p)$             |                                   |                                                                         | Status Affected:         | None                                                                                                                                                                                           |                     |                               |  |

| Status Affected:             | None                      |                                   |                                                                         | Encoding:                | 1011                                                                                                                                                                                           | 1000 ui             | uuu kkkk                      |  |

| Encoding:                    | 011p                      | pppp ff                           | ff ffff                                                                 | Description:             | The four bi                                                                                                                                                                                    | t literal 'k' is lo | baded in the                  |  |

| Description:                 | to data mer<br>can be any | mory location '<br>where in the 2 | nory location 'f'<br>p'. Location 'f'<br>56 word data<br>'p' can be 00h |                          | Bank Select Register (BSR). Only the<br>low 4-bits of the Bank Select Register<br>are affected. The upper half of the BSR<br>is unchanged. The assembler will<br>encode the "u" fields as '0'. |                     |                               |  |

|                              |                           | 'f' can be WR                     | EG (a useful                                                            | Words:                   | 1                                                                                                                                                                                              |                     |                               |  |

|                              | special situ              | ,                                 | ful for transfer-                                                       | Cycles:                  | 1                                                                                                                                                                                              |                     |                               |  |

|                              |                           |                                   | on to a periph-                                                         | Q Cycle Activity:        |                                                                                                                                                                                                |                     |                               |  |

|                              |                           |                                   | transmit buffer                                                         | Q1                       | Q2                                                                                                                                                                                             | Q3                  | Q4                            |  |

|                              | indirectly a              | ort). Both 'f' an<br>ddressed.    | d p can be                                                              | Decode                   | Read                                                                                                                                                                                           | Execute             | Write literal                 |  |

| Words:                       | 1                         |                                   |                                                                         |                          | literal 'u:k'                                                                                                                                                                                  |                     | 'k' to<br>BSR<3:0>            |  |

| Cycles:                      | 1                         |                                   |                                                                         | Example:                 | MOVLB                                                                                                                                                                                          | 0x5                 |                               |  |

| Q Cycle Activity             | :                         |                                   |                                                                         | Before Instru            | uction                                                                                                                                                                                         |                     |                               |  |

| Q1                           | Q2                        | Q3                                | Q4                                                                      | BSR reg                  | ister = 0x                                                                                                                                                                                     | :22                 |                               |  |

| Decode                       | Read<br>register 'f'      | Execute                           | Write<br>register 'p'                                                   | After Instruc<br>BSR reg |                                                                                                                                                                                                | :25                 |                               |  |

| Example:                     | MOVFP I                   | REG1, REG2                        |                                                                         | Note: For th             | ne PIC17C42                                                                                                                                                                                    | 2, only the lo      | ow four bits of               |  |

| Before Insti<br>REG1<br>REG2 |                           | 33,<br>11                         |                                                                         |                          | BSR registe<br>ed. The uppe                                                                                                                                                                    |                     | sically imple-<br>ead as '0'. |  |

| After Instru<br>REG1         |                           | 33,                               |                                                                         |                          |                                                                                                                                                                                                |                     |                               |  |

REG2

0x33

=

| MOVPF                         | Move p to f                                                                                                                                                                                  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                       | [ <i>label</i> ] MOVPF p,f                                                                                                                                                                   |

| Operands:                     | $0 \le f \le 255$ $0 \le p \le 31$                                                                                                                                                           |

| Operation:                    | $(p) \rightarrow (f)$                                                                                                                                                                        |

| Status Affected:              | Z                                                                                                                                                                                            |

| Encoding:                     | 010p pppp ffff ffff                                                                                                                                                                          |

| Description:                  | Move data from data memory location<br>'p' to data memory location 'f'. Location<br>'f' can be anywhere in the 256 byte data<br>space (00h to FFh) while 'p' can be 00h<br>to 1Fh.           |

|                               | Either 'p' or 'f' can be WREG (a useful special situation).                                                                                                                                  |

|                               | MOVPF is particularly useful for transfer-<br>ring a peripheral register (e.g. the timer<br>or an I/O port) to a data memory loca-<br>tion. Both 'f' and 'p' can be indirectly<br>addressed. |

| Words:                        | 1                                                                                                                                                                                            |

| Cycles:                       | 1                                                                                                                                                                                            |

| Q Cycle Activity:             |                                                                                                                                                                                              |

| Q1                            | Q2 Q3 Q4                                                                                                                                                                                     |

| Decode                        | ReadExecuteWriteregister 'p'register 'f'                                                                                                                                                     |

| Example:                      | MOVPF REG1, REG2                                                                                                                                                                             |

| Before Instru                 | ction                                                                                                                                                                                        |

| REG1<br>REG2                  | = 0x11<br>= 0x33                                                                                                                                                                             |

| After Instruc<br>REG1<br>REG2 | ion<br>= 0x11<br>= 0x11                                                                                                                                                                      |

| MO\        | /WF                          | Ν               | love WR            | EG to f                       |     |   |                     |

|------------|------------------------------|-----------------|--------------------|-------------------------------|-----|---|---------------------|

| Synt       | ax:                          | [ /             | label ]            | MOVWF                         | = f |   |                     |

| Ope        | rands:                       | 0               | ≤ f ≤ 25           | 5                             |     |   |                     |

| Ope        | ration:                      | (\              | VREG) ·            | $\rightarrow$ (f)             |     |   |                     |

| State      | us Affected:                 | N               | one                |                               |     |   |                     |

| Enco       | oding:                       |                 | 0000               | 0001                          | fff | f | ffff                |

| Des        | cription:                    | Lo              |                    | from WR<br>can be a<br>space. |     | • |                     |

| Wor        | ds:                          | 1               |                    |                               |     |   |                     |

| Cycl       | es:                          | 1               |                    |                               |     |   |                     |

| QC         | ycle Activity:               |                 |                    |                               |     |   |                     |

|            | Q1                           |                 | Q2                 | Q3                            | 3   |   | Q4                  |

|            | Decode                       |                 | Read<br>gister 'f' | Execu                         | ute |   | Write<br>gister 'f' |

| <u>Exa</u> | <u>mple</u> :                | M               | OVWF               | REG                           |     |   |                     |

|            | Before Instru<br>WREG<br>REG | uctio<br>=<br>= | n<br>0x4F<br>0xFF  |                               |     |   |                     |

|            | After Instruc<br>WREG<br>REG | tion<br>=<br>=  | 0x4F<br>0x4F       |                               |     |   |                     |

| RETFIE      |                         | Return fr                                                                         | om Inte                               | rrupt                                  |                                    |

|-------------|-------------------------|-----------------------------------------------------------------------------------|---------------------------------------|----------------------------------------|------------------------------------|

| Syntax:     |                         | [ label ]                                                                         | RETFIE                                |                                        |                                    |

| Operands    | :                       | None                                                                              |                                       |                                        |                                    |

| Operation   | :                       | $\begin{array}{l} TOS \rightarrow (I \\ 0 \rightarrow GLIN \\ PCLATH \end{array}$ | ITD;                                  | nged.                                  |                                    |

| Status Affe | ected:                  | GLINTD                                                                            |                                       |                                        |                                    |

| Encoding:   |                         | 0000                                                                              | 0000                                  | 0000                                   | 0101                               |

| Descriptio  | n:                      | Return from<br>and Top of<br>PC. Interru<br>the GLINT<br>interrupt di             | Stack (To<br>pts are ei<br>D bit. GLI | OS) is load<br>nabled by<br>NTD is the | ded in the<br>clearing<br>e global |

| Words:      |                         | 1                                                                                 |                                       |                                        |                                    |

| Cycles:     |                         | 2                                                                                 |                                       |                                        |                                    |

| Q Cycle A   | ctivity:                |                                                                                   |                                       |                                        |                                    |

| (           | Q1                      | Q2                                                                                | Q                                     | 3                                      | Q4                                 |

| Dee         | code                    | Read<br>register<br>T0STA                                                         | Exect                                 | ute                                    | NOP                                |

| Force       | d NOP                   | NOP                                                                               | Exect                                 | ute                                    | NOP                                |

| P           | Interrup<br>C<br>GLINTD | RETFIE<br>t<br>= TOS<br>= 0                                                       |                                       |                                        |                                    |

|             |                         |                                                                                   |                                       |                                        |                                    |

| RETL    | w                          | Return Li                                                                                                                                        | teral to WRI                                                                                             | EG                                                               |

|---------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Synta   | ix:                        | [label]                                                                                                                                          | RETLW k                                                                                                  |                                                                  |

| Opera   | ands:                      | $0 \le k \le 25$                                                                                                                                 | 5                                                                                                        |                                                                  |

| Opera   | ation:                     | •                                                                                                                                                | $G; TOS \rightarrow unchanged$                                                                           | • • •                                                            |

| Status  | s Affected:                | None                                                                                                                                             |                                                                                                          |                                                                  |

| Enco    | ding:                      | 1011                                                                                                                                             | 0110 kk                                                                                                  | kk kkkk                                                          |

| Descr   | ription:                   | 'k'. The proo<br>the top of th                                                                                                                   | gram counter i<br>le stack (the re<br>Idress latch (F                                                    | eight bit literal<br>s loaded from<br>eturn address).<br>PCLATH) |

| Words   | s:                         | 1                                                                                                                                                |                                                                                                          |                                                                  |

| Cycle   | S:                         | 2                                                                                                                                                |                                                                                                          |                                                                  |

| O Cvi   | cle Activity:              |                                                                                                                                                  |                                                                                                          |                                                                  |

| Q Oy    | CIE ACTIVITY.              |                                                                                                                                                  |                                                                                                          |                                                                  |

| Q 0 / ( | Q1                         | Q2                                                                                                                                               | Q3                                                                                                       | Q4                                                               |

|         | -                          | Q2<br>Read<br>literal 'k'                                                                                                                        | Q3<br>Execute                                                                                            | Q4<br>Write to<br>WREG                                           |

|         | Q1                         | Read                                                                                                                                             |                                                                                                          | Write to                                                         |

|         | Q1<br>Decode<br>Forced NOP | Read<br>literal 'k'                                                                                                                              | Execute                                                                                                  | Write to<br>WREG<br>NOP                                          |

| F       | Q1<br>Decode<br>Forced NOP | Read<br>literal 'k'<br>NOP                                                                                                                       | Execute<br>Execute<br>BLE ; WREG co<br>; offset<br>; WREG n<br>; table<br>C ; WREG =<br>C ; Begin t<br>; | Write to<br>WREG<br>NOP                                          |

| Exam    | Q1<br>Decode<br>Forced NOP | Read<br>literal 'k'<br>NOP<br>CALL TAN<br>CALL TAN<br>CALL TAN<br>:<br>TABLE<br>ADDWF PC<br>RETLW ki<br>:<br>:<br>RETLW ki<br>:<br>:<br>RETLW ki | Execute<br>Execute<br>BLE ; WREG co<br>; offset<br>; WREG n<br>; table<br>C ; WREG =<br>C ; Begin t<br>; | Write to<br>WREG<br>NOP                                          |

| RRNCF                                                                                                        | Rotate                                                                                 | Right f (no                                                       | carry)                    |                     |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------|---------------------|

| Syntax:                                                                                                      | [ label ]                                                                              | RRNCF                                                             | f,d                       |                     |

| Operands:                                                                                                    | 0 ≤ f ≤ 2<br>d ∈ [0,1]                                                                 |                                                                   |                           |                     |

| Operation:                                                                                                   | $f < n > \rightarrow f < 0 > \rightarrow$                                              |                                                                   |                           |                     |

| Status Affected:                                                                                             | None                                                                                   |                                                                   |                           |                     |

| Encoding:                                                                                                    | 0010                                                                                   | b000                                                              | ffff                      | ffff                |

| Description:                                                                                                 | one bit to<br>placed in                                                                | ents of regis<br>the right. If '<br>WREG. If 'd<br>ack in registe | d' is 0 the<br>' is 1 the | e result is         |

|                                                                                                              | Г                                                                                      | ► reg                                                             | ister f                   | J►                  |

| Words:                                                                                                       | 1                                                                                      |                                                                   |                           |                     |

| Cycles:                                                                                                      | 1                                                                                      |                                                                   |                           |                     |

| Q Cycle Activity:                                                                                            |                                                                                        |                                                                   |                           |                     |