Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 232 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-25e-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

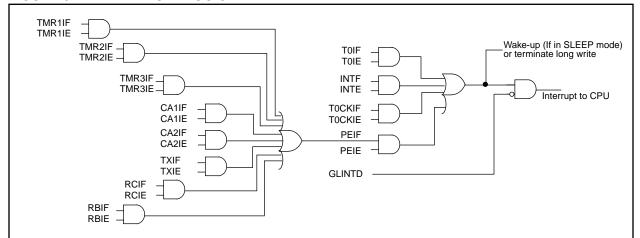

## 5.0 INTERRUPTS

The PIC17C4X devices have 11 sources of interrupt:

- External interrupt from the RA0/INT pin

- Change on RB7:RB0 pins

- TMR0 Overflow

- TMR1 Overflow

- TMR2 Overflow

- TMR3 Overflow

- USART Transmit buffer empty

- USART Receive buffer full

- Capture1

- Capture2

- T0CKI edge occurred

There are four registers used in the control and status of interrupts. These are:

- CPUSTA

- INTSTA

- PIE

- PIR

The CPUSTA register contains the GLINTD bit. This is the Global Interrupt Disable bit. When this bit is set, all interrupts are disabled. This bit is part of the controller core functionality and is described in the Memory Organization section. When an interrupt is responded to, the GLINTD bit is automatically set to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with the interrupt vector address. There are four interrupt vectors. Each vector address is for a specific interrupt source (except the peripheral interrupts which have the same vector address). These sources are:

- External interrupt from the RA0/INT pin

- TMR0 Overflow

- T0CKI edge occurred

- Any peripheral interrupt

When program execution vectors to one of these interrupt vector addresses (except for the peripheral interrupt address), the interrupt flag bit is automatically cleared. Vectoring to the peripheral interrupt vector address does not automatically clear the source of the interrupt. In the peripheral interrupt service routine, the source(s) of the interrupt can be determined by testing the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests.

All of the individual interrupt flag bits will be set regardless of the status of their corresponding mask bit or the GLINTD bit.

For external interrupt events, there will be an interrupt latency. For two cycle instructions, the latency could be one instruction cycle longer.

The "return from interrupt" instruction, RETFIE, can be used to mark the end of the interrupt service routine. When this instruction is executed, the stack is "POPed", and the GLINTD bit is cleared (to re-enable interrupts).

## FIGURE 5-1: INTERRUPT LOGIC

© 1996 Microchip Technology Inc.

### 12.1.3.3.1 MAX RESOLUTION/FREQUENCY FOR EXTERNAL CLOCK INPUT

The use of an external clock for the PWM time-base (Timer1 or Timer2) limits the PWM output to a maximum resolution of 8-bits. The PWxDCL<7:6> bits must be kept cleared. Use of any other value will distort the PWM output. All resolutions are supported when internal clock mode is selected. The maximum attainable frequency is also lower. This is a result of the timing requirements of an external clock input for a timer (see the Electrical Specification section). The maximum PWM frequency, when the timers clock source is the RB4/TCLK12 pin, is shown in Table 12-3 (standard resolution mode).

## 12.2 <u>Timer3</u>

Timer3 is a 16-bit timer consisting of the TMR3H and TMR3L registers. TMR3H is the high byte of the timer and TMR3L is the low byte. This timer has an associated 16-bit period register (PR3H/CA1H:PR3L/CA1L). This period register can be software configured to be a second 16-bit capture register.

When the TMR3CS bit (TCON1<2>) is clear, the timer increments every instruction cycle (Fosc/4). When TMR3CS is set, the timer increments on every falling edge of the RB5/TCLK3 pin. In either mode, the TMR3ON bit must be set for the timer to increment. When TMR3ON is clear, the timer will not increment or set the TMR3IF bit.

Timer3 has two modes of operation, depending on the CA1/PR3 bit (TCON2<3>). These modes are:

- · One capture and one period register mode

- Dual capture register mode

The PIC17C4X has up to two 16-bit capture registers that capture the 16-bit value of TMR3 when events are detected on capture pins. There are two capture pins (RB0/CAP1 and RB1/CAP2), one for each capture register. The capture pins are multiplexed with PORTB pins. An event can be:

- · a rising edge

- a falling edge

- every 4th rising edge

- every 16th rising edge

Each 16-bit capture register has an interrupt flag associated with it. The flag is set when a capture is made. The capture module is truly part of the Timer3 block. Figure 12-7 and Figure 12-8 show the block diagrams for the two modes of operation.

| Address       | Name   | Bit 7      | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets<br>(Note1) |

|---------------|--------|------------|--------|--------|--------|---------|--------|--------|--------|-------------------------------|--------------------------------------------|

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0 | CA1ED1 | CA1ED0 | T16     | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                                  |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF | PWM2ON | PWM10N | CA1/PR3 | TMR3ON | TMR2ON | TMR1ON | 0000 0000                     | 0000 0000                                  |

| 10h, Bank 2   | TMR1   | Timer1 reg | ister  |        |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                                  |

| 11h, Bank 2   | TMR2   | Timer2 reg | ister  |        |        |         |        |        |        | XXXX XXXX                     | uuuu uuuu                                  |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF | TMR2IF | TMR1IF | CA2IF   | CA1IF  | TXIF   | RCIF   | 0000 0010                     | 0000 0010                                  |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE | TMR2IE | TMR1IE | CA2IE   | CA1IE  | TXIE   | RCIE   | 0000 0000                     | 0000 0000                                  |

| 07h, Unbanked | INTSTA | PEIF       | T0CKIF | T0IF   | INTF   | PEIE    | TOCKIE | TOIE   | INTE   | 0000 0000                     | 0000 0000                                  |

| 06h, Unbanked | CPUSTA | —          | _      | STKAV  | GLINTD | TO      | PD     | —      | _      | 11 11                         | 11 qq                                      |

| 10h, Bank 3   | PW1DCL | DC1        | DC0    | —      | —      | —       |        |        | _      | xx                            | uu                                         |

| 11h, Bank 3   | PW2DCL | DC1        | DC0    | TM2PW2 | _      | —       |        |        | _      | xx0                           | uu0                                        |

| 12h, Bank 3   | PW1DCH | DC9        | DC8    | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                                  |

| 13h, Bank 3   | PW2DCH | DC9        | DC8    | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | XXXX XXXX                     | uuuu uuuu                                  |

## TABLE 12-4: REGISTERS/BITS ASSOCIATED WITH PWM

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on conditions, shaded cells are not used by PWM.

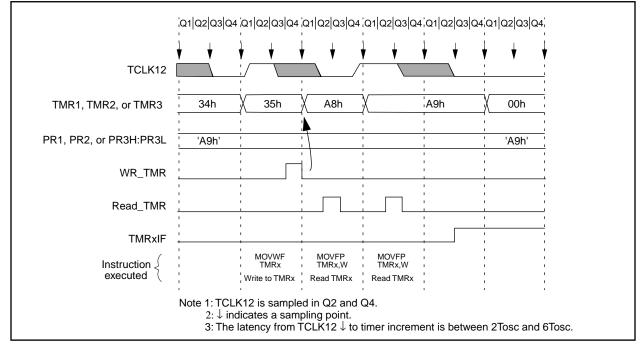

### 12.2.3 EXTERNAL CLOCK INPUT FOR TIMER3

When TMR3CS is set, the 16-bit TMR3 increments on the falling edge of clock input TCLK3. The input on the RB5/TCLK3 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on TCLK3 to the time TMR3 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section. Figure 12-9 shows the timing diagram when operating from an external clock.

### 12.2.4 READING/WRITING TIMER3

Since Timer3 is a 16-bit timer and only 8-bits at a time can be read or written, care should be taken when reading or writing while the timer is running. The best method to read or write the timer is to stop the timer, perform any read or write operation, and then restart Timer3 (using the TMR3ON bit). However, if it is necessary to keep Timer3 free-running, care must be taken. For writing to the 16-bit TMR3, Example 12-2 may be used. For reading the 16-bit TMR3, Example 12-3 may be used. Interrupts must be disabled during this routine.

### EXAMPLE 12-2: WRITING TO TMR3

BSF CPUSTA, GLINTD ;Disable interrupt MOVFP RAM\_L, TMR3L ; MOVFP RAM\_H, TMR3H ; BCF CPUSTA, GLINTD ;Done,enable interrupt

### **EXAMPLE 12-3: READING FROM TMR3**

| MOVPF TMR3L, TMPLO ;read low t<br>MOVPF TMR3H, TMPHI ;read high<br>MOVFP TMPLO, WREG ;tmplo -> w | tmr0  |

|--------------------------------------------------------------------------------------------------|-------|

| CPFSLT TMR3L, WREG ;tmr0l < wr                                                                   | eg?   |

| RETURN ;no then re                                                                               | eturn |

| MOVPF TMR3L, TMPLO ;read low t                                                                   | .mr0  |

| MOVPF TMR3H, TMPHI ;read high                                                                    | tmr0  |

| RETURN ; return                                                                                  |       |

### FIGURE 12-9: TMR1, TMR2, AND TMR3 OPERATION IN EXTERNAL CLOCK MODE

## 13.4 USART Synchronous Slave Mode

The synchronous slave mode differs from the master mode in the fact that the shift clock is supplied externally at the RA5/TX/CK pin (instead of being supplied internally in the master mode). This allows the device to transfer or receive data in the SLEEP mode. The slave mode is entered by clearing the CSRC (TXSTA<7>) bit.

### 13.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the sync master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to TXREG and then the SLEEP instruction executes, the following will occur. The first word will immediately transfer to the TSR and will transmit as the shift clock is supplied. The second word will remain in TXREG. TXIF will not be set. When the first word has been shifted out of TSR, TXREG will transfer the second word to the TSR and the TXIF flag will now be set. If TXIE is enabled, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, then the program will branch to interrupt vector (0020h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting the SYNC and SPEN bits and clearing the CSRC bit.

- 2. Clear the CREN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. Start transmission by loading data to TXREG.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 7. Enable the transmission by setting TXEN.

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the reverse order.

## 13.4.2 USART SYNCHRONOUS SLAVE RECEPTION

Operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode. Also, SREN is a don't care in slave mode.

If receive is enabled (CREN) prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR will transfer the data to RCREG (setting RCIF) and if the RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0020h).

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting the SYNC and SPEN bits and clearing the CSRC bit.

- 2. If interrupts are desired, then set the RCIE bit.

- 3. If 9-bit reception is desired, then set the RX9 bit.

- 4. To enable reception, set the CREN bit.

- 5. The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- 6. Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading RCREG.

- 8. If any error occurred, clear the error by clearing the CREN bit.

Note: To abort reception, either clear the SPEN bit, the SREN bit (when in single receive mode), or the CREN bit (when in continuous receive mode). This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

| Address     | Name                                           | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|------------------------------------------------|-------|--------|--------|--------|-------|-------|-------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR                                            | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF      | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA                                          | SPEN  | RX9    | SREN   | CREN   |       | FERR  | OERR  | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 16h, Bank 0 | TXREG                                          | TX7   | TX6    | TX5    | TX4    | TX3   | TX2   | TX1   | TX0       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE                                            | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE      | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA                                          | CSRC  | TX9    | TXEN   | SYNC   |       | _     | TRMT  | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 | 17h, Bank 0 SPBRG Baud rate generator register |       |        |        |        |       |       |       | xxxx xxxx | uuuu uuuu                     |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous slave transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

### TABLE 13-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address     | Name                                          | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-----------------------------------------------|-------|--------|--------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank1  | PIR                                           | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank0  | RCSTA                                         | SPEN  | RX9    | SREN   | CREN   | _     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank0  | RCREG                                         | RX7   | RX6    | RX5    | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank1  | PIE                                           | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA                                         | CSRC  | TX9    | TXEN   | SYNC   | _     | -     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank0  | 17h, Bank0 SPBRG Baud rate generator register |       |        |        |        |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous slave reception.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

## 14.1 Configuration Bits

The PIC17CXX has up to seven configuration locations (Table 14-1). These locations can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. Any write to a configuration location, regardless of the data, will program that configuration bit. A TABLWT instruction is required to write to program memory locations. The configuration bits can be read by using the TABLRD instructions. Reading any configuration location between FE00h and FE07h will read the low byte of the configuration word (Figure 14-1) into the TABLATL register. The TABLATH register will be FFh. Reading a configuration location between FE08h and FE0Fh will read the high byte of the configuration word into the TABLATL register. The TABLATH register will be FFh.

Addresses FE00h thorough FE0Fh are only in the program memory space for microcontroller and code protected microcontroller modes. A device programmer will be able to read the configuration word in any processor mode. See programming specifications for more detail.

### TABLE 14-1: CONFIGURATION LOCATIONS

| Bit                | Address              |

|--------------------|----------------------|

| FOSC0              | FE00h                |

| FOSC1              | FE01h                |

| WDTPS0             | FE02h                |

| WDTPS1             | FE03h                |

| PM0                | FE04h                |

| PM1                | FE06h                |

| PM2 <sup>(1)</sup> | FE0Fh <sup>(1)</sup> |

Note 1: This location does not exist on the PIC17C42.

| Note: | When progr    |          |           |        |         |  |  |

|-------|---------------|----------|-----------|--------|---------|--|--|

|       | tion location | ns, they | must be p | orogra | mmed in |  |  |

|       | ascending     | order.   | Starting  | with   | address |  |  |

|       | FE00h.        |          |           |        |         |  |  |

## 14.2 Oscillator Configurations

### 14.2.1 OSCILLATOR TYPES

The PIC17CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LF: Low Power Crystal

- XT: Crystal/Resonator

- EC: External Clock Input

- RC: Resistor/Capacitor

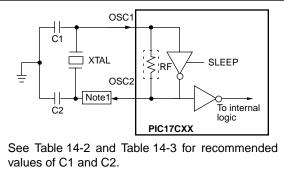

## 14.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT or LF modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 14-2). The PIC17CXX Oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications.

For frequencies above 20 MHz, it is common for the crystal to be an overtone mode crystal. Use of overtone mode crystals require a tank circuit to attenuate the gain at the fundamental frequency. Figure 14-3 shows an example of this.

### FIGURE 14-2: CRYSTAL OR CERAMIC RESONATOR OPERATION (XT OR LF OSC CONFIGURATION)

Note 1: A series resistor may be required for AT strip cut crystals.

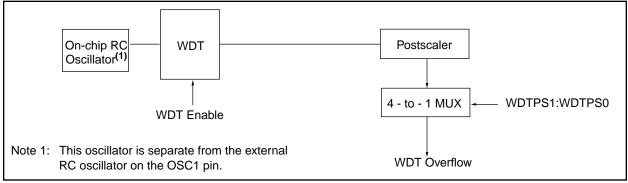

## 14.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLK-OUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation and SLEEP mode, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 14.1).

Under normal operation, the WDT must be cleared on a regular interval. This time is less the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

### 14.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms, (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a postscaler with a division ratio of up to 1:256 can be assigned to the WDT. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

### 14.3.2 CLEARING THE WDT AND POSTSCALER

The WDT and postscaler are cleared when:

- The device is in the reset state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the reset state.

### 14.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT postscaler) it may take several seconds before a WDT time-out occurs.

The WDT and postscaler is the Power-up Timer during the Power-on Reset sequence.

### 14.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the  $\overline{\text{TO}}$  bit is cleared (device is not reset). The CLRWDT instruction can be used to set the  $\overline{\text{TO}}$  bit. This allows the WDT to be a simple overflow timer. When in sleep, the WDT does not increment.

## FIGURE 14-8: WATCHDOG TIMER BLOCK DIAGRAM

### TABLE 14-4: REGISTERS/BITS ASSOCIATED WITH THE WATCHDOG TIMER

| Address       | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------|-------|-------|-------|--------|--------|--------|-------|-------|-------------------------------|-----------------------------------------|

| —             | Config | -     | PM1   | -     | PM0    | WDTPS1 | WDTPS0 | FOSC1 | FOSC0 | (Note 2)                      | (Note 2)                                |

| 06h, Unbanked | CPUSTA |       |       | STKAV | GLINTD | TO     | PD     |       | —     | 11 11                         | 11 qq                                   |

Legend: - = unimplemented read as '0', q - value depends on condition, shaded cells are not used by the WDT.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

2: This value will be as the device was programmed, or if unprogrammed, will read as all '1's.

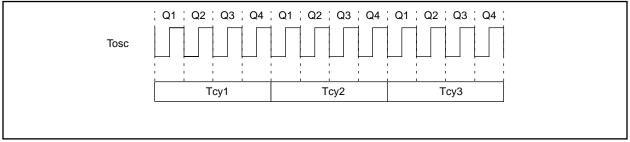

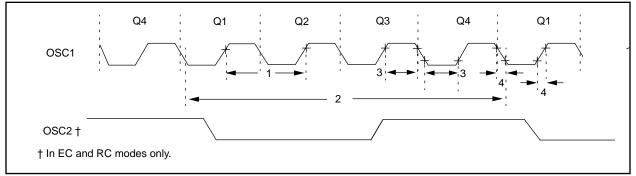

## 15.2 <u>Q Cycle Activity</u>

Each instruction cycle (Tcy) is comprised of four Q cycles (Q1-Q4). The Q cycles provide the timing/designation for the Decode, Read, Execute, Write etc., of each instruction cycle. The following diagram shows the relationship of the Q cycles to the instruction cycle.

The 4 Q cycles that make up an instruction cycle (Tcy) can be generalized as:

- Q1: Instruction Decode Cycle or forced NOP

- Q2: Instruction Read Cycle or NOP

- Q3: Instruction Execute

- Q4: Instruction Write Cycle or NOP

Each instruction will show the detailed Q cycle operation for the instruction.

## FIGURE 15-2: Q CYCLE ACTIVITY

# PIC17C4X

| INFSNZ                                               | Incremer                                                                                                            | Increment f, skip if not 0                                                            |                                                                            |                                                |  |  |  |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------|--|--|--|--|--|

| Syntax:                                              | [ <i>label</i> ] II                                                                                                 | NFSNZ                                                                                 | f,d                                                                        |                                                |  |  |  |  |  |

| Operands:                                            | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                                                                             | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$                     |                                                                            |                                                |  |  |  |  |  |

| Operation:                                           | (f) + 1 $\rightarrow$                                                                                               | (dest), s                                                                             | kip if not                                                                 | 0                                              |  |  |  |  |  |

| Status Affected:                                     | None                                                                                                                |                                                                                       |                                                                            |                                                |  |  |  |  |  |

| Encoding:                                            | 0010                                                                                                                | 010d                                                                                  | ffff                                                                       | ffff                                           |  |  |  |  |  |

| Description:                                         | The conter<br>mented. If<br>WREG. If '<br>back in reg<br>If the result<br>which is all<br>and an NO<br>it a two-cyc | 'd' is 0 the<br>d' is 1 the<br>jister 'f'.<br>t is not 0,<br>ready feto<br>P is exect | e result is p<br>result is p<br>the next in<br>ched, is dis<br>uted instea | placed in<br>blaced<br>istruction,<br>scarded, |  |  |  |  |  |

| Words:                                               | 1                                                                                                                   |                                                                                       |                                                                            |                                                |  |  |  |  |  |

| Cycles:                                              | 1(2)                                                                                                                | 1(2)                                                                                  |                                                                            |                                                |  |  |  |  |  |

| Q Cycle Activity:                                    |                                                                                                                     |                                                                                       |                                                                            |                                                |  |  |  |  |  |

| Q1                                                   | Q2                                                                                                                  | Q                                                                                     | 3                                                                          | Q4                                             |  |  |  |  |  |

| Decode                                               | Read<br>register 'f'                                                                                                | Exect                                                                                 |                                                                            | Vrite to<br>stination                          |  |  |  |  |  |

| lf skip:                                             |                                                                                                                     |                                                                                       |                                                                            |                                                |  |  |  |  |  |

| Q1                                                   | Q2                                                                                                                  | Q                                                                                     | 3                                                                          | Q4                                             |  |  |  |  |  |

| Forced NOP                                           | NOP                                                                                                                 | Exect                                                                                 | ute                                                                        | NOP                                            |  |  |  |  |  |

| Example:                                             | HERE<br>ZERO<br>NZERO                                                                                               | INFSNZ                                                                                | REG, 1                                                                     |                                                |  |  |  |  |  |

| Before Instru<br>REG                                 | uction<br>= REG                                                                                                     |                                                                                       |                                                                            |                                                |  |  |  |  |  |

| After Instruc<br>REG<br>If REG<br>PC<br>If REG<br>PC | = REG +<br>= 1;<br>= Addres<br>= 0;                                                                                 | 1<br>s (zero<br>s (nzero                                                              |                                                                            |                                                |  |  |  |  |  |

| Current           |                        | [ lahal]                                |               |                   |                  |

|-------------------|------------------------|-----------------------------------------|---------------|-------------------|------------------|

| Synt              | ax:                    | [ label ]                               | IORLW         | К                 |                  |

| Ope               | rands:                 | $0 \le k \le 25$                        | 55            |                   |                  |

| Ope               | ration:                | (WREG)                                  | .OR. (k)      | $\rightarrow$ (WR | EG)              |

| State             | us Affected:           | Z                                       |               |                   |                  |

| Enco              | oding:                 | 1011                                    | 0011          | kkkk              | kkkk             |

| Description:      |                        | The conte<br>the eight b<br>placed in \ | it literal 'k |                   |                  |

| Words:            |                        | 1                                       |               |                   |                  |

| Cycles:           |                        | 1                                       |               |                   |                  |

| Q Cycle Activity: |                        |                                         |               |                   |                  |

|                   | Q1                     | Q2                                      | Q             | 3                 | Q4               |

|                   | Decode                 | Read<br>literal 'k'                     | Exect         | ute               | Write to<br>WREG |

| Example:          |                        | IORLW                                   | 0x35          |                   |                  |

|                   | Before Instru<br>WREG  | iction<br>= 0x9A                        |               |                   |                  |

|                   | After Instruct<br>WREG | tion<br>= 0xBF                          |               |                   |                  |

## PIC17C4X

| RLNCF              | Rotate Left f (no carry)                                                                                                                             |          |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Syntax:            | [label] RLNCF f,d                                                                                                                                    |          |

| Operands:          | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$                                                                                    |          |

| Operation:         | $f < n > \rightarrow d < n+1 >;$<br>$f < 7 > \rightarrow d < 0 >$                                                                                    |          |

| Status Affected:   | None                                                                                                                                                 |          |

| Encoding:          | 0010 001d ffff                                                                                                                                       | ffff     |

| Description:       | The contents of register 'f' are re<br>one bit to the left. If 'd' is 0 the re<br>placed in WREG. If 'd' is 1 the re<br>stored back in register 'f'. | esult is |

| Words:             | 1                                                                                                                                                    |          |

| Cycles:            | 1                                                                                                                                                    |          |

| Q Cycle Activity:  |                                                                                                                                                      |          |

| Q1                 | Q2 Q3 Q                                                                                                                                              | 4        |

| Decode             | ReadExecuteWritregister 'f'destir                                                                                                                    |          |

| Example:           | RLNCF REG, 1                                                                                                                                         |          |

| Before Instru      | uction                                                                                                                                               |          |

| C<br>REG           | = 0<br>= 1110 1011                                                                                                                                   |          |

| After Instruc<br>C | tion                                                                                                                                                 |          |

| RRCF                               | Rotate Right f through Carry                                                                                                                                                                       |  |  |  |  |  |  |  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                            | [label] RRCF f,d                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Operands:                          | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$                                                                                                                                  |  |  |  |  |  |  |  |

| Operation:                         |                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Status Affected:                   | С                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Encoding:                          | 0001 100d ffff ffff                                                                                                                                                                                |  |  |  |  |  |  |  |

| Description:                       | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'. |  |  |  |  |  |  |  |

| Words:                             | 1                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Cycles:                            | 1                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Q Cycle Activity:                  |                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Q1                                 | Q2 Q3 Q4                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Decode                             | Read         Execute         Write to           register 'f'         destination                                                                                                                   |  |  |  |  |  |  |  |

| Example:                           | RRCF REG1,0                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Before Instr                       | uction                                                                                                                                                                                             |  |  |  |  |  |  |  |

| REG1<br>C                          | = 1110 0110<br>= 0                                                                                                                                                                                 |  |  |  |  |  |  |  |

| After Instruc<br>REG1<br>WREG<br>C | tion<br>= 1110 0110<br>= 0111 0011<br>= 0                                                                                                                                                          |  |  |  |  |  |  |  |

## Applicable Devices 42 R42 42A 43 R43 44

|           | Standard Operating Conditions (unless otherwise stated) |                                |                                                          |                                                           |                                                       |            |                                   |  |  |  |  |

|-----------|---------------------------------------------------------|--------------------------------|----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------|------------|-----------------------------------|--|--|--|--|

|           |                                                         |                                |                                                          |                                                           | Operating temperature                                 |            |                                   |  |  |  |  |

| DC CHARA  | DC CHARACTERISTICS                                      |                                |                                                          | $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial and |                                                       |            |                                   |  |  |  |  |

|           |                                                         |                                |                                                          |                                                           | $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |            |                                   |  |  |  |  |

|           |                                                         |                                | Operating voltage VDD range as described in Section 17.1 |                                                           |                                                       |            |                                   |  |  |  |  |

| Parameter |                                                         |                                |                                                          |                                                           |                                                       |            |                                   |  |  |  |  |

| No.       | Sym                                                     | Characteristic                 | Min                                                      | Тур†                                                      | Max                                                   | Units      | Conditions                        |  |  |  |  |

|           |                                                         | Output Low Voltage             |                                                          |                                                           |                                                       |            |                                   |  |  |  |  |

| D080      | VOL                                                     | I/O ports (except RA2 and RA3) | _                                                        | -                                                         | 0.1VDD                                                | V          | IOL = 4 mA                        |  |  |  |  |

| D081      |                                                         | with TTL buffer                | _                                                        | _                                                         | 0.4                                                   | V          | IOL = 6  mA, VDD = 4.5 V          |  |  |  |  |

|           |                                                         |                                |                                                          |                                                           |                                                       |            | Note 6                            |  |  |  |  |

| D082      |                                                         | RA2 and RA3                    | _                                                        | _                                                         | 3.0                                                   | V          | IOL = 60.0 mA, VDD = 5.5V         |  |  |  |  |

| D083      |                                                         | OSC2/CLKOUT                    | _                                                        | _                                                         | 0.4                                                   | v          | IOL = 2  mA,  VDD = 4.5  V        |  |  |  |  |

| 2000      |                                                         | (RC and EC osc modes)          |                                                          |                                                           | 0                                                     |            |                                   |  |  |  |  |

|           |                                                         | Output High Voltage (Note 3)   |                                                          |                                                           |                                                       |            |                                   |  |  |  |  |

| D090      | Vон                                                     | I/O ports (except RA2 and RA3) | 0.9Vdd                                                   | _                                                         | _                                                     | v          | IOH = -2 mA                       |  |  |  |  |

| D091      | VOIT                                                    | with TTL buffer                | 2.4                                                      |                                                           |                                                       |            | IOH = -6.0  mA, VDD = 4.5 V       |  |  |  |  |

| 0001      |                                                         |                                | 2.7                                                      |                                                           |                                                       | v          | Note 6                            |  |  |  |  |

| D092      |                                                         | RA2 and RA3                    | _                                                        | _                                                         | 12                                                    | v          | Pulled-up to externally applied   |  |  |  |  |

| 0032      |                                                         |                                | _                                                        |                                                           | 12                                                    | v          | voltage                           |  |  |  |  |

| D093      |                                                         | OSC2/CLKOUT                    | 2.4                                                      | _                                                         | _                                                     | v          | IOH = -5  mA,  VDD = 4.5  V       |  |  |  |  |

| 0095      |                                                         | (RC and EC osc modes)          | 2.4                                                      |                                                           |                                                       | v          |                                   |  |  |  |  |

|           |                                                         | Capacitive Loading Specs on    |                                                          |                                                           |                                                       |            |                                   |  |  |  |  |

|           |                                                         | Output Pins                    |                                                          |                                                           |                                                       |            |                                   |  |  |  |  |

| D100      | Conce                                                   |                                |                                                          |                                                           | 25 ++                                                 | ~ <b>Г</b> | In EC or RC osc modes when        |  |  |  |  |

| 0100      | COSC2                                                   | OSC2 pin                       | _                                                        | -                                                         | 25 ††                                                 | pF         |                                   |  |  |  |  |

|           |                                                         |                                |                                                          |                                                           |                                                       |            | OSC2 pin is outputting<br>CLKOUT. |  |  |  |  |

|           |                                                         |                                |                                                          |                                                           |                                                       |            | External clock is used to drive   |  |  |  |  |

|           |                                                         |                                |                                                          |                                                           |                                                       |            | OSC1.                             |  |  |  |  |

| D101      | Сю                                                      |                                |                                                          |                                                           | 50 ±±                                                 |            |                                   |  |  |  |  |

|           |                                                         | All I/O pins and OSC2          | _                                                        | -                                                         | 50 ††                                                 | pF         |                                   |  |  |  |  |

| D400      | 0                                                       | (in RC mode)                   |                                                          |                                                           | 400 41                                                |            | La Mission                        |  |  |  |  |

| D102      | CAD                                                     | System Interface Bus           | -                                                        | -                                                         | 100 ††                                                | pF         | In Microprocessor or              |  |  |  |  |

|           |                                                         | (PORTC, PORTD and PORTE)       |                                                          |                                                           |                                                       |            | Extended Microcontroller          |  |  |  |  |

|           |                                                         |                                |                                                          |                                                           |                                                       |            | mode                              |  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

the Design guidance to attain the AC timing specifications. These loads are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/Vpp pin may be kept in this range at times other than programming, but this is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

# PIC17C4X

## Applicable Devices 42 R42 42A 43 R43 44

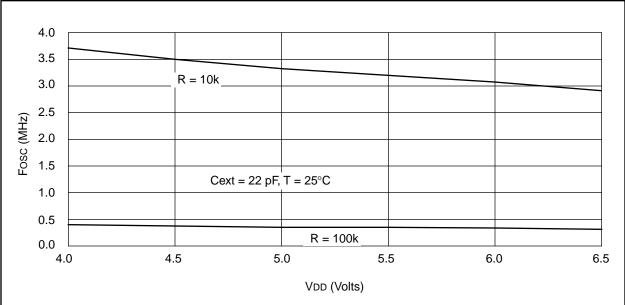

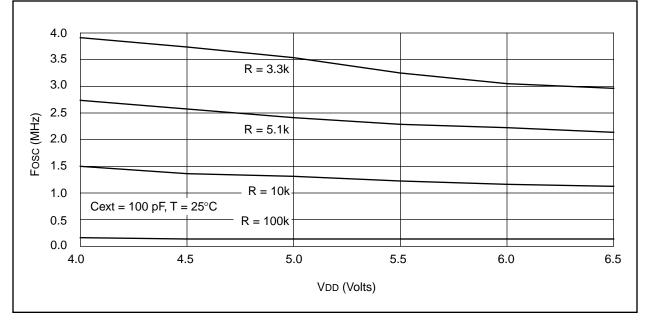

## FIGURE 18-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

## FIGURE 18-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

## PIC17C4X

## Applicable Devices 42 R42 42A 43 R43 44

## 19.5 <u>Timing Diagrams and Specifications</u>

## FIGURE 19-2: EXTERNAL CLOCK TIMING

## TABLE 19-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                     | Min   | Тур†   | Max   | Units | Conditions                               |

|--------------|-------|------------------------------------|-------|--------|-------|-------|------------------------------------------|

|              | Fosc  | External CLKIN Frequency           | DC    | _      | 8     | MHz   | EC osc mode - 08 devices (8 MHz devices) |

|              |       | (Note 1)                           | DC    | _      | 16    | MHz   | - 16 devices (16 MHz devices)            |

|              |       | (                                  | DC    | _      | 25    | MHz   | - 25 devices (25 MHz devices)            |

|              |       |                                    | DC    | —      | 33    | MHz   | - 33 devices (33 MHz devices)            |

|              |       | Oscillator Frequency               | DC    | _      | 4     | MHz   | RC osc mode                              |

|              |       | (Note 1)                           | 1     | _      | 8     | MHz   | XT osc mode - 08 devices (8 MHz devices) |

|              |       |                                    | 1     | _      | 16    | MHz   | - 16 devices (16 MHz devices)            |

|              |       |                                    | 1     | _      | 25    | MHz   | - 25 devices (25 MHz devices)            |

|              |       |                                    | 1     | _      | 33    | MHz   | - 33 devices (33 MHz devices)            |

|              |       |                                    | DC    | —      | 2     | MHz   | LF osc mode                              |

| 1            | Tosc  | External CLKIN Period              | 125   | _      | —     | ns    | EC osc mode - 08 devices (8 MHz devices) |

|              |       | (Note 1)                           | 62.5  | _      | —     | ns    | - 16 devices (16 MHz devices)            |

|              |       |                                    | 40    | _      | —     | ns    | - 25 devices (25 MHz devices)            |

|              |       |                                    | 30.3  | —      | —     | ns    | - 33 devices (33 MHz devices)            |

|              |       | Oscillator Period                  | 250   | _      | —     | ns    | RC osc mode                              |

|              |       | (Note 1)                           | 125   | _      | 1,000 | ns    | XT osc mode - 08 devices (8 MHz devices) |

|              |       |                                    | 62.5  | _      | 1,000 | ns    | - 16 devices (16 MHz devices)            |

|              |       |                                    | 40    | —      | 1,000 | ns    | - 25 devices (25 MHz devices)            |

|              |       |                                    | 30.3  | —      | 1,000 | ns    | - 33 devices (33 MHz devices)            |

|              |       |                                    | 500   | —      | —     | ns    | LF osc mode                              |

| 2            | Тсү   | Instruction Cycle Time<br>(Note 1) | 121.2 | 4/Fosc | DC    | ns    |                                          |

| 3            | TosL, | Clock in (OSC1)                    | 10 ‡  | _      | _     | ns    | EC oscillator                            |

|              | TosH  | high or low time                   |       |        |       |       |                                          |

| 4            | TosR, | Clock in (OSC1)                    |       |        | 5‡    | ns    | EC oscillator                            |

|              | TosF  | rise or fall time                  |       |        |       |       |                                          |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

## Applicable Devices 42 R42 42A 43 R43 44

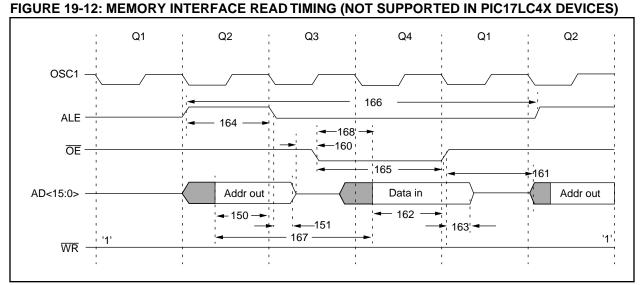

## TABLE 19-12: MEMORY INTERFACE READ REQUIREMENTS (NOT SUPPORTED IN PIC17LC4X DEVICES)

| Parameter<br>No. | Sym      | Characteristic                                            | Min           | Тур†      | Max          | Units | Conditions |

|------------------|----------|-----------------------------------------------------------|---------------|-----------|--------------|-------|------------|

| 150              | TadV2alL | AD15:AD0 (address) valid to ALE↓<br>(address setup time)  | 0.25Tcy - 10  | _         | _            | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)           | 5*            |           | _            | ns    |            |

| 160              | TadZ2oeL | AD15:AD0 hi-impedance to $\overline{\text{OE}}\downarrow$ | 0*            | _         | —            | ns    |            |

| 161              | ToeH2adD | OE↑ to AD15:AD0 driven                                    | 0.25Tcy - 15  | _         | _            | ns    |            |

| 162              | TadV2oeH | Data in valid before OE↑<br>(data setup time)             | 35            | _         | _            | ns    |            |

| 163              | ToeH2adI | OE↑to data in invalid (data hold time)                    | 0             | _         | _            | ns    |            |

| 164              | TalH     | ALE pulse width                                           | —             | 0.25Tcy § | —            | ns    |            |

| 165              | ToeL     | OE pulse width                                            | 0.5Tcy - 35 § | _         | _            | ns    |            |

| 166              | TalH2alH | ALE↑ to ALE↑(cycle time)                                  | —             | TCY §     | _            | ns    |            |

| 167              | Tacc     | Address access time                                       | —             | —         | 0.75Tcy - 30 | ns    |            |

| 168              | Тое      | Output enable access time<br>(OE low to Data Valid)       | —             | _         | 0.5Tcy - 45  | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

\*

NOTES:

#### 21.6 **Package Marking Information** 40-Lead PDIP/CERDIP Example PIC17C43-25I/P L006 AABBCDE 9441CCA MICROCHIP MICROCHIP $\bigcirc$ 40 Lead CERDIP Windowed Example XXXXXXXXXXXX PIC17C44 XXXXXXXXXXXX /JW XXXXXXXXXXXX L184 AABBCDE 9444CCT 44-Lead PLCC Example $\mathcal{M}$ $\mathcal{M}$ MICROCHIP MICROCHIP PIC17C42 XXXXXXXXXX ○ <sub>XXXXXXXXX</sub> Ο -16I/L XXXXXXXXXX L013 AABBCDE 9445CCN 44-Lead MQFP Example $\mathcal{M}$ $\mathbf{w}$ XXXXXXXXXX PIC17C44 -25/PT XXXXXXXXXX XXXXXXXXXXX L247 AABBCDE 9450CAT $\cap$ $\cap$ 44-Lead TQFP Example \$ $\mathcal{Q}$ PIC17C44 XXXXXXXXXXX -25/TQ XXXXXXXXXX XXXXXXXXXXX L247 AABBCDE 9450CAT $\cap$ $\cap$ Microchip part number information Legend: MM...M XX...X Customer specific information\* AA Year code (last 2 digits of calendar year) BΒ Week code (week of January 1 is week '01') С Facility code of the plant at which wafer is manufactured C = Chandler, Arizona, U.S.A., S = Tempe, Arizona, U.S.A. D Mask revision number Е Assembly code of the plant or country of origin in which part was assembled Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information. Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond

code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

## **APPENDIX C: WHAT'S NEW**

The structure of the document has been made consistent with other data sheets. This ensures that important topics are covered across all PIC16/17 families. Here is an overview of new features.

Added the following devices:

PIC17CR42

PIC17C42A

PIC17CR43

A 33 MHz option is now available.

## APPENDIX D: WHAT'S CHANGED

To make software more portable across the different PIC16/17 families, the name of several registers and control bits have been changed. This allows control bits that have the same function, to have the same name (regardless of processor family). Care must still be taken, since they may not be at the same special function register address. The following shows the register and bit names that have been changed:

| Old Name | New Name |

|----------|----------|

| TX8/9    | TX9      |

| RC8/9    | RX9      |

| RCD8     | RX9D     |

| TXD8     | TX9D     |

Instruction DECFSNZ corrected to DCFSNZ

Instruction INCFSNZ corrected to INFSNZ

Enhanced discussion on PWM to include equation for determining bits of PWM resolution.

Section 13.2.2 and 13.3.2 have had the description of updating the FERR and RX9 bits enhanced.

The location of configuration bit PM2 was changed (Figure 6-1 and Figure 14-1).

Enhanced description of the operation of the INTSTA register.

Added note to discussion of interrupt operation.

Tightened electrical spec D110.

Corrected steps for setting up USART Asynchronous Reception.

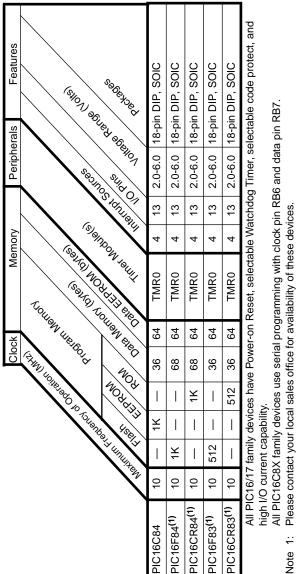

#### E.6 **PIC16C8X Family of Devices**

÷ Note

### **ON-LINE SUPPORT**

Microchip provides two methods of on-line support. These are the Microchip BBS and the Microchip World Wide Web (WWW) site.

Use Microchip's Bulletin Board Service (BBS) to get current information and help about Microchip products. Microchip provides the BBS communication channel for you to use in extending your technical staff with microcontroller and memory experts.

To provide you with the most responsive service possible, the Microchip systems team monitors the BBS, posts the latest component data and software tool updates, provides technical help and embedded systems insights, and discusses how Microchip products provide project solutions.

The web site, like the BBS, is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

### ftp.mchip.com/biz/mchip

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked

Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

### **Connecting to the Microchip BBS**

Connect worldwide to the Microchip BBS using either the Internet or the CompuServe<sup>®</sup> communications network.

### Internet:

You can telnet or ftp to the Microchip BBS at the address:

#### mchipbbs.microchip.com

### **CompuServe Communications Network:**

When using the BBS via the Compuserve Network, in most cases, a local call is your only expense. The Microchip BBS connection does not use CompuServe membership services, therefore you do not need CompuServe membership to join Microchip's BBS. There is no charge for connecting to the Microchip BBS. The procedure to connect will vary slightly from country to country. Please check with your local CompuServe agent for details if you have a problem. CompuServe service allow multiple users various baud rates depending on the local point of access.

The following connect procedure applies in most locations.

- 1. Set your modem to 8-bit, No parity, and One stop (8N1). This is not the normal CompuServe setting which is 7E1.

- 2. Dial your local CompuServe access number.

- 3. Depress the <Enter> key and a garbage string will appear because CompuServe is expecting a 7E1 setting.

- 4. Type +, depress the <Enter> key and "Host Name:" will appear.

- 5. Type MCHIPBBS, depress the <Enter> key and you will be connected to the Microchip BBS.

In the United States, to find the CompuServe phone number closest to you, set your modem to 7E1 and dial (800) 848-4480 for 300-2400 baud or (800) 331-7166 for 9600-14400 baud connection. After the system responds with "Host Name:", type NETWORK, depress the <Enter> key and follow CompuServe's directions.

For voice information (or calling from overseas), you may call (614) 723-1550 for your local CompuServe number.

Microchip regularly uses the Microchip BBS to distribute technical information, application notes, source code, errata sheets, bug reports, and interim patches for Microchip systems software products. For each SIG, a moderator monitors, scans, and approves or disapproves files submitted to the SIG. No executable files are accepted from the user community in general to limit the spread of computer viruses.

### Systems Information and Upgrade Hot Line

The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits.The Hot Line Numbers are:

1-800-755-2345 for U.S. and most of Canada, and

1-602-786-7302 for the rest of the world.

960513

Trademarks: The Microchip name, logo, PIC, PICSTART, PICMASTER and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. FlexROM, MPLAB and fuzzyLAB, are trademarks and SQTP is a service mark of Microchip in the U.S.A.

fuzzyTECH is a registered trademark of Inform Software Corporation. IBM, IBM PC-AT are registered trademarks of International Business Machines Corp. Pentium is a trademark of Intel Corporation. Windows is a trademark and MS-DOS, Microsoft Windows are registered trademarks of Microsoft Corporation. CompuServe is a registered trademark of CompuServe Incorporated.

All other trademarks mentioned herein are the property of their respective companies.

<sup>© 1996</sup> Microchip Technology Inc.