#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 232 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-25i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 OVERVIEW

This data sheet covers the PIC17C4X group of the PIC17CXX family of microcontrollers. The following devices are discussed in this data sheet:

- PIC17C42

- PIC17CR42

- PIC17C42A

- PIC17C43

- PIC17CR43

- PIC17C44

The PIC17CR42, PIC17C42A, PIC17C43, PIC17CR43, and PIC17C44 devices include architectural enhancements over the PIC17C42. These enhancements will be discussed throughout this data sheet.

The PIC17C4X devices are 40/44-Pin, EPROM/ROM-based members of the versatile PIC17CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC17CXX has enhanced core features, 16-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 16-bit wide instruction word with a separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 55 instructions (reduced instruction set) are available in the PIC17C42 and 58 instructions in all the other devices. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance. For mathematical intensive applications all devices, except the PIC17C42, have a single cycle 8 x 8 Hardware Multiplier.

PIC17CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC17C4X devices have up to 454 bytes of RAM and 33 I/O pins. In addition, the PIC17C4X adds several peripheral features useful in many high performance applications including:

- · Four timer/counters

- Two capture inputs

- Two PWM outputs

- A Universal Synchronous Asynchronous Receiver Transmitter (USART)

These special features reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LF oscillator is for low frequency crystals and minimizes power consumption, XT is a standard crystal, and the EC is for external clock input. The SLEEP (power-down) mode offers additional power saving. The user can wake-up the chip from SLEEP through several external and internal interrupts and device resets.

There are four configuration options for the device operational modes:

- Microprocessor

- Microcontroller

- Extended microcontroller

- Protected microcontroller

The microprocessor and extended microcontroller modes allow up to 64K-words of external program memory.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software malfunction.

Table 1-1 lists the features of the PIC17C4X devices.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

The PIC17C4X fits perfectly in applications ranging from precise motor control and industrial process control to automotive, instrumentation, and telecom applications. Other applications that require extremely fast execution of complex software programs or the flexibility of programming the software code as one of the last steps of the manufacturing process would also be well suited. The EPROM technology makes customization of application programs (with unique security codes, combinations, model numbers, parameter storage, etc.) fast and convenient. Small footprint package options make the PIC17C4X ideal for applications with space limitations that require high performance. High speed execution, powerful peripheral features, flexible I/O, and low power consumption all at low cost make the PIC17C4X ideal for a wide range of embedded control applications.

## 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X and PIC16CXX families of microcontrollers will see the architectural enhancements that have been implemented. These enhancements allow the device to be more efficient in software and hardware requirements. Please refer to Appendix A for a detailed list of enhancements and modifications. Code written for PIC16C5X or PIC16CXX can be easily ported to PIC17CXX family of devices (Appendix B).

## 1.2 Development Support

The PIC17CXX family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a universal programmer, a "C" compiler, and fuzzy logic support tools.

<sup>© 1996</sup> Microchip Technology Inc.

### 6.2.2.1 ALU STATUS REGISTER (ALUSTA)

The ALUSTA register contains the status bits of the Arithmetic and Logic Unit and the mode control bits for the indirect addressing register.

As with all the other registers, the ALUSTA register can be the destination for any instruction. If the ALUSTA register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the ALUSTA register as destination may be different than intended.

For example, CLRF ALUSTA will clear the upper four bits and set the Z bit. This leaves the ALUSTA register as 0000u1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions be used to alter the ALUSTA register because these instructions do not affect any status bit. To see how other instructions affect the status bits, see the "Instruction Set Summary."

| Note | 1: The C and DC bits operate as a borrow<br>out bit in subtraction. See the SUBLW and<br>SUBWF instructions for examples. |

|------|---------------------------------------------------------------------------------------------------------------------------|

| Note | 2: The overflow bit will be set if the 2's com-<br>plement result exceeds +127 or is less<br>than -128.                   |

Arithmetic and Logic Unit (ALU) is capable of carrying out arithmetic or logical operations on two operands or a single operand. All single operand instructions operate either on the WREG register or a file register. For two operand instructions, one of the operands is the WREG register and the other one is either a file register or an 8-bit immediate constant.

| FS3      | FS2                                  | FS1                                                                | FS0                                                  | OV                                                      | Z                                   | DC                       | С          | R = Readable bit                                                  |

|----------|--------------------------------------|--------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|-------------------------------------|--------------------------|------------|-------------------------------------------------------------------|

| bit7     | 1                                    | 1                                                                  |                                                      |                                                         |                                     | I                        | bit0       | W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)      |

| bit 7-6: | 01 = Pos                             | FSR1 Mo<br>t auto-dect<br>t auto-incre<br>t value de               | rement FS<br>ement FSI                               | R1 value<br>R1 value                                    |                                     |                          |            |                                                                   |

| bit 5-4: | 01 = Pos                             | FSR0 Mo<br>t auto-deci<br>t auto-incre<br>0 value de               | rement FS<br>ement FSI                               | R0 value<br>R0 value                                    |                                     |                          |            |                                                                   |

| bit 3:   | which cau<br>1 = Overfl              | s used for<br>uses the si                                          | gn bit (bit7<br>ed for sign                          | ') to chang                                             |                                     |                          |            | overflow of the 7-bit magnitude,                                  |

| bit 2:   |                                      | esult of an                                                        |                                                      |                                                         | peration is operation is            |                          |            |                                                                   |

| bit 1:   | For ADDW<br>1 = A carr $0 = No ca$   | •                                                                  | LW instruc<br>the 4th lo<br>m the 4th                | w order bi<br>low order                                 | t of the res<br>bit of the re<br>I. |                          | d          |                                                                   |

| bit 0:   | 1 = A carr<br>Note that<br>(RRCF, RL | F and ADD<br>y-out from<br>a subtrac<br>CF) instru-<br>rry-out fro | the most<br>tion is exe<br>ctions, this<br>m the mos | significant<br>cuted by a<br>bit is load<br>t significa | ded with eit<br>nt bit of the       | two's com<br>her the hig | plement of | the second operand. For rotate<br>der bit of the source register. |

### FIGURE 6-7: ALUSTA REGISTER (ADDRESS: 04h, UNBANKED)

# 9.0 I/O PORTS

The PIC17C4X devices have five I/O ports, PORTA through PORTE. PORTB through PORTE have a corresponding Data Direction Register (DDR), which is used to configure the port pins as inputs or outputs. These five ports are made up of 33 I/O pins. Some of these ports pins are multiplexed with alternate functions.

PORTC, PORTD, and PORTE are multiplexed with the system bus. These pins are configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, these pins are general purpose I/O.

PORTA and PORTB are multiplexed with the peripheral features of the device. These peripheral features are:

- Timer modules

- Capture module

- PWM module

- USART/SCI module

- External Interrupt pin

When some of these peripheral modules are turned on, the port pin will automatically configure to the alternate function. The modules that do this are:

- PWM module

- USART/SCI module

When a pin is automatically configured as an output by a peripheral module, the pins data direction (DDR) bit is unknown. After disabling the peripheral module, the user should re-initialize the DDR bit to the desired configuration.

The other peripheral modules (which require an input) must have their data direction bit configured appropriately.

**Note:** A pin that is a peripheral input, can be configured as an output (DDRx<y> is cleared). The peripheral events will be determined by the action output on the port pin.

## 9.1 PORTA Register

PORTA is a 6-bit wide latch. PORTA does not have a corresponding Data Direction Register (DDR).

Reading PORTA reads the status of the pins.

The RA1 pin is multiplexed with TMR0 clock input, and RA4 and RA5 are multiplexed with the USART functions. The control of RA4 and RA5 as outputs is automatically configured by the USART module.

9.1.1 USING RA2, RA3 AS OUTPUTS

The RA2 and RA3 pins are open drain outputs. To use the RA2 or the RA3 pin(s) as output(s), simply write to the PORTA register the desired value. A '0' will cause the pin to drive low, while a '1' will cause the pin to float (hi-impedance). An external pull-up resistor should be used to pull the pin high. Writes to PORTA will not affect the other pins.

| Note: | When using the RA2 or RA3 pin(s) as out-<br>put(s), read-modify-write instructions (such<br>as BCF, BSF, BTG) on PORTA are not rec-<br>ommended.<br>Such operations read the port pins, do the<br>desired operation, and then write this value<br>to the data latch. This may inadvertently<br>cause the RA2 or RA3 pins to switch from<br>input to output (or vice-versa).<br>It is recommended to use a shadow regis-<br>ter for PORTA. Do the bit operations on this<br>shadow register and then move it to<br>PORTA. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

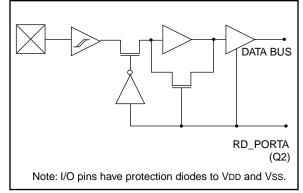

### FIGURE 9-1: RA0 AND RA1 BLOCK DIAGRAM

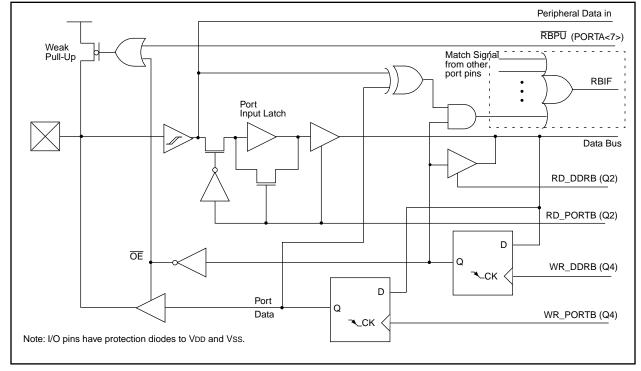

## 9.2 PORTB and DDRB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is DDRB. A '1' in DDRB configures the corresponding port pin as an input. A '0' in the DDRB register configures the corresponding port pin as an output. Reading PORTB reads the status of the pins, whereas writing to it will write to the port latch.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{\text{RBPU}}$  (PORTA<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are enabled on any reset.

PORTB also has an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB0 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB0) are compared with the value in the PORTB data latch. The "mismatch" outputs of RB7:RB0 are OR'ed together to generate the PORTB Interrupt Flag RBIF (PIR<7>). This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt by:

- a) Read-Write PORTB (such as; MOVPF PORTB, PORTB). This will end mismatch condition.

- b) Then, clear the RBIF bit.

A mismatch condition will continue to set the RBIF bit. Reading then writing PORTB will end the mismatch condition, and allow the RBIF bit to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on this port, allows easy interface to a key pad and make it possible for wake-up on key-depression. For an example, refer to AN552 in the *Embedded Control Handbook*.

The interrupt on change feature is recommended for wake-up on operations where PORTB is only used for the interrupt on change feature and key depression operation.

FIGURE 9-4: BLOCK DIAGRAM OF RB<7:4> AND RB<1:0> PORT PINS

# 10.0 OVERVIEW OF TIMER RESOURCES

The PIC17C4X has four timer modules. Each module can generate an interrupt to indicate that an event has occurred. These timers are called:

- Timer0 16-bit timer with programmable 8-bit

- prescaler

- Timer1 8-bit timer

- Timer2 8-bit timer

- Timer3 16-bit timer

For enhanced time-base functionality, two input Captures and two Pulse Width Modulation (PWM) outputs are possible. The PWMs use the TMR1 and TMR2 resources and the input Captures use the TMR3 resource.

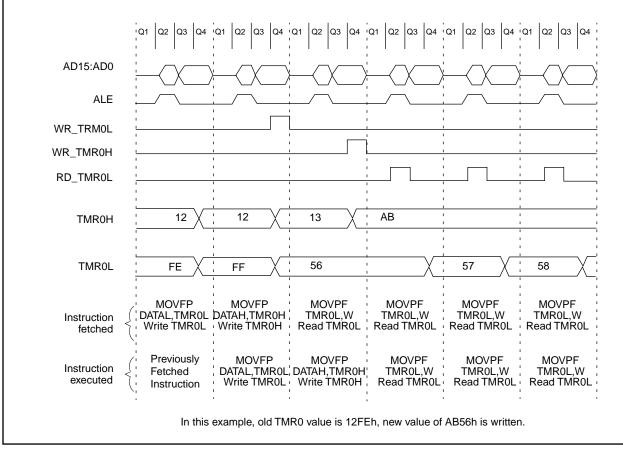

### 10.1 <u>Timer0 Overview</u>

The Timer0 module is a simple 16-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock.

The Timer0 module also has a programmable prescaler option. The PS3:PS0 bits (T0STA<4:1>) determine the prescaler value. TMR0 can increment at the following rates: 1:1, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, 1:256.

When TImer0's clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

## 10.2 <u>Timer1 Overview</u>

The TImer0 module is an 8-bit timer/counter with an 8bit period register (PR1). When the TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the Timer2 module.

TMR1 can be concatenated to TMR2 to form a 16-bit timer. The TMR1 register is the LSB and TMR2 is the MSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled.

## 10.3 <u>Timer2 Overview</u>

The TMR2 module is an 8-bit timer/counter with an 8bit period register (PR2). When the TMR2 value rolls over from the period match value to 0h, the TMR2IF flag is set, and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the TMR1 module.

TMR1 can be concatenated to TMR2 to form a 16-bit timer. The TMR2 register is the MSB and TMR1 is the LSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled.

## 10.4 <u>Timer3 Overview</u>

The TImer3 module is a 16-bit timer/counter with a 16bit period register. When the TMR3H:TMR3L value rolls over to 0h, the TMR3IF bit is set and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB5/TCLK3 pin.

When operating in the dual capture mode, the period registers become the second 16-bit capture register.

## 10.5 Role of the Timer/Counters

The timer modules are general purpose, but have dedicated resources associated with them. Tlmer1 and Timer2 are the time-bases for the two Pulse Width Modulation (PWM) outputs, while Timer3 is the timebase for the two input captures.

© 1996 Microchip Technology Inc.

| Address       | Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4  | Bit 3 | Bit 2         | Bit 1     | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------|--------|--------|-------|--------|-------|---------------|-----------|-----------|-------------------------------|-----------------------------------------|

| 05h, Unbanked | TOSTA  | INTEDG | T0SE   | TOCS  | PS3    | PS2   | PS1           | PS0       |           | 0000 000-                     | 0000 000-                               |

| 06h, Unbanked | CPUSTA | —      | _      | STKAV | GLINTD | TO    | PD            | _         | _         | 11 11                         | 11 qq                                   |

| 07h, Unbanked | INTSTA | PEIF   | TOCKIF | T0IF  | INTF   | PEIE  | <b>T0CKIE</b> | TOIE      | INTE      | 0000 0000                     | 0000 0000                               |

| 0Bh, Unbanked |        |        |        |       |        |       |               | xxxx xxxx | uuuu uuuu |                               |                                         |

| 0Ch, Unbanked |        |        |        |       |        |       |               | xxxx xxxx | uuuu uuuu |                               |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', g - value depends on condition, Shaded cells are not used by Timer0. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

### 14.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLK-OUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation and SLEEP mode, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 14.1).

Under normal operation, the WDT must be cleared on a regular interval. This time is less the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

### 14.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms, (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a postscaler with a division ratio of up to 1:256 can be assigned to the WDT. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

### 14.3.2 CLEARING THE WDT AND POSTSCALER

The WDT and postscaler are cleared when:

- The device is in the reset state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the reset state.

### 14.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT postscaler) it may take several seconds before a WDT time-out occurs.

The WDT and postscaler is the Power-up Timer during the Power-on Reset sequence.

### 14.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the  $\overline{\text{TO}}$  bit is cleared (device is not reset). The CLRWDT instruction can be used to set the  $\overline{\text{TO}}$  bit. This allows the WDT to be a simple overflow timer. When in sleep, the WDT does not increment.

# TABLE 15-2: PIC17CXX INSTRUCTION SET

| Mnemonic, |       | Description                           |       | 16-bit Opcoo   | 16-bit Opcode |           |       |  |

|-----------|-------|---------------------------------------|-------|----------------|---------------|-----------|-------|--|

| Operands  |       |                                       |       | MSb            | LSb           | Affected  |       |  |

| BYTE-ORIE |       | TILE REGISTER OPERATIONS              | •     |                |               |           | •     |  |

| ADDWF     | f,d   | ADD WREG to f                         | 1     | 0000 111d ffff | ffff          | OV,C,DC,Z |       |  |

| ADDWFC    | f,d   | ADD WREG and Carry bit to f           | 1     | 0001 000d ffff | ffff          | OV,C,DC,Z |       |  |

| ANDWF     | f,d   | AND WREG with f                       | 1     | 0000 101d ffff | ffff          | Z         |       |  |

| CLRF      | f,s   | Clear f, or Clear f and Clear WREG    | 1     | 0010 100s ffff | ffff          | None      | 3     |  |

| COMF      | f,d   | Complement f                          | 1     | 0001 001d ffff | ffff          | Z         |       |  |

| CPFSEQ    | f     | Compare f with WREG, skip if f = WREG | 1 (2) | 0011 0001 ffff | ffff          | None      | 6,8   |  |

| CPFSGT    | f     | Compare f with WREG, skip if f > WREG | 1 (2) | 0011 0010 ffff | ffff          | None      | 2,6,8 |  |

| CPFSLT    | f     | Compare f with WREG, skip if f < WREG | 1 (2) | 0011 0000 ffff | ffff          | None      | 2,6,8 |  |

| DAW       | f,s   | Decimal Adjust WREG Register          | 1     | 0010 111s ffff | ffff          | C         | 3     |  |

| DECF      | f,d   | Decrement f                           | 1     | 0000 011d ffff | ffff          | OV,C,DC,Z |       |  |

| DECFSZ    | f,d   | Decrement f, skip if 0                | 1 (2) | 0001 011d ffff | ffff          | None      | 6,8   |  |

| DCFSNZ    | f,d   | Decrement f, skip if not 0            | 1 (2) | 0010 011d ffff | ffff          | None      | 6,8   |  |

| INCF      | f,d   | Increment f                           | 1     | 0001 010d ffff | ffff          | OV,C,DC,Z |       |  |

| INCFSZ    | f,d   | Increment f, skip if 0                | 1 (2) | 0001 111d ffff | ffff          | None      | 6,8   |  |

| INFSNZ    | f,d   | Increment f, skip if not 0            | 1 (2) | 0010 010d ffff | ffff          | None      | 6,8   |  |

| IORWF     | f,d   | Inclusive OR WREG with f              | 1     | 0000 100d ffff | ffff          | Z         |       |  |

| MOVFP     | f,p   | Move f to p                           | 1     | 011p pppp ffff | ffff          | None      |       |  |

| MOVPF     | p,f   | Move p to f                           | 1     | 010p pppp ffff | ffff          | Z         |       |  |

| MOVWF     | f     | Move WREG to f                        | 1     | 0000 0001 ffff | ffff          | None      |       |  |

| MULWF     | f     | Multiply WREG with f                  | 1     | 0011 0100 ffff | ffff          | None      | 9     |  |

| NEGW      | f,s   | Negate WREG                           | 1     | 0010 110s ffff | ffff          | OV,C,DC,Z | 1,3   |  |

| NOP       | —     | No Operation                          | 1     | 0000 0000 0000 | 0000          | None      |       |  |

| RLCF      | f,d   | Rotate left f through Carry           | 1     | 0001 101d ffff | ffff          | С         |       |  |

| RLNCF     | f,d   | Rotate left f (no carry)              | 1     | 0010 001d ffff | ffff          | None      |       |  |

| RRCF      | f,d   | Rotate right f through Carry          | 1     | 0001 100d ffff | ffff          | C         |       |  |

| RRNCF     | f,d   | Rotate right f (no carry)             | 1     | 0010 000d ffff | ffff          | None      |       |  |

| SETF      | f,s   | Set f                                 | 1     | 0010 101s ffff | ffff          | None      | 3     |  |

| SUBWF     | f,d   | Subtract WREG from f                  | 1     | 0000 010d ffff | ffff          | OV,C,DC,Z | 1     |  |

| SUBWFB    | f,d   | Subtract WREG from f with Borrow      | 1     | 0000 001d ffff | ffff          | OV,C,DC,Z | 1     |  |

| SWAPF     | f,d   | Swap f                                | 1     | 0001 110d ffff | ffff          | None      |       |  |

| TABLRD    | t,i,f | Table Read                            | 2 (3) | 1010 10ti ffff | ffff          | None      | 7     |  |

Legend: Refer to Table 15-1 for opcode field descriptions.

- Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- 5: Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

| CPFS         | SLT                                            |                                                                      | Compare f with WREG,<br>skip if f < WREG                                                                                                                                                                                                                                                            |         |  |  |  |  |  |

|--------------|------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

| Synta        | ax:                                            | [label]                                                              | CPFSLT f                                                                                                                                                                                                                                                                                            |         |  |  |  |  |  |

| Opera        | ands:                                          | $0 \le f \le 25$                                                     | $0 \le f \le 255$                                                                                                                                                                                                                                                                                   |         |  |  |  |  |  |

| Opera        | ation:                                         | skip if (f) <                                                        | (f) – (WREG),<br>skip if (f) < (WREG)<br>(unsigned comparison)                                                                                                                                                                                                                                      |         |  |  |  |  |  |

| Statu        | s Affected:                                    | None                                                                 |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

| Enco         | ding:                                          | 0011                                                                 | 0000 ffi                                                                                                                                                                                                                                                                                            | ff ffff |  |  |  |  |  |

| Desc         | ription:                                       | location 'f'<br>performing<br>If the conte<br>WREG, the<br>discarded | Compares the contents of data memory<br>location 'f' to the contents of WREG by<br>performing an unsigned subtraction.<br>If the contents of 'f' < the contents of<br>WREG, then the fetched instruction is<br>discarded and an NOP is executed<br>instead making this a two-cycle instruc-<br>tion |         |  |  |  |  |  |

| Word         | s:                                             | 1                                                                    |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

| Cycle        | es:                                            | 1 (2)                                                                |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

| Q Cy         | cle Activity:                                  |                                                                      |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

|              | Q1                                             | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                                  | Q4      |  |  |  |  |  |

|              | Decode                                         | Read<br>register 'f'                                                 | Execute                                                                                                                                                                                                                                                                                             | NOP     |  |  |  |  |  |

| lf skip      | o:                                             |                                                                      |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

| -            | Q1                                             | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                                  | Q4      |  |  |  |  |  |

|              | Forced NOP                                     | NOP                                                                  | Execute                                                                                                                                                                                                                                                                                             | NOP     |  |  |  |  |  |

| <u>Exarr</u> | nple:                                          | HERE<br>NLESS<br>LESS                                                | NLESS :                                                                                                                                                                                                                                                                                             |         |  |  |  |  |  |

| E            | Before Instru<br>PC<br>W                       |                                                                      | = Address (HERE)                                                                                                                                                                                                                                                                                    |         |  |  |  |  |  |

| F            | After Instruct<br>If REG<br>PC<br>If REG<br>PC | < W<br>= Ac<br>≥ W                                                   | REG;<br>ddress (LESS)<br>REG;<br>ddress (NLESS                                                                                                                                                                                                                                                      |         |  |  |  |  |  |

| DAW                 |                                                | Decimal                                                      | Adjust WRE                                                                                                                                                                                                        | G Register                                         |  |  |  |  |  |

|---------------------|------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| Syntax              | K:                                             | [ <i>label</i> ] D                                           | AW f,s                                                                                                                                                                                                            |                                                    |  |  |  |  |  |

| Opera               | nds:                                           | $0 \le f \le 25$<br>s $\in [0,1]$                            | 5                                                                                                                                                                                                                 |                                                    |  |  |  |  |  |

| Opera               | tion:                                          | <sup>-</sup> WREG<br>else                                    | If [WREG<3:0> >9] .OR. [DC = 1] then<br>WREG<3:0> + 6 $\rightarrow$ f<3:0>, s<3:0>;<br>else<br>WREG<3:0> $\rightarrow$ f<3:0>, s<3:0>;                                                                            |                                                    |  |  |  |  |  |

|                     |                                                | WREG                                                         | If [WREG<7:4> >9] .OR. [C = 1] then<br>WREG<7:4> + 6 → f<7:4>, s<7:4><br>else                                                                                                                                     |                                                    |  |  |  |  |  |

| Status              | Affected:                                      | C                                                            | $<7:4> \rightarrow f<7:$                                                                                                                                                                                          | 4>, S<7:4>                                         |  |  |  |  |  |

| Encod               |                                                | 0010                                                         | 111s ff                                                                                                                                                                                                           | ff ffff                                            |  |  |  |  |  |

| Descri              | U                                              |                                                              | ts the eight bi                                                                                                                                                                                                   |                                                    |  |  |  |  |  |

|                     |                                                | tion of two<br>BCD forma<br>packed BC<br>s = 0: Ro<br>m<br>W | WREG resulting from the earlier addi-<br>tion of two variables (each in packed<br>BCD format) and produces a correct<br>packed BCD result.<br>s = 0: Result is placed in Data<br>memory location 'f' and<br>WREG. |                                                    |  |  |  |  |  |

|                     |                                                |                                                              | s = 1: Result is placed in Data memory location 'f'.                                                                                                                                                              |                                                    |  |  |  |  |  |

| Words               | :                                              | 1                                                            |                                                                                                                                                                                                                   |                                                    |  |  |  |  |  |

| Cycles              | 8:                                             | 1                                                            |                                                                                                                                                                                                                   |                                                    |  |  |  |  |  |

| Q Cyc               | le Activity:                                   |                                                              |                                                                                                                                                                                                                   | •                                                  |  |  |  |  |  |

|                     | Q1<br>Decode                                   | Q2<br>Read                                                   | Q3<br>Execute                                                                                                                                                                                                     | Q4<br>Write                                        |  |  |  |  |  |

|                     | Decode                                         | register 'f'                                                 | Execute                                                                                                                                                                                                           | register 'f'<br>and other<br>specified<br>register |  |  |  |  |  |

| Exam                | ole1:                                          | DAW RE                                                       | G1, 0                                                                                                                                                                                                             |                                                    |  |  |  |  |  |

| B                   | <br>efore Instru                               | iction                                                       |                                                                                                                                                                                                                   |                                                    |  |  |  |  |  |

|                     | WREG<br>REG1<br>C<br>DC                        | = 0xA5<br>= ??<br>= 0<br>= 0                                 |                                                                                                                                                                                                                   |                                                    |  |  |  |  |  |

| Ai<br><u>Exam</u> t | fter Instruct<br>WREG<br>REG1<br>C<br>DC<br>DC | ion<br>= 0x05<br>= 0x05<br>= 1<br>= 0                        |                                                                                                                                                                                                                   |                                                    |  |  |  |  |  |

| В                   | efore Instru                                   |                                                              |                                                                                                                                                                                                                   |                                                    |  |  |  |  |  |

|                     | WREG<br>REG1<br>C                              | = 0xCE<br>= ??<br>= 0                                        |                                                                                                                                                                                                                   |                                                    |  |  |  |  |  |

| U             | -    | 0    |

|---------------|------|------|

| DC            | =    | 0    |

| After Instruc | tion |      |

| WREG          | =    | 0x24 |

| REG1          | =    | 0x24 |

| С             | =    | 1    |

| DC            | =    | 0    |

Applicable Devices 42 R42 42A 43 R43 44

# 19.0 PIC17CR42/42A/43/R43/44 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings †

| 5                                                                                                            |                                   |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Ambient temperature under bias                                                                               | 55 to +125°C                      |

| Storage temperature                                                                                          | 65°C to +150°C                    |

| Voltage on VDD with respect to Vss                                                                           | 0 to +7.5V                        |

| Voltage on MCLR with respect to Vss (Note 2)                                                                 | 0.6V to +14V                      |

| Voltage on RA2 and RA3 with respect to Vss                                                                   | 0.6V to +14V                      |

| Voltage on all other pins with respect to Vss                                                                | 0.6V to VDD + 0.6V                |

| Total power dissipation (Note 1)                                                                             | 1.0W                              |

| Maximum current out of Vss pin(s) - total                                                                    | 250 mA                            |

| Maximum current into VDD pin(s) - total                                                                      | 200 mA                            |

| Input clamp current, IiK (VI < 0 or VI > VDD)                                                                | ±20 mA                            |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                               | ±20 mA                            |

| Maximum output current sunk by any I/O pin (except RA2 and RA3)                                              | 35 mA                             |

| Maximum output current sunk by RA2 or RA3 pins                                                               |                                   |

| Maximum output current sourced by any I/O pin                                                                | 20 mA                             |

| Maximum current sunk by PORTA and PORTB (combined)                                                           | 150 mA                            |

| Maximum current sourced by PORTA and PORTB (combined)                                                        | 100 mA                            |

| Maximum current sunk by PORTC, PORTD and PORTE (combined)                                                    | 150 mA                            |

| Maximum current sourced by PORTC, PORTD and PORTE (combined)                                                 | 100 mA                            |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VG | OH) X IOH} + $\Sigma$ (VOL X IOL) |

|                                                                                                              |                                   |

**Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## Applicable Devices 42 R42 42A 43 R43 44

|           |       |                                                  | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature                              |      |          |       |                                                                                                             |  |  |  |

|-----------|-------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|----------|-------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| DC CHARA  | CTERI | STICS                                            | $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial and $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |      |          |       |                                                                                                             |  |  |  |

|           |       |                                                  | Operating voltage VDD range as described in Section 19.1                                                      |      |          |       |                                                                                                             |  |  |  |

| Parameter |       |                                                  |                                                                                                               |      |          |       |                                                                                                             |  |  |  |

| No.       | Sym   | Characteristic                                   | Min                                                                                                           | Тур† | Max      | Units | Conditions                                                                                                  |  |  |  |

|           |       | Output Low Voltage                               |                                                                                                               |      |          |       |                                                                                                             |  |  |  |

| D080      | VOL   | I/O ports (except RA2 and RA3)                   |                                                                                                               |      |          |       | IOL = VDD/1.250 mA                                                                                          |  |  |  |

|           |       |                                                  | _                                                                                                             | _    | 0.1Vdd   | V     | $4.5V \le VDD \le 6.0V$                                                                                     |  |  |  |

|           |       |                                                  | _                                                                                                             | _    | 0.1Vdd * | V     | VDD = 2.5V                                                                                                  |  |  |  |

| D081      |       | with TTL buffer                                  | -                                                                                                             | _    | 0.4      | V     | IOL = 6 mA, VDD = 4.5V<br>Note 6                                                                            |  |  |  |

| D082      |       | RA2 and RA3                                      | _                                                                                                             | _    | 3.0      | V     | IOL = 60.0  mA, VDD = 6.0 V                                                                                 |  |  |  |

| D083      |       | OSC2/CLKOUT                                      | _                                                                                                             | _    | 0.4      | V     | IOL = 1 mA, VDD = 4.5V                                                                                      |  |  |  |

| D084      |       | (RC and EC osc modes)                            | _                                                                                                             | _    | 0.1Vdd * | V     | IOL = VDD/5 mA                                                                                              |  |  |  |

|           |       |                                                  |                                                                                                               |      |          |       | (PIC17LC43/LC44 only)                                                                                       |  |  |  |

|           |       | Output High Voltage (Note 3)                     |                                                                                                               |      |          |       |                                                                                                             |  |  |  |

| D090      | Vон   | I/O ports (except RA2 and RA3)                   |                                                                                                               |      |          |       | Юн = -VDD/2.500 mA                                                                                          |  |  |  |

|           |       |                                                  | 0.9Vdd                                                                                                        | _    | _        | V     | $4.5V \le VDD \le 6.0V$                                                                                     |  |  |  |

|           |       |                                                  | 0.9Vdd *                                                                                                      | _    | -        | V     | VDD = 2.5V                                                                                                  |  |  |  |

| D091      |       | with TTL buffer                                  | 2.4                                                                                                           | _    | _        | V     | IOH = -6.0 mA, VDD=4.5V<br>Note 6                                                                           |  |  |  |

| D092      |       | RA2 and RA3                                      | -                                                                                                             | _    | 12       | V     | Pulled-up to externally applied voltage                                                                     |  |  |  |

| D093      |       | OSC2/CLKOUT                                      | 2.4                                                                                                           | _    | _        | v     | IOH = -5  mA,  VDD = 4.5  V                                                                                 |  |  |  |

| D094      |       | (RC and EC osc modes)                            | 0.9Vdd *                                                                                                      | _    | _        | V     | IOH = -VDD/5 mA                                                                                             |  |  |  |

|           |       | (,                                               |                                                                                                               |      |          |       | (PIC17LC43/LC44 only)                                                                                       |  |  |  |

|           |       | Capacitive Loading Specs<br>on Output Pins       |                                                                                                               |      |          |       |                                                                                                             |  |  |  |

| D100      | Cosc2 | OSC2/CLKOUT pin                                  | _                                                                                                             | _    | 25       | pF    | In EC or RC osc modes<br>when OSC2 pin is outputting<br>CLKOUT.<br>external clock is used to<br>drive OSC1. |  |  |  |

| D101      | Сю    | All I/O pins and OSC2<br>(in RC mode)            | _                                                                                                             | _    | 50       | pF    |                                                                                                             |  |  |  |

| D102      | CAD   | System Interface Bus<br>(PORTC, PORTD and PORTE) | -                                                                                                             | _    | 50       | pF    | In Microprocessor or<br>Extended Microcontroller<br>mode                                                    |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

## Applicable Devices 42 R42 42A 43 R43 44

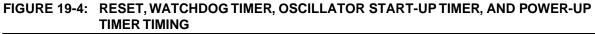

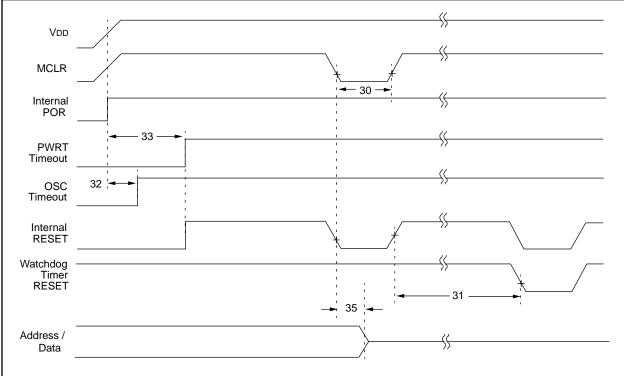

# TABLE 19-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                |                              | Min   | Тур†      | Max   | Units | Conditions         |

|------------------|----------|-----------------------------------------------|------------------------------|-------|-----------|-------|-------|--------------------|

| 30               | TmcL     | MCLR Pulse Width (low)                        |                              | 100 * | _         | _     | ns    | VDD = 5V           |

| 31               | Twdt     | Watchdog Timer Time-ou<br>(Prescale = 1)      | t Period                     | 5 *   | 12        | 25 *  | ms    | VDD = 5V           |

| 32               | Tost     | Oscillation Start-up Time                     | r Period                     | _     | 1024Tosc§ | _     | ms    | Tosc = OSC1 period |

| 33               | Tpwrt    | Power-up Timer Period                         |                              | 40 *  | 96        | 200 * | ms    | VDD = 5V           |

| 35               | TmcL2adl | MCLR to System Inter-<br>face bus (AD15:AD0>) | PIC17CR42/42A/<br>43/R43/44  | —     | _         | 100 * | ns    |                    |

|                  |          | invalid                                       | PIC17LCR42/<br>42A/43/R43/44 | —     | —         | 120 * | ns    |                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

§ This specification ensured by design.

Applicable Devices 42 R42 42A 43 R43 44

# 20.0 PIC17CR42/42A/43/R43/44 DC AND AC CHARACTERISTICS

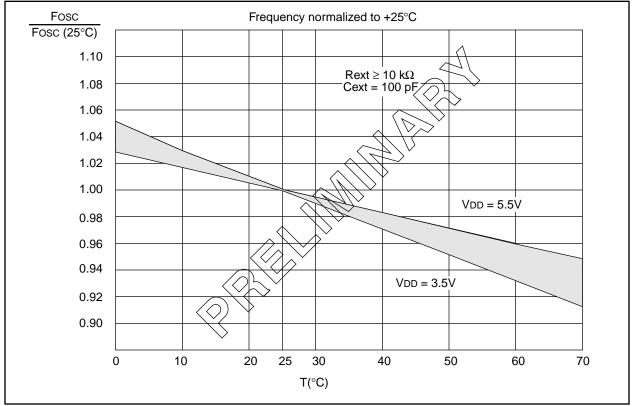

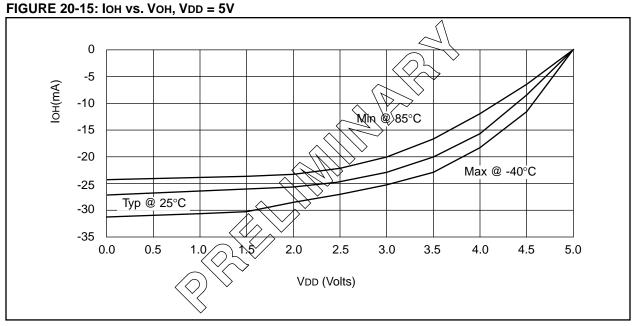

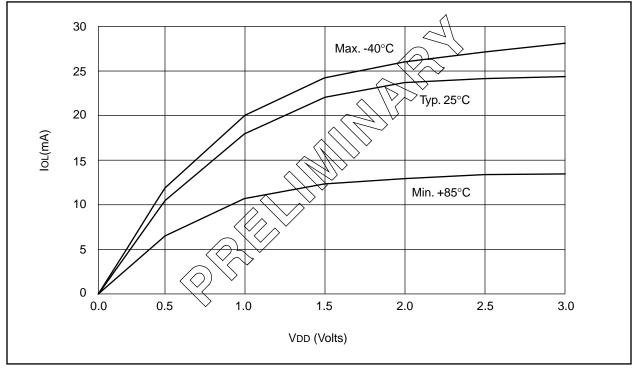

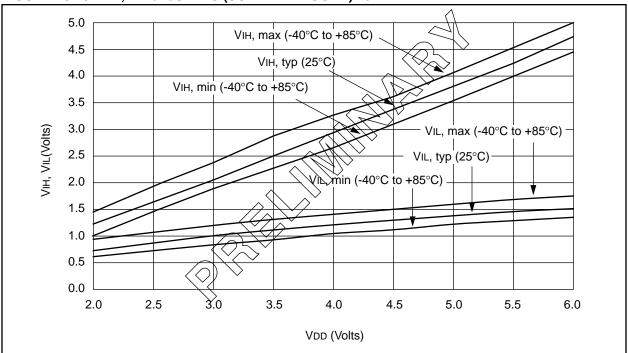

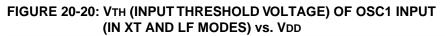

The graphs and tables provided in this section are for design guidance and are not tested nor guaranteed. In some graphs or tables the data presented is outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are ensured to operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

## TABLE 20-1: PIN CAPACITANCE PER PACKAGE TYPE

| Din Nama                               |            | Typical Capa | acitance (pF) |             |

|----------------------------------------|------------|--------------|---------------|-------------|

| Pin Name                               | 40-pin DIP | 44-pin PLCC  | 44-pin MQFP   | 44-pin TQFP |

| All pins, except MCLR,<br>VDD, and Vss | 10         | 10           | 10            | 10          |

| MCLR pin                               | 20         | 20           | 20            | 20          |

### FIGURE 20-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

# Applicable Devices 42 R42 42A 43 R43 44

FIGURE 20-16: IOL vs. VOL, VDD = 3V

## Applicable Devices 42 R42 42A 43 R43 44

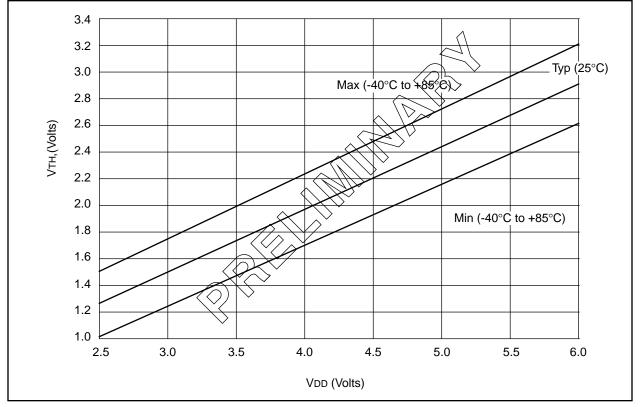

|        |        | Packag      | ge Group: Plasti | c MQFP |            |           |

|--------|--------|-------------|------------------|--------|------------|-----------|

|        |        | Millimeters |                  |        | Inches     |           |

| Symbol | Min    | Max         | Notes            | Min    | Мах        | Notes     |

| α      | 0°     | <b>7</b> °  |                  | 0°     | <b>7</b> ° |           |

| А      | 2.000  | 2.350       |                  | 0.078  | 0.093      |           |

| A1     | 0.050  | 0.250       |                  | 0.002  | 0.010      |           |

| A2     | 1.950  | 2.100       |                  | 0.768  | 0.083      |           |

| b      | 0.300  | 0.450       | Typical          | 0.011  | 0.018      | Typical   |

| С      | 0.150  | 0.180       |                  | 0.006  | 0.007      |           |

| D      | 12.950 | 13.450      |                  | 0.510  | 0.530      |           |

| D1     | 9.900  | 10.100      |                  | 0.390  | 0.398      |           |

| D3     | 8.000  | 8.000       | Reference        | 0.315  | 0.315      | Reference |

| E      | 12.950 | 13.450      |                  | 0.510  | 0.530      |           |

| E1     | 9.900  | 10.100      |                  | 0.390  | 0.398      |           |

| E3     | 8.000  | 8.000       | Reference        | 0.315  | 0.315      | Reference |

| е      | 0.800  | 0.800       |                  | 0.031  | 0.032      |           |

| L      | 0.730  | 1.030       |                  | 0.028  | 0.041      |           |

| Ν      | 44     | 44          |                  | 44     | 44         |           |

| CP     | 0.102  | _           |                  | 0.004  | _          |           |

# E.2 PIC16C5X Family of Devices

|              |      |         |           | 0           | Clock Mer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Memory  | Perip         | Peripherals | Features                                                                                                                |

|--------------|------|---------|-----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|-------------|-------------------------------------------------------------------------------------------------------------------------|

|              |      |         |           | CAN USE     | Course will a course of the co |         |               |             |                                                                                                                         |

|              |      | 1081    | to TOUSDI |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (s)     |               | ., N SOL    | 454                                                                                                                     |