Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 4KB (2K × 16)                                                              |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 232 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-25i-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.3 <u>Peripheral Interrupt Request Register</u> (PIR)

This register contains the individual flag bits for the peripheral interrupts.

**Note:** These bits will be set by the specified condition, even if the corresponding interrupt enable bit is cleared (interrupt disabled), or the GLINTD bit is set (all interrupts disabled). Before enabling an interrupt, the user may wish to clear the interrupt flag to ensure that the program does not immediately branch to the peripheral interrupt service routine.

## FIGURE 5-4: PIR REGISTER (ADDRESS: 16h, BANK 1)

|        | 0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 R-0                                                                                                                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBIF   |                                                                                                                                                                                                                                                                              |

| bit7   | bit0 W = Writable bit<br>-n = Value at POR reset                                                                                                                                                                                                                             |

| bit 7: | <b>RBIF</b> : PORTB Interrupt on Change Flag bit<br>1 = One of the PORTB inputs changed (Software must end the mismatch condition)<br>0 = None of the PORTB inputs have changed                                                                                              |

| bit 6: | TMR3IF: Timer3 Interrupt Flag bit<br>If Capture1 is enabled (CA1/PR3 = 1)<br>1 = Timer3 overflowed<br>0 = Timer3 did not overflow                                                                                                                                            |

|        | If Capture1 is disabled (CA1/ $\overline{PR3}$ = 0)<br>1 = Timer3 value has rolled over to 0000h from equalling the period register (PR3H:PR3L) value<br>0 = Timer3 value has not rolled over to 0000h from equalling the period register (PR3H:PR3L) value                  |

| bit 5: | <b>TMR2IF</b> : Timer2 Interrupt Flag bit<br>1 = Timer2 value has rolled over to 0000h from equalling the period register (PR2) value<br>0 = Timer2 value has not rolled over to 0000h from equalling the period register (PR2) value                                        |

| bit 4: | <b>TMR1IF</b> : Timer1 Interrupt Flag bit<br>If Timer1 is in 8-bit mode (T16 = 0)<br>1 = Timer1 value has rolled over to 0000h from equalling the period register (PR) value<br>0 = Timer1 value has not rolled over to 0000h from equalling the period register (PR2) value |

|        | If Timer1 is in 16-bit mode (T16 = 1)<br>1 = TMR1:TMR2 value has rolled over to 0000h from equalling the period register (PR1:PR2) value<br>0 = TMR1:TMR2 value has not rolled over to 0000h from equalling the period register (PR1:PR2) value                              |

| bit 3: | <b>CA2IF</b> : Capture2 Interrupt Flag bit<br>1 = Capture event occurred on RB1/CAP2 pin<br>0 = Capture event did not occur on RB1/CAP2 pin                                                                                                                                  |

| bit 2: | <b>CA1IF</b> : Capture1 Interrupt Flag bit<br>1 = Capture event occurred on RB0/CAP1 pin<br>0 = Capture event did not occur on RB0/CAP1 pin                                                                                                                                  |

| bit 1: | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = Transmit buffer is empty<br>0 = Transmit buffer is full                                                                                                                                                               |

| bit 0: | RCIF: USART Receive Interrupt Flag bit<br>1 = Receive buffer is full<br>0 = Receive buffer is empty                                                                                                                                                                          |

#### 6.2.2.1 ALU STATUS REGISTER (ALUSTA)

The ALUSTA register contains the status bits of the Arithmetic and Logic Unit and the mode control bits for the indirect addressing register.

As with all the other registers, the ALUSTA register can be the destination for any instruction. If the ALUSTA register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the ALUSTA register as destination may be different than intended.

For example, CLRF ALUSTA will clear the upper four bits and set the Z bit. This leaves the ALUSTA register as 0000u1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions be used to alter the ALUSTA register because these instructions do not affect any status bit. To see how other instructions affect the status bits, see the "Instruction Set Summary."

| Note | 1: The C and DC bits operate as a borrow<br>out bit in subtraction. See the SUBLW and<br>SUBWF instructions for examples. |

|------|---------------------------------------------------------------------------------------------------------------------------|

| Note | 2: The overflow bit will be set if the 2's com-<br>plement result exceeds +127 or is less<br>than -128.                   |

Arithmetic and Logic Unit (ALU) is capable of carrying out arithmetic or logical operations on two operands or a single operand. All single operand instructions operate either on the WREG register or a file register. For two operand instructions, one of the operands is the WREG register and the other one is either a file register or an 8-bit immediate constant.

| FS3      | FS2                                  | FS1                                                                | FS0                                                  | OV                                                      | Z                                   | DC                       | С          | R = Readable bit                                                  |

|----------|--------------------------------------|--------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|-------------------------------------|--------------------------|------------|-------------------------------------------------------------------|

| bit7     | 1                                    | 1                                                                  |                                                      |                                                         |                                     | I                        | bit0       | W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)      |

| bit 7-6: | 01 = Pos                             | FSR1 Mo<br>t auto-dect<br>t auto-incre<br>t value de               | rement FS<br>ement FSI                               | R1 value<br>R1 value                                    |                                     |                          |            |                                                                   |

| bit 5-4: | 01 = Pos                             | FSR0 Mo<br>t auto-deci<br>t auto-incre<br>0 value de               | rement FS<br>ement FSI                               | R0 value<br>R0 value                                    |                                     |                          |            |                                                                   |

| bit 3:   | which cau<br>1 = Overfl              | s used for<br>uses the si                                          | gn bit (bit7<br>ed for sign                          | ') to chang                                             |                                     |                          |            | overflow of the 7-bit magnitude,                                  |

| bit 2:   |                                      | esult of an                                                        |                                                      |                                                         | peration is operation is            |                          |            |                                                                   |

| bit 1:   | For ADDW<br>1 = A carr $0 = No ca$   | •                                                                  | LW instruc<br>the 4th lo<br>m the 4th                | w order bi<br>low order                                 | t of the res<br>bit of the re<br>I. |                          | d          |                                                                   |

| bit 0:   | 1 = A carr<br>Note that<br>(RRCF, RL | F and ADD<br>y-out from<br>a subtrac<br>CF) instru-<br>rry-out fro | the most<br>tion is exe<br>ctions, this<br>m the mos | significant<br>cuted by a<br>bit is load<br>t significa | ded with eit<br>nt bit of the       | two's com<br>her the hig | plement of | the second operand. For rotate<br>der bit of the source register. |

#### FIGURE 6-7: ALUSTA REGISTER (ADDRESS: 04h, UNBANKED)

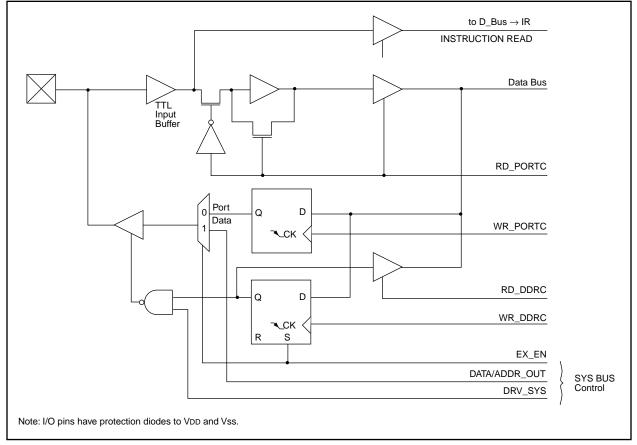

### 9.3 PORTC and DDRC Registers

PORTC is an 8-bit bi-directional port. The corresponding data direction register is DDRC. A '1' in DDRC configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTC reads the status of the pins, whereas writing to it will write to the port latch. PORTC is multiplexed with the system bus. When operating as the system bus, PORTC is the low order byte of the address/data bus (AD7:AD0). The timing for the system bus is shown in the Electrical Characteristics section.

**Note:** This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-2 shows the instruction sequence to initialize PORTC. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-2: INITIALIZING PORTC

| 1     | ;             | Select Bank 1                                        |

|-------|---------------|------------------------------------------------------|

| PORTC | ;             | Initialize PORTC data                                |

|       | ;             | latches before setting                               |

|       | ;             | the data direction                                   |

|       | ;             | register                                             |

| 0xCF  | ;             | Value used to initialize                             |

|       | ;             | data direction                                       |

| DDRC  | ;             | Set RC<3:0> as inputs                                |

|       | ;             | RC<5:4> as outputs                                   |

|       | ;             | RC<7:6> as inputs                                    |

|       | PORTC<br>0xCF | PORTC ;<br>;<br>;<br>;<br>;<br>0xCF ;<br>DDRC ;<br>; |

#### FIGURE 9-6: BLOCK DIAGRAM OF RC<7:0> PORT PINS

#### 9.5 I/O Programming Considerations

#### 9.5.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. For example, the BCF and BSF instructions read the register into the CPU, execute the bit operation, and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g. bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading a port reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (BCF, BSF, BTG, etc.) on a port, the value of the port pins is read, the desired operation is performed with this value, and the value is then written to the port latch.

Example 9-5 shows the effect of two sequential read-modify-write instructions on an I/O port.

#### EXAMPLE 9-5: READ MODIFY WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORT settings: PORTB<7:4> Inputs PORTB<3:0> Outputs ; ; PORTB<7:6> have pull-ups and are ; not connected to other circuitry ; PORT latch PORT pins ; ; \_\_\_\_\_ \_\_\_\_\_ ; PORTB, 7 BCF 01pp pppp 11pp pppp BCF PORTB, 6 10pp pppp 11pp pppp ; BCF DDRB, 7 10pp pppp 11pp pppp BCF DDRB, 6 10pp pppp 10pp pppp ; ; Note that the user may have expected the ; pin values to be 00pp pppp. The 2nd BCF ; caused RB7 to be latched as the pin value ; (High).

Note: A pin actively outputting a Low or High should not be driven from external devices in order to change the level on this pin (i.e. "wired-or", "wired-and"). The resulting high output currents may damage the device.

#### 9.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 9-9). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before executing the instruction that reads the values on that I/O port. Otherwise, the previous state of that pin may be read into the CPU rather than the "new" state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 9-9: SUCCESSIVE I/O OPERATION

| Instruction<br>fetched  | Q1  Q2  Q3  Q4<br>PC<br>MOVWF PORTB<br>write to<br>PORTB | PC + 1                           | Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4<br><u>PC+2</u> <u>PC+3</u><br>NOP NOP | Note:<br>This example shows a write to PORTB<br>followed by a read from PORTB.<br>Note that:<br>data setup time = (0.25 Tcy - TPD)<br>where TcY = instruction cycle.<br>TPD = propagation delay |

|-------------------------|----------------------------------------------------------|----------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB7:RB0                 |                                                          |                                  | X                                                             | Therefore, at higher clock<br>frequencies, a write followed by a                                                                                                                                |

|                         |                                                          |                                  | Port pin<br>sampled here                                      | read may be problematic.                                                                                                                                                                        |

| Instruction<br>executed |                                                          | MOVWF PORTB<br>write to<br>PORTB | MOVF PORTB,W NOP                                              |                                                                                                                                                                                                 |

|                         |                                                          |                                  | · · · · ·                                                     |                                                                                                                                                                                                 |

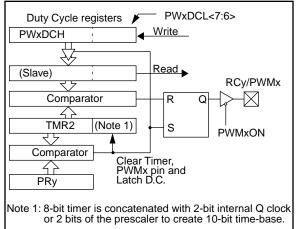

#### 12.1.3 USING PULSE WIDTH MODULATION (PWM) OUTPUTS WITH TMR1 AND TMR2

Two high speed pulse width modulation (PWM) outputs are provided. The PWM1 output uses Timer1 as its time-base, while PWM2 may be software configured to use either Timer1 or Timer2 as the time-base. The PWM outputs are on the RB2/PWM1 and RB3/PWM2 pins.

Each PWM output has a maximum resolution of 10-bits. At 10-bit resolution, the PWM output frequency is 24.4 kHz (@ 25 MHz clock) and at 8-bit resolution the PWM output frequency is 97.7 kHz. The duty cycle of the output can vary from 0% to 100%.

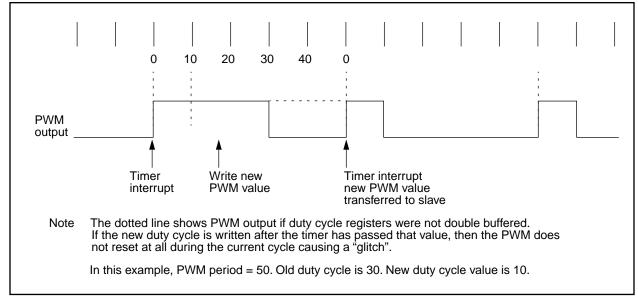

Figure 12-5 shows a simplified block diagram of the PWM module. The duty cycle register is double buffered for glitch free operation. Figure 12-6 shows how a glitch could occur if the duty cycle registers were not double buffered.

The user needs to set the PWM1ON bit (TCON2<4>) to enable the PWM1 output. When the PWM1ON bit is set, the RB2/PWM1 pin is configured as PWM1 output and forced as an output irrespective of the data direction bit (DDRB<2>). When the PWM1ON bit is clear, the pin behaves as a port pin and its direction is controlled by its data direction bit (DDRB<2>). Similarly, the PWM2ON (TCON2<5>) bit controls the configuration of the RB3/PWM2 pin.

#### FIGURE 12-5: SIMPLIFIED PWM BLOCK DIAGRAM

#### FIGURE 12-6: PWM OUTPUT

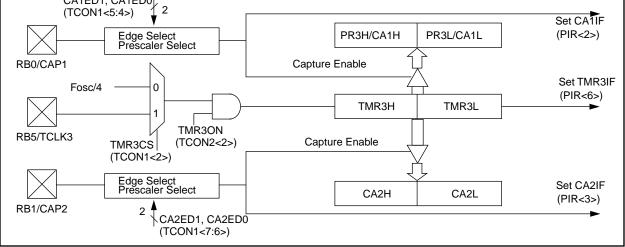

#### 12.2.2 DUAL CAPTURE REGISTER MODE

This mode is selected by setting CA1/PR3. A block diagram is shown in Figure 12-8. In this mode, TMR3 runs without a period register and increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt Flag (TMR3IF) is set on this roll over. The TMR3IF bit must be cleared in software.

Registers PR3H/CA1H and PR3L/CA1L make a 16-bit capture register (Capture1). It captures events on pin RB0/CAP1. Capture mode is configured by the CA1ED1 and CA1ED0 bits. Capture1 Interrupt Flag bit (CA1IF) is set on the capture event. The corresponding interrupt mask bit is CA1IE. The Capture1 Overflow Status bit is CA1OVF.

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the TMR3 value to the capture register which protects the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The operation of the Capture1 feature is identical to Capture2 (as described in Section 12.2.1).

#### TABLE 12-5: REGISTERS ASSOCIATED WITH CAPTURE

| Address       | Name      | Bit 7     | Bit 6                                                          | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|-----------|-----------|----------------------------------------------------------------|--------|--------|---------|--------|--------|--------|-------------------------------|-----------------------------------------|

| 16h, Bank 3   | TCON1     | CA2ED1    | CA2ED0                                                         | CA1ED1 | CA1ED0 | T16     | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                               |

| 17h, Bank 3   | TCON2     | CA2OVF    | CA10VF                                                         | PWM2ON | PWM10N | CA1/PR3 | TMR3ON | TMR2ON | TMR10N | 0000 0000                     | 0000 0000                               |

| 12h, Bank 2   | TMR3L     | TMR3 reg  | ister; low by                                                  | /te    |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 13h, Bank 2   | TMR3H     | TMR3 reg  | TMR3 register; high byte                                       |        |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 16h, Bank 1   | PIR       | RBIF      | TMR3IF                                                         | TMR2IF | TMR1IF | CA2IF   | CA1IF  | TXIF   | RCIF   | 0000 0010                     | 0000 0010                               |

| 17h, Bank 1   | PIE       | RBIE      | TMR3IE                                                         | TMR2IE | TMR1IE | CA2IE   | CA1IE  | TXIE   | RCIE   | 0000 0000                     | 0000 0000                               |

| 07h, Unbanked | INTSTA    | PEIF      | T0CKIF                                                         | T0IF   | INTF   | PEIE    | T0CKIE | T0IE   | INTE   | 0000 0000                     | 0000 0000                               |

| 06h, Unbanked | CPUSTA    | —         | _                                                              | STKAV  | GLINTD | TO      | PD     | —      | —      | 11 11                         | 11 qq                                   |

| 16h, Bank 2   | PR3L/CA1L | Timer3 pe | Timer3 period register, low byte/capture1 register, low byte   |        |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 2   | PR3H/CA1H | Timer3 pe | Timer3 period register, high byte/capture1 register, high byte |        |        |         |        |        |        |                               | uuuu uuuu                               |

| 14h, Bank 3   | CA2L      | Capture2  | Capture2 low byte                                              |        |        |         |        |        |        |                               | uuuu uuuu                               |

| 15h, Bank 3   | CA2H      | Capture2  | high byte                                                      |        |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition, shaded cells are not used by Capture.

Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset.

#### 13.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. Table 13-1 shows the formula for computation of the baud rate for different USART modes. These only apply when the USART is in synchronous master mode (internal clock) and asynchronous mode.

Given the desired baud rate and Fosc, the nearest integer value between 0 and 255 can be calculated using the formula below. The error in baud rate can then be determined.

#### TABLE 13-1: BAUD RATE FORMULA

| SYNC | Mode         | Baud Rate      |

|------|--------------|----------------|

| 0    | Asynchronous | Fosc/(64(X+1)) |

| 1    | Synchronous  | Fosc/(4(X+1))  |

X = value in SPBRG (0 to 255)

Example 13-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 SYNC = 0

#### EXAMPLE 13-1: CALCULATING BAUD RATE ERROR

Desired Baud rate=Fosc / (64 (X + 1))

$9600 = \frac{16000000}{(64 (X + 1))}$

X = 25.042 = 25

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

- Error = <u>(Calculated Baud Rate Desired Baud Rate)</u> Desired Baud Rate

- = (9615 9600) / 9600

- = 0.16%

Writing a new value to the SPBRG, causes the BRG timer to be reset (or cleared), this ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

### TABLE 13-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address                                        | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9   | SREN  | CREN  | _     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9   | TXEN  | SYNC  | —     | —     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |       |       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used by the Baud Rate Generator. $Note 1: Other (non power-up) resets include: external reset through <math>\overline{MCLR}$  and Watchdog Timer Reset.

#### 13.2 USART Asynchronous Mode

In this mode, the USART uses standard nonreturn-to-zero (NRZ) format (one start bit, eight or nine data bits, and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock x64 of the bit shift rate. Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

The asynchronous mode is selected by clearing the SYNC bit (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

#### 13.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 13-3. The heart of the transmitter is the transmit shift register (TSR). The shift register obtains its data from the read/write transmit buffer (TXREG). TXREG is loaded with data in software. The TSR is not loaded until the stop bit has been transmitted from the previous load. As soon as the stop bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one TCY at the end of the current BRG cycle), the TXREG is empty and an interrupt bit, TXIF (PIR<1>) is set. This interrupt can be enabled or disabled by the TXIE bit (PIE<1>). TXIF will be set regardless of TXIE and cannot be reset in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of the TXREG, the TRMT (TXSTA<1>) bit shows the status of the TSR. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty.

| Note: | The TSR is not mapped in data memory, |

|-------|---------------------------------------|

|       | so it is not available to the user.   |

Transmission enabled setting is by the TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 13-5). The transmission can also be started by first loading TXREG and then setting TXEN. Normally when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to TSR resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 13-6). Clearing TXEN during a transmission will cause the transmission to be aborted. This will reset the transmitter and the RA5/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty).

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. Load data to the TXREG register.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 7. Enable the transmission by setting TXEN (starts transmission).

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the opposite order.

Note: To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

# PIC17C4X

| NEGV        | v                            | Negate W                                                                                                                                                                                        |                                                                                                                                  |  |  |  |  |  |  |  |

|-------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax      | x:                           | [ <i>label</i> ] NEGW f,s                                                                                                                                                                       |                                                                                                                                  |  |  |  |  |  |  |  |

| Opera       | nds:                         | $\begin{array}{l} 0 \leq F \leq 255 \\ s \in \ [0,1] \end{array}$                                                                                                                               |                                                                                                                                  |  |  |  |  |  |  |  |

| Opera       | tion:                        | $  \overline{\text{WREG}} + 1 \rightarrow (f);                                   $                                                                                                              |                                                                                                                                  |  |  |  |  |  |  |  |

| Status      | Affected:                    | OV, C, DC, Z                                                                                                                                                                                    |                                                                                                                                  |  |  |  |  |  |  |  |

| Encod       | ling:                        | 0010 110s ffff ffff                                                                                                                                                                             |                                                                                                                                  |  |  |  |  |  |  |  |

| Descri      | iption:                      | WREG is negated using two's comple-<br>ment. If 's' is 0 the result is placed in<br>WREG and data memory location 'f'. If<br>'s' is 1 the result is placed only in data<br>memory location 'f'. | ment. If 's' is 0 the result is placed in<br>WREG and data memory location 'f'. If<br>'s' is 1 the result is placed only in data |  |  |  |  |  |  |  |

| Words       | :                            | 1                                                                                                                                                                                               | 1                                                                                                                                |  |  |  |  |  |  |  |

| Cycles      | S:                           | 1                                                                                                                                                                                               |                                                                                                                                  |  |  |  |  |  |  |  |

| Q Cyc       | le Activity:                 |                                                                                                                                                                                                 |                                                                                                                                  |  |  |  |  |  |  |  |

|             | Q1                           | Q2 Q3 Q4                                                                                                                                                                                        | _                                                                                                                                |  |  |  |  |  |  |  |

|             | Decode                       | Read Execute Write<br>register 'f' and other<br>specified<br>register                                                                                                                           |                                                                                                                                  |  |  |  |  |  |  |  |

| <u>Exam</u> | ole:                         | NEGW REG, 0                                                                                                                                                                                     |                                                                                                                                  |  |  |  |  |  |  |  |

| B           | efore Instru<br>WREG<br>REG  | ction<br>= 0011 1010 [0x3A],<br>= 1010 1011 [0xAB]                                                                                                                                              |                                                                                                                                  |  |  |  |  |  |  |  |

| A           | fter Instruct<br>WREG<br>REG | ion<br>= 1100 0111 [0xC6]<br>= 1100 0111 [0xC6]                                                                                                                                                 |                                                                                                                                  |  |  |  |  |  |  |  |

| NOF  | 0              | No Opera   | ation   |     |     |      |

|------|----------------|------------|---------|-----|-----|------|

| Synt | ax:            | [ label ]  | NOP     |     |     |      |

| Ope  | rands:         | None       |         |     |     |      |

| Ope  | ration:        | No opera   | tion    |     |     |      |

| Stat | us Affected:   | None       |         |     |     |      |

| Enco | oding:         | 0000       | 0000    | 000 | 0   | 0000 |

| Des  | cription:      | No operati | on.     |     |     |      |

| Wor  | ds:            | 1          |         |     |     |      |

| Cycl | es:            | 1          |         |     |     |      |

| QC   | ycle Activity: |            |         |     |     |      |

|      | Q1             | Q2         | Q3      |     | Q4  |      |

|      | Decode         | NOP        | Execute |     | NOP |      |

|      |                |            |         |     |     |      |

Example:

None.

| Droduct                                                                                                                                               | ** MDI ADTM                             |                                   | MD-Drivo/Mov      |                              | *** DICMACTED®/                                                                                                                                                                                                                     |                                                                |                                                                                                                                                                             |                                                                                                                                                                                                                               | DIC CTADT® DI         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|-------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|                                                                                                                                                       | Integrated                              | Compiler                          | Applications      | Explorer/Edition             | PICMASTER-CE                                                                                                                                                                                                                        | Low-Cost                                                       |                                                                                                                                                                             | Ultra Low-Cost                                                                                                                                                                                                                | Low-Cost              |

|                                                                                                                                                       | Development<br>Environment              |                                   | Code<br>Generator | Fuzzy Logic<br>Dev. Tool     | In-Circuit<br>Emulator                                                                                                                                                                                                              | In-Circuit<br>Emulator                                         | Microchip<br>Programmer                                                                                                                                                     | Dev. Kit                                                                                                                                                                                                                      | Universal<br>Dev. Kit |

| PIC12C508, 509                                                                                                                                        | SW007002                                | SW006005                          |                   | I                            | EM167015/<br>EM167101                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | 1                                                                                                                                                                                                                             | DV003001              |

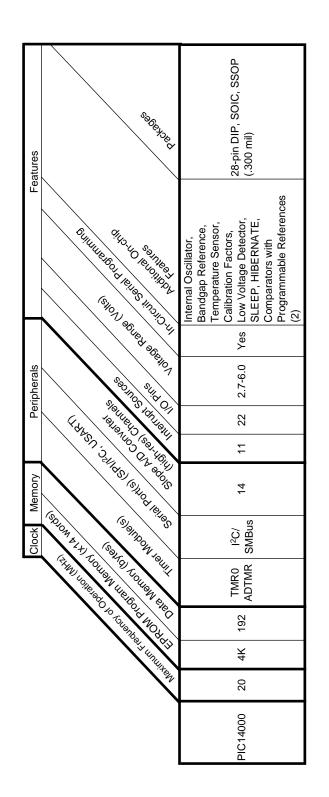

| PIC14000                                                                                                                                              | SW007002                                | SW006005                          |                   | I                            | EM147001/<br>EM147101                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | I                                                                                                                                                                                                                             | DV003001              |

| PIC16C52, 54, 54A,<br>55, 56, 57, 58A                                                                                                                 | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167015/<br>EM167101                                                                                                                                                                                                               | EM167201                                                       | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                      | DV003001              |

| PIC16C554, 556, 558                                                                                                                                   | SW007002                                | SW006005                          |                   | DV005001/<br>DV005002        | EM167033/<br>EM167113                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | I                                                                                                                                                                                                                             | DV003001              |

| PIC16C61                                                                                                                                              | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167021/<br>N/A                                                                                                                                                                                                                    | EM167205                                                       | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                      | DV003001              |

| PIC16C62, 62A,<br>64, 64A                                                                                                                             | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167025/<br>EM167103                                                                                                                                                                                                               | EM167203                                                       | DV007003                                                                                                                                                                    | DV162002                                                                                                                                                                                                                      | DV003001              |

| PIC16C620, 621, 622                                                                                                                                   | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167023/<br>EM167109                                                                                                                                                                                                               | EM167202                                                       | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                      | DV003001              |

| PIC16C63, 65, 65A,<br>73, 73A, 74, 74A                                                                                                                | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167025/<br>EM167103                                                                                                                                                                                                               | EM167204                                                       | DV007003                                                                                                                                                                    | DV162002                                                                                                                                                                                                                      | DV003001              |

| PIC16C642, 662*                                                                                                                                       | SW007002                                | SW006005                          |                   | I                            | EM167035/<br>EM167105                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | DV162002                                                                                                                                                                                                                      | DV003001              |

| PIC16C71                                                                                                                                              | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167027/<br>EM167105                                                                                                                                                                                                               | EM167205                                                       | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                      | DV003001              |

| PIC16C710, 711                                                                                                                                        | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167027/<br>EM167105                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                      | DV003001              |

| PIC16C72                                                                                                                                              | SW007002                                | SW006005                          | SW006006          | I                            | EM167025/<br>EM167103                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | DV162002                                                                                                                                                                                                                      | DV003001              |

| PIC16F83                                                                                                                                              | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167029/<br>EM167107                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                      | DV003001              |

| PIC16C84                                                                                                                                              | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167029/<br>EM167107                                                                                                                                                                                                               | EM167206                                                       | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                      | DV003001              |

| PIC16F84                                                                                                                                              | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167029/<br>EM167107                                                                                                                                                                                                               |                                                                | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                      | DV003001              |

| PIC16C923, 924*                                                                                                                                       | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167031/<br>EM167111                                                                                                                                                                                                               |                                                                | DV007003                                                                                                                                                                    | I                                                                                                                                                                                                                             | DV003001              |

| PIC17C42,<br>42A, 43, 44                                                                                                                              | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM177007/<br>EM177107                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | I                                                                                                                                                                                                                             | DV003001              |

| *Contact Microchip Technology for availability date<br>**MPLAB Integrated Development Environment includes MPLAB-SIM Simulator and<br>MPASM Assembler | innology for avails<br>velopment Enviro | ability date<br>inment includes   | s MPLAB-SIM Sii   | mulator and                  | ***All PICMASTER and PICMASTER-CE ordering part numbers above include<br>PRO MATE II programmer<br>****PRO MATE socket modules are ordered separately. See development systems<br>ordering guide for specific ordering part numbers | and PICMAST<br>rogrammer<br>at modules are<br>or specific orde | II PICMASTER and PICMASTER-CE ordering par<br>PRO MATE II programmer<br>RO MATE socket modules are ordered separately.<br>ordering guide for specific ordering part numbers | ***All PICMASTER and PICMASTER-CE ordering part numbers above include<br>PRO MATE II programmer **PRO MATE socket modules are ordered separately. See development system<br>ordering guide for specific ordering part numbers | lude<br>stems         |

| Product                                                                                                                                               | TRUEGAUGI                               | <b>TRUEGAUGE®</b> Development Kit |                   | <b>SEEVAL® Designers Kit</b> | Hopping Code Security Programmer Kit                                                                                                                                                                                                | Security Prog                                                  |                                                                                                                                                                             | Hopping Code Security Eval/Demo Kit                                                                                                                                                                                           | ity Eval/Demo Kit     |

| All 2 wire and 3 wire<br>Serial EEPROM's                                                                                                              |                                         | N/A                               |                   | DV243001                     |                                                                                                                                                                                                                                     | N/A                                                            |                                                                                                                                                                             | N/A                                                                                                                                                                                                                           |                       |

| MTA11200B                                                                                                                                             |                                         | DV114001                          |                   | N/A                          |                                                                                                                                                                                                                                     | N/A                                                            |                                                                                                                                                                             | N/A                                                                                                                                                                                                                           |                       |

| HCS200, 300, 301 *                                                                                                                                    |                                         | N/A                               | _                 | N/A                          | -                                                                                                                                                                                                                                   | PG306001                                                       |                                                                                                                                                                             | DM303001                                                                                                                                                                                                                      | 001                   |

## TABLE 16-1: DEVELOPMENT TOOLS FROM MICROCHIP

PIC17C4X

#### Applicable Devices 42 R42 42A 43 R43 44

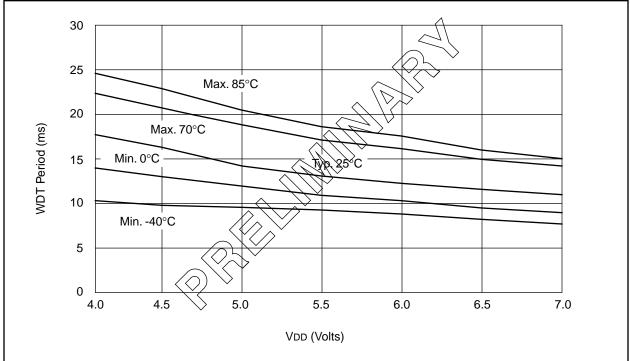

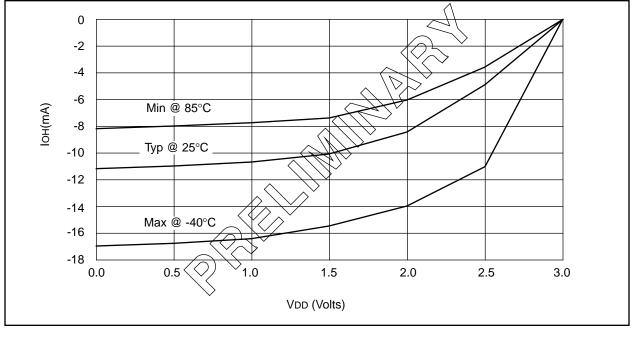

#### 19.3 DC CHARACTERISTICS:

#### PIC17CR42/42A/43/R43/44-16 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-25 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-33 (Commercial, Industrial) PIC17LCR42/42A/43/R43/44-08 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated) Operating temperature

#### DC CHARACTERISTICS

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and 0°C  $\leq$  TA  $\leq$  +70°C for commercial

| $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial<br>Operating voltage VDD range as described in Section 19.1 |       |                                |             |           |            |         |                                                                                 |

|-------------------------------------------------------------------------------------------------------------------|-------|--------------------------------|-------------|-----------|------------|---------|---------------------------------------------------------------------------------|

| Demonst                                                                                                           |       | 1                              | Operating v | oitage VI | טט range a | is desc | cribed in Section 19.1                                                          |

| Parameter<br>No.                                                                                                  | Sym   | Characteristic                 | Min         | Тур†      | Мах        | Units   | Conditions                                                                      |

|                                                                                                                   |       | Input Low Voltage              |             |           |            |         |                                                                                 |

|                                                                                                                   | VIL   | I/O ports                      |             |           |            |         |                                                                                 |

| D030                                                                                                              |       | with TTL buffer                | Vss         | -         | 0.8        | V       | $4.5V \le VDD \le 5.5V$                                                         |

|                                                                                                                   |       |                                | Vss         | -         | 0.2Vdd     | V       | $2.5V \le VDD \le 4.5V$                                                         |

| D031                                                                                                              |       | with Schmitt Trigger buffer    | Vss         | -         | 0.2Vdd     | V       |                                                                                 |

| D032                                                                                                              |       | MCLR, OSC1 (in EC and RC mode) | Vss         | -         | 0.2Vdd     | V       | Note1                                                                           |

| D033                                                                                                              |       | OSC1 (in XT, and LF mode)      | -           | 0.5Vdd    | _          | V       |                                                                                 |

|                                                                                                                   |       | Input High Voltage             |             |           |            |         |                                                                                 |

|                                                                                                                   | VIH   | I/O ports                      |             |           |            |         |                                                                                 |

| D040                                                                                                              |       | with TTL buffer                | 2.0         | -         | Vdd        | V       | $4.5V \le VDD \le 5.5V$                                                         |

|                                                                                                                   |       |                                | 1+0.2VDD    | -         | Vdd        | V       | $2.5V \le VDD \le 4.5V$                                                         |

| D041                                                                                                              |       | with Schmitt Trigger buffer    | 0.8Vdd      | -         | Vdd        | V       |                                                                                 |

| D042                                                                                                              |       | MCLR                           | 0.8Vdd      | _         | Vdd        | V       | Note1                                                                           |

| D043                                                                                                              |       | OSC1 (XT, and LF mode)         | -           | 0.5Vdd    | _          | V       |                                                                                 |

| D050                                                                                                              | VHYS  | Hysteresis of                  | 0.15Vdd *   | -         | -          | V       |                                                                                 |

|                                                                                                                   |       | Schmitt Trigger inputs         |             |           |            |         |                                                                                 |

|                                                                                                                   |       | Input Leakage Current          |             |           |            |         |                                                                                 |

| Daga                                                                                                              |       | (Notes 2, 3)                   |             |           |            |         |                                                                                 |

| D060                                                                                                              | lı∟   | I/O ports (except RA2, RA3)    | _           | _         | ±1         | μΑ      | Vss ≤ VPIN ≤ VDD,<br>I/O Pin at hi-impedance<br>PORTB weak pull-ups<br>disabled |

| D061                                                                                                              |       | MCLR                           | -           | -         | <u>+2</u>  | μA      | VPIN = Vss or VPIN = VDD                                                        |

| D062                                                                                                              |       | RA2, RA3                       |             |           | ±2         | μA      | $Vss \le Vra2$ , $Vra3 \le 12V$                                                 |

| D063                                                                                                              |       | OSC1, TEST (EC, RC modes)      | -           | -         | ±1         | μA      | $Vss \le VPIN \le VDD$                                                          |

| D063B                                                                                                             |       | OSC1, TEST (XT, LF modes)      | -           | -         | VPIN       | μA      | $R_F \ge 1 M\Omega$ , see Figure 14.2                                           |

| D064                                                                                                              |       | MCLR                           | -           | -         | 10         | μA      | VMCLR = VPP = 12V<br>(when not programming)                                     |

| D070                                                                                                              | IPURB | PORTB weak pull-up current     | 60          | 200       | 400        | μA      | VPIN = VSS, $\overline{\text{RBPU}} = 0$<br>4.5V $\leq$ VDD $\leq$ 6.0V         |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

Negative current is defined as coming out of the pin.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

## Applicable Devices 42 R42 42A 43 R43 44

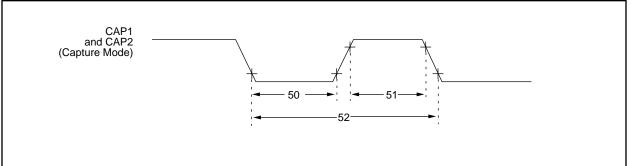

### FIGURE 19-7: CAPTURE TIMINGS

#### TABLE 19-7: CAPTURE REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                        | Min                | Тур† | Max | Units | Conditions                      |

|------------------|------|---------------------------------------|--------------------|------|-----|-------|---------------------------------|

| 50               | TccL | Capture1 and Capture2 input low time  | 10 *               | —    | —   | ns    |                                 |

| 51               | TccH | Capture1 and Capture2 input high time | 10 *               | —    |     | ns    |                                 |

| 52               | TccP | Capture1 and Capture2 input period    | <u>2Tcy</u> §<br>N | _    | _   | ns    | N = prescale value<br>(4 or 16) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

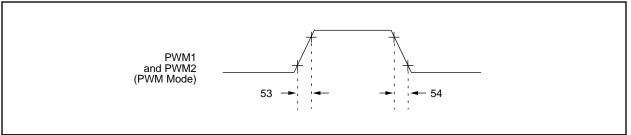

#### FIGURE 19-8: PWM TIMINGS

#### TABLE 19-8: PWM REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                           | Min | Тур† | Max   | Units | Conditions |

|------------------|------|------------------------------------------|-----|------|-------|-------|------------|

| 53               | TccR | PWM1 and PWM2 output rise time           |     | 10 * | 35 *§ | ns    |            |

| 54               | TccF | PWM1 and PWM2 output fall time           |     | 10 * | 35 *§ | ns    |            |

| * The            |      | motors are observatorized but not tested |     |      |       |       |            |