Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 232 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-25i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

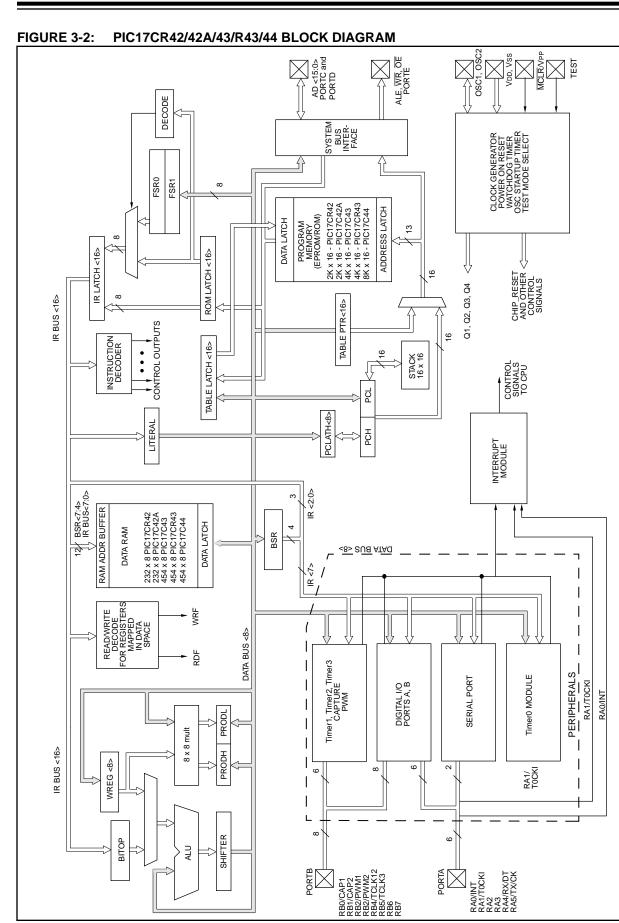

## 1.0 OVERVIEW

This data sheet covers the PIC17C4X group of the PIC17CXX family of microcontrollers. The following devices are discussed in this data sheet:

- PIC17C42

- PIC17CR42

- PIC17C42A

- PIC17C43

- PIC17CR43

- PIC17C44

The PIC17CR42, PIC17C42A, PIC17C43, PIC17CR43, and PIC17C44 devices include architectural enhancements over the PIC17C42. These enhancements will be discussed throughout this data sheet.

The PIC17C4X devices are 40/44-Pin, EPROM/ROM-based members of the versatile PIC17CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC17CXX has enhanced core features, 16-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 16-bit wide instruction word with a separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 55 instructions (reduced instruction set) are available in the PIC17C42 and 58 instructions in all the other devices. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance. For mathematical intensive applications all devices, except the PIC17C42, have a single cycle 8 x 8 Hardware Multiplier.

PIC17CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC17C4X devices have up to 454 bytes of RAM and 33 I/O pins. In addition, the PIC17C4X adds several peripheral features useful in many high performance applications including:

- · Four timer/counters

- Two capture inputs

- Two PWM outputs

- A Universal Synchronous Asynchronous Receiver Transmitter (USART)

These special features reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LF oscillator is for low frequency crystals and minimizes power consumption, XT is a standard crystal, and the EC is for external clock input. The SLEEP (power-down) mode offers additional power saving. The user can wake-up the chip from SLEEP through several external and internal interrupts and device resets.

There are four configuration options for the device operational modes:

- Microprocessor

- Microcontroller

- Extended microcontroller

- Protected microcontroller

The microprocessor and extended microcontroller modes allow up to 64K-words of external program memory.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software malfunction.

Table 1-1 lists the features of the PIC17C4X devices.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

The PIC17C4X fits perfectly in applications ranging from precise motor control and industrial process control to automotive, instrumentation, and telecom applications. Other applications that require extremely fast execution of complex software programs or the flexibility of programming the software code as one of the last steps of the manufacturing process would also be well suited. The EPROM technology makes customization of application programs (with unique security codes, combinations, model numbers, parameter storage, etc.) fast and convenient. Small footprint package options make the PIC17C4X ideal for applications with space limitations that require high performance. High speed execution, powerful peripheral features, flexible I/O, and low power consumption all at low cost make the PIC17C4X ideal for a wide range of embedded control applications.

## 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X and PIC16CXX families of microcontrollers will see the architectural enhancements that have been implemented. These enhancements allow the device to be more efficient in software and hardware requirements. Please refer to Appendix A for a detailed list of enhancements and modifications. Code written for PIC16C5X or PIC16CXX can be easily ported to PIC17CXX family of devices (Appendix B).

## 1.2 Development Support

The PIC17CXX family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a universal programmer, a "C" compiler, and fuzzy logic support tools.

<sup>© 1996</sup> Microchip Technology Inc.

## TABLE 1-1: PIC17CXX FAMILY OF DEVICES

| Features                    |          | PIC17C42             | PIC17CR42            | PIC17C42A            | PIC17C43             | PIC17CR43            | PIC17C44             |

|-----------------------------|----------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Maximum Frequency of O      | peration | 25 MHz               | 33 MHz               | 33 MHz               | 33 MHz               | 33 MHz 33 MHz        |                      |

| Operating Voltage Range     |          | 4.5 - 5.5V           | 2.5 - 6.0V           |

| Program Memory x16          | (EPROM)  | 2K                   | -                    | 2K                   | 4K                   | -                    | 8K                   |

|                             | (ROM)    | -                    | 2K                   | -                    | -                    | 4K                   | -                    |

| Data Memory (bytes)         |          | 232                  | 232                  | 232                  | 454                  | 454                  | 454                  |

| Hardware Multiplier (8 x 8  | )        | -                    | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer0 (16-bit + 8-bit post | scaler)  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer1 (8-bit)              |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer2 (8-bit)              |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer3 (16-bit)             |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Capture inputs (16-bit)     |          | 2                    | 2                    | 2                    | 2                    | 2                    | 2                    |

| PWM outputs (up to 10-bit   | t)       | 2                    | 2                    | 2                    | 2 2                  |                      | 2                    |

| USART/SCI                   |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Power-on Reset              |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Watchdog Timer              |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| External Interrupts         |          | Yes                  | Yes                  | Yes                  | Yes Yes              |                      | Yes                  |

| Interrupt Sources           |          | 11                   | 11                   | 11                   | 11 11                |                      | 11                   |

| Program Memory Code P       | rotect   | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| I/O Pins                    |          | 33                   | 33                   | 33                   | 33                   | 33                   | 33                   |

| I/O High Current Capabil-   | Source   | 25 mA                |

| ity                         | Sink     | 25 mA <sup>(1)</sup> |

| Package Types               |          | 40-pin DIP           |

|                             |          | 44-pin PLCC          |

|                             |          | 44-pin MQFP          |

|                             |          |                      | 44-pin TQFP          |

Note 1: Pins RA2 and RA3 can sink up to 60 mA.

| Addr                                                        | Unbanked                                                                                  |                                                        |                                                           |                                                               |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|

| 00h                                                         | INDF0                                                                                     |                                                        |                                                           |                                                               |

| 01h                                                         | FSR0                                                                                      |                                                        |                                                           |                                                               |

| 02h                                                         | PCL                                                                                       |                                                        |                                                           |                                                               |

| 03h                                                         | PCLATH                                                                                    |                                                        |                                                           |                                                               |

| 04h                                                         | ALUSTA                                                                                    |                                                        |                                                           |                                                               |

| 05h                                                         | TOSTA                                                                                     |                                                        |                                                           |                                                               |

| 06h                                                         | CPUSTA                                                                                    |                                                        |                                                           |                                                               |

| 07h                                                         | INTSTA                                                                                    |                                                        |                                                           |                                                               |

| 08h                                                         | INDF1                                                                                     |                                                        |                                                           |                                                               |

| 09h                                                         | FSR1                                                                                      |                                                        |                                                           |                                                               |

| 0Ah                                                         | WREG                                                                                      |                                                        |                                                           |                                                               |

| 0Bh                                                         | TMR0L                                                                                     |                                                        |                                                           |                                                               |

| 0Ch                                                         | TMR0H                                                                                     |                                                        |                                                           |                                                               |

| 0Dh                                                         | TBLPTRL                                                                                   |                                                        |                                                           |                                                               |

| 0Eh                                                         | TBLPTRH                                                                                   |                                                        |                                                           |                                                               |

| 0Fh                                                         | BSR                                                                                       |                                                        |                                                           |                                                               |

| 1                                                           |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | Bank 0                                                                                    | Bank 1 <sup>(1)</sup>                                  | Bank 2 <sup>(1)</sup>                                     | Bank 3 <sup>(1)</sup>                                         |

| 10h                                                         | Bank 0<br>PORTA                                                                           | Bank 1 <sup>(1)</sup><br>DDRC                          | Bank 2 <sup>(1)</sup><br>TMR1                             | Bank 3 <sup>(1)</sup><br>PW1DCL                               |

| 10h<br>11h                                                  |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | PORTA                                                                                     | DDRC                                                   | TMR1                                                      | PW1DCL                                                        |

| 11h                                                         | PORTA<br>DDRB                                                                             | DDRC<br>PORTC                                          | TMR1<br>TMR2                                              | PW1DCL<br>PW2DCL                                              |

| 11h<br>12h                                                  | PORTA<br>DDRB<br>PORTB                                                                    | DDRC<br>PORTC<br>DDRD                                  | TMR1<br>TMR2<br>TMR3L                                     | PW1DCL<br>PW2DCL<br>PW1DCH                                    |

| 11h<br>12h<br>13h                                           | PORTA<br>DDRB<br>PORTB<br>RCSTA                                                           | DDRC<br>PORTC<br>DDRD<br>PORTD                         | TMR1<br>TMR2<br>TMR3L<br>TMR3H                            | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH                          |

| 11h<br>12h<br>13h<br>14h                                    | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG                                                  | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE                 | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1                     | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L                  |

| 11h<br>12h<br>13h<br>14h<br>15h                             | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA                                         | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE        | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2              | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H          |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h                      | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h               | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h        | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

## FIGURE 6-5: PIC17C42 REGISTER FILE MAP

Note 1: SFR file locations 10h - 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

## FIGURE 6-6: PIC17CR42/42A/43/R43/44 REGISTER FILE MAP

| Addr | Unbanked           |                       |                       |                       |

|------|--------------------|-----------------------|-----------------------|-----------------------|

| 00h  | INDF0              |                       |                       |                       |

| 01h  | FSR0               |                       |                       |                       |

| 02h  | PCL                |                       |                       |                       |

| 03h  | PCLATH             |                       |                       |                       |

| 04h  | ALUSTA             |                       |                       |                       |

| 05h  | TOSTA              |                       |                       |                       |

| 06h  | CPUSTA             |                       |                       |                       |

| 07h  | INTSTA             |                       |                       |                       |

| 08h  | INDF1              |                       |                       |                       |

| 09h  | FSR1               |                       |                       |                       |

| 0Ah  | WREG               |                       |                       |                       |

| 0Bh  | TMR0L              |                       |                       |                       |

| 0Ch  | TMR0H              |                       |                       |                       |

| 0Dh  | TBLPTRL            |                       |                       |                       |

| 0Eh  | TBLPTRH            |                       |                       |                       |

| 0Fh  | BSR                |                       |                       |                       |

|      | Bank 0             | Bank 1 <sup>(1)</sup> | Bank 2 <sup>(1)</sup> | Bank 3 <sup>(1)</sup> |

| 10h  | PORTA              | DDRC                  | TMR1                  | PW1DCL                |

| 11h  | DDRB               | PORTC                 | TMR2                  | PW2DCL                |

| 12h  | PORTB              | DDRD                  | TMR3L                 | PW1DCH                |

| 13h  | RCSTA              | PORTD                 | TMR3H                 | PW2DCH                |

| 14h  | RCREG              | DDRE                  | PR1                   | CA2L                  |

| 15h  | TXSTA              | PORTE                 | PR2                   | CA2H                  |

| 16h  | TXREG              | PIR                   | PR3L/CA1L             | TCON1                 |

| 17h  | SPBRG              | PIE                   | PR3H/CA1H             | TCON2                 |

| 18h  | PRODL              |                       |                       |                       |

| 19h  | PRODH              |                       |                       |                       |

| 1Ah  |                    |                       |                       |                       |

|      |                    |                       |                       |                       |

| 1Fh  |                    |                       | 1                     |                       |

| 20h  | General            | General               |                       |                       |

|      | Purpose            | Purpose               |                       |                       |

|      | RAM <sup>(2)</sup> | RAM (2)               |                       |                       |

|      |                    |                       |                       |                       |

| FFh  |                    |                       |                       |                       |

- Note 1: SFR file locations 10h 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

- 2: General Purpose Registers (GPR) locations 20h - FFh and 120h - 1FFh are banked. All other GPRs ignore the Bank Select Register (BSR) bits.

| TABLE 6-3: | SPECIAL FUNCTION REGISTERS |

|------------|----------------------------|

|------------|----------------------------|

| Address            | Name          | Bit 7        | Bit 6          | Bit 5         | Bit 4        | Bit 3        | Bit 2           | Bit 1          | Bit 0           | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|---------------|--------------|----------------|---------------|--------------|--------------|-----------------|----------------|-----------------|-------------------------------|-------------------------------------|

| Unbank             | ed            | •            |                |               |              | •            |                 |                | •               |                               |                                     |

| 00h                | INDF0         | Uses con     | tents of FSI   | R0 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 01h                | FSR0          | Indirect d   | ata memory     | address po    | inter 0      |              |                 |                |                 | XXXX XXXX                     | uuuu uuuu                           |

| 02h                | PCL           | Low orde     | r 8-bits of P  | С             |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | PCLATH        | Holding re   | egister for u  | pper 8-bits o | of PC        |              |                 |                |                 | 0000 0000                     | uuuu uuuu                           |

| 04h                | ALUSTA        | FS3          | FS2            | FS1           | FS0          | OV           | Z               | DC             | С               | 1111 xxxx                     | 1111 uuuu                           |

| 05h                | TOSTA         | INTEDG       | TOSE           | TOCS          | PS3          | PS2          | PS1             | PS0            | —               | 0000 000-                     | 0000 000-                           |

| 06h <b>(2)</b>     | CPUSTA        | _            | _              | STKAV         | GLINTD       | TO           | PD              | _              | _               | 11 11                         | 11 qq                               |

| 07h                | INTSTA        | PEIF         | TOCKIF         | T0IF          | INTF         | PEIE         | TOCKIE          | TOIE           | INTE            | 0000 0000                     | 0000 0000                           |

| 08h                | INDF1         | Uses con     | tents of FSI   | R1 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 09h                | FSR1          | Indirect d   | ata memory     | address po    | inter 1      |              | , ,             |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ah                | WREG          | Working r    | egister        |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Bh                | TMR0L         | TMR0 reg     | gister; low b  | yte           |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ch                | TMR0H         | TMR0 reg     | gister; high I | oyte          |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Dh                | TBLPTRL       | Low byte     | of program     | memory tab    | le pointer   |              |                 |                |                 | (4)                           | (4)                                 |

| 0Eh                | TBLPTRH       | High byte    | of program     | memory tal    | ole pointer  |              |                 |                |                 | (4)                           | (4)                                 |

| 0Fh                | BSR           | Bank sele    | ect register   |               |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| Bank 0             |               | 1            |                |               |              |              |                 |                |                 | I                             |                                     |

| 10h                | PORTA         | RBPU         | _              | RA5           | RA4          | RA3          | RA2             | RA1/T0CKI      | RA0/INT         | 0-xx xxxx                     | 0-uu uuuu                           |

| 11h                | DDRB          | Data dire    | ction registe  | er for PORTE  | 3            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 12h                | PORTB         | PORTB d      | ata latch      |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | RCSTA         | SPEN         | RX9            | SREN          | CREN         | —            | FERR            | OERR           | RX9D            | 0000 -00x                     | 0000 -00u                           |

| 14h                | RCREG         | Serial por   | t receive re   | gister        |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | TXSTA         | CSRC         | TX9            | TXEN          | SYNC         | —            | —               | TRMT           | TX9D            | 00001x                        | 00001u                              |

| 16h                | TXREG         | Serial por   | t transmit re  | egister       |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | SPBRG         | Baud rate    | generator      | register      |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| Bank 1             |               |              |                |               |              |              |                 |                |                 |                               |                                     |

| 10h                | DDRC          | Data dire    | ction registe  | er for PORT   | 2            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 11h                | PORTC         | RC7/<br>AD7  | RC6/<br>AD6    | RC5/<br>AD5   | RC4/<br>AD4  | RC3/<br>AD3  | RC2/<br>AD2     | RC1/<br>AD1    | RC0/<br>AD0     | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | DDRD          | Data dire    | ction registe  | er for PORTI  | )            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 4.01-              | PORTD         | RD7/<br>AD15 | RD6/<br>AD14   | RD5/<br>AD13  | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10    | RD1/<br>AD9    | RD0/<br>AD8     | xxxx xxxx                     | uuuu uuuu                           |

| 13h                |               | Data dira    | ction reaiste  | er for PORTE  | -            |              |                 | 1              |                 | 111                           | 111                                 |

| 13h<br>14h         | DDRE          | Data dire    |                |               |              |              |                 | -              |                 |                               |                                     |

|                    | DDRE<br>PORTE | Data dire    | _              | _             | _            | _            | RE2/WR          | RE1/OE         | RE0/ALE         | xxx                           | uuu                                 |

| 14h                |               | RBIF         | —<br>TMR3IF    | —<br>TMR2IF   | —<br>TMR1IF  | —<br>CA2IF   | RE2/WR<br>CA1IF | RE1/OE<br>TXIF | RE0/ALE<br>RCIF | xxx<br>0000 0010              | uuu<br>0000 0010                    |

x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated Legend: Note 1:

from or transferred to the upper byte of the program counter. The TO and PD status bits in CPUSTA are not affected by a MCLR reset. 2:

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

4:

The following values are for both TBLPTRL and TBLPTRH: All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000) except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu)

5: The PRODL and PRODH registers are not implemented on the PIC17C42.

### 6.2.2.1 ALU STATUS REGISTER (ALUSTA)

The ALUSTA register contains the status bits of the Arithmetic and Logic Unit and the mode control bits for the indirect addressing register.

As with all the other registers, the ALUSTA register can be the destination for any instruction. If the ALUSTA register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the ALUSTA register as destination may be different than intended.

For example, CLRF ALUSTA will clear the upper four bits and set the Z bit. This leaves the ALUSTA register as 0000u1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions be used to alter the ALUSTA register because these instructions do not affect any status bit. To see how other instructions affect the status bits, see the "Instruction Set Summary."

| Note | 1: The C and DC bits operate as a borrow<br>out bit in subtraction. See the SUBLW and<br>SUBWF instructions for examples. |

|------|---------------------------------------------------------------------------------------------------------------------------|

| Note | 2: The overflow bit will be set if the 2's com-<br>plement result exceeds +127 or is less<br>than -128.                   |

Arithmetic and Logic Unit (ALU) is capable of carrying out arithmetic or logical operations on two operands or a single operand. All single operand instructions operate either on the WREG register or a file register. For two operand instructions, one of the operands is the WREG register and the other one is either a file register or an 8-bit immediate constant.

| FS3      | FS2                                  | FS1                                                                | FS0                                                  | OV                                                      | Z                                   | DC                       | С          | R = Readable bit                                                  |

|----------|--------------------------------------|--------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|-------------------------------------|--------------------------|------------|-------------------------------------------------------------------|

| bit7     | 1                                    | 1                                                                  |                                                      |                                                         |                                     | I                        | bit0       | W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)      |

| bit 7-6: | 01 = Pos                             | FSR1 Mo<br>t auto-dect<br>t auto-incre<br>t value de               | rement FS<br>ement FSI                               | R1 value<br>R1 value                                    |                                     |                          |            |                                                                   |

| bit 5-4: | 01 = Pos                             | FSR0 Mo<br>t auto-deci<br>t auto-incre<br>0 value de               | rement FS<br>ement FSI                               | R0 value<br>R0 value                                    |                                     |                          |            |                                                                   |

| bit 3:   | which cau<br>1 = Overfl              | s used for<br>uses the si                                          | gn bit (bit7<br>ed for sign                          | ') to chang                                             |                                     |                          |            | overflow of the 7-bit magnitude,                                  |

| bit 2:   |                                      | esult of an                                                        |                                                      |                                                         | peration is operation is            |                          |            |                                                                   |

| bit 1:   | For ADDW<br>1 = A carr $0 = No ca$   | •                                                                  | LW instruc<br>the 4th lo<br>m the 4th                | w order bi<br>low order                                 | t of the res<br>bit of the re<br>I. |                          | d          |                                                                   |

| bit 0:   | 1 = A carr<br>Note that<br>(RRCF, RL | F and ADD<br>y-out from<br>a subtrac<br>CF) instru-<br>rry-out fro | the most<br>tion is exe<br>ctions, this<br>m the mos | significant<br>cuted by a<br>bit is load<br>t significa | ded with eit<br>nt bit of the       | two's com<br>her the hig | plement of | the second operand. For rotate<br>der bit of the source register. |

## FIGURE 6-7: ALUSTA REGISTER (ADDRESS: 04h, UNBANKED)

## 7.1 <u>Table Writes to Internal Memory</u>

A table write operation to internal memory causes a long write operation. The long write is necessary for programming the internal EPROM. Instruction execution is halted while in a long write cycle. The long write will be terminated by any enabled interrupt. To ensure that the EPROM location has been well programmed, a minimum programming time is required (see specification #D114). Having only one interrupt enabled to terminate the long write ensures that no unintentional interrupts will prematurely terminate the long write.

The sequence of events for programming an internal program memory location should be:

- 1. Disable all interrupt sources, except the source to terminate EPROM program write.

- 2. Raise MCLR/VPP pin to the programming voltage.

- 3. Clear the WDT.

- 4. Do the table write. The interrupt will terminate the long write.

- 5. Verify the memory location (table read).

- **Note:** Programming requirements must be met. See timing specification in electrical specifications for the desired device. Violating these specifications (including temperature) may result in EPROM locations that are not fully programmed and may lose their state over time.

## 7.1.1 TERMINATING LONG WRITES

An interrupt source or reset are the only events that terminate a long write operation. Terminating the long write from an interrupt source requires that the interrupt enable and flag bits are set. The GLINTD bit only enables the vectoring to the interrupt address.

If the TOCKI, RA0/INT, or TMR0 interrupt source is used to terminate the long write; the interrupt flag, of the highest priority enabled interrupt, will terminate the long write and automatically be cleared.

- **Note 1:** If an interrupt is pending, the TABLWT is aborted (an NOP is executed). The highest priority pending interrupt, from the TOCKI, RA0/INT, or TMR0 sources that is enabled, has its flag cleared.

- **Note 2:** If the interrupt is not being used for the program write timing, the interrupt should be disabled. This will ensure that the interrupt is not lost, nor will it terminate the long write prematurely.

If a peripheral interrupt source is used to terminate the long write, the interrupt enable and flag bits must be set. The interrupt flag will not be automatically cleared upon the vectoring to the interrupt vector address.

If the GLINTD bit is cleared prior to the long write, when the long write is terminated, the program will branch to the interrupt vector.

If the GLINTD bit is set prior to the long write, when the long write is terminated, the program will not vector to the interrupt address.

| Interrupt<br>Source     | GLINTD | Enable<br>Bit | Flag<br>Bit | Action                                                                                                              |

|-------------------------|--------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------|

| RA0/INT, TMR0,<br>T0CKI | 0      | 1             | 1           | Terminate long table write (to internal program<br>memory), branch to interrupt vector (branch clears<br>flag bit). |

|                         | 0      | 1             | 0           | None                                                                                                                |

|                         | 1      | 0             | x           | None                                                                                                                |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is automatically cleared).                           |

| Peripheral              | 0      | 1             | 1           | Terminate table write, branch to interrupt vector.                                                                  |

|                         | 0      | 1             | 0           | None                                                                                                                |

|                         | 1      | 0             | x           | None                                                                                                                |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is set).                                             |

## TABLE 7-1: INTERRUPT - TABLE WRITE INTERACTION

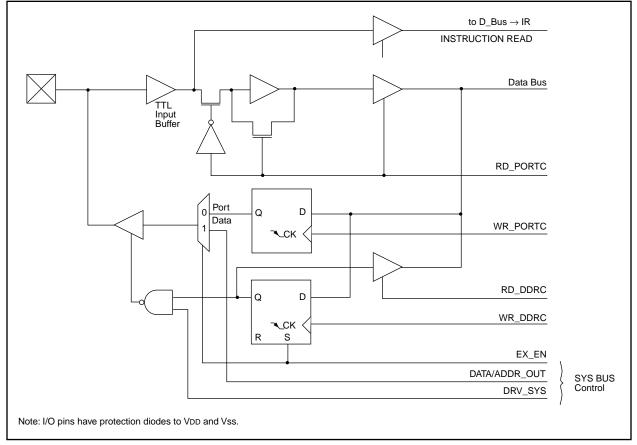

## 9.3 PORTC and DDRC Registers

PORTC is an 8-bit bi-directional port. The corresponding data direction register is DDRC. A '1' in DDRC configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTC reads the status of the pins, whereas writing to it will write to the port latch. PORTC is multiplexed with the system bus. When operating as the system bus, PORTC is the low order byte of the address/data bus (AD7:AD0). The timing for the system bus is shown in the Electrical Characteristics section.

**Note:** This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-2 shows the instruction sequence to initialize PORTC. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

## EXAMPLE 9-2: INITIALIZING PORTC

| 1     | ;             | Select Bank 1                                        |

|-------|---------------|------------------------------------------------------|

| PORTC | ;             | Initialize PORTC data                                |

|       | ;             | latches before setting                               |

|       | ;             | the data direction                                   |

|       | ;             | register                                             |

| 0xCF  | ;             | Value used to initialize                             |

|       | ;             | data direction                                       |

| DDRC  | ;             | Set RC<3:0> as inputs                                |

|       | ;             | RC<5:4> as outputs                                   |

|       | ;             | RC<7:6> as inputs                                    |

|       | PORTC<br>0xCF | PORTC ;<br>;<br>;<br>;<br>;<br>0xCF ;<br>DDRC ;<br>; |

## FIGURE 9-6: BLOCK DIAGRAM OF RC<7:0> PORT PINS

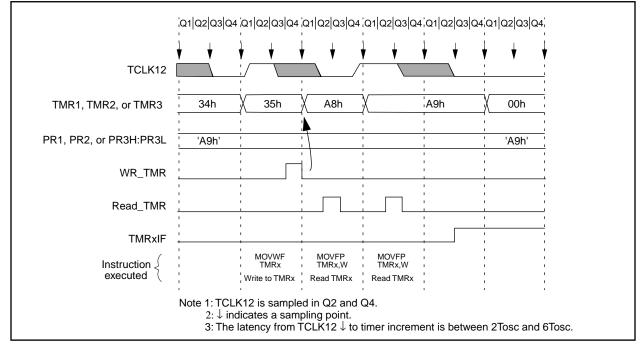

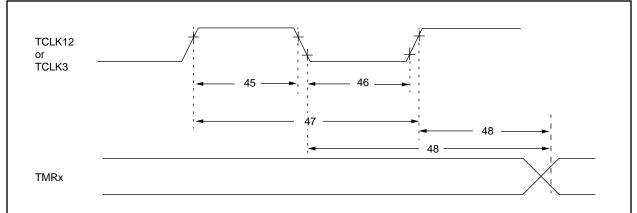

#### 12.2.3 EXTERNAL CLOCK INPUT FOR TIMER3

When TMR3CS is set, the 16-bit TMR3 increments on the falling edge of clock input TCLK3. The input on the RB5/TCLK3 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on TCLK3 to the time TMR3 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section. Figure 12-9 shows the timing diagram when operating from an external clock.

#### 12.2.4 READING/WRITING TIMER3

Since Timer3 is a 16-bit timer and only 8-bits at a time can be read or written, care should be taken when reading or writing while the timer is running. The best method to read or write the timer is to stop the timer, perform any read or write operation, and then restart Timer3 (using the TMR3ON bit). However, if it is necessary to keep Timer3 free-running, care must be taken. For writing to the 16-bit TMR3, Example 12-2 may be used. For reading the 16-bit TMR3, Example 12-3 may be used. Interrupts must be disabled during this routine.

#### EXAMPLE 12-2: WRITING TO TMR3

BSF CPUSTA, GLINTD ;Disable interrupt MOVFP RAM\_L, TMR3L ; MOVFP RAM\_H, TMR3H ; BCF CPUSTA, GLINTD ;Done,enable interrupt

#### **EXAMPLE 12-3: READING FROM TMR3**

| MOVPF TMR3L, TMPLO ;read low t<br>MOVPF TMR3H, TMPHI ;read high<br>MOVFP TMPLO, WREG ;tmplo -> w | tmr0  |

|--------------------------------------------------------------------------------------------------|-------|

| CPFSLT TMR3L, WREG ;tmr0l < wr                                                                   | eg?   |

| RETURN ;no then re                                                                               | eturn |

| MOVPF TMR3L, TMPLO ;read low t                                                                   | .mr0  |

| MOVPF TMR3H, TMPHI ;read high                                                                    | tmr0  |

| RETURN ; return                                                                                  |       |

## FIGURE 12-9: TMR1, TMR2, AND TMR3 OPERATION IN EXTERNAL CLOCK MODE

| SWAPF                            | Swap f                                                            |                       |                              |                       |  |  |  |

|----------------------------------|-------------------------------------------------------------------|-----------------------|------------------------------|-----------------------|--|--|--|

| Syntax:                          | [label]                                                           | SWAPF                 | f,d                          |                       |  |  |  |

| Operands:                        | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ | 5                     |                              |                       |  |  |  |

| Operation:                       | $f < 3:0 > \rightarrow f < 7:4 > \rightarrow$                     |                       | ,                            |                       |  |  |  |

| Status Affected:                 | None                                                              |                       |                              |                       |  |  |  |

| Encoding:                        | 0001                                                              | 110d                  | ffff                         | ffff                  |  |  |  |

| Description:                     | The upper<br>'f' are excha<br>placed in W<br>placed in re         | anged. If<br>/REG. If | 'd' is 0 the<br>'d' is 1 the | e result is           |  |  |  |

| Words:                           | 1                                                                 |                       |                              |                       |  |  |  |

| Cycles:                          | 1                                                                 |                       |                              |                       |  |  |  |

| Q Cycle Activity:                |                                                                   |                       |                              |                       |  |  |  |

| Q1                               | Q2                                                                | Q                     | 3                            | Q4                    |  |  |  |

| Decode                           | Read<br>register 'f'                                              | Exect                 |                              | Vrite to<br>stination |  |  |  |

| Example:                         | SWAPF I                                                           | REG,                  | 0                            |                       |  |  |  |

| Before Instruction<br>REG = 0x53 |                                                                   |                       |                              |                       |  |  |  |

| After Instruc<br>REG             | tion<br>= 0x35                                                    |                       |                              |                       |  |  |  |

| TABLRD            | Table Rea                                                                                                                                                                                                                             | d            |                       |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|--|--|--|

| Syntax:           | [label]                                                                                                                                                                                                                               | rablrd t,i,f |                       |  |  |  |

| Operands:         | $0 \le f \le 255$<br>$i \in [0,1]$<br>$t \in [0,1]$                                                                                                                                                                                   | 5            |                       |  |  |  |

| Operation:        | If t = 1,<br>TBLATH $\rightarrow$ f;<br>If t = 0,<br>TBLATL $\rightarrow$ f;<br>Prog Mem (TBLPTR) $\rightarrow$ TBLAT<br>If i = 1,<br>TBLPTR + 1 $\rightarrow$ TBLPTR                                                                 |              |                       |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                  |              |                       |  |  |  |

| Encoding:         | 1010                                                                                                                                                                                                                                  | 10ti ff      | ff ffff               |  |  |  |

| Description:      | <ol> <li>A byte of the table latch (TBLAT)<br/>is moved to register file 'f'.<br/>If t = 0: the high byte is moved;<br/>If t = 1: the low byte is moved</li> </ol>                                                                    |              |                       |  |  |  |

|                   | <ol> <li>Then the contents of the program memory location pointed to by the 16-bit Table Pointer (TBLPTR) is loaded into the 16-bit Table Latch (TBLAT).</li> <li>If i = 1: TBLPTR is incremented; If i = 0: TBLPTR is not</li> </ol> |              |                       |  |  |  |

| Words:            | incremented                                                                                                                                                                                                                           |              |                       |  |  |  |

| Cycles:           | 2 (3 cycle if f = PCL)                                                                                                                                                                                                                |              |                       |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                       |              |                       |  |  |  |

| Q1                | Q2                                                                                                                                                                                                                                    | Q3           | Q4                    |  |  |  |

| Decode            | Read<br>register<br>TBLATH or<br>TBLATL                                                                                                                                                                                               | Execute      | Write<br>register 'f' |  |  |  |

| TLWT              | Table Late                      | ch Write                           |                     | TSTFSZ                    | Test f, sk            | ip if 0                                                                                                                      |             |  |  |

|-------------------|---------------------------------|------------------------------------|---------------------|---------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| Syntax:           | [label] T                       | LWT t,f                            |                     | Syntax:                   | [ label ]             | TSTFSZ f                                                                                                                     |             |  |  |

| Operands:         | 0 ≤ f ≤ 255                     | 5                                  |                     | Operands:                 | 0 ≤ f ≤ 25            | 5                                                                                                                            |             |  |  |

|                   | t ∈ [0,1]                       |                                    |                     | Operation:                | skip if f =           | 0                                                                                                                            |             |  |  |

| Operation:        | If $t = 0$ ,                    |                                    |                     | Status Affected:          | None                  |                                                                                                                              |             |  |  |

|                   | $f \rightarrow TB$<br>If t = 1, | LAIL;                              |                     | Encoding:                 | 0011                  | 0011 fff                                                                                                                     | f ffff      |  |  |

|                   | $f \rightarrow TB$              | LATH                               |                     | Description:              | If 'f' = 0, the       | e next instructio                                                                                                            | on, fetched |  |  |

| Status Affected:  | None                            |                                    |                     | ·                         |                       | If 'f' = 0, the next instruction, fetched<br>during the current instruction executior<br>is discarded and an NOP is executed |             |  |  |

| Encoding:         | 1010                            | 01tx ff:                           | ff ffff             |                           |                       | a and an NOP<br>a two-cycle in                                                                                               |             |  |  |

| Description:      | Data from fi                    | ile register 'f' i                 | s written into      | Words:                    | 1                     | ·                                                                                                                            |             |  |  |

| ·                 |                                 | able latch (TBI                    |                     | Cycles:                   | 1 (2)                 |                                                                                                                              |             |  |  |

|                   | -                               | byte is writte                     |                     | Q Cycle Activity:         | ( )                   |                                                                                                                              |             |  |  |

|                   |                                 | byte is written<br>tion is used in |                     | Q1                        | Q2                    | Q3                                                                                                                           | Q4          |  |  |

|                   |                                 |                                    | lata from data      | Decode                    | Read                  | Execute                                                                                                                      | NOP         |  |  |

|                   | memory to                       | program mem                        | iory.               |                           | register 'f'          |                                                                                                                              |             |  |  |

| Words:            | 1                               |                                    |                     | If skip:                  | 00                    | 02                                                                                                                           | 04          |  |  |

| Cycles:           | 1                               |                                    |                     | Q1<br>Forced NOP          | Q2<br>NOP             | Q3<br>Execute                                                                                                                | Q4<br>NOP   |  |  |

| Q Cycle Activity: |                                 |                                    |                     |                           |                       |                                                                                                                              | NOI         |  |  |

| Q1                | Q2                              | Q3                                 | Q4                  | Example:                  | HERE<br>NZERO         | TSTFSZ CNT<br>:                                                                                                              |             |  |  |

| Decode            | Read<br>register 'f'            | Execute                            | Write<br>register   |                           | ZERO :                | -                                                                                                                            |             |  |  |

|                   | regioner 1                      |                                    | TBLATH or<br>TBLATL | Before Instru<br>PC = Ado | lction<br>dress(HERE) |                                                                                                                              |             |  |  |

| Example:          | TLWT t                          | :, RAM                             |                     | After Instruct            | tion                  |                                                                                                                              |             |  |  |

| Before Instru     |                                 |                                    |                     | If CNT                    |                       | .00,                                                                                                                         |             |  |  |

| t                 | = 0                             |                                    |                     | PC<br>If CNT              |                       | dress (ZERO)<br>00,                                                                                                          |             |  |  |

| RAM<br>TBLAT      | = 0xB7<br>= 0x0000              | (TBLATH =                          | 0×00)               | PC                        | = Ac                  | dress (NZERO                                                                                                                 | )           |  |  |

| IDEAI             | - 000000                        | (TBLATL =                          |                     |                           |                       |                                                                                                                              |             |  |  |

| After Instruct    | tion                            |                                    |                     |                           |                       |                                                                                                                              |             |  |  |

| RAM               | = 0xB7                          |                                    |                     |                           |                       |                                                                                                                              |             |  |  |

| TBLAT             | = 0x00B7                        | (TBLATH =<br>(TBLATL =             | ,                   |                           |                       |                                                                                                                              |             |  |  |

| Before Instru     |                                 |                                    |                     |                           |                       |                                                                                                                              |             |  |  |

| t<br>RAM          | = 1<br>= 0xB7                   |                                    |                     |                           |                       |                                                                                                                              |             |  |  |

| TBLAT             | = 0x0000                        | (TBLATH =<br>(TBLATL =             | ,                   |                           |                       |                                                                                                                              |             |  |  |

| After Instruct    | tion                            |                                    |                     |                           |                       |                                                                                                                              |             |  |  |

| RAM               | = 0xB7                          |                                    |                     |                           |                       |                                                                                                                              |             |  |  |

| TBLAT             | = 0xB700                        | · ·                                | ,                   |                           |                       |                                                                                                                              |             |  |  |

|                   |                                 | (TBLATL =                          | UXUU)               |                           |                       |                                                                                                                              |             |  |  |

## Applicable Devices 42 R42 42A 43 R43 44

#### 17.2 DC CHARACTERISTICS:

#### PIC17C42-16 (Commercial, Industrial) PIC17C42-25 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated) Operating temperature

#### DC CHARACTERISTICS

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and  $0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

Operating voltage VDD range as described in Section 17.1 Parameter No. Sym Characteristic Min Typ† Max Units Conditions Input Low Voltage VIL I/O ports D030 with TTL buffer Vss 0.8 V D031 with Schmitt Trigger buffer Vss 0.2VDD V \_ D032 MCLR, OSC1 (in EC and RC Vss 0.2Vdd V Note1 \_ mode) D033 OSC1 (in XT, and LF mode) 0.5VDD V \_ Input High Voltage Vн I/O ports V D040 2.0 with TTL buffer \_ Vdd D041 with Schmitt Trigger buffer 0.8VDD Vdd V \_ D042 MCLR 0.8Vdd Vdd Note1 V D043 OSC1 (XT, and LF mode) 0.5VDD V D050 Hysteresis of 0.15VDD\* VHYS V \_ \_ Schmitt Trigger inputs Input Leakage Current (Notes 2, 3) D060 lı∟ I/O ports (except RA2, RA3)  $Vss \leq VPIN \leq VDD$ , ±1 μΑ I/O Pin at hi-impedance PORTB weak pull-ups disabled MCLR D061 <u>+2</u> μA VPIN = Vss or VPIN = VDD D062 **RA2, RA3** ±2 μΑ  $Vss \leq VRA2$ ,  $VRA3 \leq 12V$ D063 OSC1, TEST ±1 μΑ  $Vss \le VPIN \le VDD$

D070 IPURB PORTB weak pull-up current 60 These parameters are characterized but not tested.

MCLR

D064

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only t and are not tested.

200

10

400

μA

μΑ

These parameters are for design guidance only and are not tested, nor characterized. t

Design guidance to attain the AC timing specifications. These loads are not tested. ++

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/Vpp pin may be kept in this range at times other than programming, but this is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

VMCLR = VPP = 12V

(when not programming)

VPIN = Vss.  $\overline{RBPU} = 0$

## Applicable Devices 42 R42 42A 43 R43 44

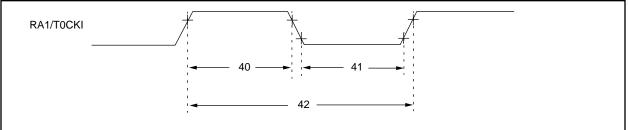

## FIGURE 17-5: TIMER0 CLOCK TIMINGS

## TABLE 17-5: TIMER0 CLOCK REQUIREMENTS

| Parameter<br>No. | Sum  | Characteristic         |                | Min               | Tunt | Мах   | Unito | Conditions         |

|------------------|------|------------------------|----------------|-------------------|------|-------|-------|--------------------|

| NO.              | Sym  | Characteristic         |                | IVIIII            | Typ† | IVIAX | Units | Conditions         |

| 40               | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5TCY + 20 §     | _    | _     | ns    |                    |

|                  |      |                        | With Prescaler | 10*               | —    | —     | ns    |                    |

| 41               | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5Tcy + 20 §     | —    | —     | ns    |                    |

|                  |      |                        | With Prescaler | 10*               | —    | —     | ns    |                    |

| 42               | Tt0P | T0CKI Period           | •              | <u>Tcy + 40</u> § | —    | —     | ns    | N = prescale value |

|                  |      |                        |                | N                 |      |       |       | (1, 2, 4,, 256)    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

## FIGURE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK TIMINGS

## TABLE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK REQUIREMENTS

| Parameter |           |                                                               |                        | Тур |          |       |                                    |

|-----------|-----------|---------------------------------------------------------------|------------------------|-----|----------|-------|------------------------------------|

| No.       | Sym       | Characteristic                                                | Min                    | †   | Max      | Units | Conditions                         |

| 45        | Tt123H    | TCLK12 and TCLK3 high time                                    | 0.5 TCY + 20 §         |     | _        | ns    |                                    |

| 46        | Tt123L    | TCLK12 and TCLK3 low time                                     | 0.5 TCY + 20 §         |     | _        | ns    |                                    |

| 47        | Tt123P    | TCLK12 and TCLK3 input period                                 | <u>Tcy + 40</u> §<br>N |     |          | ns    | N = prescale value<br>(1, 2, 4, 8) |

| 48        | TckE2tmrl | Delay from selected External Clock Edge to<br>Timer increment | 2Tosc §                |     | 6 Tosc § | _     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

Applicable Devices 42 R42 42A 43 R43 44

## TABLE 19-1:CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS<br/>AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc              | PIC17LCR42-08<br>PIC17LC42A-08<br>PIC17LC43-08<br>PIC17LCR43-08<br>PIC17LC44-08<br>PIC17LC44-08               | PIC17CR42-16<br>PIC17C42A-16<br>PIC17C43-16<br>PIC17CR43-16<br>PIC17CR43-16<br>PIC17C44-16                                                                                                                                | PIC17CR42-25<br>PIC17C42A-25<br>PIC17C43-25<br>PIC17CR43-25<br>PIC17CR43-25                                   | PIC17CR42-33<br>PIC17C42A-33<br>PIC17C43-33<br>PIC17CR43-33<br>PIC17CR43-33                                   | JW Devices<br>(Ceramic Windowed<br>Devices)                                                                   |