Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 33MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 232 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-33e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

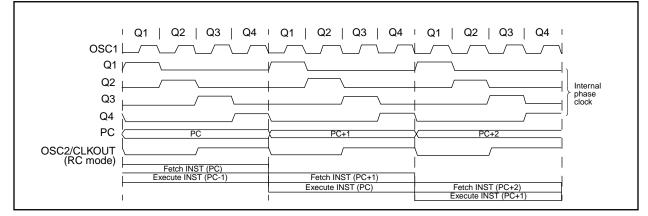

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-3.

### 3.2 Instruction Flow/Pipelining

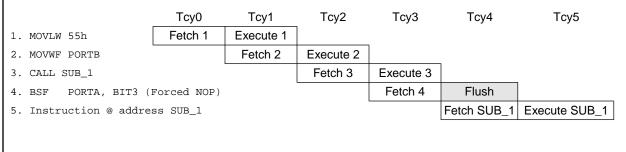

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g.GOTO) then two cycles are required to complete the instruction (Example 3-2).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-2: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

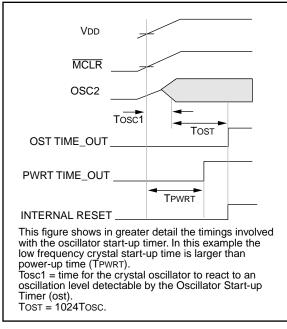

### FIGURE 4-5: OSCILLATOR START-UPTIME

### FIGURE 4-6: USING ON-CHIP POR

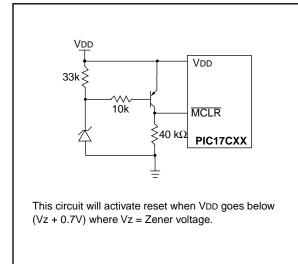

### FIGURE 4-7: BROWN-OUT PROTECTION CIRCUIT 1

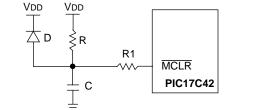

### FIGURE 4-8: PIC17C42 EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: An external Power-on Reset circuit is required only if VDD power-up time is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R < 40 k $\Omega$  is recommended to ensure that the voltage drop across R does not exceed 0.2V (max. leakage current spec. on the  $\overline{MCLR}/VPP$  pin is 5  $\mu$ A). A larger voltage drop will degrade VIH level on the  $\overline{MCLR}/VPP$  pin.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or (Electrical Overstress) EOS.

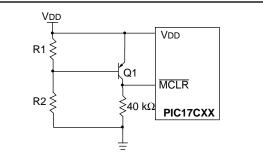

FIGURE 4-9: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

| Addr                                                        | Unbanked                                                                                  |                                                        |                                                           |                                                               |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|

| 00h                                                         | INDF0                                                                                     |                                                        |                                                           |                                                               |

| 01h                                                         | FSR0                                                                                      |                                                        |                                                           |                                                               |

| 02h                                                         | PCL                                                                                       |                                                        |                                                           |                                                               |

| 03h                                                         | PCLATH                                                                                    |                                                        |                                                           |                                                               |

| 04h                                                         | ALUSTA                                                                                    |                                                        |                                                           |                                                               |

| 05h                                                         | TOSTA                                                                                     |                                                        |                                                           |                                                               |

| 06h                                                         | CPUSTA                                                                                    |                                                        |                                                           |                                                               |

| 07h                                                         | INTSTA                                                                                    |                                                        |                                                           |                                                               |

| 08h                                                         | INDF1                                                                                     |                                                        |                                                           |                                                               |

| 09h                                                         | FSR1                                                                                      |                                                        |                                                           |                                                               |

| 0Ah                                                         | WREG                                                                                      |                                                        |                                                           |                                                               |

| 0Bh                                                         | TMR0L                                                                                     |                                                        |                                                           |                                                               |

| 0Ch                                                         | TMR0H                                                                                     |                                                        |                                                           |                                                               |

| 0Dh                                                         | TBLPTRL                                                                                   |                                                        |                                                           |                                                               |

| 0Eh                                                         | TBLPTRH                                                                                   |                                                        |                                                           |                                                               |

| 0Fh                                                         | BSR                                                                                       |                                                        |                                                           |                                                               |

| 1                                                           |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | Bank 0                                                                                    | Bank 1 <sup>(1)</sup>                                  | Bank 2 <sup>(1)</sup>                                     | Bank 3 <sup>(1)</sup>                                         |

| 10h                                                         | Bank 0<br>PORTA                                                                           | Bank 1 <sup>(1)</sup><br>DDRC                          | Bank 2 <sup>(1)</sup><br>TMR1                             | Bank 3 <sup>(1)</sup><br>PW1DCL                               |

| 10h<br>11h                                                  |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | PORTA                                                                                     | DDRC                                                   | TMR1                                                      | PW1DCL                                                        |

| 11h                                                         | PORTA<br>DDRB                                                                             | DDRC<br>PORTC                                          | TMR1<br>TMR2                                              | PW1DCL<br>PW2DCL                                              |

| 11h<br>12h                                                  | PORTA<br>DDRB<br>PORTB                                                                    | DDRC<br>PORTC<br>DDRD                                  | TMR1<br>TMR2<br>TMR3L                                     | PW1DCL<br>PW2DCL<br>PW1DCH                                    |

| 11h<br>12h<br>13h                                           | PORTA<br>DDRB<br>PORTB<br>RCSTA                                                           | DDRC<br>PORTC<br>DDRD<br>PORTD                         | TMR1<br>TMR2<br>TMR3L<br>TMR3H                            | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH                          |

| 11h<br>12h<br>13h<br>14h                                    | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG                                                  | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE                 | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1                     | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L                  |

| 11h<br>12h<br>13h<br>14h<br>15h                             | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA                                         | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE        | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2              | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H          |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h                      | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h               | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h        | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

## FIGURE 6-5: PIC17C42 REGISTER FILE MAP

Note 1: SFR file locations 10h - 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

### FIGURE 6-6: PIC17CR42/42A/43/R43/44 REGISTER FILE MAP

| Addr | Unbanked           |                       |                       |                       |

|------|--------------------|-----------------------|-----------------------|-----------------------|

| 00h  | INDF0              |                       |                       |                       |

| 01h  | FSR0               |                       |                       |                       |

| 02h  | PCL                |                       |                       |                       |

| 03h  | PCLATH             |                       |                       |                       |

| 04h  | ALUSTA             |                       |                       |                       |

| 05h  | TOSTA              |                       |                       |                       |

| 06h  | CPUSTA             |                       |                       |                       |

| 07h  | INTSTA             |                       |                       |                       |

| 08h  | INDF1              |                       |                       |                       |

| 09h  | FSR1               |                       |                       |                       |

| 0Ah  | WREG               |                       |                       |                       |

| 0Bh  | TMR0L              |                       |                       |                       |

| 0Ch  | TMR0H              |                       |                       |                       |

| 0Dh  | TBLPTRL            |                       |                       |                       |

| 0Eh  | TBLPTRH            |                       |                       |                       |

| 0Fh  | BSR                |                       |                       |                       |

|      | Bank 0             | Bank 1 <sup>(1)</sup> | Bank 2 <sup>(1)</sup> | Bank 3 <sup>(1)</sup> |

| 10h  | PORTA              | DDRC                  | TMR1                  | PW1DCL                |

| 11h  | DDRB               | PORTC                 | TMR2                  | PW2DCL                |

| 12h  | PORTB              | DDRD                  | TMR3L                 | PW1DCH                |

| 13h  | RCSTA              | PORTD                 | TMR3H                 | PW2DCH                |

| 14h  | RCREG              | DDRE                  | PR1                   | CA2L                  |

| 15h  | TXSTA              | PORTE                 | PR2                   | CA2H                  |

| 16h  | TXREG              | PIR                   | PR3L/CA1L             | TCON1                 |

| 17h  | SPBRG              | PIE                   | PR3H/CA1H             | TCON2                 |

| 18h  | PRODL              |                       |                       |                       |

| 19h  | PRODH              |                       |                       |                       |

| 1Ah  |                    |                       |                       |                       |

|      |                    |                       |                       |                       |

| 1Fh  |                    |                       | 1                     |                       |

| 20h  | General            | General               |                       |                       |

|      | Purpose            | Purpose               |                       |                       |

|      | RAM <sup>(2)</sup> | RAM (2)               |                       |                       |

|      |                    |                       |                       |                       |

| FFh  |                    |                       |                       |                       |

- Note 1: SFR file locations 10h 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

- 2: General Purpose Registers (GPR) locations 20h - FFh and 120h - 1FFh are banked. All other GPRs ignore the Bank Select Register (BSR) bits.

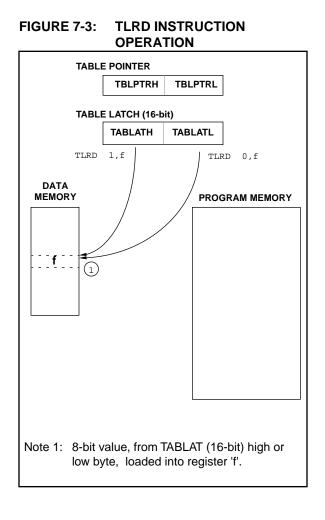

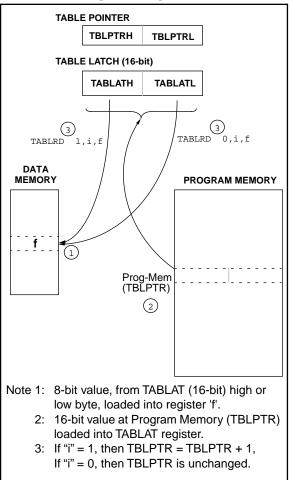

### FIGURE 7-4: TABLRD INSTRUCTION OPERATION

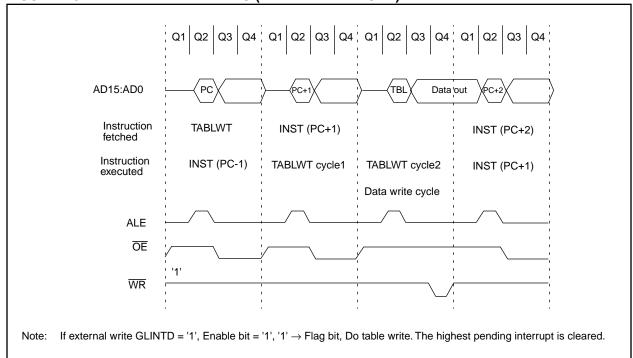

### 7.2 <u>Table Writes to External Memory</u>

Table writes to external memory are always two-cycle instructions. The second cycle writes the data to the external memory location. The sequence of events for an external memory write are the same for an internal write.

| Note: | If an interrupt is pending or occurs during the TABLWT, the two cycle table write |

|-------|-----------------------------------------------------------------------------------|

|       | completes. The RA0/INT, TMR0, or T0CKI                                            |

|       | interrupt flag is automatically cleared or                                        |

|       | the pending peripheral interrupt is                                               |

|       | acknowledged.                                                                     |

7.2.2 TABLE WRITE CODE

The "i" operand of the TABLWT instruction can specify that the value in the 16-bit TBLPTR register is automatically incremented for the next write. In Example 7-1, the TBLPTR register is not automatically incremented.

### EXAMPLE 7-1: TABLE WRITE

| CLRWDT |                 | ; | Clear WDT      |

|--------|-----------------|---|----------------|

| MOVLW  | HIGH (TBL_ADDR) | ; | Load the Table |

| MOVWF  | TBLPTRH         | ; | address        |

| MOVLW  | LOW (TBL_ADDR)  | ; |                |

| MOVWF  | TBLPTRL         | ; |                |

| MOVLW  | HIGH (DATA)     | ; | Load HI byte   |

| TLWT   | 1, WREG         | ; | in TABLATCH    |

| MOVLW  | LOW (DATA)      | ; | Load LO byte   |

| TABLWT | 0,0,WREG        | ; | in TABLATCH    |

|        |                 | ; | and write to   |

|        |                 | ; | program memory |

|        |                 | ; | (Ext. SRAM)    |

|        |                 |   |                |

### FIGURE 7-5: TABLWT WRITE TIMING (EXTERNAL MEMORY)

### 10.0 OVERVIEW OF TIMER RESOURCES

The PIC17C4X has four timer modules. Each module can generate an interrupt to indicate that an event has occurred. These timers are called:

- Timer0 16-bit timer with programmable 8-bit

- prescaler

- Timer1 8-bit timer

- Timer2 8-bit timer

- Timer3 16-bit timer

For enhanced time-base functionality, two input Captures and two Pulse Width Modulation (PWM) outputs are possible. The PWMs use the TMR1 and TMR2 resources and the input Captures use the TMR3 resource.

### 10.1 <u>Timer0 Overview</u>

The Timer0 module is a simple 16-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock.

The Timer0 module also has a programmable prescaler option. The PS3:PS0 bits (T0STA<4:1>) determine the prescaler value. TMR0 can increment at the following rates: 1:1, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, 1:256.

When TImer0's clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

### 10.2 <u>Timer1 Overview</u>

The TImer0 module is an 8-bit timer/counter with an 8bit period register (PR1). When the TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the Timer2 module.

TMR1 can be concatenated to TMR2 to form a 16-bit timer. The TMR1 register is the LSB and TMR2 is the MSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled.

### 10.3 <u>Timer2 Overview</u>

The TMR2 module is an 8-bit timer/counter with an 8bit period register (PR2). When the TMR2 value rolls over from the period match value to 0h, the TMR2IF flag is set, and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the TMR1 module.

TMR1 can be concatenated to TMR2 to form a 16-bit timer. The TMR2 register is the MSB and TMR1 is the LSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled.

### 10.4 <u>Timer3 Overview</u>

The TImer3 module is a 16-bit timer/counter with a 16bit period register. When the TMR3H:TMR3L value rolls over to 0h, the TMR3IF bit is set and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB5/TCLK3 pin.

When operating in the dual capture mode, the period registers become the second 16-bit capture register.

### 10.5 Role of the Timer/Counters

The timer modules are general purpose, but have dedicated resources associated with them. Tlmer1 and Timer2 are the time-bases for the two Pulse Width Modulation (PWM) outputs, while Timer3 is the timebase for the two input captures.

© 1996 Microchip Technology Inc.

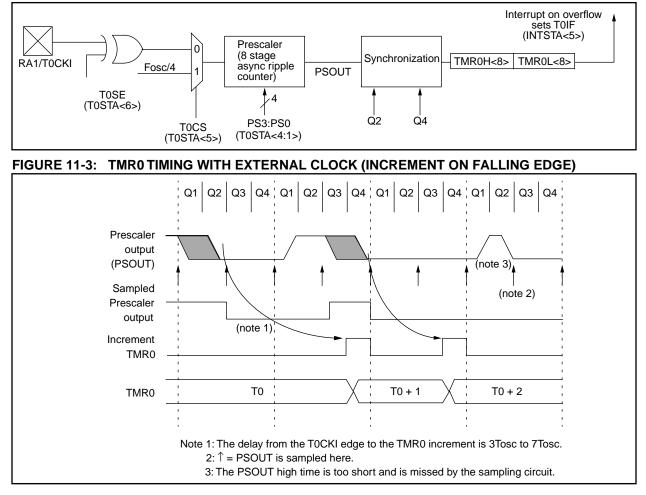

### 11.1 <u>Timer0 Operation</u>

When the TOCS (TOSTA<5>) bit is set, TMR0 increments on the internal clock. When TOCS is clear, TMR0 increments on the external clock (RA1/T0CKI pin). The external clock edge can be configured in software. When the TOSE (TOSTA<6>) bit is set, the timer will increment on the rising edge of the RA1/T0CKI pin. When T0SE is clear, the timer will increment on the falling edge of the RA1/T0CKI pin. The prescaler can be programmed to introduce a prescale of 1:1 to 1:256. The timer increments from 0000h to FFFFh and rolls over to 0000h. On overflow, the TMR0 Interrupt Flag bit (T0IF) is set. The TMR0 interrupt can be masked by clearing the corresponding TMR0 Interrupt Enable bit (T0IE). The TMR0 Interrupt Flag bit (T0IF) is automatically cleared when vectoring to the TMR0 interrupt vector.

### 11.2 Using Timer0 with External Clock

When the external clock input is used for Timer0, it is synchronized with the internal phase clocks. Figure 11-3 shows the synchronization of the external clock. This synchronization is done after the prescaler. The output of the prescaler (PSOUT) is sampled twice in every instruction cycle to detect a rising or a falling edge. The timing requirements for the external clock are detailed in the electrical specification section for the desired device.

### 11.2.1 DELAY FROM EXTERNAL CLOCK EDGE

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time TMR0 is actually incremented. Figure 11-3 shows that this delay is between 3Tosc and 7Tosc. Thus, for example, measuring the interval between two edges (e.g. period) will be accurate within  $\pm$ 4Tosc ( $\pm$ 121 ns @ 33 MHz).

### FIGURE 11-2: TIMER0 MODULE BLOCK DIAGRAM

| Address       | Name                                             | Bit 7    | Bit 6                                       | Bit 5 | Bit 4  | Bit 3 | Bit 2         | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------------------------------------------------|----------|---------------------------------------------|-------|--------|-------|---------------|-------|-----------|-------------------------------|-----------------------------------------|

| 05h, Unbanked | TOSTA                                            | INTEDG   | T0SE                                        | TOCS  | PS3    | PS2   | PS1           | PS0   |           | 0000 000-                     | 0000 000-                               |

| 06h, Unbanked | CPUSTA                                           | —        | _                                           | STKAV | GLINTD | TO    | PD            | _     | _         | 11 11                         | 11 qq                                   |

| 07h, Unbanked | INTSTA                                           | PEIF     | TOCKIF                                      | T0IF  | INTF   | PEIE  | <b>T0CKIE</b> | TOIE  | INTE      | 0000 0000                     | 0000 0000                               |

| 0Bh, Unbanked | d TMROL TMRO register; low byte xxxx xxxx uuuu u |          |                                             |       |        |       |               |       | uuuu uuuu |                               |                                         |

| 0Ch, Unbanked | TMR0H                                            | TMR0 reg | IRO register; high byte xxxx xxxx uuuu uuuu |       |        |       |               |       |           |                               |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', g - value depends on condition, Shaded cells are not used by Timer0. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

### 14.1 Configuration Bits

The PIC17CXX has up to seven configuration locations (Table 14-1). These locations can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. Any write to a configuration location, regardless of the data, will program that configuration bit. A TABLWT instruction is required to write to program memory locations. The configuration bits can be read by using the TABLRD instructions. Reading any configuration location between FE00h and FE07h will read the low byte of the configuration word (Figure 14-1) into the TABLATL register. The TABLATH register will be FFh. Reading a configuration location between FE08h and FE0Fh will read the high byte of the configuration word into the TABLATL register. The TABLATH register will be FFh.

Addresses FE00h thorough FE0Fh are only in the program memory space for microcontroller and code protected microcontroller modes. A device programmer will be able to read the configuration word in any processor mode. See programming specifications for more detail.

### TABLE 14-1: CONFIGURATION LOCATIONS

| Bit                | Address              |

|--------------------|----------------------|

| FOSC0              | FE00h                |

| FOSC1              | FE01h                |

| WDTPS0             | FE02h                |

| WDTPS1             | FE03h                |

| PM0                | FE04h                |

| PM1                | FE06h                |

| PM2 <sup>(1)</sup> | FE0Fh <sup>(1)</sup> |

Note 1: This location does not exist on the PIC17C42.

| Note: | When programming the desired configura- |          |           |        |         |  |

|-------|-----------------------------------------|----------|-----------|--------|---------|--|

|       | tion location                           | ns, they | must be p | orogra | mmed in |  |

|       | ascending                               | order.   | Starting  | with   | address |  |

|       | FE00h.                                  |          |           |        |         |  |

### 14.2 Oscillator Configurations

### 14.2.1 OSCILLATOR TYPES

The PIC17CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LF: Low Power Crystal

- XT: Crystal/Resonator

- EC: External Clock Input

- RC: Resistor/Capacitor

### 14.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

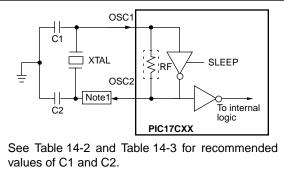

In XT or LF modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 14-2). The PIC17CXX Oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications.

For frequencies above 20 MHz, it is common for the crystal to be an overtone mode crystal. Use of overtone mode crystals require a tank circuit to attenuate the gain at the fundamental frequency. Figure 14-3 shows an example of this.

### FIGURE 14-2: CRYSTAL OR CERAMIC RESONATOR OPERATION (XT OR LF OSC CONFIGURATION)

Note 1: A series resistor may be required for AT strip cut crystals.

| DCF                                                                                | SNZ                     | Decreme                                                  | ent f, skij                                                                             | o if no                                            | ot O                                                                    |  |

|------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------|--|

| Synt                                                                               | tax:                    | [ <i>label</i> ] D                                       | CFSNZ                                                                                   | f,d                                                |                                                                         |  |

| Ope                                                                                | rands:                  | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]                                                                |                                                    |                                                                         |  |

| Ope                                                                                | ration:                 | (f) – 1 $\rightarrow$ skip if not                        | • • •                                                                                   |                                                    |                                                                         |  |

| Stat                                                                               | us Affected:            | None                                                     |                                                                                         |                                                    |                                                                         |  |

| Enc                                                                                | oding:                  | 0010                                                     | 011d                                                                                    | ffff                                               | ffff                                                                    |  |

| Des                                                                                | cription:               | WREG. If '<br>back in reg<br>If the resul<br>which is al | 'd' is 0 the<br>d' is 1 the<br>gister 'f'.<br>t is not 0, t<br>ready fetc<br>DP is exec | e result<br>result<br>he nex<br>hed, is<br>uted in | is placed in<br>is placed<br>t instruction,<br>discarded,<br>stead mak- |  |

| Wor                                                                                | ds:                     | 1                                                        |                                                                                         |                                                    |                                                                         |  |

| Cycl                                                                               | es:                     | 1(2)                                                     |                                                                                         |                                                    |                                                                         |  |

| QC                                                                                 | ycle Activity:          |                                                          |                                                                                         |                                                    |                                                                         |  |

|                                                                                    | Q1                      | Q2                                                       | Q3                                                                                      |                                                    | Q4                                                                      |  |

|                                                                                    | Decode                  | Read<br>register 'f'                                     | Execu                                                                                   | ıte                                                | Write to destination                                                    |  |

| lf sk                                                                              | ip:                     |                                                          |                                                                                         |                                                    |                                                                         |  |

|                                                                                    | Q1                      | Q2                                                       | Q3                                                                                      |                                                    | Q4                                                                      |  |

|                                                                                    | Forced NOP              | NOP                                                      | Execu                                                                                   | ute                                                | NOP                                                                     |  |

| <u>Exa</u>                                                                         | <u>mple</u> :           | HERE<br>ZERO<br>NZERO                                    | DCFSNZ<br>:<br>:                                                                        | TEMP                                               | P, 1                                                                    |  |

|                                                                                    | Before Instru<br>TEMP_V |                                                          | ?                                                                                       |                                                    |                                                                         |  |

| After Instructio<br>TEMP_VAL<br>If TEMP_V/<br>If TEMP_V/<br>PC<br>If TEMP_V/<br>PC |                         | ALUE =<br>VALUE =<br>=                                   | 0;<br>Addre:<br>0;                                                                      | _VALU<br>ss (ze<br>ss (nz                          | RO)                                                                     |  |

| Syntax:<br>Operand | de.         | [ label ]                                                                           | 0010                                             |                                     |                                  |

|--------------------|-------------|-------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------|----------------------------------|

| Operand            | 18.         | $0 \le k \le 81$                                                                    | ~                                                | i.                                  |                                  |

|                    |             |                                                                                     | •                                                |                                     |                                  |

| Operatio           | on:         | k → PC<1<br>k<12:8> -<br>PC<15:13                                                   | → PCLA                                           |                                     | ,                                |

| Status A           | Affected:   | None                                                                                |                                                  |                                     |                                  |

| Encodin            | ig:         | 110k                                                                                | kkkk                                             | kkkk                                | kkkl                             |

| Descript           |             | anywhere w<br>The thirtee<br>loaded into<br>upper eigh<br>PCLATH. o<br>instruction. | n bit imm<br>PC bits<br>t bits of P<br>30T0 is a | ediate va<br><12:0>. 1<br>C are loa | alue is<br>Then the<br>aded into |

| Words:             |             | 1                                                                                   |                                                  |                                     |                                  |

| Cycles:            |             | 2                                                                                   |                                                  |                                     |                                  |

| Q Cycle            | Activity:   |                                                                                     |                                                  |                                     |                                  |

|                    | Q1          | Q2                                                                                  | Q3                                               | 5                                   | Q4                               |

| C                  | Decode      | Read literal<br>'k'<7:0>                                                            | Execu                                            | ute                                 | NOP                              |

| For                | ced NOP     | NOP                                                                                 | Execu                                            | ute                                 | NOP                              |

| Example            | <u>e</u> :  | GOTO THE                                                                            | RE                                               |                                     |                                  |

| Afte               | er Instruct | tion                                                                                |                                                  |                                     |                                  |

|                    | PC =        | Address (TH                                                                         | HERE )                                           |                                     |                                  |

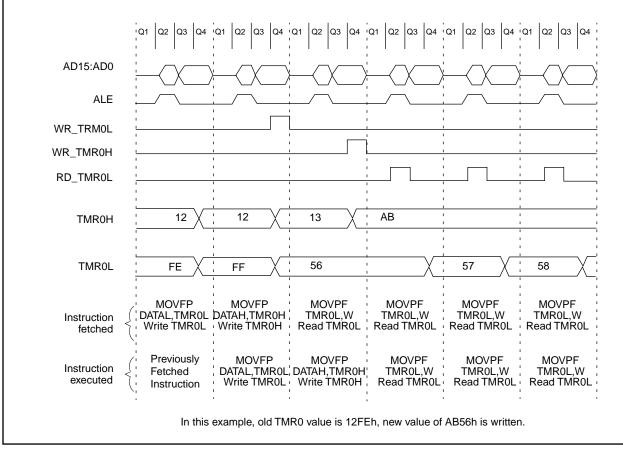

| MOVPF                         | Move p to f                                                                                                                                                                                  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                       | [ <i>label</i> ] MOVPF p,f                                                                                                                                                                   |

| Operands:                     | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq p \leq 31 \end{array}$                                                                                                                         |

| Operation:                    | $(p) \rightarrow (f)$                                                                                                                                                                        |

| Status Affected:              | Z                                                                                                                                                                                            |

| Encoding:                     | 010p pppp ffff ffff                                                                                                                                                                          |

| Description:                  | Move data from data memory location<br>'p' to data memory location 'f'. Location<br>'f' can be anywhere in the 256 byte data<br>space (00h to FFh) while 'p' can be 00h<br>to 1Fh.           |

|                               | Either 'p' or 'f' can be WREG (a useful special situation).                                                                                                                                  |

|                               | MOVPF is particularly useful for transfer-<br>ring a peripheral register (e.g. the timer<br>or an I/O port) to a data memory loca-<br>tion. Both 'f' and 'p' can be indirectly<br>addressed. |

| Words:                        | 1                                                                                                                                                                                            |

| Cycles:                       | 1                                                                                                                                                                                            |

| Q Cycle Activity:             |                                                                                                                                                                                              |

| Q1                            | Q2 Q3 Q4                                                                                                                                                                                     |

| Decode                        | ReadExecuteWriteregister 'p'register 'f'                                                                                                                                                     |

| Example:                      | MOVPF REG1, REG2                                                                                                                                                                             |

| Before Instru                 | iction                                                                                                                                                                                       |

| REG1<br>REG2                  | = 0x11<br>= 0x33                                                                                                                                                                             |

| After Instruc<br>REG1<br>REG2 | ion<br>= 0x11<br>= 0x11                                                                                                                                                                      |

| MO\        | /WF                          | Ν               | love WR            | EG to f                       |     |   |                     |

|------------|------------------------------|-----------------|--------------------|-------------------------------|-----|---|---------------------|

| Synt       | ax:                          | [ /             | label ]            | MOVWF                         | = f |   |                     |

| Ope        | rands:                       | 0               | ≤ f ≤ 25           | 5                             |     |   |                     |

| Ope        | ration:                      | (\              | VREG) ·            | $\rightarrow$ (f)             |     |   |                     |

| State      | us Affected:                 | N               | one                |                               |     |   |                     |

| Enco       | oding:                       |                 | 0000               | 0001                          | fff | f | ffff                |

| Des        | cription:                    | Lo              |                    | from WR<br>can be a<br>space. |     | • |                     |

| Wor        | ds:                          | 1               |                    |                               |     |   |                     |

| Cycl       | es:                          | 1               |                    |                               |     |   |                     |

| QC         | ycle Activity:               |                 |                    |                               |     |   |                     |

|            | Q1                           |                 | Q2                 | Q3                            | 3   |   | Q4                  |

|            | Decode                       |                 | Read<br>gister 'f' | Execu                         | ute |   | Write<br>gister 'f' |

| <u>Exa</u> | <u>mple</u> :                | M               | OVWF               | REG                           |     |   |                     |

|            | Before Instru<br>WREG<br>REG | uctio<br>=<br>= | n<br>0x4F<br>0xFF  |                               |     |   |                     |

|            | After Instruc<br>WREG<br>REG | tion<br>=<br>=  | 0x4F<br>0x4F       |                               |     |   |                     |

| RLNCF             | Rotate L                    | Rotate Left f (no carry)                                                                   |                                    |  |  |  |

|-------------------|-----------------------------|--------------------------------------------------------------------------------------------|------------------------------------|--|--|--|

| Syntax:           | [ label ]                   | RLNCF f,d                                                                                  |                                    |  |  |  |

| Operands:         | 0 ≤ f ≤ 25<br>d ∈ [0,1]     | $0 \le f \le 255$<br>$d \in [0,1]$                                                         |                                    |  |  |  |

| Operation:        |                             | $f < n > \rightarrow d < n+1 >;$<br>$f < 7 > \rightarrow d < 0 >$                          |                                    |  |  |  |

| Status Affected:  | None                        |                                                                                            |                                    |  |  |  |

| Encoding:         | 0010                        | 001d ff                                                                                    | ff ffff                            |  |  |  |

| Description:      | one bit to t<br>placed in \ | nts of register<br>the left. If 'd' is<br>WREG. If 'd' is<br>k in register 'f'<br>register | 0 the result is<br>1 the result is |  |  |  |

| Words:            | 1                           |                                                                                            |                                    |  |  |  |

| Cycles:           | 1                           |                                                                                            |                                    |  |  |  |

| Q Cycle Activity: |                             |                                                                                            |                                    |  |  |  |

| Q1                | Q2                          | Q3                                                                                         | Q4                                 |  |  |  |

| Decode            | Read<br>register 'f'        | Execute                                                                                    | Write to destination               |  |  |  |

| Example:          | RLNCF                       | REG, 1                                                                                     |                                    |  |  |  |

| Before Instr      | uction                      |                                                                                            |                                    |  |  |  |

| C<br>REG          | = 0<br>= 1110 1             | .011                                                                                       |                                    |  |  |  |

| After Instruc     | tion                        |                                                                                            |                                    |  |  |  |

| RRCF Rotate Right f through Carry  |                                                                                                                                                                                                    |  |  |  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                            | [ label ] RRCF f,d                                                                                                                                                                                 |  |  |  |

| Operands:                          | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$                                                                                                                                  |  |  |  |

| Operation:                         | $f < n > \rightarrow d < n-1 >;$<br>$f < 0 > \rightarrow C;$<br>$C \rightarrow d < 7 >$                                                                                                            |  |  |  |

| Status Affected:                   | С                                                                                                                                                                                                  |  |  |  |

| Encoding:                          | 0001 100d ffff ffff                                                                                                                                                                                |  |  |  |

| Description:                       | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'. |  |  |  |

| Words:                             | 1                                                                                                                                                                                                  |  |  |  |

| Cycles:                            | 1                                                                                                                                                                                                  |  |  |  |

| Q Cycle Activity:                  |                                                                                                                                                                                                    |  |  |  |

| Q1                                 | Q2 Q3 Q4                                                                                                                                                                                           |  |  |  |

| Decode                             | Read         Execute         Write to           register 'f'         destination                                                                                                                   |  |  |  |

| Example:                           | RRCF REG1,0                                                                                                                                                                                        |  |  |  |

| Before Instr                       | uction                                                                                                                                                                                             |  |  |  |

| REG1<br>C                          | = 1110 0110<br>= 0                                                                                                                                                                                 |  |  |  |

| After Instruc<br>REG1<br>WREG<br>C | tion<br>= 1110 0110<br>= 0111 0011<br>= 0                                                                                                                                                          |  |  |  |

| SWAPF                            | Swap f                                                            |                                                                                                                                                                 |      |                       |  |  |

|----------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|--|--|

| Syntax:                          | [label]                                                           | SWAPF                                                                                                                                                           | f,d  |                       |  |  |

| Operands:                        | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ | 0 ≤ f ≤ 255<br>d ∈ [0,1]                                                                                                                                        |      |                       |  |  |

| Operation:                       | $f < 3:0 > \rightarrow f < 7:4 > \rightarrow$                     |                                                                                                                                                                 | ,    |                       |  |  |

| Status Affected:                 | None                                                              |                                                                                                                                                                 |      |                       |  |  |

| Encoding:                        | 0001                                                              | 110d                                                                                                                                                            | ffff | ffff                  |  |  |

| Description:                     | 'f' are excha<br>placed in V                                      | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in WREG. If 'd' is 1 the result is<br>placed in register 'f'. |      |                       |  |  |

| Words:                           | 1                                                                 |                                                                                                                                                                 |      |                       |  |  |

| Cycles:                          | 1                                                                 |                                                                                                                                                                 |      |                       |  |  |

| Q Cycle Activity:                |                                                                   |                                                                                                                                                                 |      |                       |  |  |

| Q1                               | Q2                                                                | Q                                                                                                                                                               | 3    | Q4                    |  |  |

| Decode                           | Read<br>register 'f'                                              | Exect                                                                                                                                                           |      | Vrite to<br>stination |  |  |

| Example: SWAPF REG, 0            |                                                                   |                                                                                                                                                                 |      |                       |  |  |

| Before Instruction<br>REG = 0x53 |                                                                   |                                                                                                                                                                 |      |                       |  |  |

| After Instruction<br>REG = 0x35  |                                                                   |                                                                                                                                                                 |      |                       |  |  |

| TABLRD            | Table Rea                                                                                                                                                            | ad                                                                                                                                                                 |      |                     |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|--|--|

| Syntax:           | [ label ] TABLRD t,i,f                                                                                                                                               |                                                                                                                                                                    |      |                     |  |  |

| Operands:         | $0 \le f \le 255$<br>i $\in [0,1]$<br>t $\in [0,1]$                                                                                                                  |                                                                                                                                                                    |      |                     |  |  |

| Operation:        | If t = 1,<br>TBLATH $\rightarrow$ f;<br>If t = 0,<br>TBLATL $\rightarrow$ f;<br>Prog Mem (TBLPTR) $\rightarrow$ TBLA<br>If i = 1,<br>TBLPTR + 1 $\rightarrow$ TBLPTR |                                                                                                                                                                    |      |                     |  |  |

| Status Affected:  | None                                                                                                                                                                 |                                                                                                                                                                    |      |                     |  |  |

| Encoding:         | 1010                                                                                                                                                                 | 10ti                                                                                                                                                               | ffff | ffff                |  |  |

| Description:      | is mov<br>If t = 0                                                                                                                                                   | <ol> <li>A byte of the table latch (TBLAT)<br/>is moved to register file 'f'.<br/>If t = 0: the high byte is moved;<br/>If t = 1: the low byte is moved</li> </ol> |      |                     |  |  |

|                   | memo<br>the<br>(TBLP<br>16-bit<br>3. If i = 1                                                                                                                        | memory location pointed to by<br>the 16-bit Table Pointer<br>(TBLPTR) is loaded into the<br>16-bit Table Latch (TBLAT).                                            |      |                     |  |  |

|                   |                                                                                                                                                                      | increme                                                                                                                                                            |      |                     |  |  |

| Words:            | 1                                                                                                                                                                    |                                                                                                                                                                    |      |                     |  |  |

| Cycles:           | 2 (3 cycle                                                                                                                                                           | if f = PC                                                                                                                                                          | L)   |                     |  |  |

| Q Cycle Activity: |                                                                                                                                                                      |                                                                                                                                                                    |      |                     |  |  |

| Q1                | Q2                                                                                                                                                                   | Q3                                                                                                                                                                 |      | Q4                  |  |  |

| Decode            | Read<br>register<br>TBLATH or<br>TBLATL                                                                                                                              | Execu                                                                                                                                                              |      | Write<br>gister 'f' |  |  |

Applicable Devices 42 R42 42A 43 R43 44

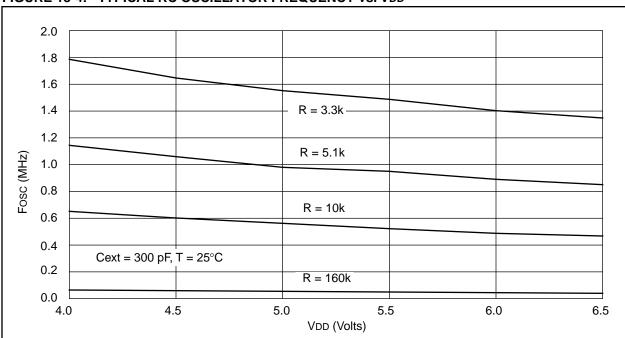

### FIGURE 18-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

### TABLE 18-2: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average<br>Fosc @ 5V, 25°C |       |

|--------|------|----------------------------|-------|

| 22 pF  | 10k  | 3.33 MHz                   | ± 12% |

|        | 100k | 353 kHz                    | ± 13% |

| 100 pF | 3.3k | 3.54 MHz                   | ± 10% |

|        | 5.1k | 2.43 MHz                   | ± 14% |

|        | 10k  | 1.30 MHz                   | ± 17% |

|        | 100k | 129 kHz                    | ± 10% |

| 300 pF | 3.3k | 1.54 MHz                   | ± 14% |

|        | 5.1k | 980 kHz                    | ± 12% |

|        | 10k  | 564 kHz                    | ± 16% |

|        | 160k | 35 kHz                     | ± 18% |

NOTES:

Applicable Devices 42 R42 42A 43 R43 44

### 19.0 PIC17CR42/42A/43/R43/44 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings †

| 5                                                                                                           |                                    |

|-------------------------------------------------------------------------------------------------------------|------------------------------------|

| Ambient temperature under bias                                                                              | 55 to +125°C                       |

| Storage temperature                                                                                         | 65°C to +150°C                     |

| Voltage on VDD with respect to Vss                                                                          | 0 to +7.5V                         |

| Voltage on MCLR with respect to Vss (Note 2)                                                                | 0.6V to +14V                       |

| Voltage on RA2 and RA3 with respect to Vss                                                                  | 0.6V to +14V                       |

| Voltage on all other pins with respect to Vss                                                               | 0.6V to VDD + 0.6V                 |

| Total power dissipation (Note 1)                                                                            | 1.0W                               |

| Maximum current out of Vss pin(s) - total                                                                   | 250 mA                             |

| Maximum current into VDD pin(s) - total                                                                     | 200 mA                             |

| Input clamp current, IiK (VI < 0 or VI > VDD)                                                               | ±20 mA                             |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              | ±20 mA                             |

| Maximum output current sunk by any I/O pin (except RA2 and RA3)                                             | 35 mA                              |

| Maximum output current sunk by RA2 or RA3 pins                                                              |                                    |

| Maximum output current sourced by any I/O pin                                                               | 20 mA                              |

| Maximum current sunk by PORTA and PORTB (combined)                                                          | 150 mA                             |

| Maximum current sourced by PORTA and PORTB (combined)                                                       | 100 mA                             |

| Maximum current sunk by PORTC, PORTD and PORTE (combined)                                                   | 150 mA                             |

| Maximum current sourced by PORTC, PORTD and PORTE (combined)                                                | 100 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-V | 'OH) x IOH} + $\Sigma$ (VOL x IOL) |

|                                                                                                             |                                    |

**Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### Applicable Devices 42 R42 42A 43 R43 44

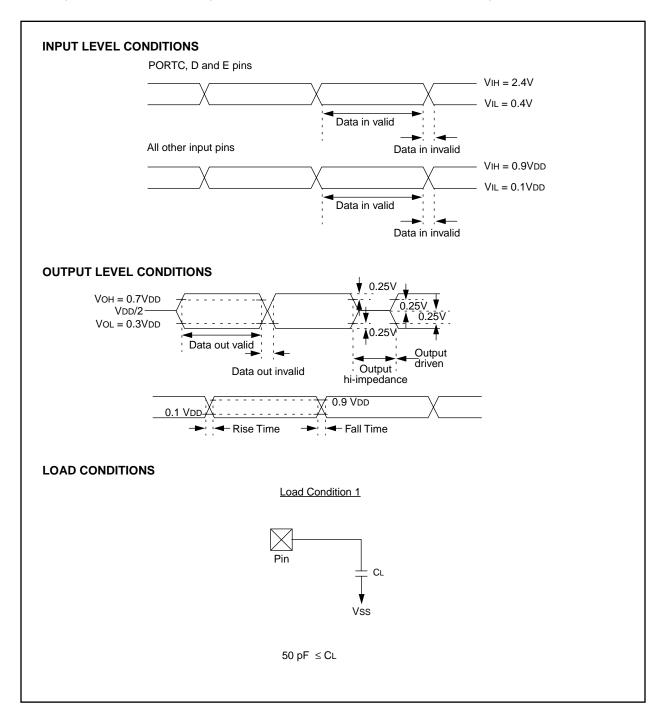

### FIGURE 19-1: PARAMETER MEASUREMENT INFORMATION

All timings are measure between high and low measurement points as indicated in the figures below.

Applicable Devices 42 R42 42A 43 R43 44

### 20.0 PIC17CR42/42A/43/R43/44 DC AND AC CHARACTERISTICS

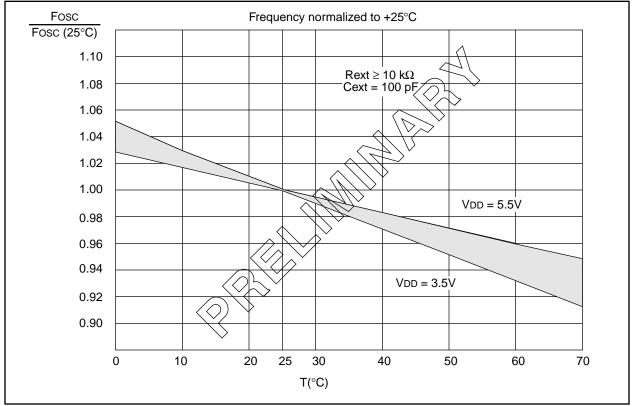

The graphs and tables provided in this section are for design guidance and are not tested nor guaranteed. In some graphs or tables the data presented is outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are ensured to operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

### TABLE 20-1: PIN CAPACITANCE PER PACKAGE TYPE

| Din Nama                               | Typical Capacitance (pF) |             |             |             |  |

|----------------------------------------|--------------------------|-------------|-------------|-------------|--|

| Pin Name                               | 40-pin DIP               | 44-pin PLCC | 44-pin MQFP | 44-pin TQFP |  |

| All pins, except MCLR,<br>VDD, and Vss | 10                       | 10          | 10          | 10          |  |

| MCLR pin                               | 20                       | 20          | 20          | 20          |  |

### FIGURE 20-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

### **PIC17C4X Product Identification System**

To order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers, and refer to the factory or the listed sales offices.

| PART NO. – XX X /XX XXX |                                                                                                                                                                                 | Examples                                                                                   |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|