#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 33MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 232 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

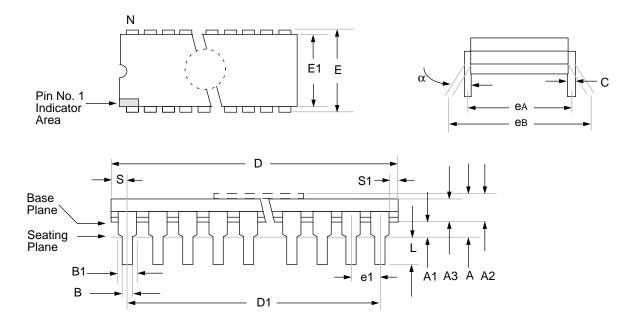

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42a-33i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

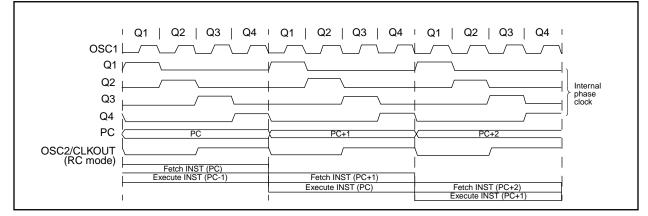

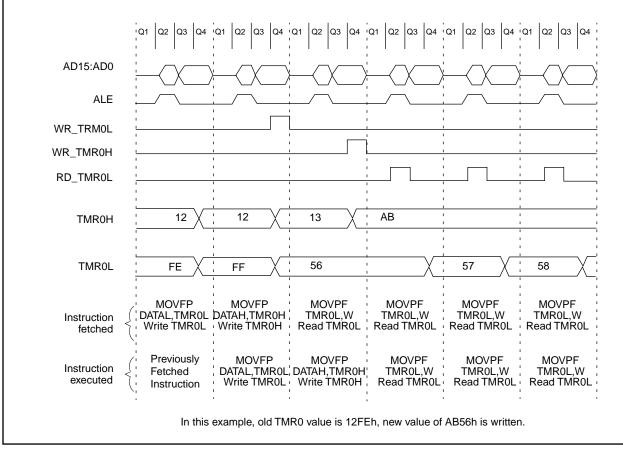

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-3.

#### 3.2 Instruction Flow/Pipelining

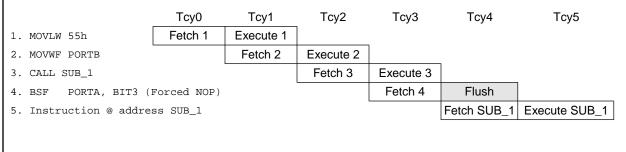

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g.GOTO) then two cycles are required to complete the instruction (Example 3-2).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-2: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### 5.2 <u>Peripheral Interrupt Enable Register</u> (PIE)

This register contains the individual flag bits for the Peripheral interrupts.

# FIGURE 5-3: PIE REGISTER (ADDRESS: 17h, BANK 1)

| RBIE   | 0 R/W - 0 R/W<br>TMR3IE TMR2IE TMR1IE CA2IE CA1IE TXIE R0                                              | CIE R = Readable bit                             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| bit7   |                                                                                                                                                | bit0 W = Writable bit<br>-n = Value at POR reset |

| bit 7: | <b>RBIE</b> : PORTB Interrupt on Change Enable bit<br>1 = Enable PORTB interrupt on change<br>0 = Disable PORTB interrupt on change            |                                                  |

| bit 6: | <b>TMR3IE</b> : Timer3 Interrupt Enable bit<br>1 = Enable Timer3 interrupt<br>0 = Disable Timer3 interrupt                                     |                                                  |

| bit 5: | <b>TMR2IE</b> : Timer2 Interrupt Enable bit<br>1 = Enable Timer2 interrupt<br>0 = Disable Timer2 interrupt                                     |                                                  |

| bit 4: | <b>TMR1IE</b> : Timer1 Interrupt Enable bit<br>1 = Enable Timer1 interrupt<br>0 = Disable Timer1 interrupt                                     |                                                  |

| bit 3: | <b>CA2IE</b> : Capture2 Interrupt Enable bit<br>1 = Enable Capture interrupt on RB1/CAP2 pin<br>0 = Disable Capture interrupt on RB1/CAP2 pin  |                                                  |

| bit 2: | <b>CA1IE</b> : Capture1 Interrupt Enable bit<br>1 = Enable Capture interrupt on RB2/CAP1 pin<br>0 = Disable Capture interrupt on RB2/CAP1 pin  |                                                  |

| bit 1: | <b>TXIE</b> : USART Transmit Interrupt Enable bit<br>1 = Enable Transmit buffer empty interrupt<br>0 = Disable Transmit buffer empty interrupt |                                                  |

| bit 0: | <b>RCIE</b> : USART Receive Interrupt Enable bit<br>1 = Enable Receive buffer full interrupt<br>0 = Disable Receive buffer full interrupt      |                                                  |

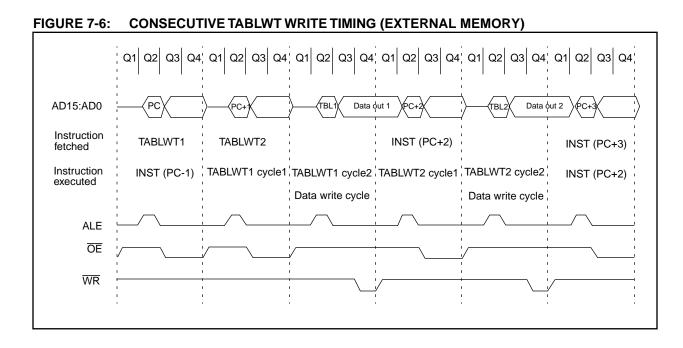

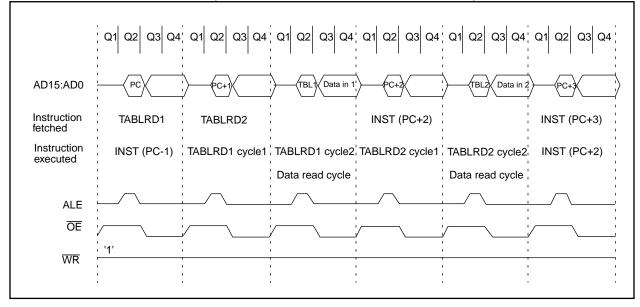

#### 7.3 <u>Table Reads</u>

FIGURE 7-7:

The table read allows the program memory to be read. This allows constant data to be stored in the program memory space, and retrieved into data memory when needed. Example 7-2 reads the 16-bit value at program memory address TBLPTR. After the dummy byte has been read from the TABLATH, the TABLATH is loaded with the 16-bit data from program memory address TBLPTR + 1. The first read loads the data into the latch, and can be considered a dummy read (unknown data loaded into 'f'). INDF0 should be configured for either auto-increment or auto-decrement.

# + 1. The first read loads the data into TABLRD 0,1,INDF0 ; Read LO byte ; of TABLATCH and ; of TABLATCH and ; Update TABLATCH auto-increment or auto-decrement.

MOVLW

MOVWF

MOVLW

MOVWF

TLRD

TABLRD

EXAMPLE 7-2: TABLE READ

LOW (TBL\_ADDR)

TBLPTRH

TBLPTRL

0,0,DUMMY

1, INDF0

HIGH (TBL\_ADDR) ; Load the Table

;

;

;

;

address

; Dummy read,

; Read HI byte

; Updates TABLATCH

of TABLATCH

#### Q4 | AD15:AD0 Data in PC PC-TBL PC4 Instruction TABLRD INST (PC+1) INST (PC+2) fetched Instruction INST (PC-1) TABLRD cycle1 TABLRD cycle2 INST (PC+1) executed Data read cycle ALE ŌĒ $\overline{\mathsf{WR}}$

#### FIGURE 7-8: TABLRD TIMING (CONSECUTIVE TABLRD INSTRUCTIONS)

DS30412C-page 48

Example 9-1 shows the instruction sequence to initialize PORTB. The Bank Select Register (BSR) must be selected to Bank 0 for the port to be initialized.

#### EXAMPLE 9-1: INITIALIZING PORTB

| MOVLB | 0     | ; | Select Bank 0                |

|-------|-------|---|------------------------------|

| CLRF  | PORTB | ; | Initialize PORTB by clearing |

|       |       | ; | output data latches          |

| MOVLW | 0xCF  | ; | Value used to initialize     |

|       |       | ; | data direction               |

| MOVWF | DDRB  | ; | Set RB<3:0> as inputs        |

|       |       | ; | RB<5:4> as outputs           |

|       |       | ; | RB<7:6> as inputs            |

|       |       |   |                              |

| Name       | Bit  | Buffer Type | Function                                                                                                                                 |

|------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/CAP1   | bit0 | ST          | Input/Output or the RB0/CAP1 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB1/CAP2   | bit1 | ST          | Input/Output or the RB1/CAP2 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB2/PWM1   | bit2 | ST          | Input/Output or the RB2/PWM1 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB3/PWM2   | bit3 | ST          | Input/Output or the RB3/PWM2 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB4/TCLK12 | bit4 | ST          | Input/Output or the external clock input to Timer1 and Timer2. Software pro-<br>grammable weak pull-up and interrupt on change features. |

| RB5/TCLK3  | bit5 | ST          | Input/Output or the external clock input to Timer3. Software programmable weak pull-up and interrupt on change features.                 |

| RB6        | bit6 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

| RB7        | bit7 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

### TABLE 9-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger input.

#### TABLE 9-4: REGISTERS/BITS ASSOCIATED WITH PORTB

| Address       | Name   | Bit 7      | Bit 6         | Bit 5        | Bit 4  | Bit 3   | Bit 2  | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets<br>(Note1) |

|---------------|--------|------------|---------------|--------------|--------|---------|--------|-----------|---------|-------------------------------|--------------------------------------------|

| 12h, Bank 0   | PORTB  | PORTB d    | ata latch     |              |        |         |        |           |         | xxxx xxxx                     | uuuu uuuu                                  |

| 11h, Bank 0   | DDRB   | Data dired | ction registe | er for PORTE | 5      |         |        |           |         | 1111 1111                     | 1111 1111                                  |

| 10h, Bank 0   | PORTA  | RBPU       | _             | RA5          | RA4    | RA3     | RA2    | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                                  |

| 06h, Unbanked | CPUSTA | —          | _             | STKAV        | GLINTD | TO      | PD     | _         | _       | 11 11                         | 11 qq                                      |

| 07h, Unbanked | INTSTA | PEIF       | <b>T0CKIF</b> | T0IF         | INTF   | PEIE    | T0CKIE | T0IE      | INTE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF        | TMR2IF       | TMR1IF | CA2IF   | CA1IF  | TXIF      | RCIF    | 0000 0010                     | 0000 0010                                  |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE        | TMR2IE       | TMR1IE | CA2IE   | CA1IE  | TXIE      | RCIE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0        | CA1ED1       | CA1ED0 | T16     | TMR3CS | TMR2CS    | TMR1CS  | 0000 0000                     | 0000 0000                                  |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF        | PWM2ON       | PWM10N | CA1/PR3 | TMR3ON | TMR2ON    | TMR10N  | 0000 0000                     | 0000 0000                                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = Value depends on condition.

Shaded cells are not used by PORTB.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

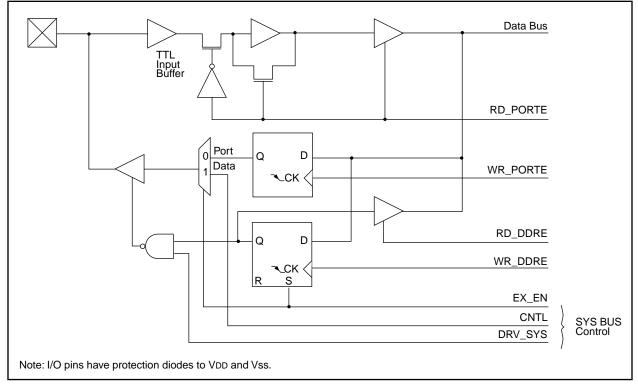

#### 9.4.1 PORTE AND DDRE REGISTER

PORTE is a 3-bit bi-directional port. The corresponding data direction register is DDRE. A '1' in DDRE configures the corresponding port pin as an input. A '0' in the DDRE register configures the corresponding port pin as an output. Reading PORTE reads the status of the pins, whereas writing to it will write to the port latch. PORTE is multiplexed with the system bus. When operating as the system bus, PORTE contains the control signals for the address/data bus (AD15:AD0). These control signals are Address Latch Enable (ALE), Output Enable ( $\overline{OE}$ ), and Write ( $\overline{WR}$ ). The control signals  $\overline{OE}$  and  $\overline{WR}$  are active low signals. The timing for the system bus is shown in the Electrical Characteristics section.

Note: This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-4 shows the instruction sequence to initialize PORTE. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-4: INITIALIZING PORTE

| MOVLB | 1     | ; | Select Bank 1            |

|-------|-------|---|--------------------------|

| CLRF  | PORTE | ; | Initialize PORTE data    |

|       |       | ; | latches before setting   |

|       |       | ; | the data direction       |

|       |       | ; | register                 |

| MOVLW | 0x03  | ; | Value used to initialize |

|       |       | ; | data direction           |

| MOVWF | DDRE  | ; | Set RE<1:0> as inputs    |

|       |       | ; | RE<2> as outputs         |

|       |       | ; | RE<7:3> are always       |

|       |       | ; | read as '0'              |

#### FIGURE 9-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Address       | Name   | Bit 7    | Bit 6                                        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------|----------|----------------------------------------------|-------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 05h, Unbanked | TOSTA  | INTEDG   | T0SE                                         | TOCS  | PS3    | PS2   | PS1   | PS0   |       | 0000 000-                     | 0000 000-                               |

| 06h, Unbanked | CPUSTA | —        | _                                            | STKAV | GLINTD | TO    | PD    | _     | _     | 11 11                         | 11 qq                                   |

| 07h, Unbanked | INTSTA | PEIF     | EIF TOCKIF TOIF INTE PEIE TOCKIE TOIE INTE O |       |        |       |       |       |       | 0000 0000                     | 0000 0000                               |

| 0Bh, Unbanked | TMR0L  | TMR0 reg | MR0 register; low byte xxxx xxxx uuuu uuuu   |       |        |       |       |       |       |                               |                                         |

| 0Ch, Unbanked | TMR0H  | TMR0 reg | IRO register; high byte xxxx xxxx uuuu uuuu  |       |        |       |       |       |       |                               |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', g - value depends on condition, Shaded cells are not used by Timer0. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

# 14.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real time applications. The PIC17CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- OSC selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- · Code protection

The PIC17CXX has a Watchdog Timer which can be shut off only through EPROM bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 96 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

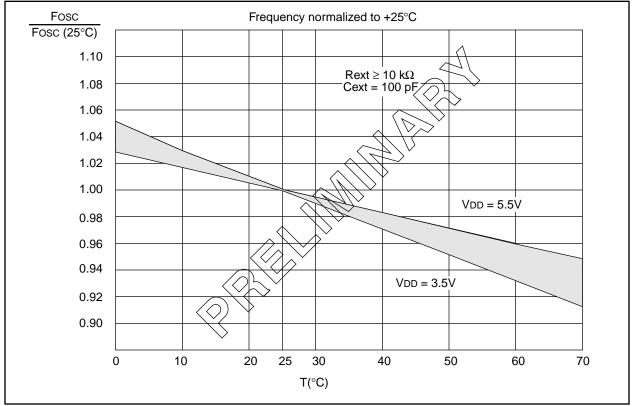

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake from SLEEP through external reset, Watchdog Timer Reset or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LF crystal option saves power. Configuration bits are used to select various options. This configuration word has the format shown in Figure 14-1.

| <u>R/P - 1</u><br>PM2 <sup>(1)</sup> | U - x                                                       | U - x                                  | <u>U-x</u>                             | U - x       | U - x   | <u>U-x</u> | U - x         |                                                                                                                 |

|--------------------------------------|-------------------------------------------------------------|----------------------------------------|----------------------------------------|-------------|---------|------------|---------------|-----------------------------------------------------------------------------------------------------------------|

| bit15-7                              |                                                             |                                        | _                                      |             |         |            | bit0          |                                                                                                                 |

| U - x                                | R/P - 1                                                     | U - x                                  | <u>R/P - 1</u>                         | R/P - 1     | R/P - 1 | R/P - 1    | R/P - 1       | R = Readable bit                                                                                                |

| <br>bit15-7                          | PM1                                                         |                                        | PM0                                    | WDTPS1      | WDTPS0  | FOSC1      | FOSC0<br>bit0 | P = Programmable bit $P = Programmable bit$ $U = Unimplemented$ $- n = Value for Erased Device$ $(x = unknown)$ |

| bit 15-9:                            | Unimpler                                                    | nented: R                              | ead as a                               | '1'         |         |            |               |                                                                                                                 |

|                                      |                                                             | rocontrolle<br>ended mic<br>de protect | er mode<br>crocontrol<br>ed microc     | ontroller m | ode     |            |               |                                                                                                                 |

| bit 7, 5:                            | Unimpler                                                    | nented: R                              | ead as a                               | '0'         |         |            |               |                                                                                                                 |

| bit 3-2:                             | 11 = WD<br>10 = WD<br>01 = WD                               | Γ enabled<br>Γ enabled<br>Γ enabled    | , postscal<br>, postscal<br>, postscal | er = 256    |         |            |               |                                                                                                                 |

| bit 1-0:                             | FOSC1:F<br>11 = EC (<br>10 = XT (<br>01 = RC (<br>00 = LF ( | oscillator<br>oscillator<br>oscillator | scillator S                            | elect bits  |         |            |               |                                                                                                                 |

|                                      |                                                             |                                        |                                        |             |         |            |               |                                                                                                                 |

#### FIGURE 14-1: CONFIGURATION WORD

<sup>© 1996</sup> Microchip Technology Inc.

# TABLE 15-2: PIC17CXX INSTRUCTION SET

| Mnemonic, |          | Description                           | Cycles | 16-bit Opcoo   | le    | Status<br>Affected | Notes |  |

|-----------|----------|---------------------------------------|--------|----------------|-------|--------------------|-------|--|

| Operands  | )perands |                                       |        | MSb            | b LSb |                    |       |  |

| BYTE-ORIE |          | TILE REGISTER OPERATIONS              | •      |                |       |                    | •     |  |

| ADDWF     | f,d      | ADD WREG to f                         | 1      | 0000 111d ffff | ffff  | OV,C,DC,Z          |       |  |

| ADDWFC    | f,d      | ADD WREG and Carry bit to f           | 1      | 0001 000d ffff | ffff  | OV,C,DC,Z          |       |  |

| ANDWF     | f,d      | AND WREG with f                       | 1      | 0000 101d ffff | ffff  | Z                  |       |  |

| CLRF      | f,s      | Clear f, or Clear f and Clear WREG    | 1      | 0010 100s ffff | ffff  | None               | 3     |  |

| COMF      | f,d      | Complement f                          | 1      | 0001 001d ffff | ffff  | Z                  |       |  |

| CPFSEQ    | f        | Compare f with WREG, skip if f = WREG | 1 (2)  | 0011 0001 ffff | ffff  | None               | 6,8   |  |

| CPFSGT    | f        | Compare f with WREG, skip if f > WREG | 1 (2)  | 0011 0010 ffff | ffff  | None               | 2,6,8 |  |

| CPFSLT    | f        | Compare f with WREG, skip if f < WREG | 1 (2)  | 0011 0000 ffff | ffff  | None               | 2,6,8 |  |

| DAW       | f,s      | Decimal Adjust WREG Register          | 1      | 0010 111s ffff | ffff  | C                  | 3     |  |

| DECF      | f,d      | Decrement f                           | 1      | 0000 011d ffff | ffff  | OV,C,DC,Z          |       |  |

| DECFSZ    | f,d      | Decrement f, skip if 0                | 1 (2)  | 0001 011d ffff | ffff  | None               | 6,8   |  |

| DCFSNZ    | f,d      | Decrement f, skip if not 0            | 1 (2)  | 0010 011d ffff | ffff  | None               | 6,8   |  |

| INCF      | f,d      | Increment f                           | 1      | 0001 010d ffff | ffff  | OV,C,DC,Z          |       |  |

| INCFSZ    | f,d      | Increment f, skip if 0                | 1 (2)  | 0001 111d ffff | ffff  | None               | 6,8   |  |

| INFSNZ    | f,d      | Increment f, skip if not 0            | 1 (2)  | 0010 010d ffff | ffff  | None               | 6,8   |  |

| IORWF     | f,d      | Inclusive OR WREG with f              | 1      | 0000 100d ffff | ffff  | Z                  |       |  |

| MOVFP     | f,p      | Move f to p                           | 1      | 011p pppp ffff | ffff  | None               |       |  |

| MOVPF     | p,f      | Move p to f                           | 1      | 010p pppp ffff | ffff  | Z                  |       |  |

| MOVWF     | f        | Move WREG to f                        | 1      | 0000 0001 ffff | ffff  | None               |       |  |

| MULWF     | f        | Multiply WREG with f                  | 1      | 0011 0100 ffff | ffff  | None               | 9     |  |

| NEGW      | f,s      | Negate WREG                           | 1      | 0010 110s ffff | ffff  | OV,C,DC,Z          | 1,3   |  |

| NOP       | —        | No Operation                          | 1      | 0000 0000 0000 | 0000  | None               |       |  |

| RLCF      | f,d      | Rotate left f through Carry           | 1      | 0001 101d ffff | ffff  | С                  |       |  |

| RLNCF     | f,d      | Rotate left f (no carry)              | 1      | 0010 001d ffff | ffff  | None               |       |  |

| RRCF      | f,d      | Rotate right f through Carry          | 1      | 0001 100d ffff | ffff  | C                  |       |  |

| RRNCF     | f,d      | Rotate right f (no carry)             | 1      | 0010 000d ffff | ffff  | None               |       |  |

| SETF      | f,s      | Set f                                 | 1      | 0010 101s ffff | ffff  | None               | 3     |  |

| SUBWF     | f,d      | Subtract WREG from f                  | 1      | 0000 010d ffff | ffff  | OV,C,DC,Z          | 1     |  |

| SUBWFB    | f,d      | Subtract WREG from f with Borrow      | 1      | 0000 001d ffff | ffff  | OV,C,DC,Z          | 1     |  |

| SWAPF     | f,d      | Swap f                                | 1      | 0001 110d ffff | ffff  | None               |       |  |

| TABLRD    | t,i,f    | Table Read                            | 2 (3)  | 1010 10ti ffff | ffff  | None               | 7     |  |

Legend: Refer to Table 15-1 for opcode field descriptions.

- Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- 5: Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

# PIC17C4X

| IORWF                    | Inclusive            |                                                   | with f               | LCALL             | Long Cal                                      | I                                                                                                                                         |                                  |  |  |

|--------------------------|----------------------|---------------------------------------------------|----------------------|-------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Syntax:                  | [label]              | ORWF f,d                                          |                      | Syntax:           | [ label ]                                     | LCALL k                                                                                                                                   |                                  |  |  |

| Operands:                | 0 ≤ f ≤ 255          | 5                                                 |                      | Operands:         | $0 \le k \le 25$                              | 5                                                                                                                                         |                                  |  |  |

|                          | d ∈ [0,1]            |                                                   |                      | Operation:        | PC + 1 $\rightarrow$                          | TOS;                                                                                                                                      |                                  |  |  |

| Operation:               | (WREG) .             | $OR.\left(f ight) ightarrow\left(de ight)$        | est)                 |                   | $k \rightarrow PCL$ ,                         | (PCLATH) -                                                                                                                                | → PCH                            |  |  |

| Status Affected:         | Z                    |                                                   |                      | Status Affected:  | None                                          |                                                                                                                                           |                                  |  |  |

| Encoding:                | 0000                 | 100d ff                                           | ff ffff              | Encoding:         | 1011                                          | 0111 kk                                                                                                                                   | kk kkkk                          |  |  |

| Description:             | 'd' is 0 the r       | R WREG with<br>esult is placed<br>esult is placed | 0                    | Description:      | tine call to a<br>gram memor<br>First, the re | LCALL allows an unconditional subr<br>tine call to anywhere within the 64k<br>gram memory space.<br>First, the return address (PC + 1) is |                                  |  |  |

| Words:                   | 1                    |                                                   |                      |                   | •                                             | to the stack. A ress is then lo                                                                                                           |                                  |  |  |

| Cycles:                  | 1                    |                                                   |                      |                   | program co                                    | ounter. The lo                                                                                                                            | wer 8-bits of                    |  |  |

| Q Cycle Activity:        |                      |                                                   |                      |                   |                                               |                                                                                                                                           | s embedded in<br>er 8-bits of PC |  |  |

| Q1                       | Q2                   | Q3                                                | Q4                   |                   |                                               | om PC high h                                                                                                                              |                                  |  |  |

| Decode                   | Read<br>register 'f' | Execute                                           | Write to destination |                   | PCLATH.                                       |                                                                                                                                           |                                  |  |  |

| Evemple:                 |                      |                                                   | uccundulori          | Words:            | 1                                             |                                                                                                                                           |                                  |  |  |

| Example:                 |                      | ESULT, O                                          |                      | Cycles:           | 2                                             |                                                                                                                                           |                                  |  |  |

| Before Instru<br>RESULT  |                      |                                                   |                      | Q Cycle Activity: |                                               |                                                                                                                                           |                                  |  |  |

| WREG                     | = 0x13<br>= 0x91     |                                                   |                      | Q1                | Q2                                            | Q3                                                                                                                                        | Q4                               |  |  |

| After Instruct<br>RESULT |                      |                                                   |                      | Decode            | Read<br>literal 'k'                           | Execute                                                                                                                                   | Write<br>register PCL            |  |  |

| WREG                     | = 0x13<br>= 0x93     |                                                   |                      | Forced NOP        | NOP                                           | Execute                                                                                                                                   | NOP                              |  |  |

|                          |                      |                                                   |                      | Example:          | MOVPF W                                       | IGH(SUBROU<br>REG, PCLAT<br>OW(SUBROUT                                                                                                    | Н                                |  |  |

**Before Instruction**

| SUBROUTINE<br>PC  | =<br>= | 16-bit Address<br>? |  |  |  |  |  |

|-------------------|--------|---------------------|--|--|--|--|--|

| After Instruction |        |                     |  |  |  |  |  |

| PC = Address | (SUBROUTINE) |

|--------------|--------------|

|--------------|--------------|

| MULLW                                                  | Multiply I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _iteral with V                                                                                                                                                                            | VREG                                                                                      | MULWF                                         | Multiply V                                                                                                                  | VREG with                                                                                                                                                                                                              | f                                                                                                              |  |  |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                                | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MULLW k                                                                                                                                                                                   |                                                                                           | Syntax:                                       | [ label ]                                                                                                                   | MULWF f                                                                                                                                                                                                                |                                                                                                                |  |  |

| Operands:                                              | $0 \le k \le 25$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                         |                                                                                           | Operands:                                     | $0 \le f \le 25$                                                                                                            | $0 \le f \le 255$                                                                                                                                                                                                      |                                                                                                                |  |  |

| Operation:                                             | (k x WRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | G) $\rightarrow$ PRODI                                                                                                                                                                    | H:PRODL                                                                                   | Operation:                                    | (WREG x                                                                                                                     | (WREG x f) $\rightarrow$ PRODH:PRODL                                                                                                                                                                                   |                                                                                                                |  |  |

| Status Affected:                                       | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                           |                                                                                           | Status Affected                               | : None                                                                                                                      | None                                                                                                                                                                                                                   |                                                                                                                |  |  |

| Encoding:                                              | 1011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1100 kk                                                                                                                                                                                   | kk kkkk                                                                                   | Encoding:                                     | 0011                                                                                                                        | 0100 ff                                                                                                                                                                                                                | Ef ffff                                                                                                        |  |  |

| Description:                                           | out betwee<br>and the 8-b<br>result is pla<br>register pai<br>high byte.<br>WREG is u<br>None of the<br>Note that n<br>is possible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ed multiplicatio<br>n the contents<br>bit literal 'k'. The<br>aced in PRODH<br>ir. PRODH con<br>unchanged.<br>e status flags a<br>either overflow<br>in this operatio<br>ssible but not o | of WREG<br>e 16-bit<br>H:PRODL<br>tains the<br>are affected.<br>/ nor carry<br>on. A zero | Description:                                  | out betwee<br>and the reg<br>16-bit resul<br>PRODH:PF<br>PRODH co<br>Both WREC<br>None of the<br>Note that n<br>is possible | ed multiplication<br>in the contents<br>gister file locati<br>t is stored in the<br>RODL register<br>ntains the hig<br>G and 'f' are un<br>e status flags a<br>either overflow<br>in this operations<br>ssible but not | s of WREG<br>ion 'f'. The<br>he<br>pair.<br>h byte.<br>nchanged.<br>are affected.<br>v nor carry<br>on. A zero |  |  |

| Words:                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                           |                                                                                           | Words:                                        | 1                                                                                                                           |                                                                                                                                                                                                                        |                                                                                                                |  |  |

| Cycles:                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                           |                                                                                           | Cycles:                                       | 1                                                                                                                           |                                                                                                                                                                                                                        |                                                                                                                |  |  |

| Q Cycle Activity:                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                           |                                                                                           | Q Cycle Activity                              | :                                                                                                                           |                                                                                                                                                                                                                        |                                                                                                                |  |  |

| Q1                                                     | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Q3                                                                                                                                                                                        | Q4                                                                                        | Q1                                            | Q2                                                                                                                          | Q3                                                                                                                                                                                                                     | Q4                                                                                                             |  |  |

| Decode                                                 | Read<br>literal 'k'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Execute                                                                                                                                                                                   | Write<br>registers<br>PRODH:<br>PRODL                                                     | Decode                                        | Read<br>register 'f'                                                                                                        | Execute                                                                                                                                                                                                                | Write<br>registers<br>PRODH:<br>PRODL                                                                          |  |  |