Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 16MHz                                                                       |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 4KB (2K x 16)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                |                                                                             |

| RAM Size                   | 232 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-QFP                                                                      |

| Supplier Device Package    | 44-MQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42at-16e-pq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

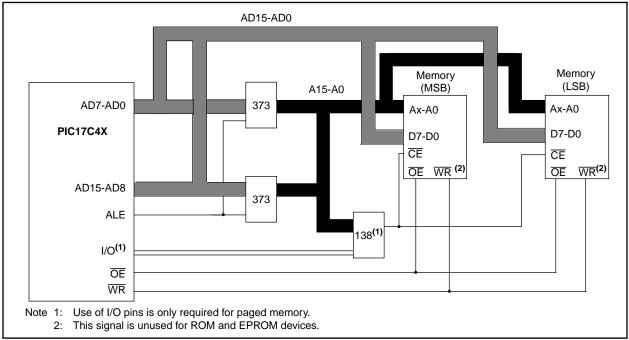

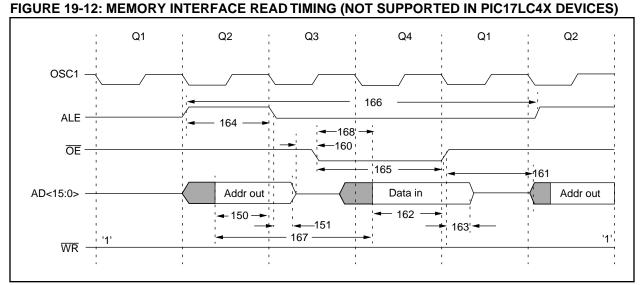

#### 6.1.2 EXTERNAL MEMORY INTERFACE

When either microprocessor or extended microcontroller mode is selected, PORTC, PORTD and PORTE are configured as the system bus. PORTC and PORTD are the multiplexed address/data bus and PORTE is for the control signals. External components are needed to demultiplex the address and data. This can be done as shown in Figure 6-4. The waveforms of address and data are shown in Figure 6-3. For complete timings, please refer to the electrical specification section.

#### FIGURE 6-3: EXTERNAL PROGRAM MEMORY ACCESS WAVEFORMS

| :      | Q1   Q2   Q3   Q4   | Q1   Q2   Q3   Q4   Q1 |

|--------|---------------------|------------------------|

| AD     | X                   |                        |

| <15:0> | Address out Data in | Address out Data out   |

| ALE    |                     |                        |

| OE;    | '4'                 | · · · ·                |

| WR     | '1'                 | <u> </u>               |

|        | Read cycle          | Write cycle            |

|        |                     | , white cycle          |

The system bus requires that there is no bus conflict (minimal leakage), so the output value (address) will be capacitively held at the desired value.

As the speed of the processor increases, external EPROM memory with faster access time must be used. Table 6-2 lists external memory speed requirements for a given PIC17C4X device frequency.

In extended microcontroller mode, when the device is executing out of internal memory, the control signals will continue to be active. That is, they indicate the action that is occurring in the internal memory. The external memory access is ignored.

This following selection is for use with Microchip EPROMs. For interfacing to other manufacturers memory, please refer to the electrical specifications of the desired PIC17C4X device, as well as the desired memory device to ensure compatibility.

| TABLE 6-2: | EPROM MEMORY ACCESS  |

|------------|----------------------|

|            | TIME ORDERING SUFFIX |

| PIC17C4X                | Instruction         | EPROM Suffix |                      |  |  |  |  |

|-------------------------|---------------------|--------------|----------------------|--|--|--|--|

| Oscillator<br>Frequency | Cycle<br>Time (Tcy) | PIC17C42     | PIC17C43<br>PIC17C44 |  |  |  |  |

| 8 MHz                   | 500 ns              | -25          | -25                  |  |  |  |  |

| 16 MHz                  | 250 ns              | -12          | -15                  |  |  |  |  |

| 20 MHz                  | 200 ns              | -90          | -10                  |  |  |  |  |

| 25 MHz                  | 160 ns              | N.A.         | -70                  |  |  |  |  |

| 33 MHz                  | 121 ns              | N.A.         | (1)                  |  |  |  |  |

Note 1: The access times for this requires the use of fast SRAMS.

**Note:** The external memory interface is not supported for the LC devices.

FIGURE 6-4: TYPICAL EXTERNAL PROGRAM MEMORY CONNECTION DIAGRAM

© 1996 Microchip Technology Inc.

#### 6.2.2.3 TMR0 STATUS/CONTROL REGISTER (T0STA)

This register contains various control bits. Bit7 (INTEDG) is used to control the edge upon which a signal on the RA0/INT pin will set the RB0/INT interrupt flag. The other bits configure the Timer0 prescaler and clock source. (Figure 11-1).

#### FIGURE 6-9: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

| R/W - 0        | R/W - 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W - 0                                                                                                                                                                                                                      | R/W - 0                                                            | R/W - 0    | R/W - 0 | R/W - 0 | U - 0 |                                                                                                       |  |  |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------|---------|---------|-------|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| INTEDG<br>bit7 | TOSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TOCS                                                                                                                                                                                                                         | PS3                                                                | PS2        | PS1     | PS0     | bit0  | R = Readable bit<br>W = Writable bit<br>U = Unimplemented,<br>reads as '0'<br>-n = Value at POR reset |  |  |  |  |  |

| bit 7:         | This bit selected to the test of test | NTEDG: RA0/INT Pin Interrupt Edge Select bit<br>This bit selects the edge upon which the interrupt is detected.<br>I = Rising edge of RA0/INT pin generates interrupt<br>D = Falling edge of RA0/INT pin generates interrupt |                                                                    |            |         |         |       |                                                                                                       |  |  |  |  |  |

| bit 6:         | <b>T0SE</b> : Timer0 Clock Input Edge Select bit<br>This bit selects the edge upon which TMR0 will increment.<br><u>When T0CS = 0</u><br>1 = Rising edge of RA1/T0CKI pin increments TMR0 and/or generates a T0CKIF interrupt0 = Falling edge of RA1/T0CKI pin increments TMR0 and/or generates a T0CKIF interruptWhen T0CS = 1Don't care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                              |                                                                    |            |         |         |       |                                                                                                       |  |  |  |  |  |

| bit 5:         | <b>TOCS</b> : Time<br>This bit sele<br>1 = Internal<br>0 = TOCKI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ects the clo<br>instruction                                                                                                                                                                                                  | ock source                                                         | for Timer0 |         |         |       |                                                                                                       |  |  |  |  |  |

| bit 4-1:       | PS3:PS0: 7<br>These bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                              |                                                                    |            | ner0.   |         |       |                                                                                                       |  |  |  |  |  |

|                | PS3:PS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pre                                                                                                                                                                                                                          | scale Valu                                                         | е          |         |         |       |                                                                                                       |  |  |  |  |  |

|                | 0000<br>001<br>0010<br>010<br>0100<br>0101<br>0110<br>0111<br>1xxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                              | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 |            |         |         |       |                                                                                                       |  |  |  |  |  |

| bit 0:         | Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>ented</b> : Rea                                                                                                                                                                                                           | id as '0'                                                          |            |         |         |       |                                                                                                       |  |  |  |  |  |

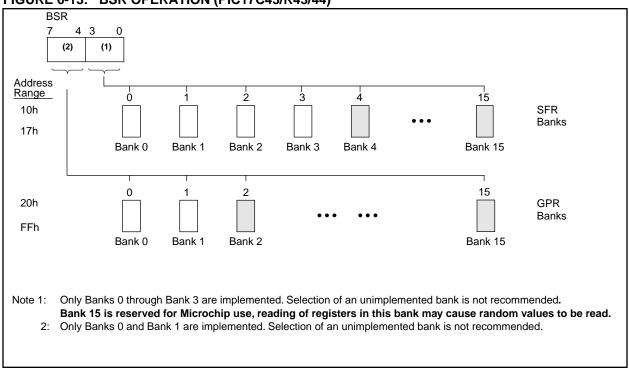

#### 6.8 Bank Select Register (BSR)

The BSR is used to switch between banks in the data memory area (Figure 6-13). In the PIC17C42, PIC17CR42, and PIC17C42A only the lower nibble is implemented. While in the PIC17C43, PIC17CR43, and PIC17C44 devices, the entire byte is implemented. The lower nibble is used to select the peripheral register bank. The upper nibble is used to select the general purpose memory bank.

All the Special Function Registers (SFRs) are mapped into the data memory space. In order to accommodate the large number of registers, a banking scheme has been used. A segment of the SFRs, from address 10h to address 17h, is banked. The lower nibble of the bank select register (BSR) selects the currently active "peripheral bank." Effort has been made to group the peripheral registers of related functionality in one bank. However, it will still be necessary to switch from bank to bank in order to address all peripherals related to a single task. To assist this, a MOVLB bank instruction is in the instruction set. For the PIC17C43, PIC17CR43, and PIC17C44 devices, the need for a large general purpose memory space dictated a general purpose RAM banking scheme. The upper nibble of the BSR selects the currently active general purpose RAM bank. To assist this, a MOVLR bank instruction has been provided in the instruction set.

If the currently selected bank is not implemented (such as Bank 13), any read will read all '0's. Any write is completed to the bit bucket and the ALU status bits will be set/cleared as appropriate.

**Note:** Registers in Bank 15 in the Special Function Register area, are reserved for Microchip use. Reading of registers in this bank may cause random values to be read.

#### FIGURE 6-13: BSR OPERATION (PIC17C43/R43/44)

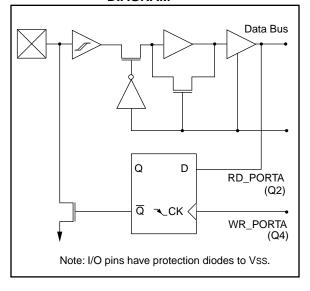

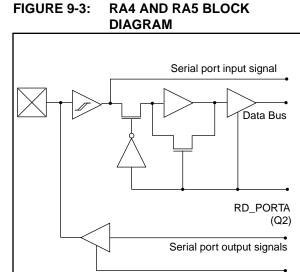

FIGURE 9-2: RA2 AND RA3 BLOCK DIAGRAM

$\overline{OE}$  = SPEN,SYNC,TXEN,  $\overline{CREN}$ ,  $\overline{SREN}$  for RA4  $\overline{OE}$  = SPEN ( $\overline{SYNC}$ +SYNC, $\overline{CSRC}$ ) for RA5

Note: I/O pins have protection diodes to VDD and VSS.

| TABLE 9-1: | PO | RTA FUNCTI | ONS |

|------------|----|------------|-----|

|            |    |            |     |

. . . . .

\_ \_ \_ \_ . . . . . . . . . . . . . . .

| Name      | Bit0 | Buffer Type | Function                                                                            |

|-----------|------|-------------|-------------------------------------------------------------------------------------|

| RA0/INT   | bit0 | ST          | Input or external interrupt input.                                                  |

| RA1/T0CKI | bit1 | ST          | Input or clock input to the TMR0 timer/counter, and/or an external interrupt input. |

| RA2       | bit2 | ST          | Input/Output. Output is open drain type.                                            |

| RA3       | bit3 | ST          | Input/Output. Output is open drain type.                                            |

| RA4/RX/DT | bit4 | ST          | Input or USART Asynchronous Receive or USART Synchronous Data.                      |

| RA5/TX/CK | bit5 | ST          | Input or USART Asynchronous Transmit or USART Synchronous Clock.                    |

| RBPU      | bit7 |             | Control bit for PORTB weak pull-ups.                                                |

Legend: ST = Schmitt Trigger input.

#### TABLE 9-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address       | Name  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|-------|--------|-------|-------|-------|-------|-------|-----------|---------|-------------------------------|-----------------------------------------|

| 10h, Bank 0   | PORTA | RBPU   | _     | RA5   | RA4   | RA3   | RA2   | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                               |

| 05h, Unbanked | TOSTA | INTEDG | T0SE  | TOCS  | PS3   | PS2   | PS1   | PS0       | _       | 0000 000-                     | 0000 000-                               |

| 13h, Bank 0   | RCSTA | SPEN   | RC9   | SREN  | CREN  | —     | FERR  | OERR      | RC9D    | 0000 -00x                     | 0000 -00u                               |

| 15h, Bank 0   | TXSTA | CSRC   | TX9   | TXEN  | SYNC  | _     | —     | TRMT      | TX9D    | 00001x                        | 0000lu                                  |

Legend: x = unknown, u = unchanged, - = unimplemented reads as '0'. Shaded cells are not used by PORTA. Note 1: Other (non power-up) resets include: external reset through  $\overline{MCLR}$  and the Watchdog Timer Reset.

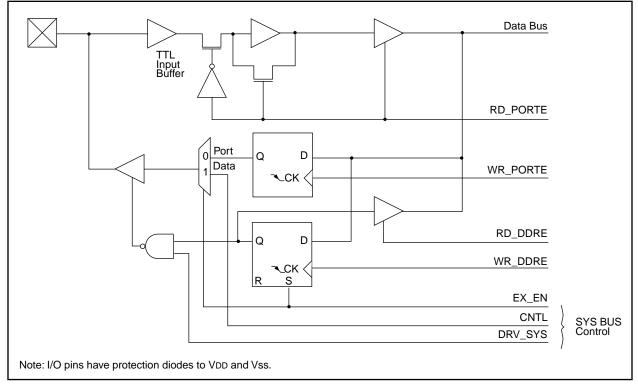

#### 9.4.1 PORTE AND DDRE REGISTER

PORTE is a 3-bit bi-directional port. The corresponding data direction register is DDRE. A '1' in DDRE configures the corresponding port pin as an input. A '0' in the DDRE register configures the corresponding port pin as an output. Reading PORTE reads the status of the pins, whereas writing to it will write to the port latch. PORTE is multiplexed with the system bus. When operating as the system bus, PORTE contains the control signals for the address/data bus (AD15:AD0). These control signals are Address Latch Enable (ALE), Output Enable ( $\overline{OE}$ ), and Write ( $\overline{WR}$ ). The control signals  $\overline{OE}$  and  $\overline{WR}$  are active low signals. The timing for the system bus is shown in the Electrical Characteristics section.

Note: This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-4 shows the instruction sequence to initialize PORTE. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-4: INITIALIZING PORTE

| MOVLB | 1     | ; | Select Bank 1            |

|-------|-------|---|--------------------------|

| CLRF  | PORTE | ; | Initialize PORTE data    |

|       |       | ; | latches before setting   |

|       |       | ; | the data direction       |

|       |       | ; | register                 |

| MOVLW | 0x03  | ; | Value used to initialize |

|       |       | ; | data direction           |

| MOVWF | DDRE  | ; | Set RE<1:0> as inputs    |

|       |       | ; | RE<2> as outputs         |

|       |       | ; | RE<7:3> are always       |

|       |       | ; | read as '0'              |

#### FIGURE 9-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

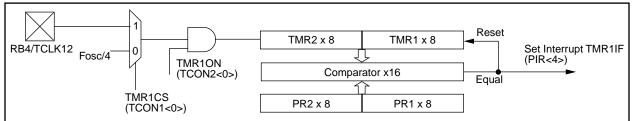

#### 12.1.2 TIMER1 & TIMER2 IN 16-BIT MODE

To select 16-bit mode, the T16 bit must be set. In this mode TMR1 and TMR2 are concatenated to form a 16-bit timer (TMR2:TMR1). The 16-bit timer increments until it matches the 16-bit period register (PR2:PR1). On the following timer clock, the timer value is reset to 0h, and the TMR1IF bit is set.

When selecting the clock source for the16-bit timer, the TMR1CS bit controls the entire 16-bit timer and TMR2CS is a "don't care." When TMR1CS is clear, the timer increments once every instruction cycle (Fosc/4). When TMR1CS is set, the timer increments on every falling edge of the RB4/TCLK12 pin. For the 16-bit timer to increment, both TMR1ON and TMR2ON bits must be set (Table 12-1).

#### 12.1.2.1 EXTERNAL CLOCK INPUT FOR TMR1:TMR2

When TMR1CS is set, the 16-bit TMR2:TMR1 increments on the falling edge of clock input TCLK12. The input on the RB4/TCLK12 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on RB4/TCLK12 to the time TMR2:TMR1 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

| TMR2ON | TMR10N | Result                         |

|--------|--------|--------------------------------|

| 1      | 1      | 16-bit timer<br>(TMR2:TMR1) ON |

| 0      | 1      | Only TMR1 increments           |

| x      | 0      | 16-bit timer OFF               |

#### FIGURE 12-4: TMR1 AND TMR2 IN 16-BIT TIMER/COUNTER MODE

#### TABLE 12-2: SUMMARY OF TIMER1 AND TIMER2 REGISTERS

| Address       | Name   | Bit 7      | Bit 6        | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------|------------|--------------|--------|-----------|-----------|--------|--------|--------|-------------------------------|-----------------------------------------|

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0       | CA1ED1 | CA1ED0    | T16       | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                               |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF       | PWM2ON | PWM1ON    | CA1/PR3   | TMR3ON | TMR2ON | TMR10N | 0000 0000                     | 0000 0000                               |

| 10h, Bank 2   | TMR1   | Timer1 reg | gister       |        |           |           |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 11h, Bank 2   | TMR2   | Timer2 reg | gister       |        | xxxx xxxx | uuuu uuuu |        |        |        |                               |                                         |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF       | TMR2IF | TMR1IF    | CA2IF     | CA1IF  | TXIF   | RCIF   | 0000 0010                     | 0000 0010                               |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE       | TMR2IE | TMR1IE    | CA2IE     | CA1IE  | TXIE   | RCIE   | 0000 0000                     | 0000 0000                               |

| 07h, Unbanked | INTSTA | PEIF       | T0CKIF       | T0IF   | INTF      | PEIE      | T0CKIE | TOIE   | INTE   | 0000 0000                     | 0000 0000                               |

| 06h, Unbanked | CPUSTA | _          | -            | STKAV  | GLINTD    | TO        | PD     | _      | _      | 11 11                         | 11 qq                                   |

| 14h, Bank 2   | PR1    | Timer1 pe  | riod registe | r      |           |           |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 15h, Bank 2   | PR2    | Timer2 pe  | riod registe | r      |           |           |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 10h, Bank 3   | PW1DCL | DC1        | DC0          | —      | _         | —         | —      | —      | —      | xx                            | uu                                      |

| 11h, Bank 3   | PW2DCL | DC1        | DC0          | TM2PW2 |           | —         | _      | _      | _      | xx0                           | uu0                                     |

| 12h, Bank 3   | PW1DCH | DC9        | DC8          | DC7    | DC6       | DC5       | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                               |

| 13h, Bank 3   | PW2DCH | DC9        | DC8          | DC7    | DC6       | DC5       | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', q - value depends on condition,

shaded cells are not used by Timer1 or Timer2.

Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset.

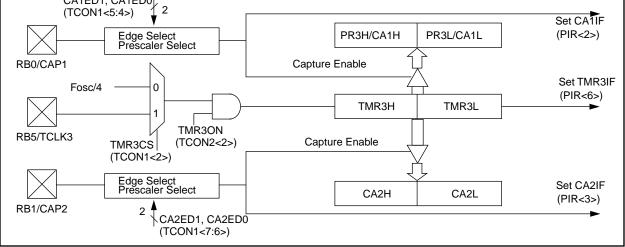

#### 12.2.2 DUAL CAPTURE REGISTER MODE

This mode is selected by setting CA1/PR3. A block diagram is shown in Figure 12-8. In this mode, TMR3 runs without a period register and increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt Flag (TMR3IF) is set on this roll over. The TMR3IF bit must be cleared in software.

Registers PR3H/CA1H and PR3L/CA1L make a 16-bit capture register (Capture1). It captures events on pin RB0/CAP1. Capture mode is configured by the CA1ED1 and CA1ED0 bits. Capture1 Interrupt Flag bit (CA1IF) is set on the capture event. The corresponding interrupt mask bit is CA1IE. The Capture1 Overflow Status bit is CA1OVF.

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the TMR3 value to the capture register which protects the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The operation of the Capture1 feature is identical to Capture2 (as described in Section 12.2.1).

#### TABLE 12-5: REGISTERS ASSOCIATED WITH CAPTURE

| Address       | Name      | Bit 7     | Bit 6                                                          | Bit 5          | Bit 4         | Bit 3         | Bit 2  | Bit 1  | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|-----------|-----------|----------------------------------------------------------------|----------------|---------------|---------------|--------|--------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 3   | TCON1     | CA2ED1    | CA2ED0                                                         | CA1ED1         | CA1ED0        | T16           | TMR3CS | TMR2CS | TMR1CS    | 0000 0000                     | 0000 0000                               |

| 17h, Bank 3   | TCON2     | CA2OVF    | CA10VF                                                         | PWM2ON         | PWM10N        | CA1/PR3       | TMR3ON | TMR2ON | TMR10N    | 0000 0000                     | 0000 0000                               |

| 12h, Bank 2   | TMR3L     | TMR3 reg  | IR3 register; low byte                                         |                |               |               |        |        |           |                               | uuuu uuuu                               |

| 13h, Bank 2   | TMR3H     | TMR3 reg  | MR3 register; high byte                                        |                |               |               |        |        | xxxx xxxx | uuuu uuuu                     |                                         |

| 16h, Bank 1   | PIR       | RBIF      | TMR3IF                                                         | TMR2IF         | TMR1IF        | CA2IF         | CA1IF  | TXIF   | RCIF      | 0000 0010                     | 0000 0010                               |

| 17h, Bank 1   | PIE       | RBIE      | TMR3IE                                                         | TMR2IE         | TMR1IE        | CA2IE         | CA1IE  | TXIE   | RCIE      | 0000 0000                     | 0000 0000                               |

| 07h, Unbanked | INTSTA    | PEIF      | T0CKIF                                                         | T0IF           | INTF          | PEIE          | T0CKIE | T0IE   | INTE      | 0000 0000                     | 0000 0000                               |

| 06h, Unbanked | CPUSTA    | —         | _                                                              | STKAV          | GLINTD        | TO            | PD     | —      | —         | 11 11                         | 11 qq                                   |

| 16h, Bank 2   | PR3L/CA1L | Timer3 pe | riod registe                                                   | r, low byte/ca | apture1 regis | ter, low byte | e      |        |           | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 2   | PR3H/CA1H | Timer3 pe | Timer3 period register, high byte/capture1 register, high byte |                |               |               |        |        | xxxx xxxx | uuuu uuuu                     |                                         |

| 14h, Bank 3   | CA2L      | Capture2  | Capture2 low byte                                              |                |               |               |        |        |           | xxxx xxxx                     | uuuu uuuu                               |

| 15h, Bank 3   | CA2H      | Capture2  | high byte                                                      |                |               |               |        |        |           | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition, shaded cells are not used by Capture.

Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset.

### FIGURE 13-2: RCSTA REGISTER (ADDRESS: 13h, BANK 0)

| SPEN   | N.W0         R/W - 0         R/W - 0         U - 0         R - 0         R - 0         R - x           RX9         SREN         CREN         —         FERR         OERR         RX9D         R = Readable bit                                                                                                                                             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit7   | bit 0<br>W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)                                                                                                                                                                                                                                                                                      |

| bit 7: | <b>SPEN</b> : Serial Port Enable bit<br>1 = Configures RA5/RX/DT and RA4/TX/CK pins as serial port pins<br>0 = Serial port disabled                                                                                                                                                                                                                        |

| bit 6: | <b>RX9</b> : 9-bit Receive Enable bit<br>1 = Selects 9-bit reception<br>0 = Selects 8-bit reception                                                                                                                                                                                                                                                        |

| bit 5: | SREN: Single Receive Enable bit         This bit enables the reception of a single byte. After receiving the byte, this bit is automatically cleared.         Synchronous mode:         1 = Enable reception         0 = Disable reception         Note: This bit is ignored in synchronous slave reception.         Asynchronous mode:         Don't care |

| bit 4: | CREN: Continuous Receive Enable bit<br>This bit enables the continuous reception of serial data.<br><u>Asynchronous mode:</u><br>1 = Enable reception<br>0 = Disables reception<br><u>Synchronous mode:</u><br>1 = Enables continuous reception until CREN is cleared (CREN overrides SREN)<br>0 = Disables continuous reception                           |

| bit 3: | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                 |

| bit 2: | FERR: Framing Error bit<br>1 = Framing error (Updated by reading RCREG)<br>0 = No framing error                                                                                                                                                                                                                                                            |

| bit 1: | OERR: Overrun Error bit<br>1 = Overrun (Cleared by clearing CREN)<br>0 = No overrun error                                                                                                                                                                                                                                                                  |

| bit 0: | <b>RX9D</b> : 9th bit of receive data (can be the software calculated parity bit)                                                                                                                                                                                                                                                                          |

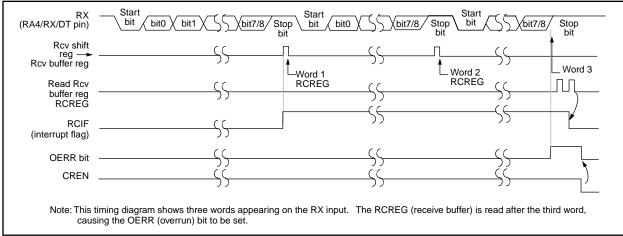

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

#### FIGURE 13-8: ASYNCHRONOUS RECEPTION

| <b>TABLE 13-6</b> : | <b>REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION</b> |

|---------------------|---------------------------------------------------------|

|                     |                                                         |

| Address     | Name                                           | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|------------------------------------------------|-------|--------|--------|--------|-------|-------|-------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR                                            | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF      | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA                                          | SPEN  | RX9    | SREN   | CREN   | _     | FERR  | OERR  | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0 | RCREG                                          | RX7   | RX6    | RX5    | RX4    | RX3   | RX2   | RX1   | RX0       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE                                            | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE      | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA                                          | CSRC  | TX9    | TXEN   | SYNC   | _     | —     | TRMT  | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 | 17h, Bank 0 SPBRG Baud rate generator register |       |        |        |        |       |       |       | xxxx xxxx | uuuu uuuu                     |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous reception. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

### TABLE 13-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address     | Name                                           | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|------------------------------------------------|-------|--------|--------|--------|-------|-------|-------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR                                            | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF      | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA                                          | SPEN  | RX9    | SREN   | CREN   | —     | FERR  | OERR  | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 16h, Bank 0 | TXREG                                          | TX7   | TX6    | TX5    | TX4    | TX3   | TX2   | TX1   | TX0       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE                                            | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE      | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA                                          | CSRC  | TX9    | TXEN   | SYNC   | —     |       | TRMT  | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 | 17h, Bank 0 SPBRG Baud rate generator register |       |        |        |        |       |       |       | xxxx xxxx | uuuu uuuu                     |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous master transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

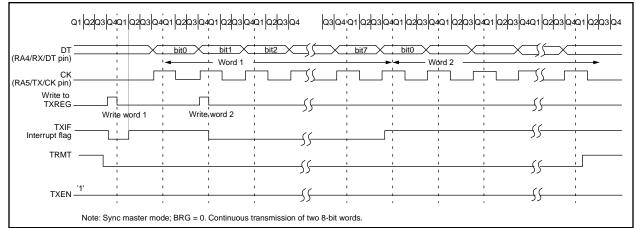

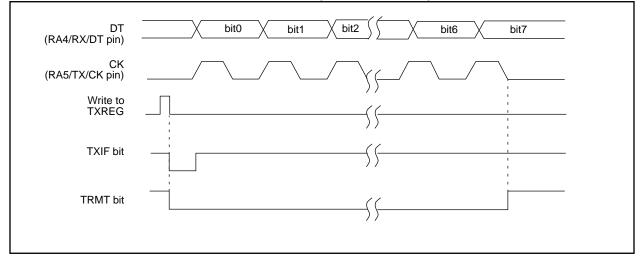

#### FIGURE 13-9: SYNCHRONOUS TRANSMISSION

#### FIGURE 13-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

## TABLE 15-2: PIC17CXX INSTRUCTION SET

| Mnemonic, |       | Description                           | Cycles | 16-bit Opcoo   | le   | Status    | Notes |

|-----------|-------|---------------------------------------|--------|----------------|------|-----------|-------|

| Operands  |       |                                       |        | MSb            | LSb  | Affected  |       |

| BYTE-ORIE |       | TILE REGISTER OPERATIONS              | •      |                |      |           | •     |

| ADDWF     | f,d   | ADD WREG to f                         | 1      | 0000 111d ffff | ffff | OV,C,DC,Z |       |

| ADDWFC    | f,d   | ADD WREG and Carry bit to f           | 1      | 0001 000d ffff | ffff | OV,C,DC,Z |       |

| ANDWF     | f,d   | AND WREG with f                       | 1      | 0000 101d ffff | ffff | Z         |       |

| CLRF      | f,s   | Clear f, or Clear f and Clear WREG    | 1      | 0010 100s ffff | ffff | None      | 3     |

| COMF      | f,d   | Complement f                          | 1      | 0001 001d ffff | ffff | Z         |       |

| CPFSEQ    | f     | Compare f with WREG, skip if f = WREG | 1 (2)  | 0011 0001 ffff | ffff | None      | 6,8   |

| CPFSGT    | f     | Compare f with WREG, skip if f > WREG | 1 (2)  | 0011 0010 ffff | ffff | None      | 2,6,8 |

| CPFSLT    | f     | Compare f with WREG, skip if f < WREG | 1 (2)  | 0011 0000 ffff | ffff | None      | 2,6,8 |

| DAW       | f,s   | Decimal Adjust WREG Register          | 1      | 0010 111s ffff | ffff | C         | 3     |

| DECF      | f,d   | Decrement f                           | 1      | 0000 011d ffff | ffff | OV,C,DC,Z |       |

| DECFSZ    | f,d   | Decrement f, skip if 0                | 1 (2)  | 0001 011d ffff | ffff | None      | 6,8   |

| DCFSNZ    | f,d   | Decrement f, skip if not 0            | 1 (2)  | 0010 011d ffff | ffff | None      | 6,8   |

| INCF      | f,d   | Increment f                           | 1      | 0001 010d ffff | ffff | OV,C,DC,Z |       |

| INCFSZ    | f,d   | Increment f, skip if 0                | 1 (2)  | 0001 111d ffff | ffff | None      | 6,8   |

| INFSNZ    | f,d   | Increment f, skip if not 0            | 1 (2)  | 0010 010d ffff | ffff | None      | 6,8   |

| IORWF     | f,d   | Inclusive OR WREG with f              | 1      | 0000 100d ffff | ffff | Z         |       |

| MOVFP     | f,p   | Move f to p                           | 1      | 011p pppp ffff | ffff | None      |       |

| MOVPF     | p,f   | Move p to f                           | 1      | 010p pppp ffff | ffff | Z         |       |

| MOVWF     | f     | Move WREG to f                        | 1      | 0000 0001 ffff | ffff | None      |       |

| MULWF     | f     | Multiply WREG with f                  | 1      | 0011 0100 ffff | ffff | None      | 9     |

| NEGW      | f,s   | Negate WREG                           | 1      | 0010 110s ffff | ffff | OV,C,DC,Z | 1,3   |

| NOP       | —     | No Operation                          | 1      | 0000 0000 0000 | 0000 | None      |       |

| RLCF      | f,d   | Rotate left f through Carry           | 1      | 0001 101d ffff | ffff | С         |       |

| RLNCF     | f,d   | Rotate left f (no carry)              | 1      | 0010 001d ffff | ffff | None      |       |

| RRCF      | f,d   | Rotate right f through Carry          | 1      | 0001 100d ffff | ffff | C         |       |

| RRNCF     | f,d   | Rotate right f (no carry)             | 1      | 0010 000d ffff | ffff | None      |       |

| SETF      | f,s   | Set f                                 | 1      | 0010 101s ffff | ffff | None      | 3     |

| SUBWF     | f,d   | Subtract WREG from f                  | 1      | 0000 010d ffff | ffff | OV,C,DC,Z | 1     |

| SUBWFB    | f,d   | Subtract WREG from f with Borrow      | 1      | 0000 001d ffff | ffff | OV,C,DC,Z | 1     |

| SWAPF     | f,d   | Swap f                                | 1      | 0001 110d ffff | ffff | None      |       |

| TABLRD    | t,i,f | Table Read                            | 2 (3)  | 1010 10ti ffff | ffff | None      | 7     |

Legend: Refer to Table 15-1 for opcode field descriptions.

- Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- 5: Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

| Mnemonic,  |        | Description                                   | Cycles |      | 16-bit | Opcod | e    | Status    | Notes |

|------------|--------|-----------------------------------------------|--------|------|--------|-------|------|-----------|-------|

| Operands   |        |                                               |        | MSb  |        |       | LSb  | Affected  |       |

| TABLWT     | t,i,f  | Table Write                                   | 2      | 1010 | 11ti   | ffff  | ffff | None      | 5     |

| TLRD       | t,f    | Table Latch Read                              | 1      | 1010 | 00tx   | ffff  | ffff | None      |       |

| TLWT       | t,f    | Table Latch Write                             | 1      | 1010 | 01tx   | ffff  | ffff | None      |       |

| TSTFSZ     | f      | Test f, skip if 0                             | 1 (2)  | 0011 | 0011   | ffff  | ffff | None      | 6,8   |

| XORWF      | f,d    | Exclusive OR WREG with f                      | 1      | 0000 | 110d   | ffff  | ffff | Z         |       |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS                         | 1      |      |        |       |      |           |       |

| BCF        | f,b    | Bit Clear f                                   | 1      | 1000 | 1bbb   | ffff  | ffff | None      |       |

| BSF        | f,b    | Bit Set f                                     | 1      | 1000 | 0bbb   | ffff  | ffff | None      |       |

| BTFSC      | f,b    | Bit test, skip if clear                       | 1 (2)  | 1001 | 1bbb   | ffff  | ffff | None      | 6,8   |

| BTFSS      | f,b    | Bit test, skip if set                         | 1 (2)  | 1001 | 0bbb   | ffff  | ffff | None      | 6,8   |

| BTG        | f,b    | Bit Toggle f                                  | 1      | 0011 | 1bbb   | ffff  | ffff | None      |       |

| LITERAL AN | ID CO  | NTROL OPERATIONS                              |        |      |        |       |      |           |       |

| ADDLW      | k      | ADD literal to WREG                           | 1      | 1011 | 0001   | kkkk  | kkkk | OV,C,DC,Z |       |

| ANDLW      | k      | AND literal with WREG                         | 1      | 1011 | 0101   | kkkk  | kkkk | Z         |       |

| CALL       | k      | Subroutine Call                               | 2      | 111k | kkkk   | kkkk  | kkkk | None      | 7     |

| CLRWDT     | _      | Clear Watchdog Timer                          | 1      | 0000 | 0000   | 0000  | 0100 | TO,PD     |       |

| GOTO       | k      | Unconditional Branch                          | 2      | 110k | kkkk   | kkkk  | kkkk | None      | 7     |

| IORLW      | k      | Inclusive OR literal with WREG                | 1      | 1011 | 0011   | kkkk  | kkkk | Z         |       |

| LCALL      | k      | Long Call                                     | 2      | 1011 | 0111   | kkkk  | kkkk | None      | 4,7   |

| MOVLB      | k      | Move literal to low nibble in BSR             | 1      | 1011 | 1000   | uuuu  | kkkk | None      |       |

| MOVLR      | k      | Move literal to high nibble in BSR            | 1      | 1011 | 101x   | kkkk  | uuuu | None      | 9     |

| MOVLW      | k      | Move literal to WREG                          | 1      | 1011 | 0000   | kkkk  | kkkk | None      |       |

| MULLW      | k      | Multiply literal with WREG                    | 1      | 1011 | 1100   | kkkk  | kkkk | None      | 9     |

| RETFIE     | _      | Return from interrupt (and enable interrupts) | 2      | 0000 | 0000   | 0000  | 0101 | GLINTD    | 7     |

| RETLW      | k      | Return literal to WREG                        | 2      | 1011 | 0110   | kkkk  | kkkk | None      | 7     |

| RETURN     | _      | Return from subroutine                        | 2      | 0000 | 0000   | 0000  | 0010 | None      | 7     |

| SLEEP      | _      | Enter SLEEP Mode                              | 1      | 0000 | 0000   | 0000  | 0011 | TO, PD    |       |

| SUBLW      | k      | Subtract WREG from literal                    | 1      | 1011 | 0010   | kkkk  | kkkk | OV,C,DC,Z |       |

| XORLW      | k      | Exclusive OR literal with WREG                | 1      | 1011 | 0100   | kkkk  | kkkk | Z         |       |

### TABLE 15-2: PIC17CXX INSTRUCTION SET (Cont.'d)

Legend: Refer to Table 15-1 for opcode field descriptions.

Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

- 3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

## PIC17C4X

| ADD          | <b>WFC</b>                                                                              | ADD WRE                                               | EG and C                     | arry bit                    | to f                     |

|--------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------|-----------------------------|--------------------------|

| Synt         | ax:                                                                                     | [ <i>label</i> ] A[                                   | DDWFC                        | f,d                         |                          |

| Ope          | rands:                                                                                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]                              | 5                            |                             |                          |

| Ope          | ration:                                                                                 | (WREG) +                                              | - (f) + C -                  | → (dest)                    |                          |

| Stat         | us Affected:                                                                            | OV, C, DC                                             | , Z                          |                             |                          |

| Enco         | oding:                                                                                  | 0001                                                  | 000d                         | ffff                        | ffff                     |

| Description: |                                                                                         | Add WREG<br>memory loc<br>placed in W<br>placed in da | ation 'f'. If<br>/REG. If 'd | 'd' is 0, th<br>' is 1, the | e result is<br>result is |

| Wor          | ds:                                                                                     | 1                                                     |                              |                             |                          |

| Cycl         | es:                                                                                     | 1                                                     |                              |                             |                          |

| QC           | ycle Activity:                                                                          |                                                       |                              |                             |                          |

|              | Q1                                                                                      | Q2                                                    | Q3                           |                             | Q4                       |

|              | Decode                                                                                  | Read<br>register 'f'                                  | Execut                       | -                           | rite to<br>tination      |

| <u>Exa</u>   | mple:                                                                                   | ADDWFC                                                | REG                          | 0                           |                          |

|              | Before Instru<br>Carry bit<br>REG<br>WREG<br>After Instruct<br>Carry bit<br>REG<br>WREG | = 1<br>= 0x02<br>= 0x4D                               |                              |                             |                          |

| ANDLW                  | And Liter           | al with WR                            | EG  |                  |  |  |  |  |  |  |

|------------------------|---------------------|---------------------------------------|-----|------------------|--|--|--|--|--|--|

| Syntax:                | [ <i>label</i> ] A  | NDLW k                                |     |                  |  |  |  |  |  |  |

| Operands:              | $0 \le k \le 25$    | 5                                     |     |                  |  |  |  |  |  |  |

| Operation:             | (WREG) .            | (WREG) .AND. (k) $\rightarrow$ (WREG) |     |                  |  |  |  |  |  |  |

| Status Affected:       | Z                   | Z                                     |     |                  |  |  |  |  |  |  |

| Encoding:              | 1011                | 0101 k                                | kkk | kkkk             |  |  |  |  |  |  |

| Description:           |                     | ts of WREG<br>eral 'k'. The re        |     |                  |  |  |  |  |  |  |

| Words:                 | 1                   |                                       |     |                  |  |  |  |  |  |  |

| Cycles:                | 1                   |                                       |     |                  |  |  |  |  |  |  |

| Q Cycle Activity:      |                     |                                       |     |                  |  |  |  |  |  |  |

| Q1                     | Q2                  | Q3                                    |     | Q4               |  |  |  |  |  |  |

| Decode                 | Read literal<br>'k' | Execute                               |     | Vrite to<br>VREG |  |  |  |  |  |  |

| Example:               | ANDLW               | 0x5F                                  |     |                  |  |  |  |  |  |  |

| Before Instru<br>WREG  | iction<br>= 0xA3    |                                       |     |                  |  |  |  |  |  |  |

| After Instruct<br>WREG |                     |                                       |     |                  |  |  |  |  |  |  |

| CPFSEQ                                         | Compare<br>skip if f =                                        | f with WREC<br>WREG                                                                                       | Э,                                                       | CPF        | SGT                                           | Compare<br>skip if f >                                                                 | f with WRE<br>WREG                                                                       | G,            |

|------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------|-----------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------|

| Syntax:                                        | [label]                                                       | CPFSEQ f                                                                                                  |                                                          | Syn        | tax:                                          | [label]                                                                                | CPFSGT f                                                                                 |               |

| Operands:                                      | $0 \le f \le 255$                                             | 5                                                                                                         |                                                          | Ope        | rands:                                        | $0 \le f \le 255$                                                                      | 5                                                                                        |               |

| Operation:                                     | (f) – (WRE)<br>skip if (f) =<br>(unsigned o                   |                                                                                                           |                                                          | Ope        | ration:                                       | (f) – (WRE0<br>skip if (f) ><br>(unsigned o                                            |                                                                                          |               |

| Status Affected:                               | None                                                          |                                                                                                           |                                                          | Stat       | us Affected:                                  | None                                                                                   |                                                                                          |               |

| Encoding:                                      | 0011                                                          | 0001 fff                                                                                                  | f ffff                                                   | Enc        | oding:                                        | 0011                                                                                   | 0010 ff:                                                                                 | ff ffff       |

| Description:                                   | location 'f' t<br>performing<br>If 'f' = WRE<br>tion is disca | the contents of<br>o the contents<br>an unsigned s<br>G then the fetc<br>arded and an N<br>ad making this | of WREG by<br>ubtraction.<br>hed instruc-<br>IOP is exe- | Des        | cription:                                     | location 'f' t<br>by performi<br>If the conte<br>WREG the<br>discarded a<br>instead ma | o the contents<br>ng an unsigne<br>nts of 'f' > the<br>n the fetched in<br>and an NOP is | nstruction is |

| Words:                                         | 1                                                             |                                                                                                           |                                                          | 14/0 -     | de .                                          | tion.<br>1                                                                             |                                                                                          |               |

| Cycles:                                        | 1 (2)                                                         |                                                                                                           |                                                          | Wor        |                                               | -                                                                                      |                                                                                          |               |

| Q Cycle Activity:                              |                                                               |                                                                                                           |                                                          | Cyc        |                                               | 1 (2)                                                                                  |                                                                                          |               |