Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 25MHz                                                                       |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 4KB (2K x 16)                                                               |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 232 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

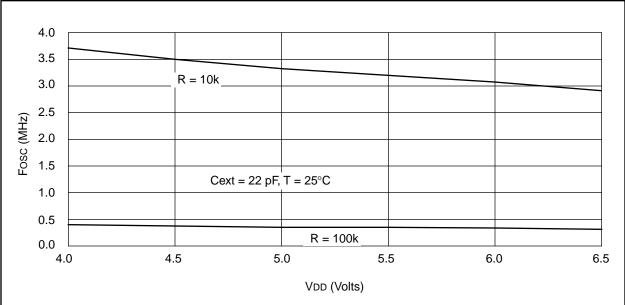

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-QFP                                                                      |

| Supplier Device Package    | 44-MQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42at-25e-pq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

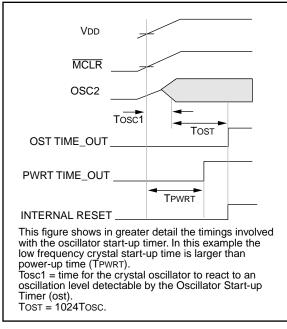

#### FIGURE 4-5: OSCILLATOR START-UPTIME

#### FIGURE 4-6: USING ON-CHIP POR

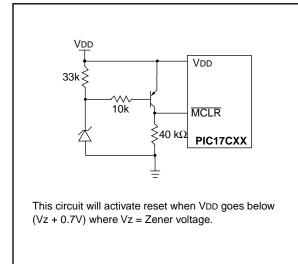

#### FIGURE 4-7: BROWN-OUT PROTECTION CIRCUIT 1

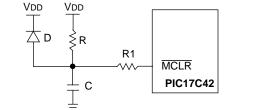

# FIGURE 4-8: PIC17C42 EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: An external Power-on Reset circuit is required only if VDD power-up time is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R < 40 k $\Omega$  is recommended to ensure that the voltage drop across R does not exceed 0.2V (max. leakage current spec. on the  $\overline{MCLR}/VPP$  pin is 5  $\mu$ A). A larger voltage drop will degrade VIH level on the  $\overline{MCLR}/VPP$  pin.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or (Electrical Overstress) EOS.

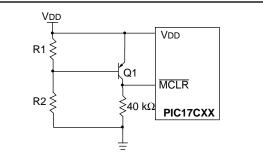

FIGURE 4-9: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

NOTES:

Example 8-3 shows the sequence to do a 16 x 16 unsigned multiply. Equation 8-1 shows the algorithm that is used. The 32-bit result is stored in 4 registers RES3:RES0.

#### **EQUATION 8-1:** 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

=

- ARG1H:ARG1L \* ARG2H:ARG2L RES3:RES0 =

- (ARG1H \* ARG2H \* 2<sup>16</sup>) +

(ARG1H \* ARG2L \* 2<sup>8</sup>) +

(ARG1L \* ARG2H \* 2<sup>8</sup>) (ARG1L \* ARG2L)

+

#### EXAMPLE 8-3: 16 x 16 MULTIPLY ROUTINE

|   |                                  |                            | ; ARG1L * ARG2L -<br>; PRODH:PRODL  | > |

|---|----------------------------------|----------------------------|-------------------------------------|---|

| ; |                                  | PRODH, RES1<br>PRODL, RES0 | ;                                   |   |

| , |                                  |                            | ; ARG1H * ARG2H -<br>; PRODH:PRODL  | > |

| ; |                                  | PRODH, RES3<br>PRODL, RES2 |                                     |   |

| - | MOVFP<br>MULWF                   |                            | ; ARG1L * ARG2H -<br>; PRODH:PRODL  | > |

|   | ADDWF<br>MOVFP<br>ADDWFC         |                            | ; Add cross<br>; products<br>;      |   |

| ; | ADDWFC                           | RES3, F<br>ARG1H, WREG     | ;                                   |   |

|   | MULWF                            | ARG2L                      | ; ARG1H * ARG2L -<br>; PRODH:PRODL  | > |

|   | ADDWF<br>MOVFP<br>ADDWFC<br>CLRF |                            | ; Add cross<br>; products<br>;<br>; |   |

| Address                                      | Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4  | Bit 3 | Bit 2         | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|----------------------------------------------|--------|--------|--------|-------|--------|-------|---------------|-------|-------|-------------------------------|-----------------------------------------|

| 05h, Unbanked                                | TOSTA  | INTEDG | T0SE   | TOCS  | PS3    | PS2   | PS1           | PS0   |       | 0000 000-                     | 0000 000-                               |

| 06h, Unbanked                                | CPUSTA | —      | _      | STKAV | GLINTD | TO    | PD            | _     | _     | 11 11                         | 11 qq                                   |

| 07h, Unbanked                                | INTSTA | PEIF   | TOCKIF | T0IF  | INTF   | PEIE  | <b>T0CKIE</b> | TOIE  | INTE  | 0000 0000                     | 0000 0000                               |

| 0Bh, Unbanked TMR0L TMR0 register; low byte  |        |        |        |       |        |       |               |       |       | xxxx xxxx                     | uuuu uuuu                               |

| 0Ch, Unbanked TMR0H TMR0 register; high byte |        |        |        |       |        |       |               |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', g - value depends on condition, Shaded cells are not used by Timer0. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

## FIGURE 12-2: TCON2 REGISTER (ADDRESS: 17h, BANK 3)

| R - 0  | R - 0 R/W - 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | F CA10VF PWM20N PWM10N CA1/PR3 TMR30N TMR20N TMR10N R = Readable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit7   | bit0 W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | -n = Value at POR reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 7: | <ul> <li>CA2OVF: Capture2 Overflow Status bit</li> <li>This bit indicates that the capture value had not been read from the capture register pair (CA2H:CA2L)</li> <li>before the next capture event occurred. The capture register retains the oldest unread capture value (last capture before overflow). Subsequent capture events will not update the capture register with the Timer3 value until the capture register has been read (both bytes).</li> <li>1 = Overflow occurred on Capture2 register</li> <li>0 = No overflow occurred on Capture2 register</li> </ul> |

| bit 6: | <b>CA1OVF</b> : Capture1 Overflow Status bit<br>This bit indicates that the capture value had not been read from the capture register pair<br>(PR3H/CA2H:PR3L/CA2L) before the next capture event occurred. The capture register retains the old-<br>est unread capture value (last capture before overflow). Subsequent capture events will not update the<br>capture register with the TMR3 value until the capture register has been read (both bytes).<br>1 = Overflow occurred on Capture1 register<br>0 = No overflow occurred on Capture1 register                     |

| bit 5: | <b>PWM2ON</b> : PWM2 On bit<br>1 = PWM2 is enabled (The RB3/PWM2 pin ignores the state of the DDRB<3> bit)<br>0 = PWM2 is disabled (The RB3/PWM2 pin uses the state of the DDRB<3> bit for data direction)                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4: | <b>PWM1ON</b> : PWM1 On bit<br>1 = PWM1 is enabled (The RB2/PWM1 pin ignores the state of the DDRB<2> bit)<br>0 = PWM1 is disabled (The RB2/PWM1 pin uses the state of the DDRB<2> bit for data direction)                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3: | <b>CA1/PR3</b> : CA1/PR3 Register Mode Select bit<br>1 = Enables Capture1 (PR3H/CA1H:PR3L/CA1L is the Capture1 register. Timer3 runs without<br>a period register)<br>0 = Enables the Period register (PR3H/CA1H:PR3L/CA1L is the Period register for Timer3)                                                                                                                                                                                                                                                                                                                 |

| bit 2: | TMR3ON: Timer3 On bit<br>1 = Starts Timer3<br>0 = Stops Timer3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 1: | <b>TMR2ON</b> : Timer2 On bit<br>This bit controls the incrementing of the Timer2 register. When Timer2:Timer1 form the 16-bit timer (T16<br>is set), TMR2ON must be set. This allows the MSB of the timer to increment.<br>1 = Starts Timer2 (Must be enabled if the T16 bit (TCON1<3>) is set)<br>0 = Stops Timer2                                                                                                                                                                                                                                                          |

| bit 0: | TMR1ON: Timer1 On bit<br><u>When T16 is set (in 16-bit Timer Mode)</u><br>1 = Starts 16-bit Timer2:Timer1<br>0 = Stops 16-bit Timer2:Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | <u>When T16 is clear (in 8-bit Timer Mode)</u><br>1 = Starts 8-bit Timer1<br>0 = Stops 8-bit Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### 12.2.3 EXTERNAL CLOCK INPUT FOR TIMER3

When TMR3CS is set, the 16-bit TMR3 increments on the falling edge of clock input TCLK3. The input on the RB5/TCLK3 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on TCLK3 to the time TMR3 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section. Figure 12-9 shows the timing diagram when operating from an external clock.

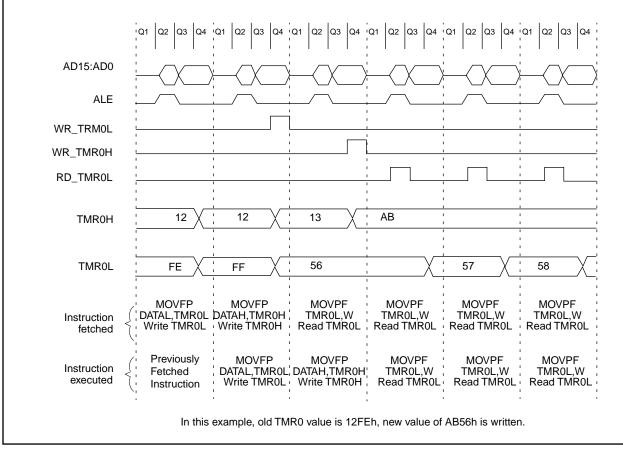

#### 12.2.4 READING/WRITING TIMER3

Since Timer3 is a 16-bit timer and only 8-bits at a time can be read or written, care should be taken when reading or writing while the timer is running. The best method to read or write the timer is to stop the timer, perform any read or write operation, and then restart Timer3 (using the TMR3ON bit). However, if it is necessary to keep Timer3 free-running, care must be taken. For writing to the 16-bit TMR3, Example 12-2 may be used. For reading the 16-bit TMR3, Example 12-3 may be used. Interrupts must be disabled during this routine.

#### EXAMPLE 12-2: WRITING TO TMR3

BSF CPUSTA, GLINTD ;Disable interrupt MOVFP RAM\_L, TMR3L ; MOVFP RAM\_H, TMR3H ; BCF CPUSTA, GLINTD ;Done,enable interrupt

#### **EXAMPLE 12-3: READING FROM TMR3**

| MOVPF TMR3L, TMPLO ;read low t<br>MOVPF TMR3H, TMPHI ;read high<br>MOVFP TMPLO, WREG ;tmplo -> w | tmr0  |

|--------------------------------------------------------------------------------------------------|-------|

| CPFSLT TMR3L, WREG ;tmr0l < wr                                                                   | eg?   |

| RETURN ;no then re                                                                               | eturn |

| MOVPF TMR3L, TMPLO ;read low t                                                                   | .mr0  |

| MOVPF TMR3H, TMPHI ;read high                                                                    | tmr0  |

| RETURN ; return                                                                                  |       |

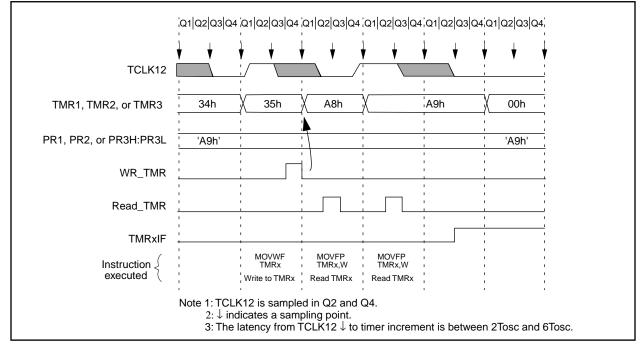

#### FIGURE 12-9: TMR1, TMR2, AND TMR3 OPERATION IN EXTERNAL CLOCK MODE

#### 13.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. Table 13-1 shows the formula for computation of the baud rate for different USART modes. These only apply when the USART is in synchronous master mode (internal clock) and asynchronous mode.

Given the desired baud rate and Fosc, the nearest integer value between 0 and 255 can be calculated using the formula below. The error in baud rate can then be determined.

#### TABLE 13-1: BAUD RATE FORMULA

| SYNC | Mode         | Baud Rate      |

|------|--------------|----------------|

| 0    | Asynchronous | Fosc/(64(X+1)) |

| 1    | Synchronous  | Fosc/(4(X+1))  |

X = value in SPBRG (0 to 255)

Example 13-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 SYNC = 0

#### EXAMPLE 13-1: CALCULATING BAUD RATE ERROR

Desired Baud rate=Fosc / (64 (X + 1))

$9600 = \frac{16000000}{(64 (X + 1))}$

X = 25.042 = 25

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

- Error = <u>(Calculated Baud Rate Desired Baud Rate)</u> Desired Baud Rate

- = (9615 9600) / 9600

- = 0.16%

Writing a new value to the SPBRG, causes the BRG timer to be reset (or cleared), this ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

#### TABLE 13-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address                                        | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------|-------------------------------|-----------------------------------------|

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9   | SREN  | CREN  | _     | FERR  | OERR  | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9   | TXEN  | SYNC  | —     | —     | TRMT  | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |       |       |       |       |       |       | xxxx xxxx | uuuu uuuu                     |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used by the Baud Rate Generator. $Note 1: Other (non power-up) resets include: external reset through <math>\overline{MCLR}$  and Watchdog Timer Reset.

| BAUD        | Fosc = 3 | 3 MHz  | SPBRG              | Fosc = 25 MHz |        | SPBRG              |       |        | SPBRG              | Fosc = 1 | SPBRG  |                    |

|-------------|----------|--------|--------------------|---------------|--------|--------------------|-------|--------|--------------------|----------|--------|--------------------|

| RATE<br>(K) | KBAUD    | %ERROR | value<br>(decimal) | KBAUD         | %ERROR | value<br>(decimal) | KBAUD | %ERROR | value<br>(decimal) | KBAUD    | %ERROR | value<br>(decimal) |

| 0.3         | NA       | _      | —                  | NA            | _      |                    | NA    | _      | _                  | NA       | _      | -                  |

| 1.2         | NA       | _      | _                  | NA            | _      | _                  | 1.221 | +1.73  | 255                | 1.202    | +0.16  | 207                |

| 2.4         | 2.398    | -0.07  | 214                | 2.396         | 0.14   | 162                | 2.404 | +0.16  | 129                | 2.404    | +0.16  | 103                |

| 9.6         | 9.548    | -0.54  | 53                 | 9.53          | -0.76  | 40                 | 9.469 | -1.36  | 32                 | 9.615    | +0.16  | 25                 |

| 19.2        | 19.09    | -0.54  | 26                 | 19.53         | +1.73  | 19                 | 19.53 | +1.73  | 15                 | 19.23    | +0.16  | 12                 |

| 76.8        | 73.66    | -4.09  | 6                  | 78.13         | +1.73  | 4                  | 78.13 | +1.73  | 3                  | 83.33    | +8.51  | 2                  |

| 96          | 103.12   | +7.42  | 4                  | 97.65         | +1.73  | 3                  | 104.2 | +8.51  | 2                  | NA       | _      | _                  |

| 300         | 257.81   | -14.06 | 1                  | 390.63        | +30.21 | 0                  | 312.5 | +4.17  | 0                  | NA       | _      | -                  |

| 500         | 515.62   | +3.13  | 0                  | NA            | _      | _                  | NA    | _      | _                  | NA       | _      | -                  |

| HIGH        | 515.62   | _      | 0                  | _             | _      | 0                  | 312.5 | _      | 0                  | 250      | _      | 0                  |

| LOW         | 2.014    | —      | 255                | 1.53          | —      | 255                | 1.221 | —      | 255                | 0.977    | _      | 255                |

## TABLE 13-4: BAUD RATES FOR ASYNCHRONOUS MODE

| BAUD<br>RATE | Fosc = 10 MH | Iz     | SPBRG<br>value     | Fosc = 7.159 | ) MHz  | SPBRG<br>value     | FOSC = 5.068 | 8 MHz  | SPBRG<br>value     |

|--------------|--------------|--------|--------------------|--------------|--------|--------------------|--------------|--------|--------------------|

| (K)          | KBAUD        | %ERROR | (decimal)          | KBAUD        | %ERROR | (decimal)          | KBAUD        | %ERROR | (decimal)          |

| 0.3          | NA           | _      | _                  | NA           | _      | _                  | 0.31         | +3.13  | 255                |

| 1.2          | 1.202        | +0.16  | 129                | 1.203        | _0.23  | 92                 | 1.2          | 0      | 65                 |

| 2.4          | 2.404        | +0.16  | 64                 | 2.380        | -0.83  | 46                 | 2.4          | 0      | 32                 |

| 9.6          | 9.766        | +1.73  | 15                 | 9.322        | -2.90  | 11                 | 9.9          | -3.13  | 7                  |

| 19.2         | 19.53        | +1.73  | 7                  | 18.64        | -2.90  | 5                  | 19.8         | +3.13  | 3                  |

| 76.8         | 78.13        | +1.73  | 1                  | NA           | _      | —                  | 79.2         | +3.13  | 0                  |

| 96           | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 300          | NA           | _      | —                  | NA           | _      | —                  | NA           | _      | _                  |

| 500          | NA           | _      | _                  | NA           | _      | _                  | NA           | _      | _                  |

| HIGH         | 156.3        | _      | 0                  | 111.9        | _      | 0                  | 79.2         | _      | 0                  |

| LOW          | 0.610        | —      | 255                | 0.437        | —      | 255                | 0.309        | _      | 2 <b>55</b>        |

| BAUD         | Fosc = 3.579 | MHz    | SPBRG              | Fosc = 1 MH  | z      | SPBRG              | FOSC = 32.76 | 8 kHz  | SPBRG              |

| RATE<br>(K)  | KBAUD        | %ERROR | value<br>(decimal) | KBAUD        | %ERROR | value<br>(decimal) | KBAUD        | %ERROR | value<br>(decimal) |

| 0.3          | 0.301        | +0.23  | 185                | 0.300        | +0.16  | 51                 | 0.256        | -14.67 | 1                  |

| 1.2          | 1.190        | -0.83  | 46                 | 1.202        | +0.16  | 12                 | NA           | —      | —                  |

| 2.4          | 2.432        | +1.32  | 22                 | 2.232        | -6.99  | 6                  | NA           | —      | —                  |

| 9.6          | 9.322        | -2.90  | 5                  | NA           | _      | _                  | NA           | _      | _                  |

| 19.2         | 18.64        | -2.90  | 2                  | NA           | —      | —                  | NA           | —      | —                  |

| 76.8         | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 96           | NA           | _      | _                  | NA           | _      | _                  | NA           | _      | _                  |

| 300          | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 500          | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| HIGH         | 55.93        | _      | 0                  | 15.63        | _      | 0                  | 0.512        | _      | 0                  |

| l mon        |              |        |                    |              |        |                    |              |        |                    |

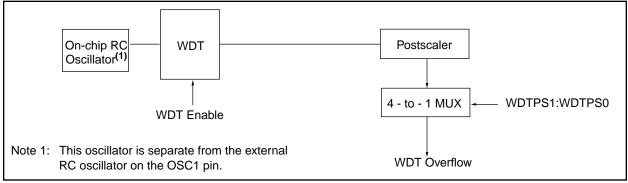

#### FIGURE 14-8: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 14-4: REGISTERS/BITS ASSOCIATED WITH THE WATCHDOG TIMER

| Address       | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------|-------|-------|-------|--------|--------|--------|-------|-------|-------------------------------|-----------------------------------------|

| —             | Config | -     | PM1   | -     | PM0    | WDTPS1 | WDTPS0 | FOSC1 | FOSC0 | (Note 2)                      | (Note 2)                                |

| 06h, Unbanked | CPUSTA |       |       | STKAV | GLINTD | TO     | PD     |       | —     | 11 11                         | 11 qq                                   |

Legend: - = unimplemented read as '0', q - value depends on condition, shaded cells are not used by the WDT.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

2: This value will be as the device was programmed, or if unprogrammed, will read as all '1's.

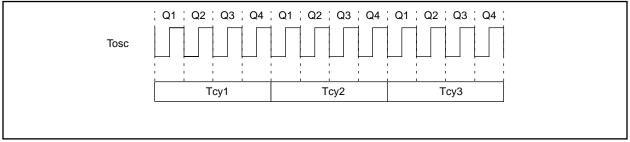

#### 15.2 <u>Q Cycle Activity</u>

Each instruction cycle (Tcy) is comprised of four Q cycles (Q1-Q4). The Q cycles provide the timing/designation for the Decode, Read, Execute, Write etc., of each instruction cycle. The following diagram shows the relationship of the Q cycles to the instruction cycle.

The 4 Q cycles that make up an instruction cycle (Tcy) can be generalized as:

- Q1: Instruction Decode Cycle or forced NOP

- Q2: Instruction Read Cycle or NOP

- Q3: Instruction Execute

- Q4: Instruction Write Cycle or NOP

Each instruction will show the detailed Q cycle operation for the instruction.

#### FIGURE 15-2: Q CYCLE ACTIVITY

| CPFS                                                                                                 | SLT                      |                                                                      | Compare f with WREG,<br>skip if f < WREG                                                                                                                                                                                                                                                            |         |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|--|--|

| Synta                                                                                                | ax:                      | [label]                                                              | [label] CPFSLT f                                                                                                                                                                                                                                                                                    |         |  |  |  |  |  |  |  |

| Opera                                                                                                | ands:                    | $0 \le f \le 25$                                                     | $0 \le f \le 255$                                                                                                                                                                                                                                                                                   |         |  |  |  |  |  |  |  |

| Opera                                                                                                | ation:                   | skip if (f) <                                                        | (f) – (WREG),<br>skip if (f) < (WREG)<br>(unsigned comparison)                                                                                                                                                                                                                                      |         |  |  |  |  |  |  |  |

| Statu                                                                                                | s Affected:              | None                                                                 |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |  |  |

| Enco                                                                                                 | ding:                    | 0011                                                                 | 0000 ffi                                                                                                                                                                                                                                                                                            | ff ffff |  |  |  |  |  |  |  |

| Desc                                                                                                 | ription:                 | location 'f'<br>performing<br>If the conte<br>WREG, the<br>discarded | Compares the contents of data memory<br>location 'f' to the contents of WREG by<br>performing an unsigned subtraction.<br>If the contents of 'f' < the contents of<br>WREG, then the fetched instruction is<br>discarded and an NOP is executed<br>instead making this a two-cycle instruc-<br>tion |         |  |  |  |  |  |  |  |

| Word                                                                                                 | s:                       | 1                                                                    |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |  |  |

| Cycle                                                                                                | es:                      | 1 (2)                                                                | 1 (2)                                                                                                                                                                                                                                                                                               |         |  |  |  |  |  |  |  |

| Q Cy                                                                                                 | cle Activity:            |                                                                      |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |  |  |

|                                                                                                      | Q1                       | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                                  | Q4      |  |  |  |  |  |  |  |

|                                                                                                      | Decode                   | Read<br>register 'f'                                                 | Execute                                                                                                                                                                                                                                                                                             | NOP     |  |  |  |  |  |  |  |

| lf skip                                                                                              | o:                       |                                                                      |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |  |  |

| -                                                                                                    | Q1                       | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                                  | Q4      |  |  |  |  |  |  |  |

|                                                                                                      | Forced NOP               | NOP                                                                  | Execute                                                                                                                                                                                                                                                                                             | NOP     |  |  |  |  |  |  |  |

| <u>Exarr</u>                                                                                         | nple:                    | HERE<br>NLESS<br>LESS                                                | CPFSLT REG<br>:<br>:                                                                                                                                                                                                                                                                                |         |  |  |  |  |  |  |  |

| E                                                                                                    | Before Instru<br>PC<br>W |                                                                      | ddress (HERE)                                                                                                                                                                                                                                                                                       |         |  |  |  |  |  |  |  |

| After Instruction<br>If REG < WREG;<br>PC = Address (LESS)<br>If REG ≥ WREG;<br>PC = Address (NLESS) |                          |                                                                      |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |  |  |

| DAW                 |                                                                  | Decimal                                       | Adjust WRE                                                                                                                                                                                     | G Register                                         |  |  |  |  |  |

|---------------------|------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| Syntax              | K:                                                               | [ <i>label</i> ] D                            | AW f,s                                                                                                                                                                                         |                                                    |  |  |  |  |  |

| Opera               | nds:                                                             | $0 \le f \le 25$<br>s $\in [0,1]$             | $0 \le f \le 255$<br>$s \in [0,1]$                                                                                                                                                             |                                                    |  |  |  |  |  |

| Opera               | tion:                                                            | WREG                                          | $ \begin{array}{l} \mbox{If [WREG<3:0>>9].OR. [DC = 1] then} \\ \mbox{WREG<3:0>+6 $\rightarrow$ f<3:0>, s<3:0>;} \\ \mbox{else} \\ \mbox{WREG<3:0>$\rightarrow$ f<3:0>, s<3:0>;} \end{array} $ |                                                    |  |  |  |  |  |

|                     |                                                                  | WREG                                          |                                                                                                                                                                                                | f<7:4>, s<7:4>                                     |  |  |  |  |  |

| Status              | Affected:                                                        | C                                             | $<7:4> \rightarrow f<7:$                                                                                                                                                                       | 4>, S<7:4>                                         |  |  |  |  |  |

| Encod               |                                                                  | 0010                                          | 111s ff                                                                                                                                                                                        | ff ffff                                            |  |  |  |  |  |

| Descri              | U                                                                |                                               | DAW adjusts the eight bit value in                                                                                                                                                             |                                                    |  |  |  |  |  |

|                     |                                                                  | BCD forma<br>packed BC<br>s = 0: R(<br>m<br>W | tion of two variables (each in packed<br>BCD format) and produces a correct<br>packed BCD result.<br>s = 0: Result is placed in Data<br>memory location 'f' and<br>WREG.                       |                                                    |  |  |  |  |  |

|                     |                                                                  |                                               | s = 1: Result is placed in Data memory location 'f'.                                                                                                                                           |                                                    |  |  |  |  |  |

| Words               | :                                                                | 1                                             |                                                                                                                                                                                                |                                                    |  |  |  |  |  |

| Cycles:             |                                                                  | 1                                             |                                                                                                                                                                                                |                                                    |  |  |  |  |  |

| Q Cyc               | le Activity:                                                     |                                               | 02 02 04                                                                                                                                                                                       |                                                    |  |  |  |  |  |

|                     | Q1<br>Decode                                                     | Q2<br>Read                                    | Q3<br>Execute                                                                                                                                                                                  | Q4<br>Write                                        |  |  |  |  |  |

|                     | Decode                                                           | register 'f'                                  | Execute                                                                                                                                                                                        | register 'f'<br>and other<br>specified<br>register |  |  |  |  |  |

| Exam                | ole1:                                                            | DAW RE                                        | G1, 0                                                                                                                                                                                          |                                                    |  |  |  |  |  |

| B                   | <br>efore Instru                                                 | iction                                        |                                                                                                                                                                                                |                                                    |  |  |  |  |  |

|                     | WREG<br>REG1<br>C<br>DC                                          | = 0xA5<br>= ??<br>= 0<br>= 0                  |                                                                                                                                                                                                |                                                    |  |  |  |  |  |

| At<br><u>Exam</u> p | fter Instruct<br>WREG<br>REG1<br>C<br>DC<br>DC<br><u>Dle 2</u> : | ion<br>= 0x05<br>= 0x05<br>= 1<br>= 0         |                                                                                                                                                                                                |                                                    |  |  |  |  |  |

| В                   | efore Instru                                                     |                                               |                                                                                                                                                                                                |                                                    |  |  |  |  |  |

|                     | WREG<br>REG1<br>C                                                | = 0xCE<br>= ??<br>= 0                         |                                                                                                                                                                                                |                                                    |  |  |  |  |  |

| U             | -    | 0    |

|---------------|------|------|

| DC            | =    | 0    |

| After Instruc | tion |      |

| WREG          | =    | 0x24 |

| REG1          | =    | 0x24 |

| С             | =    | 1    |

| DC            | =    | 0    |

| MOVLR                                                      | Move Literal to high nibble in BSR                                                                                                                                                                                                                                          |                              |  |  |  |  |  |  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|--|--|--|

| Syntax:                                                    | [ <i>label</i> ] MOVLR k                                                                                                                                                                                                                                                    |                              |  |  |  |  |  |  |

| Operands:                                                  | $0 \le k \le 15$                                                                                                                                                                                                                                                            |                              |  |  |  |  |  |  |

| Operation:                                                 | $k \rightarrow (BSR < 7:4>)$                                                                                                                                                                                                                                                | $k \rightarrow (BSR < 7:4>)$ |  |  |  |  |  |  |

| Status Affected:                                           | None                                                                                                                                                                                                                                                                        |                              |  |  |  |  |  |  |

| Encoding:                                                  | 1011 101x kkkk uuuu                                                                                                                                                                                                                                                         |                              |  |  |  |  |  |  |

| Description:                                               | The 4-bit literal 'k' is loaded into the<br>most significant 4-bits of the Bank<br>Select Register (BSR). Only the high<br>4-bits of the Bank Select Register<br>are affected. The lower half of the<br>BSR is unchanged. The assembler<br>will encode the "u" fields as 0. |                              |  |  |  |  |  |  |

| Words:                                                     | 1                                                                                                                                                                                                                                                                           |                              |  |  |  |  |  |  |

| Cycles:                                                    | 1                                                                                                                                                                                                                                                                           |                              |  |  |  |  |  |  |

| Q Cycle Activity:                                          |                                                                                                                                                                                                                                                                             |                              |  |  |  |  |  |  |

| Q1                                                         | Q2 Q3 Q4                                                                                                                                                                                                                                                                    |                              |  |  |  |  |  |  |

| Decode                                                     | Read literal         Execute         Write           'k:u'         literal 'k' to         BSR<7:4>                                                                                                                                                                          |                              |  |  |  |  |  |  |

| Example:                                                   | MOVLR 5                                                                                                                                                                                                                                                                     |                              |  |  |  |  |  |  |

| Before Instru<br>BSR regis<br>After Instructi<br>BSR regis | ion                                                                                                                                                                                                                                                                         |                              |  |  |  |  |  |  |

| Note: This i                                               | instruction is not available in th<br>C42 device.                                                                                                                                                                                                                           | e                            |  |  |  |  |  |  |

| MOVLW             | Move Lite            | Move Literal to WREG                           |      |                  |  |  |  |  |  |

|-------------------|----------------------|------------------------------------------------|------|------------------|--|--|--|--|--|

| Syntax:           | [ label ]            | MOVLW                                          | / k  |                  |  |  |  |  |  |

| Operands:         | $0 \le k \le 25$     | $0 \le k \le 255$                              |      |                  |  |  |  |  |  |

| Operation:        | $k \rightarrow (WR)$ | EG)                                            |      |                  |  |  |  |  |  |

| Status Affected:  | None                 |                                                |      |                  |  |  |  |  |  |

| Encoding:         | 1011                 | 0000                                           | kkkł | k kkkk           |  |  |  |  |  |

| Description:      | The eight b<br>WREG. | The eight bit literal 'k' is loaded into WREG. |      |                  |  |  |  |  |  |

| Words:            | 1                    |                                                |      |                  |  |  |  |  |  |

| Cycles:           | 1                    |                                                |      |                  |  |  |  |  |  |

| Q Cycle Activity: |                      |                                                |      |                  |  |  |  |  |  |

| Q1                | Q2                   | Q3                                             | 3    | Q4               |  |  |  |  |  |

| Decode            | Read<br>literal 'k'  | Execu                                          | ute  | Write to<br>WREG |  |  |  |  |  |

| Example:          | MOVLW                | 0x5A                                           |      |                  |  |  |  |  |  |

| After Instruct    | ion                  |                                                |      |                  |  |  |  |  |  |

WREG = 0x5A

| SUBWF                                   | Sub                               | trac                     | t WREG                                           | from             | h f              |                       |          |  |

|-----------------------------------------|-----------------------------------|--------------------------|--------------------------------------------------|------------------|------------------|-----------------------|----------|--|

| Syntax:                                 | [ lab                             | el]                      | SUBWF                                            | f,d              |                  |                       | -        |  |

| Operands:                               | -                                 | 0 ≤ f ≤ 255<br>d ∈ [0,1] |                                                  |                  |                  |                       |          |  |

| Operation:                              | (f) –                             | (W)                      | $\rightarrow$ (dest                              | )                |                  |                       |          |  |

| Status Affected:                        | OV,                               | C, D                     | C, Z                                             |                  |                  |                       | (        |  |

| Encoding:                               | 00                                | 00                       | 010d                                             | fff              | f                | ffff                  | :        |  |

| Description:                            | com<br>resu                       | pleme<br>It is si        | VREG fro<br>ent metho<br>tored in W<br>tored bac | d). If '<br>/REG | d' is<br>. If 'c | 0 the<br>I' is 1 the  | l        |  |

| Words:                                  | 1                                 |                          |                                                  |                  |                  |                       |          |  |

| Cycles:                                 | 1                                 |                          |                                                  |                  |                  |                       | ,        |  |

| Q Cycle Activity:                       |                                   |                          |                                                  |                  |                  |                       |          |  |

| Q1                                      | Qź                                |                          | Q3                                               | 3                |                  | Q4                    |          |  |

| Decode                                  | Rea<br>registe                    |                          | Execu                                            | ute              |                  | Vrite to<br>stination |          |  |

|                                         |                                   |                          | DECI                                             | 1                | ue               | Sunation              |          |  |

| Example 1:                              | SUB                               | NE                       | REG1,                                            | T                |                  |                       |          |  |

| Before Instru<br>REG1<br>WREG<br>C      | iction<br>= 3<br>= 2<br>= ?       |                          |                                                  |                  |                  |                       | <u> </u> |  |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= 1<br>= 2<br>= 1<br>= 0  | ;                        | result is p                                      | oositiv          | e                |                       |          |  |

| Example 2:                              |                                   |                          |                                                  |                  |                  |                       |          |  |

| Before Instru<br>REG1<br>WREG<br>C      | uction<br>= 2<br>= 2<br>= ?       |                          |                                                  |                  |                  |                       | <u> </u> |  |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= 0<br>= 2<br>= 1<br>= 1  | ;                        | result is z                                      | zero             |                  |                       |          |  |

| Example 3:                              |                                   |                          |                                                  |                  |                  |                       |          |  |

| Before Instru<br>REG1<br>WREG<br>C      | uction<br>= 1<br>= 2<br>= ?       |                          |                                                  |                  |                  |                       | ļ        |  |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= FI<br>= 2<br>= 0<br>= 0 |                          | result is r                                      | negativ          | ve               |                       |          |  |

| SUBWFB                                 | •••••                    | Subtract WREG from f with                                                         |                                           |                        |  |  |  |  |

|----------------------------------------|--------------------------|-----------------------------------------------------------------------------------|-------------------------------------------|------------------------|--|--|--|--|

| Syntax:                                |                          | Borrow<br>[label] SUBWFB f,d                                                      |                                           |                        |  |  |  |  |

| Operands:                              | -                        | -                                                                                 | J 1,u                                     |                        |  |  |  |  |

| Operands.                              | d ∈ [(                   | $0 \le f \le 255$<br>$d \in [0,1]$                                                |                                           |                        |  |  |  |  |

| Operation:                             | (f) — (                  | $(f)-(W)-\overline{C}\to(dest)$                                                   |                                           |                        |  |  |  |  |

| Status Affected                        | I: OV, C                 | OV, C, DC, Z                                                                      |                                           |                        |  |  |  |  |

| Encoding:                              | 000                      | 0000 001d ffff ffff                                                               |                                           |                        |  |  |  |  |

| Description:                           | (borro<br>ment<br>storec | act WREG ar<br>w) from regis<br>method). If 'd<br>I in WREG. If<br>I back in regi | ter 'f' (2's<br>' is 0 the<br>'d' is 1 th | s comple-<br>result is |  |  |  |  |

| Words:                                 | 1                        |                                                                                   |                                           |                        |  |  |  |  |

| Cycles:                                | 1                        | 1                                                                                 |                                           |                        |  |  |  |  |

| Q Cycle Activity                       | y:                       |                                                                                   |                                           |                        |  |  |  |  |

| Q1                                     | Q2                       | Q                                                                                 | 3                                         | Q4                     |  |  |  |  |

| Decode                                 | Read<br>register         |                                                                                   |                                           | Write to estination    |  |  |  |  |

| Example 1:                             | SUBWI                    | FB REG1,                                                                          | 1                                         |                        |  |  |  |  |

| Before Inst                            | truction                 |                                                                                   |                                           |                        |  |  |  |  |

| REG1<br>WREG<br>C                      | = 0x1<br>= 0x0<br>= 1    |                                                                                   | 1001)<br>1101)                            |                        |  |  |  |  |

| After Instru                           | uction                   |                                                                                   |                                           |                        |  |  |  |  |

| REG1<br>WREG<br>C                      | = 1                      | D (0000                                                                           | 1011)<br>1101)<br>t is posit              | ve                     |  |  |  |  |

| Z                                      | = 0                      |                                                                                   |                                           |                        |  |  |  |  |

| Example2:                              | SUBWF1                   | B REG1,0                                                                          |                                           |                        |  |  |  |  |

| Before Insi<br>REG1<br>WREG<br>C       | = 0x1                    | <b>(</b>                                                                          | 1011)<br>1010)                            |                        |  |  |  |  |

| After Instru                           | uction                   |                                                                                   |                                           |                        |  |  |  |  |

| REG1<br>WREG                           | = 0x1                    | •                                                                                 | 1011)                                     |                        |  |  |  |  |

| C<br>Z                                 | i = 0x0<br>= 1<br>= 1    |                                                                                   | ; result is zero                          |                        |  |  |  |  |

| Example3:                              | SUBWFI                   | B REG1,1                                                                          |                                           |                        |  |  |  |  |

| Before Inst<br>REG1<br>WREG<br>C       | = 0x0                    |                                                                                   | 0011)<br>1101)                            |                        |  |  |  |  |

| After Instru<br>REG1<br>WREG<br>C<br>Z | = 0xF                    | )E (0000                                                                          | 0100)<br>1101)<br>t is nega               | [2's comp]<br>tive     |  |  |  |  |

| Droduct                                                                                                                                               | ** MDI ADTM                             |                                   | MD-Drivo/Mov      |                              | *** DICMACTED®/                                                                                                                                                                                                                     |                                                                |                                                                                                                                                                             |                                                                                                                                                                                                                                  | DIC CTADT® DI         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|-------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|                                                                                                                                                       | Integrated                              | Compiler                          | Applications      | Explorer/Edition             | PICMASTER-CE                                                                                                                                                                                                                        | Low-Cost                                                       | II Universal                                                                                                                                                                | Ultra Low-Cost                                                                                                                                                                                                                   | Low-Cost              |

|                                                                                                                                                       | Development<br>Environment              |                                   | Code<br>Generator | Fuzzy Logic<br>Dev. Tool     | In-Circuit<br>Emulator                                                                                                                                                                                                              | In-Circuit<br>Emulator                                         | Microchip<br>Programmer                                                                                                                                                     | Dev. Kit                                                                                                                                                                                                                         | Universal<br>Dev. Kit |

| PIC12C508, 509                                                                                                                                        | SW007002                                | SW006005                          | 1                 | I                            | EM167015/<br>EM167101                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | 1                                                                                                                                                                                                                                | DV003001              |

| PIC14000                                                                                                                                              | SW007002                                | SW006005                          | I                 | I                            | EM147001/<br>EM147101                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | I                                                                                                                                                                                                                                | DV003001              |

| PIC16C52, 54, 54A,<br>55, 56, 57, 58A                                                                                                                 | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167015/<br>EM167101                                                                                                                                                                                                               | EM167201                                                       | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                         | DV003001              |

| PIC16C554, 556, 558                                                                                                                                   | SW007002                                | SW006005                          | 1                 | DV005001/<br>DV005002        | EM167033/<br>EM167113                                                                                                                                                                                                               | 1                                                              | DV007003                                                                                                                                                                    | I                                                                                                                                                                                                                                | DV003001              |

| PIC16C61                                                                                                                                              | SW007002                                | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167021/<br>N/A                                                                                                                                                                                                                    | EM167205                                                       | DV007003                                                                                                                                                                    | DV162003                                                                                                                                                                                                                         | DV003001              |