Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete           |

|----------------------------|--------------------|

| Core Processor             | PIC                |

| Core Size                  | 8-Bit              |

| Speed                      | 25MHz              |

| Connectivity               | UART/USART         |

| Peripherals                | POR, PWM, WDT      |

| Number of I/O              | 33                 |

| Program Memory Size        | 4KB (2K x 16)      |

| Program Memory Type        | ОТР                |

| EEPROM Size                | -                  |

| RAM Size                   | 232 x 8            |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V          |

| Data Converters            | -                  |

| Oscillator Type            | External           |

| Operating Temperature      | -40°C ~ 125°C (TA) |

| Mounting Type              | Surface Mount      |

| Package / Case             | 44-TQFP            |

| Supplier Device Package    | 44-TQFP (10x10)    |

|                            |                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABLE 3-1:  | FINU       | UT DES      |            |               |                |                                                                                                                                                                                                                                     |

|-------------|------------|-------------|------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name        | DIP<br>No. | PLCC<br>No. | QFP<br>No. | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                         |

| OSC1/CLKIN  | 19         | 21          | 37         | I             | ST             | Oscillator input in crystal/resonator or RC oscillator mode.<br>External clock input in external clock mode.                                                                                                                        |

| OSC2/CLKOUT | 20         | 22          | 38         | 0             |                | Oscillator output. Connects to crystal or resonator in crystal oscillator mode. In RC oscillator or external clock modes OSC2 pin outputs CLKOUT which has one fourth the frequency of OSC1 and denotes the instruction cycle rate. |

| MCLR/VPP    | 32         | 35          | 7          | I/P           | ST             | Master clear (reset) input/Programming Voltage (VPP) input.<br>This is the active low reset input to the chip.                                                                                                                      |

|             |            |             |            |               |                | PORTA is a bi-directional I/O Port except for RA0 and RA1 which are input only.                                                                                                                                                     |

| RA0/INT     | 26         | 28          | 44         | I             | ST             | RA0/INT can also be selected as an external interrupt<br>input. Interrupt can be configured to be on positive or<br>negative edge.                                                                                                  |

| RA1/T0CKI   | 25         | 27          | 43         | I             | ST             | RA1/T0CKI can also be selected as an external interrupt<br>input, and the interrupt can be configured to be on posi-<br>tive or negative edge. RA1/T0CKI can also be selected<br>to be the clock input to the Timer0 timer/counter. |

| RA2         | 24         | 26          | 42         | I/O           | ST             | High voltage, high current, open drain input/output port pins.                                                                                                                                                                      |

| RA3         | 23         | 25          | 41         | I/O           | ST             | High voltage, high current, open drain input/output port pins.                                                                                                                                                                      |

| RA4/RX/DT   | 22         | 24          | 40         | I/O           | ST             | RA4/RX/DT can also be selected as the USART (SCI)<br>Asynchronous Receive or USART (SCI) Synchronous<br>Data.                                                                                                                       |

| RA5/TX/CK   | 21         | 23          | 39         | I/O           | ST             | RA5/TX/CK can also be selected as the USART (SCI)<br>Asynchronous Transmit or USART (SCI) Synchronous<br>Clock.                                                                                                                     |

|             |            |             |            |               |                | PORTB is a bi-directional I/O Port with software configurable weak pull-ups.                                                                                                                                                        |

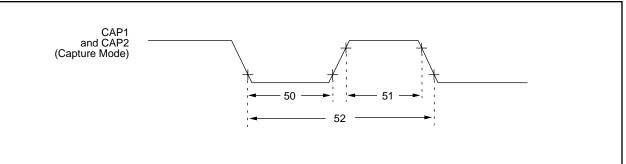

| RB0/CAP1    | 11         | 13          | 29         | I/O           | ST             | RB0/CAP1 can also be the CAP1 input pin.                                                                                                                                                                                            |

| RB1/CAP2    | 12         | 14          | 30         | I/O           | ST             | RB1/CAP2 can also be the CAP2 input pin.                                                                                                                                                                                            |

| RB2/PWM1    | 13         | 15          | 31         | I/O           | ST             | RB2/PWM1 can also be the PWM1 output pin.                                                                                                                                                                                           |

| RB3/PWM2    | 14         | 16          | 32         | I/O           | ST             | RB3/PWM2 can also be the PWM2 output pin.                                                                                                                                                                                           |

| RB4/TCLK12  | 15         | 17          | 33         | I/O           | ST             | RB4/TCLK12 can also be the external clock input to<br>Timer1 and Timer2.                                                                                                                                                            |

| RB5/TCLK3   | 16         | 18          | 34         | I/O           | ST             | RB5/TCLK3 can also be the external clock input to<br>Timer3.                                                                                                                                                                        |

| RB6         | 17         | 19          | 35         | I/O           | ST             |                                                                                                                                                                                                                                     |

| RB7         | 18         | 20          | 36         | I/O           | ST             |                                                                                                                                                                                                                                     |

|             |            |             |            |               |                | PORTC is a bi-directional I/O Port.                                                                                                                                                                                                 |

| RC0/AD0     | 2          | 3           | 19         | I/O           | TTL            | This is also the lower half of the 16-bit wide system bus                                                                                                                                                                           |

| RC1/AD1     | 3          | 4           | 20         | I/O           | TTL            | in microprocessor mode or extended microcontroller                                                                                                                                                                                  |

| RC2/AD2     | 4          | 5           | 21         | I/O           | TTL            | mode. In multiplexed system bus configuration, these pins are address output as well as data input or output.                                                                                                                       |

| RC3/AD3     | 5          | 6           | 22         | I/O           | TTL            |                                                                                                                                                                                                                                     |

| RC4/AD4     | 6          | 7           | 23         | I/O           | TTL            |                                                                                                                                                                                                                                     |

| RC5/AD5     | 7          | 8           | 24         | I/O           | TTL            |                                                                                                                                                                                                                                     |

| RC6/AD6     | 8          | 9           | 25         | I/O           | TTL            |                                                                                                                                                                                                                                     |

| RC7/AD7     | 9          | 10          | 26         | I/O           | TTL            |                                                                                                                                                                                                                                     |

TABLE 3-1:PINOUT DESCRIPTIONS

Legend: I = Input only; O = Output only; I/O = Input/Output; P = Power; — = Not Used; TTL = TTL input; ST = Schmitt Trigger input.

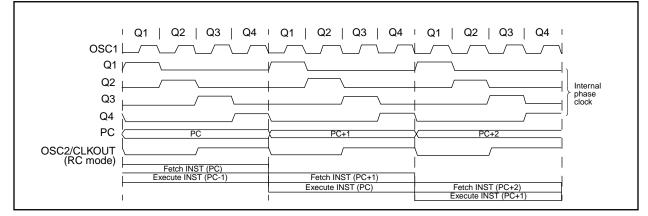

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-3.

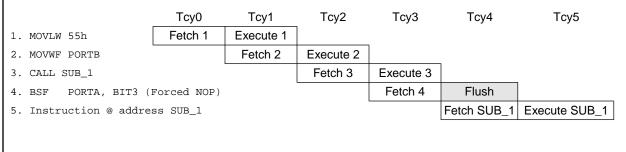

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g.GOTO) then two cycles are required to complete the instruction (Example 3-2).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-2: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

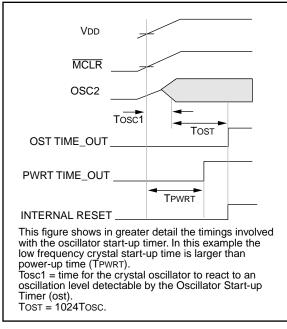

#### FIGURE 4-5: OSCILLATOR START-UPTIME

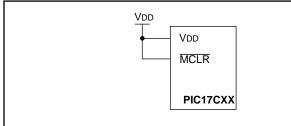

#### FIGURE 4-6: USING ON-CHIP POR

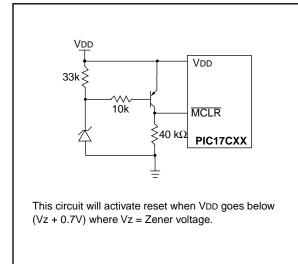

#### FIGURE 4-7: BROWN-OUT PROTECTION CIRCUIT 1

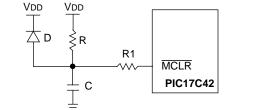

## FIGURE 4-8: PIC17C42 EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: An external Power-on Reset circuit is required only if VDD power-up time is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R < 40 k $\Omega$  is recommended to ensure that the voltage drop across R does not exceed 0.2V (max. leakage current spec. on the  $\overline{MCLR}/VPP$  pin is 5  $\mu$ A). A larger voltage drop will degrade VIH level on the  $\overline{MCLR}/VPP$  pin.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or (Electrical Overstress) EOS.

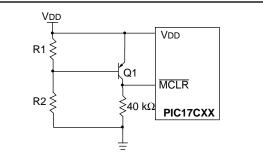

FIGURE 4-9: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

#### 5.1 Interrupt Status Register (INTSTA)

The Interrupt Status/Control register (INTSTA) records the individual interrupt requests in flag bits, and contains the individual interrupt enable bits (not for the peripherals).

The PEIF bit is a read only, bit wise OR of all the peripheral flag bits in the PIR register (Figure 5-4).

Note: T0IF, INTF, T0CKIF, or PEIF will be set by the specified condition, even if the corresponding interrupt enable bit is clear (interrupt disabled) or the GLINTD bit is set (all interrupts disabled).

Care should be taken when clearing any of the INTSTA register enable bits when interrupts are enabled (GLINTD is clear). If any of the INTSTA flag bits (T0IF, INTF, T0CKIF, or PEIF) are set in the same instruction cycle as the corresponding interrupt enable bit is cleared, the device will vector to the reset address (0x00).

When disabling any of the INTSTA enable bits, the GLINTD bit should be set (disabled).

### FIGURE 5-2: INTSTA REGISTER (ADDRESS: 07h, UNBANKED)

| bit $W = V$                                                                                                                                                                                                                                                                                                                | eadable bit<br>/ritable bit<br>/alue at POR reset                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| bit 7: <b>PEIF</b> : Peripheral Interrupt Flag bit<br>This bit is the OR of all peripheral interrupt flag bits AND'ed with their corres<br>1 = A peripheral interrupt is pending                                                                                                                                           | /alue at POR reset                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| bit 7: <b>PEIF</b> : Peripheral Interrupt Flag bit<br>This bit is the OR of all peripheral interrupt flag bits AND'ed with their corres<br>1 = A peripheral interrupt is pending                                                                                                                                           |                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                            | ponding enable bits.                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>bit 6: TOCKIF: External Interrupt on TOCKI Pin Flag bit</li> <li>This bit is cleared by hardware, when the interrupt logic forces program exercised</li> <li>1 = The software specified edge occurred on the RA1/T0CKI pin</li> <li>0 = The software specified edge did not occur on the RA1/T0CKI pin</li> </ul> | This bit is cleared by hardware, when the interrupt logic forces program execution to vector (18h).<br>1 = The software specified edge occurred on the RA1/T0CKI pin |  |  |  |  |  |  |  |  |  |  |

| bit 5: <b>T0IF</b> : TMR0 Overflow Interrupt Flag bit<br>This bit is cleared by hardware, when the interrupt logic forces program exer<br>1 = TMR0 overflowed<br>0 = TMR0 did not overflow                                                                                                                                 | This bit is cleared by hardware, when the interrupt logic forces program execution to vector (10h).<br>1 = TMR0 overflowed                                           |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>bit 4: INTF: External Interrupt on INT Pin Flag bit</li> <li>This bit is cleared by hardware, when the interrupt logic forces program exercise</li> <li>1 = The software specified edge occurred on the RA0/INT pin</li> <li>0 = The software specified edge did not occur on the RA0/INT pin</li> </ul>          | cution to vector (08h).                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>bit 3: PEIE: Peripheral Interrupt Enable bit</li> <li>This bit enables all peripheral interrupts that have their corresponding enabl</li> <li>1 = Enable peripheral interrupts</li> <li>0 = Disable peripheral interrupts</li> </ul>                                                                              | e bits set.                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

| bit 2: <b>TOCKIE</b> : External Interrupt on TOCKI Pin Enable bit<br>1 = Enable software specified edge interrupt on the RA1/TOCKI pin<br>0 = Disable interrupt on the RA1/TOCKI pin                                                                                                                                       |                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 1: <b>T0IE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enable TMR0 overflow interrupt<br>0 = Disable TMR0 overflow interrupt                                                                                                                                                                                       | 1 = Enable TMR0 overflow interrupt                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| bit 0: <b>INTE</b> : External Interrupt on RA0/INT Pin Enable bit<br>1 = Enable software specified edge interrupt on the RA0/INT pin<br>0 = Disable software specified edge interrupt on the RA0/INT pin                                                                                                                   |                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| TABLE 6-3: | SPECIAL FUNCTION REGISTERS |

|------------|----------------------------|

|------------|----------------------------|

| Address            | Name          | Bit 7                             | Bit 6                | Bit 5         | Bit 4        | Bit 3        | Bit 2           | Bit 1          | Bit 0           | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|---------------|-----------------------------------|----------------------|---------------|--------------|--------------|-----------------|----------------|-----------------|-------------------------------|-------------------------------------|

| Unbank             | ed            | •                                 |                      |               |              | •            |                 |                | •               |                               |                                     |

| 00h                | INDF0         | Uses con                          | tents of FSI         | R0 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 01h                | FSR0          | Indirect d                        | ata memory           | address po    | inter 0      |              |                 |                |                 | XXXX XXXX                     | uuuu uuuu                           |

| 02h                | PCL           | Low orde                          | r 8-bits of P        | С             |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | PCLATH        | Holding re                        | egister for u        | pper 8-bits o | of PC        |              |                 |                |                 | 0000 0000                     | uuuu uuuu                           |

| 04h                | ALUSTA        | FS3                               | FS2                  | FS1           | FS0          | OV           | Z               | DC             | С               | 1111 xxxx                     | 1111 uuuu                           |

| 05h                | TOSTA         | INTEDG                            | TOSE                 | TOCS          | PS3          | PS2          | PS1             | PS0            | —               | 0000 000-                     | 0000 000-                           |

| 06h <b>(2)</b>     | CPUSTA        | _                                 | _                    | STKAV         | GLINTD       | TO           | PD              | _              | _               | 11 11                         | 11 qq                               |

| 07h                | INTSTA        | PEIF                              | TOCKIF               | T0IF          | INTF         | PEIE         | TOCKIE          | TOIE           | INTE            | 0000 0000                     | 0000 0000                           |

| 08h                | INDF1         | Uses con                          | tents of FSI         | R1 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 09h                | FSR1          | Indirect d                        | ata memory           | address po    | inter 1      |              | , ,             |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ah                | WREG          | Working r                         | egister              |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Bh                | TMR0L         | TMR0 reg                          | gister; low b        | yte           |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ch                | TMR0H         | TMR0 reg                          | gister; high I       | oyte          |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Dh                | TBLPTRL       | Low byte                          | of program           | memory tab    | le pointer   |              |                 |                |                 | (4)                           | (4)                                 |

| 0Eh                | TBLPTRH       | High byte                         | of program           | memory tal    | ole pointer  |              |                 |                |                 | (4)                           | (4)                                 |

| 0Fh                | BSR           | Bank sele                         | Bank select register |               |              |              |                 |                |                 |                               | 0000 0000                           |

| Bank 0             |               | 1                                 |                      |               |              |              |                 |                |                 | I                             |                                     |

| 10h                | PORTA         | RBPU                              | _                    | RA5           | RA4          | RA3          | RA2             | RA1/T0CKI      | RA0/INT         | 0-xx xxxx                     | 0-uu uuuu                           |

| 11h                | DDRB          | Data dire                         | ction registe        | er for PORTE  | 3            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 12h                | PORTB         | PORTB d                           | ata latch            |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | RCSTA         | SPEN                              | RX9                  | SREN          | CREN         | —            | FERR            | OERR           | RX9D            | 0000 -00x                     | 0000 -00u                           |

| 14h                | RCREG         | Serial por                        | t receive re         | gister        |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | TXSTA         | CSRC                              | TX9                  | TXEN          | SYNC         | —            | —               | TRMT           | TX9D            | 00001x                        | 00001u                              |

| 16h                | TXREG         | Serial por                        | t transmit re        | egister       |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | SPBRG         | Baud rate                         | generator            | register      |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| Bank 1             |               |                                   |                      |               |              |              |                 |                |                 |                               |                                     |

| 10h                | DDRC          | Data dire                         | ction registe        | er for PORT   | 2            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 11h                | PORTC         | RC7/<br>AD7                       | RC6/<br>AD6          | RC5/<br>AD5   | RC4/<br>AD4  | RC3/<br>AD3  | RC2/<br>AD2     | RC1/<br>AD1    | RC0/<br>AD0     | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | DDRD          | Data dire                         | ction registe        | er for PORTI  | )            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 4.01-              | PORTD         | RD7/<br>AD15                      | RD6/<br>AD14         | RD5/<br>AD13  | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10    | RD1/<br>AD9    | RD0/<br>AD8     | xxxx xxxx                     | uuuu uuuu                           |

| 13h                |               | Data direction register for PORTE |                      |               |              |              |                 |                |                 |                               | 111                                 |

| 13h<br>14h         | DDRE          | Data dire                         |                      |               |              |              |                 | -              |                 |                               |                                     |

|                    | DDRE<br>PORTE | Data dire                         | _                    | _             | _            | _            | RE2/WR          | RE1/OE         | RE0/ALE         | xxx                           | uuu                                 |

| 14h                |               | RBIF                              | —<br>TMR3IF          | —<br>TMR2IF   | —<br>TMR1IF  | —<br>CA2IF   | RE2/WR<br>CA1IF | RE1/OE<br>TXIF | RE0/ALE<br>RCIF | xxx<br>0000 0010              | uuu<br>0000 0010                    |

x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated Legend: Note 1:

from or transferred to the upper byte of the program counter. The TO and PD status bits in CPUSTA are not affected by a MCLR reset. 2:

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

4:

The following values are for both TBLPTRL and TBLPTRH: All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000) except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu)

5: The PRODL and PRODH registers are not implemented on the PIC17C42.

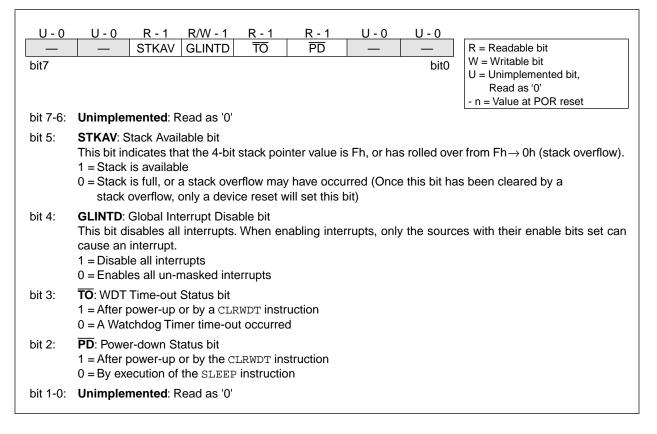

#### 6.2.2.2 CPU STATUS REGISTER (CPUSTA)

The CPUSTA register contains the status and control bits for the CPU. This register is used to globally enable/disable interrupts. If only a specific interrupt is desired to be enabled/disabled, please refer to the INTerrupt STAtus (INTSTA) register and the Peripheral Interrupt Enable (PIE) register. This register also indicates if the stack is available and contains the Power-down (PD) and Time-out (TO) bits. The TO, PD, and STKAV bits are not writable. These bits are set and cleared according to device logic. Therefore, the result of an instruction with the CPUSTA register as destination may be different than intended.

#### FIGURE 6-8: CPUSTA REGISTER (ADDRESS: 06h, UNBANKED)

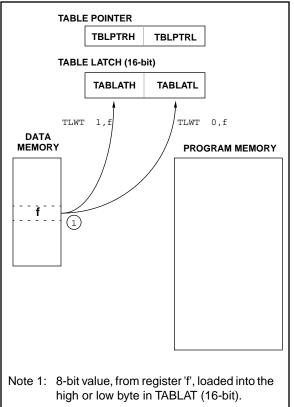

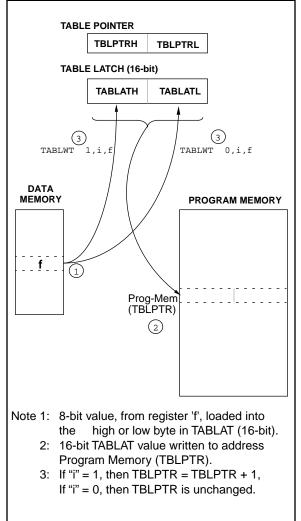

### 7.0 TABLE READS AND TABLE WRITES

The PIC17C4X has four instructions that allow the processor to move data from the data memory space to the program memory space, and vice versa. Since the program memory space is 16-bits wide and the data memory space is 8-bits wide, two operations are required to move 16-bit values to/from the data memory.

The TLWT t,f and TABLWT t,i,f instructions are used to write data from the data memory space to the program memory space. The TLRD t,f and TABLRD t,i,f instructions are used to write data from the program memory space to the data memory space.

The program memory can be internal or external. For the program memory access to be external, the device needs to be operating in extended microcontroller or microprocessor mode.

Figure 7-1 through Figure 7-4 show the operation of these four instructions.

#### FIGURE 7-2: TABLWT INSTRUCTION OPERATION

© 1996 Microchip Technology Inc.

Example 8-4 shows the sequence to do an 16 x 16 signed multiply. Equation 8-2 shows the algorithm that used. The 32-bit result is stored in four registers RES3:RES0. To account for the sign bits of the arguments, each argument pairs most significant bit (MSb) is tested and the appropriate subtractions are done.

| EQUATION 8-2: | 16 x 16 SIGNED |

|---------------|----------------|

|               | MULTIPLICATION |

|               | ALGORITHM      |

RES3:RES0

- = ARG1H:ARG1L \* ARG2H:ARG2L

- - (-1 \* ARG1H<7> \* ARG2H:ARG2L \* 2<sup>16</sup>)

# EXAMPLE 8-4: 16 x 16 SIGNED MULTIPLY

|     |          | ROUTI       | N | E                |

|-----|----------|-------------|---|------------------|

|     | MOVFP    | ARG1L, WREG |   |                  |

|     | MULWF    | ARG2L       | ; | ARG1L * ARG2L -> |

|     |          |             |   | PRODH:PRODL      |

|     | MOVPF    | PRODH, RES1 |   |                  |

|     |          | PRODL, RESO |   |                  |

| ;   |          | - ,         |   |                  |

|     | MOVFP    | ARG1H, WREG |   |                  |

|     |          |             |   | ARG1H * ARG2H -> |

|     | 110201   | into bii    | ; |                  |

|     | MOVPF    | PRODH, RES3 |   | TRODUCTRODE      |

|     |          | PRODL, RES2 |   |                  |

| ;   | 110 11 1 | TRODE, REDZ | ' |                  |

| '   | MOVFP    | ARG1L, WREG |   |                  |

|     |          |             |   | ARG1L * ARG2H -> |

|     | HOLMI    | 1110211     | ; |                  |

|     | MOVFP    | PRODL, WREG |   | TRODITITRODE     |

|     |          |             |   | Add cross        |

|     |          |             |   |                  |

|     |          |             | ; | products         |

|     |          |             |   |                  |

|     |          | WREG, F     | ; |                  |

|     | ADDWFC   | RES3, F     | ; |                  |

| ;   | NOTED    |             |   |                  |

|     |          | ARG1H, WREG | ' |                  |

|     | MULWF    | ARG2L       |   | ARG1H * ARG2L -> |

|     |          |             | , | PRODH:PRODL      |

|     | MOMED    |             |   |                  |

|     |          | PRODL, WREG |   | Add man          |

|     | ADDWF    | RES1, F     |   |                  |

|     |          | PRODH, WREG |   | products         |

|     |          |             | ; |                  |

|     | CLRF     | WREG, F     | ; |                  |

|     | ADDWFC   | RES3, F     | ; |                  |

| ;   |          |             |   |                  |

|     |          | ARG2H, 7    | ' | ARG2H:ARG2L neg? |

|     |          |             |   | no, check ARG1   |

|     | MOVFP    | ARG1L, WREG |   |                  |

|     |          | RES2        | ; |                  |

|     | MOVFP    | ARG1H, WREG | ; |                  |

|     | SUBWFB   | RES3        |   |                  |

| ;   |          |             |   |                  |

| SIC | GN_ARG1  |             |   |                  |

|     |          |             |   | ARG1H:ARG1L neg? |

|     | GOTO     | CONT_CODE   |   | no, done         |

|     |          | ARG2L, WREG |   |                  |

|     | SUBWF    | RES2        | ; |                  |

|     | MOVFP    | ARG2H, WREG | ; |                  |

|     | SUBWFB   | RES3        |   |                  |

| ;   |          |             |   |                  |

| COI | NT_CODE  |             |   |                  |

|     | :        |             |   |                  |

### 11.0 TIMER0

The Timer0 module consists of a 16-bit timer/counter, TMR0. The high byte is TMR0H and the low byte is TMR0L. A software programmable 8-bit prescaler makes an effective 24-bit overflow timer. The clock source is also software programmable as either the internal instruction clock or the RA1/T0CKI pin. The control bits for this module are in register T0STA (Figure 11-1).

| R/W - 0        | R/W - 0                                                              | R/W - 0                     | R/W - 0                                                            | R/W - 0                    | R/W - 0                  | R/W - 0 | U - 0     |                                                                                                      |  |

|----------------|----------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------|----------------------------|--------------------------|---------|-----------|------------------------------------------------------------------------------------------------------|--|

| INTEDG<br>bit7 | TOSE                                                                 | TOCS                        | PS3                                                                | PS2                        | PS1                      | PS0     | —<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented,<br>Read as '0'<br>-n = Value at POR reset |  |

| bit 7:         | <b>INTEDG</b> : R<br>This bit sele<br>1 = Rising e<br>0 = Falling e  | ects the ed<br>edge of RA   | ge upon w<br>0/INT pin g                                           | hich the in<br>generates i | terrupt is d<br>nterrupt | etected |           | -n = value al POR lesel                                                                              |  |

| bit 6:         |                                                                      |                             |                                                                    |                            |                          |         |           |                                                                                                      |  |

| bit 5:         | <b>TOCS</b> : Time<br>This bit self<br>1 = Internal<br>0 = TOCKI     | ects the clo<br>instruction | ck source                                                          | for TMR0.                  |                          |         |           |                                                                                                      |  |

| bit 4-1:       | <b>PS3:PS0</b> : T<br>These bits                                     |                             |                                                                    |                            | R0.                      |         |           |                                                                                                      |  |

|                | PS3:PS0                                                              | Pre                         | scale Valu                                                         | е                          |                          |         |           |                                                                                                      |  |

|                | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1xxx |                             | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 |                            |                          |         |           |                                                                                                      |  |

| bit 0:         | Unimplem                                                             | <b>ented</b> : Rea          | id as '0'                                                          |                            |                          |         |           |                                                                                                      |  |

#### FIGURE 11-1: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

#### © 1996 Microchip Technology Inc.

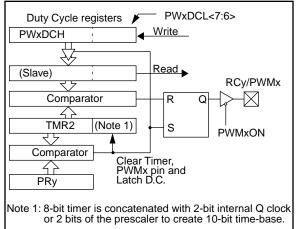

#### 12.1.3 USING PULSE WIDTH MODULATION (PWM) OUTPUTS WITH TMR1 AND TMR2

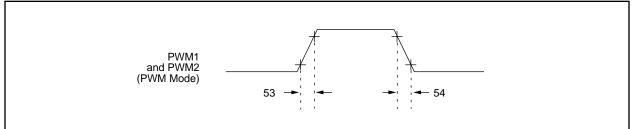

Two high speed pulse width modulation (PWM) outputs are provided. The PWM1 output uses Timer1 as its time-base, while PWM2 may be software configured to use either Timer1 or Timer2 as the time-base. The PWM outputs are on the RB2/PWM1 and RB3/PWM2 pins.

Each PWM output has a maximum resolution of 10-bits. At 10-bit resolution, the PWM output frequency is 24.4 kHz (@ 25 MHz clock) and at 8-bit resolution the PWM output frequency is 97.7 kHz. The duty cycle of the output can vary from 0% to 100%.

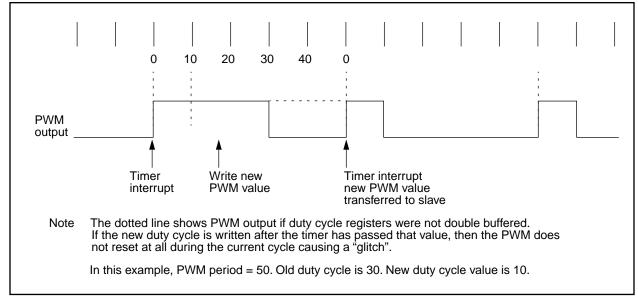

Figure 12-5 shows a simplified block diagram of the PWM module. The duty cycle register is double buffered for glitch free operation. Figure 12-6 shows how a glitch could occur if the duty cycle registers were not double buffered.

The user needs to set the PWM1ON bit (TCON2<4>) to enable the PWM1 output. When the PWM1ON bit is set, the RB2/PWM1 pin is configured as PWM1 output and forced as an output irrespective of the data direction bit (DDRB<2>). When the PWM1ON bit is clear, the pin behaves as a port pin and its direction is controlled by its data direction bit (DDRB<2>). Similarly, the PWM2ON (TCON2<5>) bit controls the configuration of the RB3/PWM2 pin.

#### FIGURE 12-5: SIMPLIFIED PWM BLOCK DIAGRAM

#### FIGURE 12-6: PWM OUTPUT

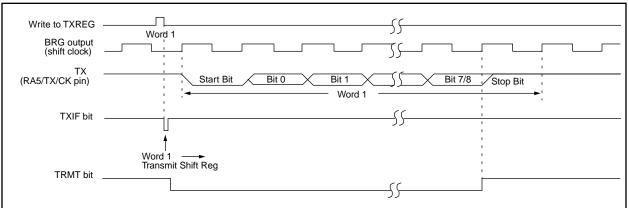

#### FIGURE 13-5: ASYNCHRONOUS MASTER TRANSMISSION

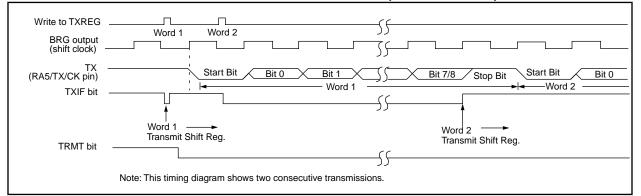

### FIGURE 13-6: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 13-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                                        | Name  | Bit 7       | Bit 6       | Bit 5   | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------------|-------------|---------|--------|-------|-------|-------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 1                                    | PIR   | RBIF        | TMR3IF      | TMR2IF  | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF      | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0                                    | RCSTA | SPEN        | RX9         | SREN    | CREN   | —     | FERR  | OERR  | RX9D      | x00- 0000                     | 0000 -00u                               |

| 16h, Bank 0                                    | TXREG | Serial port | transmit re | egister |        |       |       |       |           | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1                                    | PIE   | RBIE        | TMR3IE      | TMR2IE  | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE      | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0                                    | TXSTA | CSRC        | TX9         | TXEN    | SYNC   | —     | —     | TRMT  | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |             |             |         |        |       |       |       | xxxx xxxx | uuuu uuuu                     |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

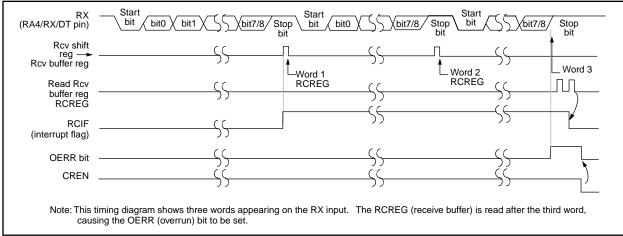

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

#### FIGURE 13-8: ASYNCHRONOUS RECEPTION

| <b>TABLE 13-6</b> : | <b>REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION</b> |

|---------------------|---------------------------------------------------------|

|                     |                                                         |

| Address                                        | Name  | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|--------|--------|--------|-------|-------|-------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 1                                    | PIR   | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF      | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9    | SREN   | CREN   | —     | FERR  | OERR  | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0                                    | RCREG | RX7   | RX6    | RX5    | RX4    | RX3   | RX2   | RX1   | RX0       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1                                    | PIE   | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE      | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9    | TXEN   | SYNC   | —     | —     | TRMT  | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |        |        |        |       |       |       | xxxx xxxx | uuuu uuuu                     |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous reception. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

| CPFS         | SLT                                            | Compare<br>skip if f <                                               | f with WREG                                                                                                                                                                                                                                                                                 | G,      |  |  |  |  |  |  |

|--------------|------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|--|

| Synta        | ax:                                            | [label]                                                              | CPFSLT f                                                                                                                                                                                                                                                                                    |         |  |  |  |  |  |  |

| Opera        | ands:                                          | $0 \le f \le 25$                                                     | 5                                                                                                                                                                                                                                                                                           |         |  |  |  |  |  |  |

| Opera        | ation:                                         | (f) – (WRE<br>skip if (f) <<br>(unsigned                             | G),<br>(WREG)<br>comparison)                                                                                                                                                                                                                                                                |         |  |  |  |  |  |  |

| Statu        | s Affected:                                    | None                                                                 |                                                                                                                                                                                                                                                                                             |         |  |  |  |  |  |  |

| Enco         | ding:                                          | 0011                                                                 | 0000 ffi                                                                                                                                                                                                                                                                                    | ff ffff |  |  |  |  |  |  |

| Desc         | ription:                                       | location 'f'<br>performing<br>If the conte<br>WREG, the<br>discarded | Compares the contents of data memory<br>location 'f' to the contents of WREG by<br>performing an unsigned subtraction.<br>If the contents of 'f' < the contents of<br>WREG, then the fetched instruction is<br>discarded and an NOP is executed<br>instead making this a two-cycle instruc- |         |  |  |  |  |  |  |

| Word         | s:                                             | 1                                                                    |                                                                                                                                                                                                                                                                                             |         |  |  |  |  |  |  |

| Cycle        | es:                                            | 1 (2)                                                                |                                                                                                                                                                                                                                                                                             |         |  |  |  |  |  |  |

| Q Cy         | cle Activity:                                  |                                                                      |                                                                                                                                                                                                                                                                                             |         |  |  |  |  |  |  |

|              | Q1                                             | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                          | Q4      |  |  |  |  |  |  |

|              | Decode                                         | Read<br>register 'f'                                                 | Execute                                                                                                                                                                                                                                                                                     | NOP     |  |  |  |  |  |  |

| lf skip      | o:                                             |                                                                      |                                                                                                                                                                                                                                                                                             |         |  |  |  |  |  |  |

| -            | Q1                                             | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                          | Q4      |  |  |  |  |  |  |

|              | Forced NOP                                     | NOP                                                                  | Execute                                                                                                                                                                                                                                                                                     | NOP     |  |  |  |  |  |  |

| <u>Exarr</u> | nple:                                          | HERE<br>NLESS<br>LESS                                                | CPFSLT REG<br>:<br>:                                                                                                                                                                                                                                                                        |         |  |  |  |  |  |  |

| E            | Before Instru<br>PC<br>W                       |                                                                      | ddress (HERE)                                                                                                                                                                                                                                                                               |         |  |  |  |  |  |  |

| ŀ            | After Instruct<br>If REG<br>PC<br>If REG<br>PC | < W<br>= Ac<br>≥ W                                                   | REG;<br>ddress (LESS)<br>REG;<br>ddress (NLESS                                                                                                                                                                                                                                              |         |  |  |  |  |  |  |

| DAW                 |                                                | Decimal                                                      | Decimal Adjust WREG Register                                                                                                                                                                                      |                                                    |  |  |  |

|---------------------|------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| Syntax              | K:                                             | [ <i>label</i> ] D                                           | AW f,s                                                                                                                                                                                                            |                                                    |  |  |  |

| Opera               | nds:                                           | $0 \le f \le 25$<br>s $\in [0,1]$                            | 5                                                                                                                                                                                                                 |                                                    |  |  |  |

| Opera               | tion:                                          | <sup>-</sup> WREG<br>else                                    |                                                                                                                                                                                                                   | [DC = 1] then<br>f<3:0>, s<3:0>;<br>0>, s<3:0>;    |  |  |  |

|                     |                                                | WREG                                                         |                                                                                                                                                                                                                   | f<7:4>, s<7:4>                                     |  |  |  |

| Status              | Affected:                                      | C                                                            | $<7:4> \rightarrow f<7:$                                                                                                                                                                                          | 4>, S<7:4>                                         |  |  |  |

| Encod               |                                                | 0010                                                         | 111s ff                                                                                                                                                                                                           | ff ffff                                            |  |  |  |

| Descri              | U                                              |                                                              | ts the eight bi                                                                                                                                                                                                   |                                                    |  |  |  |

|                     |                                                | tion of two<br>BCD forma<br>packed BC<br>s = 0: Ro<br>m<br>W | WREG resulting from the earlier addi-<br>tion of two variables (each in packed<br>BCD format) and produces a correct<br>packed BCD result.<br>s = 0: Result is placed in Data<br>memory location 'f' and<br>WREG. |                                                    |  |  |  |

|                     |                                                |                                                              | esult is placed<br>emory locatio                                                                                                                                                                                  |                                                    |  |  |  |

| Words               | :                                              | 1                                                            |                                                                                                                                                                                                                   |                                                    |  |  |  |

| Cycles              | 8:                                             | 1                                                            |                                                                                                                                                                                                                   |                                                    |  |  |  |

| Q Cyc               | le Activity:                                   |                                                              |                                                                                                                                                                                                                   | •                                                  |  |  |  |

|                     | Q1<br>Decode                                   | Q2<br>Read                                                   | Q3<br>Execute                                                                                                                                                                                                     | Q4<br>Write                                        |  |  |  |

|                     | Decode                                         | register 'f'                                                 | Execute                                                                                                                                                                                                           | register 'f'<br>and other<br>specified<br>register |  |  |  |

| Exam                | ole1:                                          | DAW RE                                                       | G1, 0                                                                                                                                                                                                             |                                                    |  |  |  |

| B                   | <br>efore Instru                               | iction                                                       |                                                                                                                                                                                                                   |                                                    |  |  |  |

|                     | WREG<br>REG1<br>C<br>DC                        | = 0xA5<br>= ??<br>= 0<br>= 0                                 |                                                                                                                                                                                                                   |                                                    |  |  |  |

| Ai<br><u>Exam</u> t | fter Instruct<br>WREG<br>REG1<br>C<br>DC<br>DC | ion<br>= 0x05<br>= 0x05<br>= 1<br>= 0                        |                                                                                                                                                                                                                   |                                                    |  |  |  |

| В                   | efore Instru                                   |                                                              |                                                                                                                                                                                                                   |                                                    |  |  |  |

|                     | WREG<br>REG1<br>C                              | = 0xCE<br>= ??<br>= 0                                        |                                                                                                                                                                                                                   |                                                    |  |  |  |

| U             | -    | 0    |

|---------------|------|------|

| DC            | =    | 0    |

| After Instruc | tion |      |

| WREG          | =    | 0x24 |

| REG1          | =    | 0x24 |

| С             | =    | 1    |

| DC            | =    | 0    |

| DCF        | SNZ                                                          | Decreme                                                                          | nt f, skip if                                                                                                                                                                                                                                                                                                                   | not ( | 0                      |  |  |

|------------|--------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|--|--|

| Syn        | tax:                                                         | [ <i>label</i> ] D                                                               | CFSNZ f,c                                                                                                                                                                                                                                                                                                                       | 1     |                        |  |  |

| Ope        | rands:                                                       | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                                          | 5                                                                                                                                                                                                                                                                                                                               |       |                        |  |  |

| Ope        | ration:                                                      |                                                                                  | (f) – 1 $\rightarrow$ (dest);<br>skip if not 0                                                                                                                                                                                                                                                                                  |       |                        |  |  |

| Stat       | us Affected:                                                 | None                                                                             |                                                                                                                                                                                                                                                                                                                                 |       |                        |  |  |

| Enc        | oding:                                                       | 0010                                                                             | 011d f:                                                                                                                                                                                                                                                                                                                         | Eff   | ffff                   |  |  |

| Des        | cription:                                                    | mented. If<br>WREG. If back in reg<br>If the result<br>which is all<br>and an NO | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'.<br>If the result is not 0, the next instruction,<br>which is already fetched, is discarded,<br>and an NOP is executed instead mak-<br>ing it a two-cycle instruction. |       |                        |  |  |

| Wor        | ds:                                                          | 1                                                                                |                                                                                                                                                                                                                                                                                                                                 |       |                        |  |  |

| Cyc        | les:                                                         | 1(2)                                                                             |                                                                                                                                                                                                                                                                                                                                 |       |                        |  |  |

| QC         | ycle Activity:                                               |                                                                                  |                                                                                                                                                                                                                                                                                                                                 |       |                        |  |  |

|            | Q1                                                           | Q2                                                                               | Q3                                                                                                                                                                                                                                                                                                                              |       | Q4                     |  |  |

|            | Decode                                                       | Read<br>register 'f'                                                             | Execute                                                                                                                                                                                                                                                                                                                         |       | Write to<br>estination |  |  |

| lf sk      | ip:                                                          |                                                                                  |                                                                                                                                                                                                                                                                                                                                 |       |                        |  |  |

|            | Q1                                                           | Q2                                                                               | Q3                                                                                                                                                                                                                                                                                                                              |       | Q4                     |  |  |

|            | Forced NOP                                                   | NOP                                                                              | Execute                                                                                                                                                                                                                                                                                                                         |       | NOP                    |  |  |

| <u>Exa</u> | <u>mple</u> :                                                | HERE<br>ZERO<br>NZERO                                                            | DCFSNZ TI<br>:<br>:                                                                                                                                                                                                                                                                                                             | EMP,  | 1                      |  |  |

|            | Before Instru<br>TEMP_V                                      |                                                                                  | ?                                                                                                                                                                                                                                                                                                                               |       |                        |  |  |

|            | After Instruct<br>TEMP_V<br>If TEMP_<br>PC<br>If TEMP_<br>PC | ALUE =<br>VALUE =<br>=                                                           | TEMP_VA<br>0;<br>Address (<br>0;<br>Address (                                                                                                                                                                                                                                                                                   | ZERO  | )                      |  |  |

| Synta            | av.           | [ label ]                                                                                                                                                                                                           | GOTO                                                                                                   | k    |      |  |

|------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|------|--|

| -                | ands:         | [ <i>iabei</i> ]<br>0 ≤ k ≤ 81                                                                                                                                                                                      |                                                                                                        | ĸ    |      |  |

| •                |               |                                                                                                                                                                                                                     |                                                                                                        |      |      |  |