Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 25MHz                                                                       |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 4KB (2K x 16)                                                               |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 232 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-QFP                                                                      |

| Supplier Device Package    | 44-MQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42at-25i-pq |

#### 4.1.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (1024Tosc) delay after  $\overline{\text{MCLR}}$  is detected high or a wake-up from SLEEP event occurs.

The OST time-out is invoked only for XT and LF oscillator modes on a Power-on Reset or a Wake-up from SLEEP.

The OST counts the oscillator pulses on the OSC1/CLKIN pin. The counter only starts incrementing after the amplitude of the signal reaches the oscillator input thresholds. This delay allows the crystal oscillator or resonator to stabilize before the device exits reset. The length of time-out is a function of the crystal/resonator frequency.

#### 4.1.4 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First the internal POR signal goes high when the POR trip point is reached. If MCLR is high, then both the OST and PWRT timers start. In general the PWRT time-out is longer, except with low frequency crystals/resonators. The total time-out also varies based on oscillator configuration. Table 4-1 shows the times that are associated with the oscillator configuration. Figure 4-2 and Figure 4-3 display these time-out sequences.

If the device voltage is not within electrical specification at the end of a time-out, the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be held low until the voltage is within the device specification. The use of an external RC delay is sufficient for many of these applications.

TABLE 4-1: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator<br>Configuration | Power-up                            | Wake up<br>from<br>SLEEP | MCLR<br>Reset |

|-----------------------------|-------------------------------------|--------------------------|---------------|

| XT, LF                      | Greater of:<br>96 ms or<br>1024Tosc | 1024Tosc                 | _             |

| EC, RC                      | Greater of:<br>96 ms or<br>1024Tosc | _                        | _             |

The time-out sequence begins from the first rising edge of  $\overline{\text{MCLR}}$ .

Table 4-3 shows the reset conditions for some special registers, while Table 4-4 shows the initialization conditions for all the registers. The shaded registers (in Table 4-4) are for all devices except the PIC17C42. In the PIC17C42, the PRODH and PRODL registers are general purpose RAM.

TABLE 4-2: STATUS BITS AND THEIR SIGNIFICANCE

| TO | PD | Event                                                                              |

|----|----|------------------------------------------------------------------------------------|

| 1  | 1  | Power-on Reset, MCLR Reset during normal operation, or CLRWDT instruction executed |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP                            |

| 0  | 1  | WDT Reset during normal operation                                                  |

| 0  | 0  | WDT Reset during SLEEP                                                             |

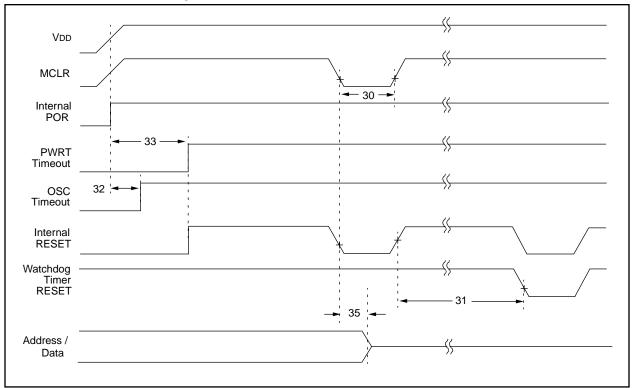

In Figure 4-2, Figure 4-3 and Figure 4-4, TPWRT > TOST, as would be the case in higher frequency crystals. For lower frequency crystals, (i.e., 32 kHz) TOST would be greater.

TABLE 4-3: RESET CONDITION FOR THE PROGRAM COUNTER AND THE CPUSTA REGISTER

| Event                              | PCH:PCL         | CPUSTA                | OST Active |         |

|------------------------------------|-----------------|-----------------------|------------|---------|

| Power-on Reset                     |                 | 0000h                 | 11 11      | Yes     |

| MCLR Reset during normal operation |                 | 0000h                 | 11 11      | No      |

| MCLR Reset during SLEEP            |                 | 0000h                 | 11 10      | Yes (2) |

| WDT Reset during normal opera      | ation           | 0000h                 | 11 01      | No      |

| WDT Reset during SLEEP (3)         |                 | 0000h                 | 11 00      | Yes (2) |

| Interrupt wake-up from SLEEP       | GLINTD is set   | PC + 1                | 11 10      | Yes (2) |

|                                    | GLINTD is clear | PC + 1 <sup>(1)</sup> | 10 10      | Yes (2) |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0'.

- Note 1: On wake-up, this instruction is executed. The instruction at the appropriate interrupt vector is fetched and then executed.

- 2: The OST is only active when the Oscillator is configured for XT or LF modes.

- 3: The Program Counter = 0, that is the device branches to the reset vector. This is different from the mid-range devices.

NOTES:

Peripheral Data in RBPU (PORTA<7>) Weak Pull-Up Match Signal\_ from other, port pins **RBIF** Port Input Latch Data Bus RD\_DDRB (Q2) RD\_PORTB (Q2) D  $\overline{\mathsf{OE}}$ WR\_DDRB (Q4) **~**\_CK D Port Q Data WR\_PORTB (Q4) PWM\_output PWM\_select Note: I/O pins have protection diodes to VDD and Vss.

FIGURE 9-5: **BLOCK DIAGRAM OF RB3 AND RB2 PORT PINS**

# 10.0 OVERVIEW OF TIMER RESOURCES

The PIC17C4X has four timer modules. Each module can generate an interrupt to indicate that an event has occurred. These timers are called:

- Timer0 16-bit timer with programmable 8-bit prescaler

- Timer1 8-bit timer

- Timer2 8-bit timer

- Timer3 16-bit timer

For enhanced time-base functionality, two input Captures and two Pulse Width Modulation (PWM) outputs are possible. The PWMs use the TMR1 and TMR2 resources and the input Captures use the TMR3 resource.

#### 10.1 <u>Timer0 Overview</u>

The Timer0 module is a simple 16-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock.

The Timer0 module also has a programmable prescaler option. The PS3:PS0 bits (T0STA<4:1>) determine the prescaler value. TMR0 can increment at the following rates: 1:1, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, 1:256.

When Timer0's clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

### 10.2 <u>Timer1 Overview</u>

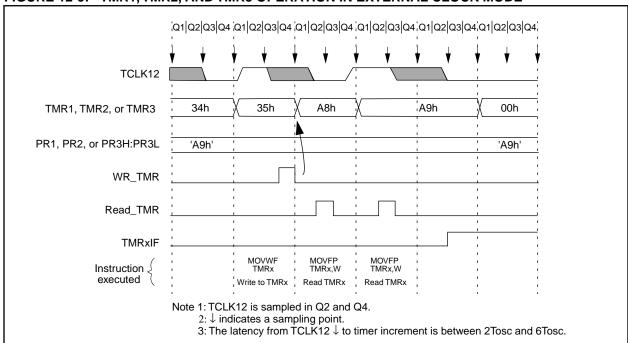

The TImer0 module is an 8-bit timer/counter with an 8-bit period register (PR1). When the TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the Timer2 module.

TMR1 can be concatenated to TMR2 to form a 16-bit timer. The TMR1 register is the LSB and TMR2 is the MSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled.

### 10.3 <u>Timer2 Overview</u>

The TMR2 module is an 8-bit timer/counter with an 8-bit period register (PR2). When the TMR2 value rolls over from the period match value to 0h, the TMR2IF flag is set, and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the TMR1 module.

TMR1 can be concatenated to TMR2 to form a 16-bit timer. The TMR2 register is the MSB and TMR1 is the LSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled.

### 10.4 <u>Timer3 Overview</u>

The TImer3 module is a 16-bit timer/counter with a 16-bit period register. When the TMR3H:TMR3L value rolls over to 0h, the TMR3IF bit is set and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB5/TCLK3 pin.

When operating in the dual capture mode, the period registers become the second 16-bit capture register.

#### 10.5 Role of the Timer/Counters

The timer modules are general purpose, but have dedicated resources associated with them. Tlmer1 and Timer2 are the time-bases for the two Pulse Width Modulation (PWM) outputs, while Timer3 is the time-base for the two input captures.

#### 12.2.3 EXTERNAL CLOCK INPUT FOR TIMER3

When TMR3CS is set, the 16-bit TMR3 increments on the falling edge of clock input TCLK3. The input on the RB5/TCLK3 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on TCLK3 to the time TMR3 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section. Figure 12-9 shows the timing diagram when operating from an external clock.

#### 12.2.4 READING/WRITING TIMER3

Since Timer3 is a 16-bit timer and only 8-bits at a time can be read or written, care should be taken when reading or writing while the timer is running. The best method to read or write the timer is to stop the timer, perform any read or write operation, and then restart Timer3 (using the TMR3ON bit). However, if it is necessary to keep Timer3 free-running, care must be taken. For writing to the 16-bit TMR3, Example 12-2 may be used. For reading the 16-bit TMR3, Example 12-3 may be used. Interrupts must be disabled during this routine.

#### **EXAMPLE 12-2: WRITING TO TMR3**

BSF CPUSTA, GLINTD ;Disable interrupt

MOVFP RAM\_L, TMR3L ;

MOVFP RAM\_H, TMR3H ;

BCF CPUSTA, GLINTD ;Done,enable interrupt

#### **EXAMPLE 12-3: READING FROM TMR3**

| MOVPF  | TMR3L, | TMPLO | <pre>;read low tmr0</pre>    |

|--------|--------|-------|------------------------------|

| MOVPF  | TMR3H, | TMPHI | <pre>;read high tmr0</pre>   |

| MOVFP  | TMPLO, | WREG  | <pre>;tmplo -&gt; wreg</pre> |

| CPFSLT | TMR3L, | WREG  | <pre>;tmr01 &lt; wreg?</pre> |

| RETURN |        |       | ;no then return              |

| MOVPF  | TMR3L, | TMPLO | <pre>;read low tmr0</pre>    |

| MOVPF  | TMR3H, | TMPHI | <pre>;read high tmr0</pre>   |

| RETURN |        |       | ;return                      |

FIGURE 12-9: TMR1, TMR2, AND TMR3 OPERATION IN EXTERNAL CLOCK MODE

TABLE 13-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address                                        | Name  | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|--------|--------|--------|-------|-------|-----------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 1                                    | PIR   | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF      | RCIF      | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9    | SREN   | CREN   | _     | FERR  | OERR      | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 16h, Bank 0                                    | TXREG | TX7   | TX6    | TX5    | TX4    | TX3   | TX2   | TX1       | TX0       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1                                    | PIE   | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE      | RCIE      | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9    | TXEN   | SYNC   | _     | _     | TRMT      | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |        |        |        |       |       | xxxx xxxx | uuuu uuuu |                               |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous slave transmission.

Note 1: Other (non power-up) resets include: external reset through  $\overline{MCLR}$  and Watchdog Timer Reset.

#### TABLE 13-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address                                       | Name  | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets (Note1) |

|-----------------------------------------------|-------|-------|--------|--------|--------|-------|-----------|-----------|-------|-------------------------------|-----------------------------------|

| 16h, Bank1                                    | PIR   | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF     | TXIF      | RCIF  | 0000 0010                     | 0000 0010                         |

| 13h, Bank0                                    | RCSTA | SPEN  | RX9    | SREN   | CREN   |       | FERR      | OERR      | RX9D  | 0000 -00x                     | 0000 -00u                         |

| 14h, Bank0                                    | RCREG | RX7   | RX6    | RX5    | RX4    | RX3   | RX2       | RX1       | RX0   | xxxx xxxx                     | uuuu uuuu                         |

| 17h, Bank1                                    | PIE   | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE     | TXIE      | RCIE  | 0000 0000                     | 0000 0000                         |

| 15h, Bank 0                                   | TXSTA | CSRC  | TX9    | TXEN   | SYNC   | _     |           | TRMT      | TX9D  | 00001x                        | 00001u                            |

| 17h, Bank0 SPBRG Baud rate generator register |       |       |        |        |        |       | xxxx xxxx | uuuu uuuu |       |                               |                                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous slave reception.

Note 1: Other (non power-up) resets include: external reset through  $\overline{\text{MCLR}}$  and Watchdog Timer Reset.

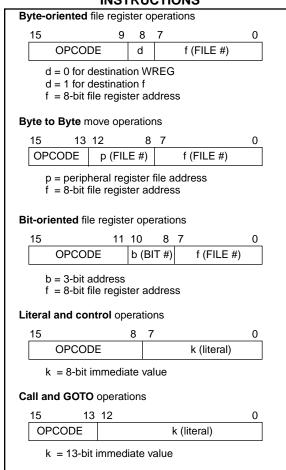

Table 15-2 lists the instructions recognized by the MPASM assembler.

**Note 1:** Any unused opcode is Reserved. Use of any reserved opcode may cause unexpected operation.

**Note 2:** The shaded instructions are not available in the PIC17C42

All instruction examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

To represent a binary number:

0000 0100b

where b signifies a binary string.

## FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

## 15.1 <u>Special Function Registers as</u> Source/Destination

The PIC17C4X's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 15.1.1 ALUSTA AS DESTINATION

If an instruction writes to ALUSTA, the Z, C, DC and OV bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF ALUSTA will clear register ALUSTA, and then set the Z bit leaving 0000 0100b in the register.

#### 15.1.2 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

Read PC:  $PCH \rightarrow PCLATH; PCL \rightarrow dest$

Write PCL: PCLATH  $\rightarrow$  PCH;

8-bit destination value → PCL

Read-Modify-Write: PCL→ ALU operand

$\begin{array}{l} \mathsf{PCLATH} \to \mathsf{PCH}; \\ \mathsf{8\text{-}bit\ result} \to \ \mathsf{PCL} \end{array}$

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 15.1.3 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write). The user should keep this in mind when operating on special function registers, such as ports.

TABLE 15-2: PIC17CXX INSTRUCTION SET

| Mnemonic, |        | Description                           | Cycles | 16-bit Opcod   | е    | Status    | Notes |

|-----------|--------|---------------------------------------|--------|----------------|------|-----------|-------|

| Operands  |        |                                       |        | MSb            | LSb  | Affected  |       |

| BYTE-ORIE | NTED I | FILE REGISTER OPERATIONS              | •      |                |      |           | •     |

| ADDWF     | f,d    | ADD WREG to f                         | 1      | 0000 111d ffff | ffff | OV,C,DC,Z |       |

| ADDWFC    | f,d    | ADD WREG and Carry bit to f           | 1      | 0001 000d ffff | ffff | OV,C,DC,Z |       |

| ANDWF     | f,d    | AND WREG with f                       | 1      | 0000 101d ffff | ffff | Z         |       |

| CLRF      | f,s    | Clear f, or Clear f and Clear WREG    | 1      | 0010 100s ffff | ffff | None      | 3     |

| COMF      | f,d    | Complement f                          | 1      | 0001 001d ffff | ffff | Z         |       |

| CPFSEQ    | f      | Compare f with WREG, skip if f = WREG | 1 (2)  | 0011 0001 ffff | ffff | None      | 6,8   |

| CPFSGT    | f      | Compare f with WREG, skip if f > WREG | 1 (2)  | 0011 0010 ffff | ffff | None      | 2,6,8 |

| CPFSLT    | f      | Compare f with WREG, skip if f < WREG | 1 (2)  | 0011 0000 ffff | ffff | None      | 2,6,8 |

| DAW       | f,s    | Decimal Adjust WREG Register          | 1      | 0010 111s ffff | ffff | С         | 3     |

| DECF      | f,d    | Decrement f                           | 1      | 0000 011d ffff | ffff | OV,C,DC,Z |       |

| DECFSZ    | f,d    | Decrement f, skip if 0                | 1 (2)  | 0001 011d ffff | ffff | None      | 6,8   |

| DCFSNZ    | f,d    | Decrement f, skip if not 0            | 1 (2)  | 0010 011d ffff | ffff | None      | 6,8   |

| INCF      | f,d    | Increment f                           | 1      | 0001 010d ffff | ffff | OV,C,DC,Z |       |

| INCFSZ    | f,d    | Increment f, skip if 0                | 1 (2)  | 0001 111d ffff | ffff | None      | 6,8   |

| INFSNZ    | f,d    | Increment f, skip if not 0            | 1 (2)  | 0010 010d ffff | ffff | None      | 6,8   |

| IORWF     | f,d    | Inclusive OR WREG with f              | 1      | 0000 100d ffff | ffff | Z         |       |

| MOVFP     | f,p    | Move f to p                           | 1      | 011p pppp ffff | ffff | None      |       |

| MOVPF     | p,f    | Move p to f                           | 1      | 010p pppp ffff | ffff | Z         |       |

| MOVWF     | f      | Move WREG to f                        | 1      | 0000 0001 ffff | ffff | None      |       |

| MULWF     | f      | Multiply WREG with f                  | 1      | 0011 0100 ffff | ffff | None      | 9     |

| NEGW      | f,s    | Negate WREG                           | 1      | 0010 110s ffff | ffff | OV,C,DC,Z | 1,3   |

| NOP       | _      | No Operation                          | 1      | 0000 0000 0000 | 0000 | None      |       |

| RLCF      | f,d    | Rotate left f through Carry           | 1      | 0001 101d ffff | ffff | С         |       |

| RLNCF     | f,d    | Rotate left f (no carry)              | 1      | 0010 001d ffff | ffff | None      |       |

| RRCF      | f,d    | Rotate right f through Carry          | 1      | 0001 100d ffff | ffff | С         |       |

| RRNCF     | f,d    | Rotate right f (no carry)             | 1      | 0010 000d ffff | ffff | None      |       |

| SETF      | f,s    | Set f                                 | 1      | 0010 101s ffff | ffff | None      | 3     |

| SUBWF     | f,d    | Subtract WREG from f                  | 1      | 0000 010d ffff | ffff | OV,C,DC,Z | 1     |

| SUBWFB    | f,d    | Subtract WREG from f with Borrow      | 1      | 0000 001d ffff | ffff | OV,C,DC,Z | 1     |

| SWAPF     | f,d    | Swap f                                | 1      | 0001 110d ffff | ffff | None      |       |

| TABLRD    | t,i,f  | Table Read                            | 2 (3)  | 1010 10ti ffff | ffff | None      | 7     |

Legend: Refer to Table 15-1 for opcode field descriptions.

- Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

- 3: If s = 11', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- 5: Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

| DECF              | Decreme                        | ent f                                                                                                                    |   |    |  |  |

|-------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------|---|----|--|--|

| Syntax:           | [ label ]                      | DECF f,                                                                                                                  | d |    |  |  |

| Operands:         | $0 \le f \le 25$ $d \in [0,1]$ | $0 \le f \le 255$<br>$d \in [0,1]$                                                                                       |   |    |  |  |

| Operation:        | $(f)-1\rightarrow$             | (dest)                                                                                                                   |   |    |  |  |

| Status Affected:  | OV, C, D                       | C, Z                                                                                                                     |   |    |  |  |

| Encoding:         | 0000 011d ffff ffff            |                                                                                                                          |   |    |  |  |

| Description:      | result is st                   | Decrement register 'f'. If 'd' is 0 the result is stored in WREG. If 'd' is 1 the result is stored back in register 'f'. |   |    |  |  |

| Words:            | 1                              |                                                                                                                          |   |    |  |  |

| Cycles:           | 1                              |                                                                                                                          |   |    |  |  |

| Q Cycle Activity: |                                |                                                                                                                          |   |    |  |  |

| Q1                | Q2                             | Q3                                                                                                                       | 3 | Q4 |  |  |

|        | <b>~</b> -          | Q3      | Q4                   |

|--------|---------------------|---------|----------------------|

| Decode | Read<br>egister 'f' | Execute | Write to destination |

CNT,

1

Example: DECF

Before Instruction

$\begin{array}{rcl}

\mathsf{CNT} & = & \mathsf{0x01} \\

\mathsf{Z} & = & \mathsf{0}

\end{array}$

After Instruction CNT = 0x00

Z = 1

| DECFSZ           | Decreme                                                | ent f, ski                                                                                                                                     | ip if 0                    |          |  |  |

|------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------|--|--|

| Syntax:          | [ label ]                                              | DECFS                                                                                                                                          | Z f,d                      |          |  |  |

| Operands:        | $0 \le f \le 25$ $d \in [0,1]$                         | $0 \le f \le 255$<br>$d \in [0,1]$                                                                                                             |                            |          |  |  |

| Operation:       | (f) $-1 \rightarrow (dest)$ ;<br>skip if result = 0    |                                                                                                                                                |                            |          |  |  |

| Status Affected: | None                                                   |                                                                                                                                                |                            |          |  |  |

| Encoding:        | 0001                                                   | 011d                                                                                                                                           | ffff                       | ffff     |  |  |

| Description:     | mented. If<br>WREG. If                                 | The contents of register 'f' are decremented. If 'd' is 0 the result is placed in WREG. If 'd' is 1 the result is placed back in register 'f'. |                            |          |  |  |

|                  | If the resu<br>which is a<br>and an NO<br>ing it a two | Iready fet<br>DP is exec                                                                                                                       | ched, is di<br>cuted inste | scarded, |  |  |

| \A/ I            | 4                                                      |                                                                                                                                                |                            |          |  |  |

Words: 1 Cycles: 1(2)

Q Cycle Activity:

|             | Q1     | Q2                   | Q3      | Q4                   |

|-------------|--------|----------------------|---------|----------------------|

|             | Decode | Read<br>register 'f' | Execute | Write to destination |

| <u>Exar</u> | mple:  | HERE                 | DECFSZ  | CNT, 1               |

GOTO CONTINUE

LOOP

Before Instruction

PC = Address (HERE)

After Instruction

CNT = CNT - 1If CNT = 0;

PC = Address (CONTINUE)

If CNT  $\neq$  0;

PC = Address (HERE+1)

| INFSNZ            | Increme                       | ent f, skip    | if not 0                                             |           |

|-------------------|-------------------------------|----------------|------------------------------------------------------|-----------|

| Syntax:           | [label]                       | INFSNZ         | f,d                                                  |           |

| Operands:         | $0 \le f \le 2$ $d \in [0,1]$ |                |                                                      |           |

| Operation:        | (f) + 1 —                     | (dest), s      | kip if not                                           | 0         |

| Status Affected:  | None                          |                |                                                      |           |

| Encoding:         | 0010                          | 010d           | ffff                                                 | ffff      |

| Description:      | mented. I                     | f 'd' is 0 the | ister 'f' are<br>e result is p<br>e result is p      | placed in |

|                   | which is a<br>and an No       | already feto   | the next in<br>ched, is dis<br>uted instea<br>ction. | scarded,  |

| Words:            | 1                             |                |                                                      |           |

| Cycles:           | 1(2)                          |                |                                                      |           |

| Q Cycle Activity: |                               |                |                                                      |           |

| 0.4               | 00                            | 0.0            |                                                      | ~ 4       |

| Q1     | Q2                   | Q3      | Q4                   |

|--------|----------------------|---------|----------------------|

| Decode | Read<br>register 'f' | Execute | Write to destination |

|        | - 3                  |         |                      |

If skip:

| Q1         | Q2  | Q3      | Q4  |  |

|------------|-----|---------|-----|--|

| Forced NOP | NOP | Execute | NOP |  |

Example: HERE INFSNZ REG, 1 ZERO

NZERO

Before Instruction

REG = REG

After Instruction

REG = REG + 1

If REG = 1;

PC = Address (ZERO)

If REG = 0;

PC = Address (NZERO)

IORLW Inclusive OR Literal with WREG

Syntax: [ label ] IORLW k

Operands:  $0 \le k \le 255$

Operation: (WREG) .OR. (k)  $\rightarrow$  (WREG)

Status Affected: Z

Encoding: 1011 0011 kkkk kkkk

Description: The contents of WREG are OR'ed with

the eight bit literal 'k'. The result is

placed in WREG.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2                  | Q3      | Q4               |

|--------|---------------------|---------|------------------|

| Decode | Read<br>literal 'k' | Execute | Write to<br>WRFG |

Example: IORLW 0x35

Before Instruction

WREG = 0x9A

After Instruction

WREG = 0xBF

RETFIE Return from Interrupt

Syntax: [label] RETFIE

Operands: None

Operation:  $TOS \rightarrow (PC)$ ;

$0 \to \text{GLINTD};$

PCLATH is unchanged.

Status Affected: GLINTD

Encoding: 0000 0000 0000 0101

Description: Return from Interrupt. Stack is POP'ed and Top of Stack (TOS) is loaded in the PC. Interrupts are enabled by clearing the GLINTD bit. GLINTD is the global

interrupt disable bit (CPUSTA<4>).

Words: 1 Cycles: 2

Q Cycle Activity:

| Q1         | Q2                        | Q3      | Q4  |

|------------|---------------------------|---------|-----|

| Decode     | Read<br>register<br>T0STA | Execute | NOP |

| Forced NOP | NOP                       | Execute | NOP |

Example: RETFIE

After Interrupt

PC = TOS GLINTD = 0 RETLW Return Literal to WREG

Syntax: [label] RETLW k

Operands:  $0 \le k \le 255$

Operation:  $k \rightarrow (WREG); TOS \rightarrow (PC);$

PCLATH is unchanged

Status Affected: None

Encoding: 1011 0110 kkkk kkkk

Description: WREG is loaded with the eight bit literal 'k'. The program counter is loaded from

the top of the stack (the return address).

The high address latch (PCLATH)

remains unchanged.

Words: 1 Cycles: 2

Q Cycle Activity:

| Q1         | Q2          | Q3      | Q4       |

|------------|-------------|---------|----------|

| Decode     | Read        | Execute | Write to |

|            | literal 'k' |         | WREG     |

| Forced NOP | NOP         | Execute | NOP      |

Example: CALL TABLE ; WREG contains table

; offset value ; WREG now has ; table value

: TABLE

ADDWF PC ; WREG = offset RETLW k0 ; Begin table RETLW k1 ;

: :

RETLW kn ; End of table

Before Instruction

WREG = 0x07

After Instruction

WREG = value of k7

## PIC17C42 ELECTRICAL CHARACTERISTICS

## **Absolute Maximum Ratings †**

| Ambient temperature under bias                                                                                          | 55 to +125°C       |

|-------------------------------------------------------------------------------------------------------------------------|--------------------|

| Storage temperature                                                                                                     | 65°C to +150°C     |

| Voltage on VDD with respect to Vss                                                                                      | 0 to +7.5V         |

| Voltage on MCLR with respect to Vss (Note 2)                                                                            | 0.6V to +14V       |

| Voltage on RA2 and RA3 with respect to Vss                                                                              | 0.6V to +12V       |

| Voltage on all other pins with respect to Vss                                                                           | 0.6V to VDD + 0.6V |

| Total power dissipation (Note 1)                                                                                        | 1.0W               |

| Maximum current out of Vss pin(s) - Total                                                                               | 250 mA             |

| Maximum current into VDD pin(s) - Total                                                                                 | 200 mA             |

| nput clamp current, lik (Vi < 0 or Vi > VDD)                                                                            | ±20 mA             |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                          | ±20 mA             |

| Maximum output current sunk by any I/O pin (except RA2 and RA3)                                                         | 35 mA              |

| Maximum output current sunk by RA2 or RA3 pins                                                                          | 60 mA              |

| Maximum output current sourced by any I/O pin                                                                           | 20 mA              |

| Maximum current sunk by PORTA and PORTB (combined)                                                                      | 150 mA             |

| Maximum current sourced by PORTA and PORTB (combined)                                                                   | 100 mA             |

| Maximum current sunk by PORTC, PORTD and PORTE (combined)                                                               | 150 mA             |

| Maximum current sourced by PORTC, PORTD and PORTE (combined)                                                            | 100 mA             |

| <b>Note 1.</b> Power dissination is calculated as follows: Pdis = $VDD \times \{IDD - \sum IOH\} + \sum \{(VDD)^{-1}\}$ |                    |

- Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{MCLR}$  pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

© 1996 Microchip Technology Inc.

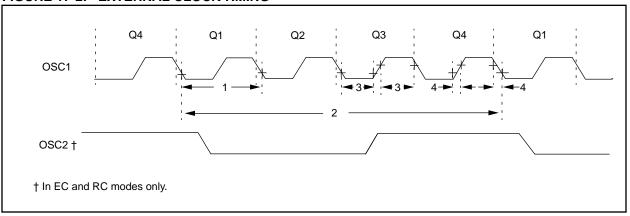

## 17.4 Timing Diagrams and Specifications

## FIGURE 17-2: EXTERNAL CLOCK TIMING

TABLE 17-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                    | Min  | Тур†   | Max   | Units | Conditions                |

|------------------|-------|-----------------------------------|------|--------|-------|-------|---------------------------|

|                  | Fosc  | External CLKIN Frequency          | DC   | _      | 16    | MHz   | EC osc mode - PIC17C42-16 |

|                  |       | (Note 1)                          | DC   | _      | 25    | MHz   | - PIC17C42-25             |

|                  |       | Oscillator Frequency              | DC   | _      | 4     | MHz   | RC osc mode               |

|                  |       | (Note 1)                          | 1    | _      | 16    | MHz   | XT osc mode - PIC17C42-16 |

|                  |       |                                   | 1    | _      | 25    | MHz   | - PIC17C42-25             |

|                  |       |                                   | DC   | _      | 2     | MHz   | LF osc mode               |

| 1                | Tosc  | External CLKIN Period             | 62.5 | _      | _     | ns    | EC osc mode - PIC17C42-16 |

|                  |       | (Note 1)                          | 40   | _      | _     | ns    | - PIC17C42-25             |

|                  |       | Oscillator Period                 | 250  | _      | _     | ns    | RC osc mode               |

|                  |       | (Note 1)                          | 62.5 | _      | 1,000 | ns    | XT osc mode - PIC17C42-16 |

|                  |       |                                   | 40   | _      | 1,000 | ns    | - PIC17C42-25             |

|                  |       |                                   | 500  | _      | _     | ns    | LF osc mode               |

| 2                | Tcy   | Instruction Cycle Time (Note 1)   | 160  | 4/Fosc | DC    | ns    |                           |

| 3                | TosL, | Clock in (OSC1) High or Low Time  | 10 ‡ | _      | _     | ns    | EC oscillator             |

|                  | TosH  |                                   |      |        |       |       |                           |

| 4                | TosR, | Clock in (OSC1) Rise or Fall Time | _    | _      | 5‡    | ns    | EC oscillator             |

|                  | TosF  |                                   |      |        |       |       |                           |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

<sup>†</sup> These parameters are for design guidance only and are not tested, nor characterized.

Applicable Devices | 42 | R42 | 42A | 43 | R43 | 44

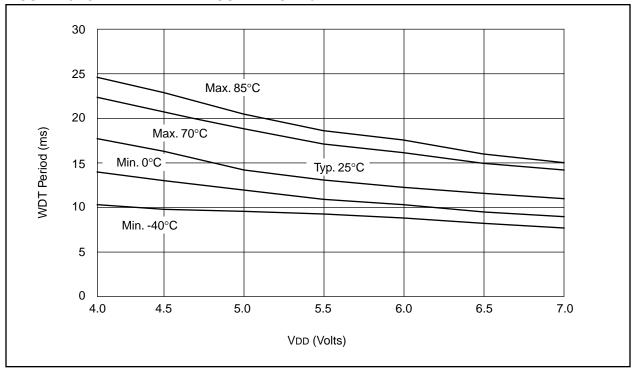

FIGURE 18-13: WDT TIMER TIME-OUT PERIOD vs. VDD

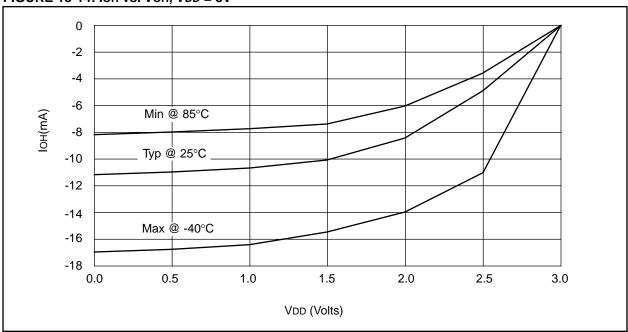

FIGURE 18-14: IOH vs. VOH, VDD = 3V

FIGURE 19-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, AND POWER-UP TIMER TIMING

TABLE 19-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                          |                              | Min  | Тур†      | Max   | Units | Conditions         |

|------------------|----------|-------------------------------------------------------------------------|------------------------------|------|-----------|-------|-------|--------------------|

| 30               | TmcL     | MCLR Pulse Width (low)                                                  | MCLR Pulse Width (low)       |      | _         | _     | ns    | VDD = 5V           |

| 31               | Twdt     | Watchdog Timer Time-out Period<br>(Prescale = 1)                        |                              | 5 *  | 12        | 25 *  | ms    | VDD = 5V           |

| 32               | Tost     | Oscillation Start-up Time                                               | r Period                     |      | 1024Tosc§ | _     | ms    | Tosc = OSC1 period |

| 33               | Tpwrt    | Power-up Timer Period                                                   |                              | 40 * | 96        | 200 * | ms    | VDD = 5V           |

| 35               | TmcL2adI | MCLR to System Inter-<br>face bus (AD15:AD0>)  PIC17CR42/42A/ 43/R43/44 |                              |      | _         | 100 * | ns    |                    |

|                  |          | invalid                                                                 | PIC17LCR42/<br>42A/43/R43/44 | _    | _         | 120 * | ns    |                    |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>‡</sup> These parameters are for design guidance only and are not tested, nor characterized.

<sup>§</sup> This specification ensured by design.

Applicable Devices | 42 | R42 | 42A | 43 | R43 | 44

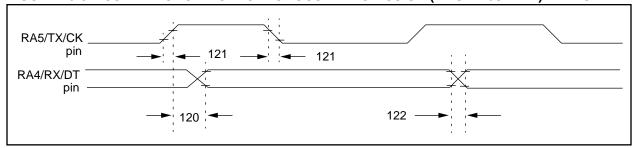

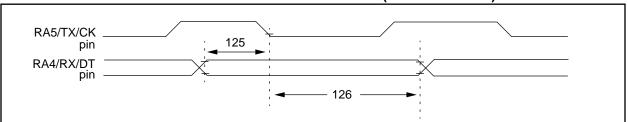

## FIGURE 19-9: USART MODULE: SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 19-9: SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                    |                          | Min | Тур† | Max | Units | Conditions |

|--------------|----------|-----------------------------------|--------------------------|-----|------|-----|-------|------------|

| 120          | TckH2dtV | SYNC XMIT (MASTER & SLAVE)        | PIC17CR42/42A/43/R43/44  | _   | _    | 50  | ns    |            |

|              |          | Clock high to data out valid      | PIC17LCR42/42A/43/R43/44 | _   | _    | 75  | ns    |            |

| 121          | TckRF    | Clock out rise time and fall time | PIC17CR42/42A/43/R43/44  | _   | _    | 25  | ns    |            |

|              |          | (Master Mode)                     | PIC17LCR42/42A/43/R43/44 | _   | _    | 40  | ns    |            |

| 122          | TdtRF    | Data out rise time and fall time  | PIC17CR42/42A/43/R43/44  | _   | _    | 25  | ns    |            |

|              |          |                                   | PIC17LCR42/42A/43/R43/44 | _   | _    | 40  | ns    |            |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## FIGURE 19-10: USART MODULE: SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## **TABLE 19-10: SYNCHRONOUS RECEIVE REQUIREMENTS**

| Parameter<br>No. | Sym      | Characteristic                                                | Min | Тур† | Max | Units | Conditions |

|------------------|----------|---------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE) Data hold before CK↓ (DT hold time) | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK↓ (DT hold time)                            | 15  | _    | _   | ns    |            |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices | 42 | R42 | 42A | 43 | R43 | 44

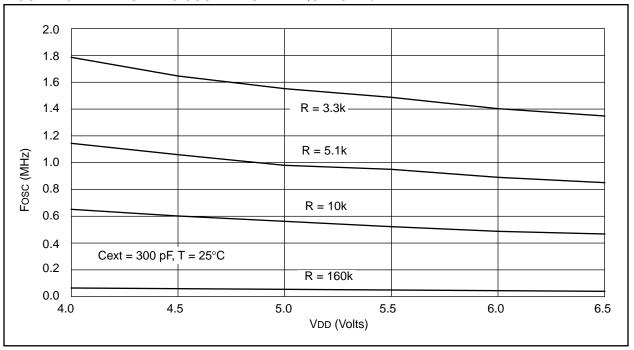

FIGURE 20-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

TABLE 20-2: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average<br>Fosc @ 5V, 25°C |       |  |

|--------|------|----------------------------|-------|--|

| 22 pF  | 10k  | 3.33 MHz                   | ± 12% |  |

|        | 100k | 353 kHz                    | ± 13% |  |

| 100 pF | 3.3k | 3.54 MHz                   | ± 10% |  |

|        | 5.1k | 2.43 MHz                   | ± 14% |  |

|        | 10k  | 1.30 MHz                   | ± 17% |  |

|        | 100k | 129 kHz                    | ± 10% |  |

| 300 pF | 3.3k | 1.54 MHz                   | ± 14% |  |

|        | 5.1k | 980 kHz                    | ± 12% |  |

|        | 10k  | 564 kHz                    | ± 16% |  |

|        | 160k | 35 kHz                     | ± 18% |  |

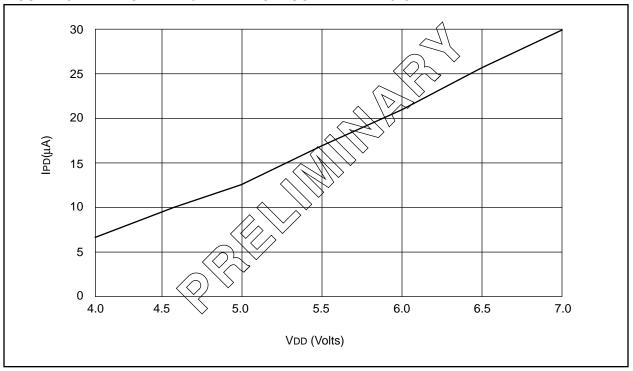

FIGURE 20-11: TYPICAL IPD vs. VDD WATCHDOG ENABLED 25°C

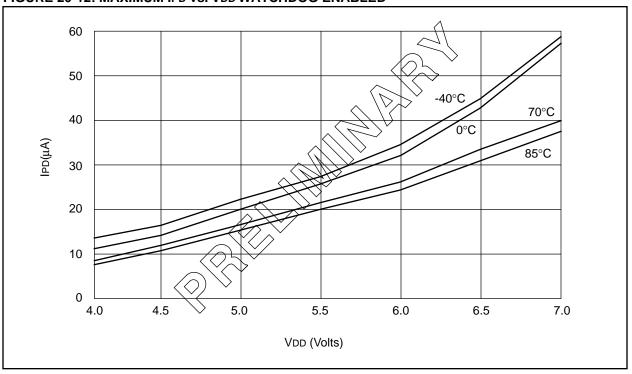

FIGURE 20-12: MAXIMUM IPD vs. VDD WATCHDOG ENABLED

## E.4 PIC16C6X Family of Devices

|                          |     |         |          |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Memory | ory                    |         | "                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Peripherals | erals   |                     |       | Features                               |

|--------------------------|-----|---------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|---------------------|-------|----------------------------------------|

|                          |     | `       | Tolla    | 10 the lade | TO LONG ON PLAN TO THE POOL OF THE POOL OF TO THE POOL OF THE POOL OF TO THE POOL OF TH |        | (LANS) SHIROLINING BEG | IND STE | TOO THE STATE OF T | Sold of the | 3       |                     | SHON  | Situate BOY Phil                       |

|                          | St. | THE THE | to de la | 10          | N tollis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Moo.   | GO SINDE               | SHOP &  | TO PILE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TO TONIES!  |         | is inoto the serios | S HOH | Selectory thousand                     |

| PIC16C62                 | 20  | 2K      |          | 128         | -MR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _      | SPI/I²C                | I       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22          | 3.0     | Yes                 | 1     | 28-pin SDIP, SOIC, SSOP                |

| PIC16C62A <sup>(1)</sup> | 20  | 2K      | 1        | 128         | TMR0,<br>TMR1, TMR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -      | SPI/I2C                | 1       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22          | 2.5-6.0 | Yes                 | Yes   | 28-pin SDIP, SOIC, SSOP                |

| PIC16CR62 <sup>(1)</sup> | 20  | _       | 2K       | 128         | TMR0,<br>TMR1, TMR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1      | SPI/I²C                | I       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22          | 2.5-6.0 | Yes                 | Yes   | 28-pin SDIP, SOIC, SSOP                |