Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 232 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42at-33-pq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

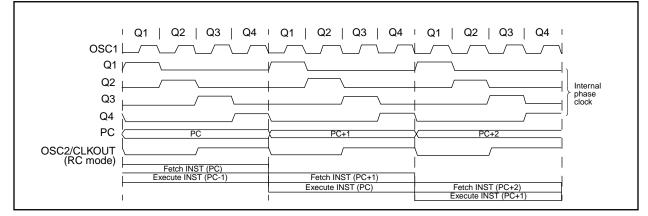

## 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-3.

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g.GOTO) then two cycles are required to complete the instruction (Example 3-2).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

## FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-2: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

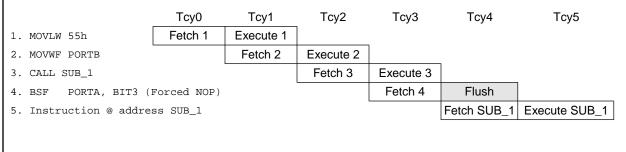

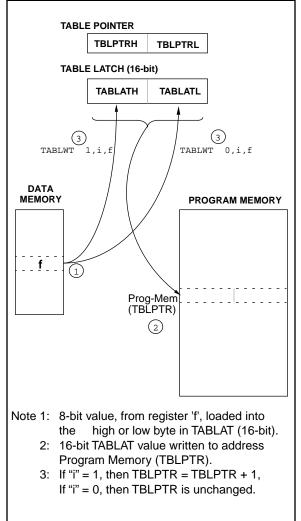

## 7.0 TABLE READS AND TABLE WRITES

The PIC17C4X has four instructions that allow the processor to move data from the data memory space to the program memory space, and vice versa. Since the program memory space is 16-bits wide and the data memory space is 8-bits wide, two operations are required to move 16-bit values to/from the data memory.

The TLWT t,f and TABLWT t,i,f instructions are used to write data from the data memory space to the program memory space. The TLRD t,f and TABLRD t,i,f instructions are used to write data from the program memory space to the data memory space.

The program memory can be internal or external. For the program memory access to be external, the device needs to be operating in extended microcontroller or microprocessor mode.

Figure 7-1 through Figure 7-4 show the operation of these four instructions.

## FIGURE 7-2: TABLWT INSTRUCTION OPERATION

© 1996 Microchip Technology Inc.

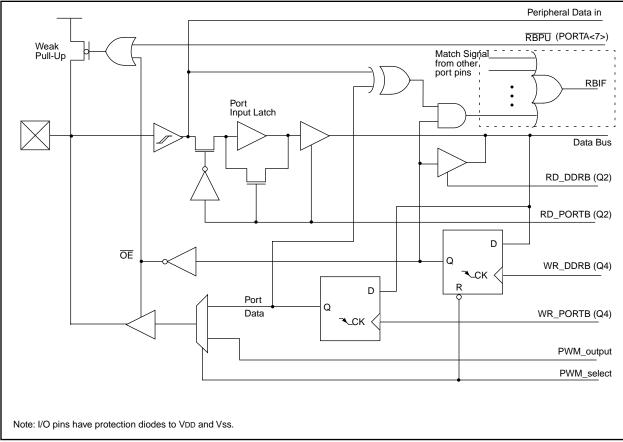

## FIGURE 9-5: BLOCK DIAGRAM OF RB3 AND RB2 PORT PINS

## TABLE 9-5: PORTC FUNCTIONS

| Name    | Bit  | Buffer Type | Function                                     |

|---------|------|-------------|----------------------------------------------|

| RC0/AD0 | bit0 | TTL         | Input/Output or system bus address/data pin. |

| RC1/AD1 | bit1 | TTL         | Input/Output or system bus address/data pin. |

| RC2/AD2 | bit2 | TTL         | Input/Output or system bus address/data pin. |

| RC3/AD3 | bit3 | TTL         | Input/Output or system bus address/data pin. |

| RC4/AD4 | bit4 | TTL         | Input/Output or system bus address/data pin. |

| RC5/AD5 | bit5 | TTL         | Input/Output or system bus address/data pin. |

| RC6/AD6 | bit6 | TTL         | Input/Output or system bus address/data pin. |

| RC7/AD7 | bit7 | TTL         | Input/Output or system bus address/data pin. |

Legend: TTL = TTL input.

## TABLE 9-6: REGISTERS/BITS ASSOCIATED WITH PORTC

| Address                                            | Name  | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|----------------------------------------------------|-------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------------------------|-----------------------------------------|

| 11h, Bank 1                                        | PORTC | RC7/<br>AD7 | RC6/<br>AD6 | RC5/<br>AD5 | RC4/<br>AD4 | RC3/<br>AD3 | RC2/<br>AD2 | RC1/<br>AD1 | RC0/<br>AD0 | xxxx xxxx                     | uuuu uuuu                               |

| 10h, Bank 1 DDRC Data direction register for PORTC |       |             |             |             |             |             |             | 1111 1111   | 1111 1111   |                               |                                         |

Legend: x = unknown, u = unchanged.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

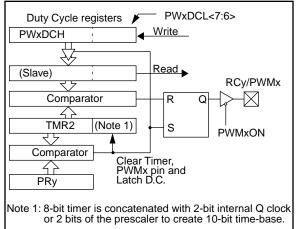

#### 12.1.3 USING PULSE WIDTH MODULATION (PWM) OUTPUTS WITH TMR1 AND TMR2

Two high speed pulse width modulation (PWM) outputs are provided. The PWM1 output uses Timer1 as its time-base, while PWM2 may be software configured to use either Timer1 or Timer2 as the time-base. The PWM outputs are on the RB2/PWM1 and RB3/PWM2 pins.

Each PWM output has a maximum resolution of 10-bits. At 10-bit resolution, the PWM output frequency is 24.4 kHz (@ 25 MHz clock) and at 8-bit resolution the PWM output frequency is 97.7 kHz. The duty cycle of the output can vary from 0% to 100%.

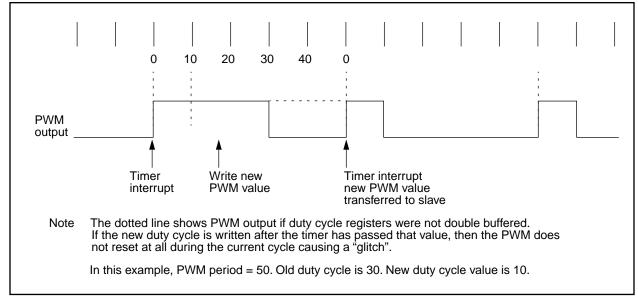

Figure 12-5 shows a simplified block diagram of the PWM module. The duty cycle register is double buffered for glitch free operation. Figure 12-6 shows how a glitch could occur if the duty cycle registers were not double buffered.

The user needs to set the PWM1ON bit (TCON2<4>) to enable the PWM1 output. When the PWM1ON bit is set, the RB2/PWM1 pin is configured as PWM1 output and forced as an output irrespective of the data direction bit (DDRB<2>). When the PWM1ON bit is clear, the pin behaves as a port pin and its direction is controlled by its data direction bit (DDRB<2>). Similarly, the PWM2ON (TCON2<5>) bit controls the configuration of the RB3/PWM2 pin.

## FIGURE 12-5: SIMPLIFIED PWM BLOCK DIAGRAM

## FIGURE 12-6: PWM OUTPUT

## FIGURE 13-2: RCSTA REGISTER (ADDRESS: 13h, BANK 0)

| SPEN   | N.W0         R/W - 0         R/W - 0         U - 0         R - 0         R - 0         R - x           RX9         SREN         CREN         —         FERR         OERR         RX9D         R = Readable bit                                                                                                                                             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit7   | bit 0<br>W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)                                                                                                                                                                                                                                                                                      |

| bit 7: | <b>SPEN</b> : Serial Port Enable bit<br>1 = Configures RA5/RX/DT and RA4/TX/CK pins as serial port pins<br>0 = Serial port disabled                                                                                                                                                                                                                        |

| bit 6: | <b>RX9</b> : 9-bit Receive Enable bit<br>1 = Selects 9-bit reception<br>0 = Selects 8-bit reception                                                                                                                                                                                                                                                        |

| bit 5: | SREN: Single Receive Enable bit         This bit enables the reception of a single byte. After receiving the byte, this bit is automatically cleared.         Synchronous mode:         1 = Enable reception         0 = Disable reception         Note: This bit is ignored in synchronous slave reception.         Asynchronous mode:         Don't care |

| bit 4: | CREN: Continuous Receive Enable bit<br>This bit enables the continuous reception of serial data.<br><u>Asynchronous mode:</u><br>1 = Enable reception<br>0 = Disables reception<br><u>Synchronous mode:</u><br>1 = Enables continuous reception until CREN is cleared (CREN overrides SREN)<br>0 = Disables continuous reception                           |

| bit 3: | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                 |

| bit 2: | FERR: Framing Error bit<br>1 = Framing error (Updated by reading RCREG)<br>0 = No framing error                                                                                                                                                                                                                                                            |

| bit 1: | OERR: Overrun Error bit<br>1 = Overrun (Cleared by clearing CREN)<br>0 = No overrun error                                                                                                                                                                                                                                                                  |

| bit 0: | <b>RX9D</b> : 9th bit of receive data (can be the software calculated parity bit)                                                                                                                                                                                                                                                                          |

## 13.2 USART Asynchronous Mode

In this mode, the USART uses standard nonreturn-to-zero (NRZ) format (one start bit, eight or nine data bits, and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock x64 of the bit shift rate. Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

The asynchronous mode is selected by clearing the SYNC bit (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

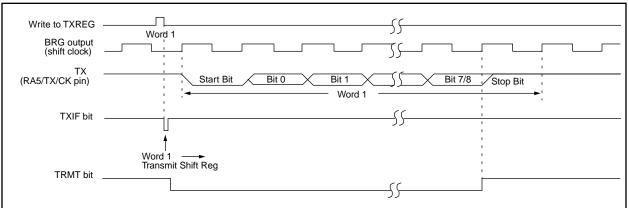

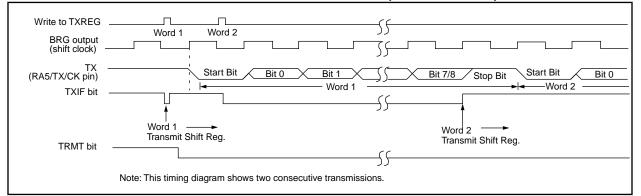

#### 13.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 13-3. The heart of the transmitter is the transmit shift register (TSR). The shift register obtains its data from the read/write transmit buffer (TXREG). TXREG is loaded with data in software. The TSR is not loaded until the stop bit has been transmitted from the previous load. As soon as the stop bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one TCY at the end of the current BRG cycle), the TXREG is empty and an interrupt bit, TXIF (PIR<1>) is set. This interrupt can be enabled or disabled by the TXIE bit (PIE<1>). TXIF will be set regardless of TXIE and cannot be reset in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of the TXREG, the TRMT (TXSTA<1>) bit shows the status of the TSR. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty.

| Note: | The TSR is not mapped in data memory, |

|-------|---------------------------------------|

|       | so it is not available to the user.   |

Transmission enabled setting is by the TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 13-5). The transmission can also be started by first loading TXREG and then setting TXEN. Normally when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to TSR resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 13-6). Clearing TXEN during a transmission will cause the transmission to be aborted. This will reset the transmitter and the RA5/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty).

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. Load data to the TXREG register.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 7. Enable the transmission by setting TXEN (starts transmission).

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the opposite order.

Note: To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

## FIGURE 13-5: ASYNCHRONOUS MASTER TRANSMISSION

## FIGURE 13-6: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 13-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                                        | Name                                       | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|--------------------------------------------|-------|--------|--------|--------|-------|-----------|-----------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1                                    | PIR                                        | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF     | TXIF      | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0                                    | RCSTA                                      | SPEN  | RX9    | SREN   | CREN   | —     | FERR      | OERR      | RX9D  | x00- 0000                     | 0000 -00u                               |

| 16h, Bank 0                                    | Bank 0 TXREG Serial port transmit register |       |        |        |        |       |           |           |       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1                                    | PIE                                        | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE     | TXIE      | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0                                    | TXSTA                                      | CSRC  | TX9    | TXEN   | SYNC   | —     | —         | TRMT      | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |                                            |       |        |        |        |       | xxxx xxxx | uuuu uuuu |       |                               |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

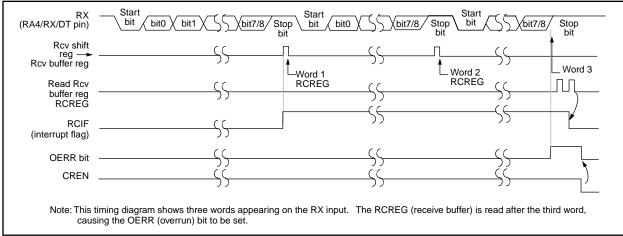

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

## FIGURE 13-8: ASYNCHRONOUS RECEPTION

| <b>TABLE 13-6</b> : | <b>REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION</b> |

|---------------------|---------------------------------------------------------|

|                     |                                                         |

| Address                                        | Name  | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|--------|--------|--------|-------|-------|-------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 1                                    | PIR   | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF      | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9    | SREN   | CREN   | _     | FERR  | OERR  | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0                                    | RCREG | RX7   | RX6    | RX5    | RX4    | RX3   | RX2   | RX1   | RX0       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1                                    | PIE   | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE      | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9    | TXEN   | SYNC   | _     | —     | TRMT  | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |        |        |        |       |       |       | xxxx xxxx | uuuu uuuu                     |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous reception. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

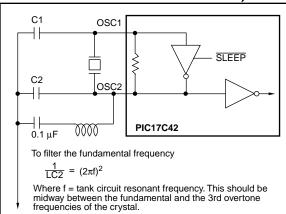

#### FIGURE 14-3: CRYSTAL OPERATION, OVERTONE CRYSTALS (XT OSC CONFIGURATION)

## TABLE 14-2: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Oscillator<br>Type | Resonator<br>Frequency         | Capacitor Range<br>C1 = C2               |

|--------------------|--------------------------------|------------------------------------------|

| LF                 | 455 kHz<br>2.0 MHz             | 15 - 68 pF<br>10 - 33 pF                 |

| ХТ                 | 4.0 MHz<br>8.0 MHz<br>16.0 MHz | 22 - 68 pF<br>33 - 100 pF<br>33 - 100 pF |

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### **Resonators Used:**

| 455 kHz                                           | Panasonic EFO-A455K04B | ± 0.3% |  |  |

|---------------------------------------------------|------------------------|--------|--|--|

| 2.0 MHz                                           | Murata Erie CSA2.00MG  | ± 0.5% |  |  |

| 4.0 MHz                                           | Murata Erie CSA4.00MG  | ± 0.5% |  |  |

| 8.0 MHz                                           | Murata Erie CSA8.00MT  | ± 0.5% |  |  |

| 16.0 MHz                                          | Murata Erie CSA16.00MX | ± 0.5% |  |  |

| Resonators used did not have built-in capacitors. |                        |        |  |  |

## TABLE 14-3:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR

| Osc<br>Type | Freq                  | C1               | C2             |

|-------------|-----------------------|------------------|----------------|

| LF          | 32 kHz <sup>(1)</sup> | 100-150 pF       | 100-150 pF     |

|             | 1 MHz                 | 10-33 pF         | 10-33 pF       |

|             | 2 MHz                 | 10-33 pF         | 10-33 pF       |

| XT          | 2 MHz                 | 47-100 pF        | 47-100 pF      |

|             | 4 MHz                 | 15-68 pF         | 15-68 pF       |

|             | 8 MHz <sup>(2)</sup>  | 15-47 pF         | 15-47 pF       |

|             | 16 MHz                | TBD              | TBD            |

|             | 25 MHz                | 15-47 pF         | 15-47 pF       |

|             | 32 MHz <sup>(3)</sup> | <sub>0</sub> (3) | <sub>(3)</sub> |

Higher capacitance increases the stability of the oscillator but also increases the start-up time and the oscillator current. These values are for design guidance only. Rs may be required in XT mode to avoid overdriving the crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values for external components.

- Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

- 2: Rs of 330Ω is required for a capacitor combination of 15/15 pF.

- 3: Only the capacitance of the board was present.

#### **Crystals Used:**

| 32.768 kHz | Epson C-001R32.768K-A | ± 20 PPM     |

|------------|-----------------------|--------------|

| 1.0 MHz    | ECS-10-13-1           | $\pm$ 50 PPM |

| 2.0 MHz    | ECS-20-20-1           | $\pm$ 50 PPM |

| 4.0 MHz    | ECS-40-20-1           | ± 50 PPM     |

| 8.0 MHz    | ECS ECS-80-S-4        | ± 50 PPM     |

|            | ECS-80-18-1           |              |

| 16.0 MHz   | ECS-160-20-1          | TBD          |

| 25 MHz     | CTS CTS25M            | $\pm$ 50 PPM |

| 32 MHz     | CRYSTEK HF-2          | $\pm$ 50 PPM |

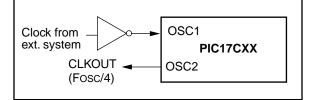

#### 14.2.3 EXTERNAL CLOCK OSCILLATOR

In the EC oscillator mode, the OSC1 input can be driven by CMOS drivers. In this mode, the OSC1/CLKIN pin is hi-impedance and the OSC2/CLK-OUT pin is the CLKOUT output (4 Tosc).

#### FIGURE 14-4: EXTERNAL CLOCK INPUT OPERATION (EC OSC CONFIGURATION)

## 14.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLK-OUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation and SLEEP mode, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 14.1).

Under normal operation, the WDT must be cleared on a regular interval. This time is less the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

#### 14.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms, (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a postscaler with a division ratio of up to 1:256 can be assigned to the WDT. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

#### 14.3.2 CLEARING THE WDT AND POSTSCALER

The WDT and postscaler are cleared when:

- The device is in the reset state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the reset state.

#### 14.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT postscaler) it may take several seconds before a WDT time-out occurs.

The WDT and postscaler is the Power-up Timer during the Power-on Reset sequence.

#### 14.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the  $\overline{\text{TO}}$  bit is cleared (device is not reset). The CLRWDT instruction can be used to set the  $\overline{\text{TO}}$  bit. This allows the WDT to be a simple overflow timer. When in sleep, the WDT does not increment.

## 15.0 INSTRUCTION SET SUMMARY

The PIC17CXX instruction set consists of 58 instructions. Each instruction is a 16-bit word divided into an OPCODE and one or more operands. The opcode specifies the instruction type, while the operand(s) further specify the operation of the instruction. The PIC17CXX instruction set can be grouped into three types:

- byte-oriented

- bit-oriented

- literal and control operations.

These formats are shown in Figure 15-1.

Table 15-1 shows the field descriptions for the opcodes. These descriptions are useful for understanding the opcodes in Table 15-2 and in each specific instruction descriptions.

**byte-oriented instructions**, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' = '0', the result is placed in the WREG register. If 'd' = '1', the result is placed in the file register specified by the instruction.

**bit-oriented instructions**, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

**literal and control operations**, 'k' represents an 8- or 11-bit constant or literal value.

The instruction set is highly orthogonal and is grouped into:

- · byte-oriented operations

- bit-oriented operations

- literal and control operations

All instructions are executed within one single instruction cycle, unless:

- a conditional test is true

- the program counter is changed as a result of an instruction

- a table read or a table write instruction is executed (in this case, the execution takes two instruction cycles with the second cycle executed as a NOP)

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 25 MHz, the normal instruction execution time is 160 ns. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 320 ns.

#### TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                          |  |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| f             | Register file address (00h to FFh)                                                                                                                                                   |  |  |  |  |  |  |  |

| р             | Peripheral register file address (00h to 1Fh)                                                                                                                                        |  |  |  |  |  |  |  |

| i             | Table pointer control i = '0' (do not change)<br>i = '1' (increment after instruction execution)                                                                                     |  |  |  |  |  |  |  |

| t             | Table byte select $t = 0'$ (perform operation on lower byte)<br>t = '1' (perform operation on upper byte literal field, constant data)                                               |  |  |  |  |  |  |  |

| WREG          | Working register (accumulator)                                                                                                                                                       |  |  |  |  |  |  |  |

| b             | Bit address within an 8-bit file register                                                                                                                                            |  |  |  |  |  |  |  |

| k             | Literal field, constant data or label                                                                                                                                                |  |  |  |  |  |  |  |

| x             | Don't care location (= '0' or '1')<br>The assembler will generate code with $x = '0'$ . It is<br>the recommended form of use for compatibility with<br>all Microchip software tools. |  |  |  |  |  |  |  |

| d             | Destination select<br>0 = store result in WREG<br>1 = store result in file register f<br>Default is d = '1'                                                                          |  |  |  |  |  |  |  |

| u             | Unused, encoded as '0'                                                                                                                                                               |  |  |  |  |  |  |  |

| s             | Destination select<br>0 = store result in file register f and in the WREG<br>1 = store result in file register f<br>Default is s = '1'                                               |  |  |  |  |  |  |  |

| label         | Label name                                                                                                                                                                           |  |  |  |  |  |  |  |

| C,DC,<br>Z,OV | ALU status bits Carry, Digit Carry, Zero, Overflow                                                                                                                                   |  |  |  |  |  |  |  |

| GLINTD        | Global Interrupt Disable bit (CPUSTA<4>)                                                                                                                                             |  |  |  |  |  |  |  |

| TBLPTR        | Table Pointer (16-bit)                                                                                                                                                               |  |  |  |  |  |  |  |

| TBLAT         | Table Latch (16-bit) consists of high byte (TBLATH) and low byte (TBLATL)                                                                                                            |  |  |  |  |  |  |  |

| TBLATL        | Table Latch low byte                                                                                                                                                                 |  |  |  |  |  |  |  |

| TBLATH        | Table Latch high byte                                                                                                                                                                |  |  |  |  |  |  |  |

| TOS           | Top of Stack                                                                                                                                                                         |  |  |  |  |  |  |  |

| PC            | Program Counter                                                                                                                                                                      |  |  |  |  |  |  |  |

| BSR           | Bank Select Register                                                                                                                                                                 |  |  |  |  |  |  |  |

| WDT           | Watchdog Timer Counter                                                                                                                                                               |  |  |  |  |  |  |  |

| TO            | Time-out bit                                                                                                                                                                         |  |  |  |  |  |  |  |

| PD            | Power-down bit                                                                                                                                                                       |  |  |  |  |  |  |  |

| dest          | Destination either the WREG register or the speci-<br>fied register file location                                                                                                    |  |  |  |  |  |  |  |

| []            | Options                                                                                                                                                                              |  |  |  |  |  |  |  |

| ()            | Contents                                                                                                                                                                             |  |  |  |  |  |  |  |

| $\rightarrow$ | Assigned to                                                                                                                                                                          |  |  |  |  |  |  |  |

| <>            | Register bit field                                                                                                                                                                   |  |  |  |  |  |  |  |

| E             | In the set of                                                                                                                                                                        |  |  |  |  |  |  |  |

| italics       | User defined term (font is courier)                                                                                                                                                  |  |  |  |  |  |  |  |

## PIC17C4X

| INC          | F                               | In                  | Increment f                                                       |              |                                              |                       |  |  |  |

|--------------|---------------------------------|---------------------|-------------------------------------------------------------------|--------------|----------------------------------------------|-----------------------|--|--|--|

| Synt         | tax:                            | [ /                 | [label] INCF f,d                                                  |              |                                              |                       |  |  |  |

| Operands:    |                                 |                     | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |              |                                              |                       |  |  |  |

| Ope          | ration:                         | (f)                 | + 1 $\rightarrow$                                                 | (dest)       |                                              |                       |  |  |  |

| Stat         | us Affected:                    | 0                   | V, C, D0                                                          | C, Z         |                                              |                       |  |  |  |

| Enco         | oding:                          |                     | 0001                                                              | 010d         | ffff                                         | ffff                  |  |  |  |

| Description: |                                 |                     | ented. If                                                         | 'd' is 0 the | ster 'f' are<br>e result is<br>e result is p | placed in             |  |  |  |

| Wor          | ds:                             | 1                   |                                                                   |              |                                              |                       |  |  |  |

| Cycl         | es:                             | 1                   |                                                                   |              |                                              |                       |  |  |  |

| QC           | ycle Activity:                  |                     |                                                                   |              |                                              |                       |  |  |  |

|              | Q1                              |                     | Q2                                                                | Q            | 3                                            | Q4                    |  |  |  |

|              | Decode                          |                     | Read<br>gister 'f'                                                | Exec         |                                              | Vrite to<br>stination |  |  |  |

| <u>Exa</u>   | <u>mple</u> :                   | IN                  | ICF                                                               | CNT,         | 1                                            |                       |  |  |  |

|              | Before Instru                   | uctior              | า                                                                 |              |                                              |                       |  |  |  |

|              | CNT                             | =                   | 0xFF                                                              |              |                                              |                       |  |  |  |

|              | Z<br>C                          | =                   | 0<br>?                                                            |              |                                              |                       |  |  |  |

|              | After Instruct<br>CNT<br>Z<br>C | tion<br>=<br>=<br>= | 0x00<br>1<br>1                                                    |              |                                              |                       |  |  |  |

| INCFSZ                                                                                                                                                                                                                                                                                                                                 | Incremen                 | Increment f, skip if 0                                            |      |                       |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------|------|-----------------------|--|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                                                                                | [ label ]                | [label] INCFSZ f,d                                                |      |                       |  |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                              | 0 ≤ f ≤ 255<br>d ∈ [0,1] | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |      |                       |  |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                                                             |                          | (f) + 1 $\rightarrow$ (dest)<br>skip if result = 0                |      |                       |  |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                                                                       | None                     |                                                                   |      |                       |  |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                                                              | 0001                     | 111d                                                              | ffff | ffff                  |  |  |  |  |

| Description: The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded,<br>and an NOP is executed instead making<br>it a two-cycle instruction. |                          |                                                                   |      |                       |  |  |  |  |

| Words:                                                                                                                                                                                                                                                                                                                                 | 1                        |                                                                   |      |                       |  |  |  |  |

| Cycles:                                                                                                                                                                                                                                                                                                                                | 1(2)                     |                                                                   |      |                       |  |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                                                                                                                      |                          |                                                                   |      |                       |  |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                                                     | Q2                       | Q3                                                                |      | Q4                    |  |  |  |  |

| Decode                                                                                                                                                                                                                                                                                                                                 | Read<br>register 'f'     | Execu                                                             |      | Vrite to<br>stination |  |  |  |  |

| lf skip:                                                                                                                                                                                                                                                                                                                               |                          |                                                                   |      |                       |  |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                                                     | Q2                       | Q3                                                                |      | Q4                    |  |  |  |  |

| Forced NOP                                                                                                                                                                                                                                                                                                                             | NOP                      | Execu                                                             | te   | NOP                   |  |  |  |  |

| Example:                                                                                                                                                                                                                                                                                                                               | NZERO                    | INCFSZ<br>:<br>:                                                  | CNT, | 1                     |  |  |  |  |

| Before Instruction<br>PC = Address (HERE)                                                                                                                                                                                                                                                                                              |                          |                                                                   |      |                       |  |  |  |  |

| After Instruction<br>CNT = CNT + 1<br>If $CNT = 0$ ;<br>PC = Address(ZERO)<br>If $CNT \neq 0$ ;<br>PC = Address(NZERO)                                                                                                                                                                                                                 |                          |                                                                   |      |                       |  |  |  |  |

# PIC17C4X

| NEGW         | V                            | Negate W                                                                                                                          |                                                             |  |  |  |  |  |  |

|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|--|

| Syntax       | <b>K</b> :                   | [ <i>label</i> ] NEGW f,s                                                                                                         | ;                                                           |  |  |  |  |  |  |

| Opera        | nds:                         | 0 ≤ F ≤ 255<br>s ∈ [0,1]                                                                                                          |                                                             |  |  |  |  |  |  |

| Opera        | tion:                        | $\frac{\overline{WREG}}{\overline{WREG}} + 1 \to (f);$ $\overline{WREG} + 1 \to s$                                                |                                                             |  |  |  |  |  |  |

| Status       | Affected:                    | OV, C, DC, Z                                                                                                                      |                                                             |  |  |  |  |  |  |

| Encod        | ling:                        | 0010 110s f                                                                                                                       | fff ffff                                                    |  |  |  |  |  |  |

| Descri       | ption:                       | WREG is negated using<br>ment. If 's' is 0 the resul<br>WREG and data memo<br>'s' is 1 the result is plac<br>memory location 'f'. | t is placed in ry location 'f'. If                          |  |  |  |  |  |  |

| Words        | :                            | 1                                                                                                                                 | 1                                                           |  |  |  |  |  |  |

| Cycles       | 3:                           | 1                                                                                                                                 |                                                             |  |  |  |  |  |  |

| Q Cyc        | le Activity:                 |                                                                                                                                   |                                                             |  |  |  |  |  |  |

|              | Q1                           | Q2 Q3                                                                                                                             | Q4                                                          |  |  |  |  |  |  |

|              | Decode                       | Read Execute<br>register 'f'                                                                                                      | Write<br>register 'f'<br>and other<br>specified<br>register |  |  |  |  |  |  |

| <u>Examp</u> | ole:                         | NEGW REG, 0                                                                                                                       |                                                             |  |  |  |  |  |  |

| B            | efore Instru<br>WREG<br>REG  | ction<br>= 0011 1010 [0x3A],<br>= 1010 1011 [0xAB]                                                                                |                                                             |  |  |  |  |  |  |

| At           | fter Instruct<br>WREG<br>REG | ion<br>= 1100 0111 [0xC6]<br>= 1100 0111 [0xC6]                                                                                   |                                                             |  |  |  |  |  |  |

| NOF               | 2            | No Operation  |         |     |    |      |  |  |  |

|-------------------|--------------|---------------|---------|-----|----|------|--|--|--|

| Syntax:           |              | [ label ]     | NOP     |     |    |      |  |  |  |

| Operands:         |              | None          | None    |     |    |      |  |  |  |

| Ope               | ration:      | No opera      | tion    |     |    |      |  |  |  |

| Stat              | us Affected: | None          | None    |     |    |      |  |  |  |

| Encoding:         |              | 0000          | 0000    | 000 | 0  | 0000 |  |  |  |

| Des               | cription:    | No operation. |         |     |    |      |  |  |  |

| Wor               | ds:          | 1             | 1       |     |    |      |  |  |  |

| Cycl              | es:          | 1             |         |     |    |      |  |  |  |

| Q Cycle Activity: |              |               |         |     |    |      |  |  |  |

|                   | Q1           | Q2            | Q3      |     | Q4 |      |  |  |  |

|                   | Decode       | NOP           | Execute |     |    | NOP  |  |  |  |

|                   |              |               |         |     |    |      |  |  |  |

Example:

None.

# PIC17C4X

## Applicable Devices 42 R42 42A 43 R43 44

#### 17.2 DC CHARACTERISTICS:

#### PIC17C42-16 (Commercial, Industrial) PIC17C42-25 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated) Operating temperature

#### DC CHARACTERISTICS

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and  $0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

Operating voltage VDD range as described in Section 17.1 Parameter No. Sym Characteristic Min Typ† Max Units Conditions Input Low Voltage VIL I/O ports D030 with TTL buffer Vss 0.8 V D031 with Schmitt Trigger buffer Vss 0.2VDD V \_ D032 MCLR, OSC1 (in EC and RC Vss 0.2Vdd V Note1 \_ mode) D033 OSC1 (in XT, and LF mode) 0.5VDD V \_ Input High Voltage Vн I/O ports V D040 2.0 with TTL buffer \_ Vdd D041 with Schmitt Trigger buffer 0.8VDD Vdd V \_ D042 MCLR 0.8Vdd Vdd Note1 V D043 OSC1 (XT, and LF mode) 0.5VDD V D050 Hysteresis of 0.15VDD\* VHYS V \_ \_ Schmitt Trigger inputs Input Leakage Current (Notes 2, 3) D060 lı∟ I/O ports (except RA2, RA3)  $Vss \leq VPIN \leq VDD$ , ±1 μΑ I/O Pin at hi-impedance PORTB weak pull-ups disabled MCLR D061 <u>+2</u> μA VPIN = Vss or VPIN = VDD D062 **RA2, RA3** ±2 μΑ  $Vss \leq VRA2$ ,  $VRA3 \leq 12V$ D063 OSC1, TEST ±1 μΑ  $Vss \le VPIN \le VDD$

D070 IPURB PORTB weak pull-up current 60 These parameters are characterized but not tested.

MCLR

D064

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only t and are not tested.

200

10

400

μA

μΑ

These parameters are for design guidance only and are not tested, nor characterized. t

Design guidance to attain the AC timing specifications. These loads are not tested. ++

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/Vpp pin may be kept in this range at times other than programming, but this is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

VMCLR = VPP = 12V

(when not programming)

VPIN = Vss.  $\overline{RBPU} = 0$

## Applicable Devices 42 R42 42A 43 R43 44

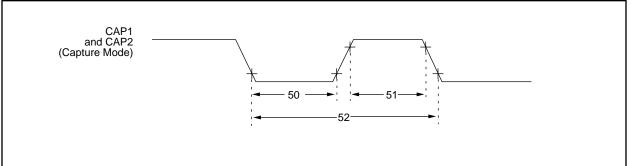

## FIGURE 19-7: CAPTURE TIMINGS

## TABLE 19-7: CAPTURE REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                        | Min                | Тур† | Max | Units | Conditions                      |

|------------------|------|---------------------------------------|--------------------|------|-----|-------|---------------------------------|

| 50               | TccL | Capture1 and Capture2 input low time  | 10 *               | —    | —   | ns    |                                 |

| 51               | TccH | Capture1 and Capture2 input high time | 10 *               | —    |     | ns    |                                 |

| 52               | TccP | Capture1 and Capture2 input period    | <u>2Tcy</u> §<br>N | _    | _   | ns    | N = prescale value<br>(4 or 16) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

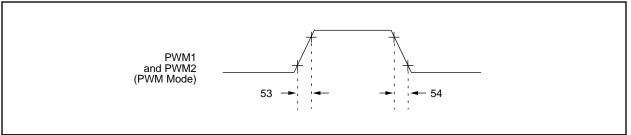

#### FIGURE 19-8: PWM TIMINGS

#### TABLE 19-8: PWM REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                           | Min | Тур† | Max   | Units | Conditions |

|------------------|------|------------------------------------------|-----|------|-------|-------|------------|

| 53               | TccR | PWM1 and PWM2 output rise time           |     | 10 * | 35 *§ | ns    |            |

| 54               | TccF | PWM1 and PWM2 output fall time           |     | 10 * | 35 *§ | ns    |            |

| * The            |      | motors are observatorized but not tested |     |      |       |       |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

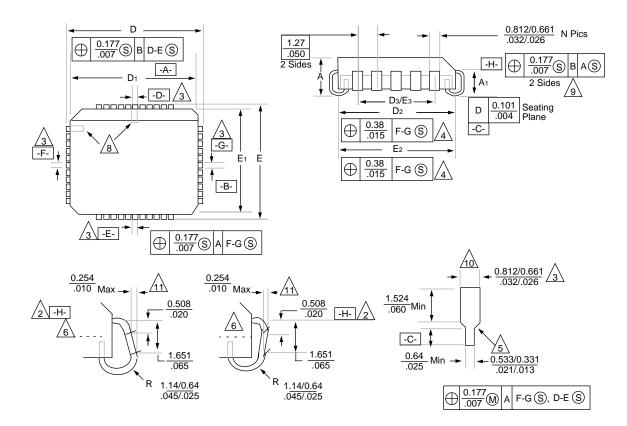

## 21.3 44-Lead Plastic Leaded Chip Carrier (Square)

|        | Package Group: Plastic Leaded Chip Carrier (PLCC) |             |           |        |       |           |  |  |  |

|--------|---------------------------------------------------|-------------|-----------|--------|-------|-----------|--|--|--|

|        |                                                   | Millimeters |           | Inches |       |           |  |  |  |

| Symbol | Min                                               | Max         | Notes     | Min    | Max   | Notes     |  |  |  |

| А      | 4.191                                             | 4.572       |           | 0.165  | 0.180 |           |  |  |  |

| A1     | 2.413                                             | 2.921       |           | 0.095  | 0.115 |           |  |  |  |

| D      | 17.399                                            | 17.653      |           | 0.685  | 0.695 |           |  |  |  |

| D1     | 16.510                                            | 16.663      |           | 0.650  | 0.656 |           |  |  |  |

| D2     | 15.494                                            | 16.002      |           | 0.610  | 0.630 |           |  |  |  |

| D3     | 12.700                                            | 12.700      | Reference | 0.500  | 0.500 | Reference |  |  |  |

| Е      | 17.399                                            | 17.653      |           | 0.685  | 0.695 |           |  |  |  |

| E1     | 16.510                                            | 16.663      |           | 0.650  | 0.656 |           |  |  |  |

| E2     | 15.494                                            | 16.002      |           | 0.610  | 0.630 |           |  |  |  |

| E3     | 12.700                                            | 12.700      | Reference | 0.500  | 0.500 | Reference |  |  |  |

| N      | 44                                                | 44          |           | 44     | 44    |           |  |  |  |

| CP     | _                                                 | 0.102       |           | _      | 0.004 |           |  |  |  |

| LT     | 0.203                                             | 0.381       |           | 0.008  | 0.015 |           |  |  |  |

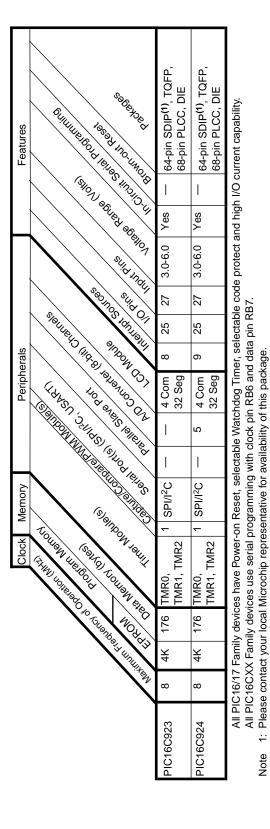

## E.7 <u>PIC16C9XX Family Of Devices</u>

## APPENDIX F: ERRATA FOR PIC17C42 SILICON

The PIC17C42 devices that you have received have the following anomalies. At present there is no intention for future revisions to the present PIC17C42 silicon. If these cause issues for the application, it is recommended that you select the PIC17C42A device.

**Note:** New designs should use the PIC17C42A.

When the Oscillator Start-Up Timer (OST) is enabled (in LF or XT oscillator modes), any interrupt that wakes the processor may cause a WDT reset. This occurs when the WDT is greater than or equal to 50% time-out period when the SLEEP instruction is executed. This will not occur in either the EC or RC oscillator modes.

#### Work-arounds

- Always ensure that the CLRWDT instruction is executed before the WDT increments past 50% of the WDT period. This will keep the "false" WDT reset from occurring.

- b) When using the WDT as a normal timer (WDT disabled), ensure that the WDT is less than or equal to 50% time-out period when the SLEEP instruction is executed. This can be done by monitoring the TO bit for changing state from set to clear. Example 1 shows putting the PIC17C42 to sleep.

#### EXAMPLE F-1: PIC17C42 TO SLEEP

| BTFSS  | CPUSTA,                 | TO                                   | ;                                       | TO = 0?                           |

|--------|-------------------------|--------------------------------------|-----------------------------------------|-----------------------------------|

| CLRWDT |                         |                                      | ;                                       | YES, WDT = $0$                    |

| BTFSC  | CPUSTA,                 | то                                   | ;                                       | WDT rollover?                     |

| GOTO   | LOOP                    |                                      | ;                                       | NO, Wait                          |

| SLEEP  |                         |                                      | ;                                       | YES, goto Sleep                   |

|        | CLRWDT<br>BTFSC<br>GOTO | CLRWDT<br>BTFSC CPUSTA,<br>GOTO LOOP | CLRWDT<br>BTFSC CPUSTA, TO<br>GOTO LOOP | BTFSC CPUSTA, TO ;<br>GOTO LOOP ; |

2. When the clock source of Timer1 or Timer2 is selected to external clock, the overflow interrupt flag will be set twice, once when the timer equals the period, and again when the timer value is reset to 0h. If the latency to clear TMRxIF is greater than the time to the next clock pulse, no problems will be noticed. If the latency is less than the time to the next timer clock pulse, the interrupt will be serviced twice.

#### Work-arounds

- a) Ensure that the timer has rolled over to 0h before clearing the flag bit.

- b) Clear the timer in software. Clearing the timer in software causes the period to be one count less than expected.

#### **Design considerations**

The device must not be operated outside of the specified voltage range. An external reset circuit must be used to ensure the device is in reset when a brown-out occurs or the VDD rise time is too long. Failure to ensure that the device is in reset when device voltage is out of specification may cause the device to lock-up and ignore the  $\overline{\text{MCLR}}$  pin. NOTES: