Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 33MHz                                                                       |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 4KB (2K x 16)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                |                                                                             |

| RAM Size                   | 232 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                   |

| Data Converters            |                                                                             |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-QFP                                                                      |

| Supplier Device Package    | 44-MQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42at-33e-pq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

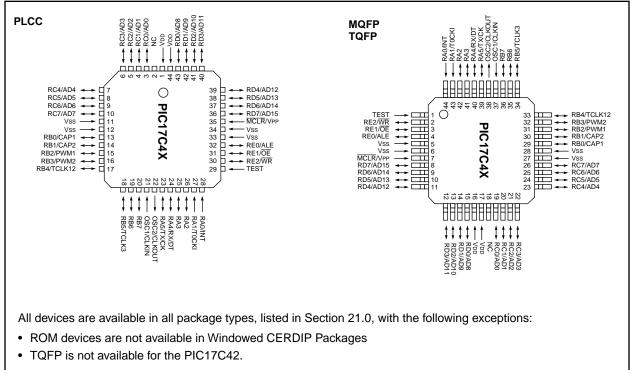

#### Pin Diagrams Cont.'d

NOTES:

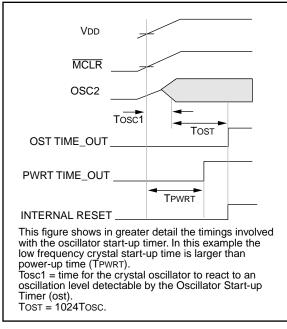

#### FIGURE 4-5: OSCILLATOR START-UPTIME

#### FIGURE 4-6: USING ON-CHIP POR

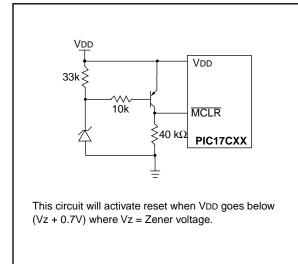

#### FIGURE 4-7: BROWN-OUT PROTECTION CIRCUIT 1

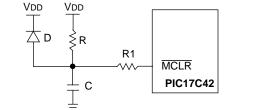

### FIGURE 4-8: PIC17C42 EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: An external Power-on Reset circuit is required only if VDD power-up time is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R < 40 k $\Omega$  is recommended to ensure that the voltage drop across R does not exceed 0.2V (max. leakage current spec. on the  $\overline{MCLR}/VPP$  pin is 5  $\mu$ A). A larger voltage drop will degrade VIH level on the  $\overline{MCLR}/VPP$  pin.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or (Electrical Overstress) EOS.

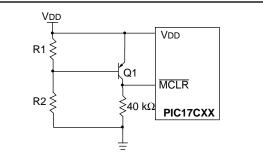

FIGURE 4-9: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

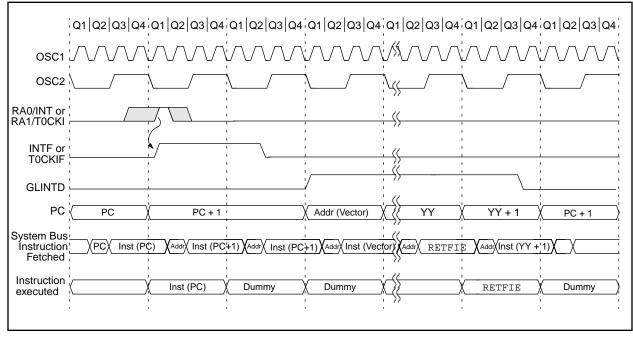

#### 5.5 RA0/INT Interrupt

The external interrupt on the RA0/INT pin is edge triggered. Either the rising edge, if INTEDG bit (T0STA<7>) is set, or the falling edge, if INTEDG bit is clear. When a valid edge appears on the RA0/INT pin, the INTF bit (INTSTA<4>) is set. This interrupt can be disabled by clearing the INTE control bit (INTSTA<0>). The INT interrupt can wake the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

#### 5.6 TMR0 Interrupt

An overflow (FFFFh  $\rightarrow$  0000h) in TMR0 will set the T0IF (INTSTA<5>) bit. The interrupt can be enabled/ disabled by setting/clearing the T0IE control bit (INTSTA<1>). For operation of the Timer0 module, see Section 11.0.

#### 5.7 TOCKI Interrupt

The external interrupt on the RA1/T0CKI pin is edge triggered. Either the rising edge, if the T0SE bit (T0STA<6>) is set, or the falling edge, if the T0SE bit is clear. When a valid edge appears on the RA1/T0CKI pin, the T0CKIF bit (INTSTA<6>) is set. This interrupt can be disabled by clearing the T0CKIE control bit (INTSTA<2>). The T0CKI interrupt can wake up the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

#### 5.8 Peripheral Interrupt

The peripheral interrupt flag indicates that at least one of the peripheral interrupts occurred (PEIF is set). The PEIF bit is a read only bit, and is a bit wise OR of all the flag bits in the PIR register AND'ed with the corresponding enable bits in the PIE register. Some of the peripheral interrupts can wake the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

#### FIGURE 5-5: INT PIN / TOCKI PIN INTERRUPT TIMING

### 6.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC17C4X; program memory and data memory. Each block has its own bus, so that access to each block can occur during the same oscillator cycle.

The data memory can further be broken down into General Purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

#### 6.1 Program Memory Organization

PIC17C4X devices have a 16-bit program counter capable of addressing a 64K x 16 program memory space. The reset vector is at 0000h and the interrupt vectors are at 0008h, 0010h, 0018h, and 0020h (Figure 6-1).

#### 6.1.1 PROGRAM MEMORY OPERATION

The PIC17C4X can operate in one of four possible program memory configurations. The configuration is selected by two configuration bits. The possible modes are:

- Microprocessor

- Microcontroller

- Extended Microcontroller

- Protected Microcontroller

The microcontroller and protected microcontroller modes only allow internal execution. Any access beyond the program memory reads unknown data. The protected microcontroller mode also enables the code protection feature.

The extended microcontroller mode accesses both the internal program memory as well as external program memory. Execution automatically switches between internal and external memory. The 16-bits of address allow a program memory range of 64K-words.

The microprocessor mode only accesses the external program memory. The on-chip program memory is ignored. The 16-bits of address allow a program memory range of 64K-words. Microprocessor mode is the default mode of an unprogrammed device.

The different modes allow different access to the configuration bits, test memory, and boot ROM. Table 6-1 lists which modes can access which areas in memory. Test Memory and Boot Memory are not required for normal operation of the device. Care should be taken to ensure that no unintended branches occur to these areas.

#### FIGURE 6-1: PROGRAM MEMORY MAP AND STACK

|                               | AND STACK                         |                     |

|-------------------------------|-----------------------------------|---------------------|

|                               | PC<15:0>                          | ]                   |

| CALL,                         | RETURN 1 16                       | 1                   |

| RETFI                         |                                   |                     |

|                               | Stack Level 1                     | 1                   |

|                               | :                                 | 1                   |

|                               | •<br>Stack Level 16               | -                   |

|                               | Stack Level 10                    | ]                   |

| T T                           | Reset Vector                      | ] 0000h             |

|                               |                                   |                     |

|                               | INT Pin Interrupt Vector          | 0008h               |

|                               | Timer0 Interrupt Vector           | 0010h               |

|                               | T0CKI Pin Interrupt Vector        | 0018h               |

|                               | Peripheral Interrupt Vector       | 0020h               |

|                               |                                   | 0021h               |

|                               |                                   |                     |

|                               |                                   | 7FFh<br>(PIC17C42,  |

| 2                             |                                   | PIC17CR42,          |

| User Memory<br>Space (1)      |                                   | PIC17C42A)          |

| ace                           |                                   | FFFh                |

| Spe                           |                                   | (PIC17C43           |

| n ∣                           |                                   | PIC17CR43)          |

|                               |                                   |                     |

|                               |                                   |                     |

|                               |                                   | 1FFFh<br>(PIC17C44) |

|                               |                                   | (FIC17C44)          |

|                               |                                   |                     |

|                               |                                   | l                   |

| <u>+</u>                      | FOSC0                             | FDFFh               |

| > [                           | FOSC0                             | FE00h<br>FE01h      |

| Jor                           | WDTPS0                            | FE02h               |

| len                           | WDTPS1                            | FE03h               |

| ≥ e                           | PM0                               | FE04h               |

| pac                           | Reserved                          | FE05h               |

| S IB                          | PM1                               | FE06h               |

| figu                          | Reserved                          | FE07h               |

| Configuration Memory<br>Space | Reserved                          | FE08h               |

|                               |                                   | FE0Eh               |

| 📕                             | PM2 <sup>(2)</sup>                | FE0Fh               |

|                               | Test EPROM                        | FE10h<br>FF5Fh      |

|                               |                                   | FF60h               |

|                               | Boot ROM                          |                     |

|                               |                                   | FFFFh               |

| Note 1: U                     | ser memory space may be inter     | nal, external, or   |

|                               | oth. The memory configuration of  |                     |

|                               | rocessor mode.                    | ,                   |

|                               | his location is reserved on the F | PIC17C42.           |

| 1                             |                                   |                     |

| Addr                                                        | Unbanked                                                                                  |                                                        |                                                           |                                                               |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|

| 00h                                                         | INDF0                                                                                     |                                                        |                                                           |                                                               |

| 01h                                                         | FSR0                                                                                      |                                                        |                                                           |                                                               |

| 02h                                                         | PCL                                                                                       |                                                        |                                                           |                                                               |

| 03h                                                         | PCLATH                                                                                    |                                                        |                                                           |                                                               |

| 04h                                                         | ALUSTA                                                                                    |                                                        |                                                           |                                                               |

| 05h                                                         | TOSTA                                                                                     |                                                        |                                                           |                                                               |

| 06h                                                         | CPUSTA                                                                                    |                                                        |                                                           |                                                               |

| 07h                                                         | INTSTA                                                                                    |                                                        |                                                           |                                                               |

| 08h                                                         | INDF1                                                                                     |                                                        |                                                           |                                                               |

| 09h                                                         | FSR1                                                                                      |                                                        |                                                           |                                                               |

| 0Ah                                                         | WREG                                                                                      |                                                        |                                                           |                                                               |

| 0Bh                                                         | TMR0L                                                                                     |                                                        |                                                           |                                                               |

| 0Ch                                                         | TMR0H                                                                                     |                                                        |                                                           |                                                               |

| 0Dh                                                         | TBLPTRL                                                                                   |                                                        |                                                           |                                                               |

| 0Eh                                                         | TBLPTRH                                                                                   |                                                        |                                                           |                                                               |

| 0Fh                                                         | BSR                                                                                       |                                                        |                                                           |                                                               |

| 1                                                           |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | Bank 0                                                                                    | Bank 1 <sup>(1)</sup>                                  | Bank 2 <sup>(1)</sup>                                     | Bank 3 <sup>(1)</sup>                                         |

| 10h                                                         | Bank 0<br>PORTA                                                                           | Bank 1 <sup>(1)</sup><br>DDRC                          | Bank 2 <sup>(1)</sup><br>TMR1                             | Bank 3 <sup>(1)</sup><br>PW1DCL                               |

| 10h<br>11h                                                  |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | PORTA                                                                                     | DDRC                                                   | TMR1                                                      | PW1DCL                                                        |

| 11h                                                         | PORTA<br>DDRB                                                                             | DDRC<br>PORTC                                          | TMR1<br>TMR2                                              | PW1DCL<br>PW2DCL                                              |

| 11h<br>12h                                                  | PORTA<br>DDRB<br>PORTB                                                                    | DDRC<br>PORTC<br>DDRD                                  | TMR1<br>TMR2<br>TMR3L                                     | PW1DCL<br>PW2DCL<br>PW1DCH                                    |

| 11h<br>12h<br>13h                                           | PORTA<br>DDRB<br>PORTB<br>RCSTA                                                           | DDRC<br>PORTC<br>DDRD<br>PORTD                         | TMR1<br>TMR2<br>TMR3L<br>TMR3H                            | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH                          |

| 11h<br>12h<br>13h<br>14h                                    | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG                                                  | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE                 | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1                     | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L                  |

| 11h<br>12h<br>13h<br>14h<br>15h                             | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA                                         | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE        | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2              | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H          |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h                      | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h               | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h        | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

### FIGURE 6-5: PIC17C42 REGISTER FILE MAP

Note 1: SFR file locations 10h - 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

#### FIGURE 6-6: PIC17CR42/42A/43/R43/44 REGISTER FILE MAP

| Addr | Unbanked           |                       |                       |                       |

|------|--------------------|-----------------------|-----------------------|-----------------------|

| 00h  | INDF0              |                       |                       |                       |

| 01h  | FSR0               |                       |                       |                       |

| 02h  | PCL                |                       |                       |                       |

| 03h  | PCLATH             |                       |                       |                       |

| 04h  | ALUSTA             |                       |                       |                       |

| 05h  | TOSTA              |                       |                       |                       |

| 06h  | CPUSTA             |                       |                       |                       |

| 07h  | INTSTA             |                       |                       |                       |

| 08h  | INDF1              |                       |                       |                       |

| 09h  | FSR1               |                       |                       |                       |

| 0Ah  | WREG               |                       |                       |                       |

| 0Bh  | TMR0L              |                       |                       |                       |

| 0Ch  | TMR0H              |                       |                       |                       |

| 0Dh  | TBLPTRL            |                       |                       |                       |

| 0Eh  | TBLPTRH            |                       |                       |                       |

| 0Fh  | BSR                |                       |                       |                       |

|      | Bank 0             | Bank 1 <sup>(1)</sup> | Bank 2 <sup>(1)</sup> | Bank 3 <sup>(1)</sup> |

| 10h  | PORTA              | DDRC                  | TMR1                  | PW1DCL                |

| 11h  | DDRB               | PORTC                 | TMR2                  | PW2DCL                |

| 12h  | PORTB              | DDRD                  | TMR3L                 | PW1DCH                |

| 13h  | RCSTA              | PORTD                 | TMR3H                 | PW2DCH                |

| 14h  | RCREG              | DDRE                  | PR1                   | CA2L                  |

| 15h  | TXSTA              | PORTE                 | PR2                   | CA2H                  |

| 16h  | TXREG              | PIR                   | PR3L/CA1L             | TCON1                 |

| 17h  | SPBRG              | PIE                   | PR3H/CA1H             | TCON2                 |

| 18h  | PRODL              |                       |                       |                       |

| 19h  | PRODH              |                       |                       |                       |

| 1Ah  |                    |                       |                       |                       |

|      |                    |                       |                       |                       |

| 1Fh  |                    |                       | 1                     |                       |

| 20h  | General            | General               |                       |                       |

|      | Purpose            | Purpose               |                       |                       |

|      | RAM <sup>(2)</sup> | RAM (2)               |                       |                       |

|      |                    |                       |                       |                       |

| FFh  |                    |                       |                       |                       |

- Note 1: SFR file locations 10h 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

- 2: General Purpose Registers (GPR) locations 20h - FFh and 120h - 1FFh are banked. All other GPRs ignore the Bank Select Register (BSR) bits.

Example 8-3 shows the sequence to do a 16 x 16 unsigned multiply. Equation 8-1 shows the algorithm that is used. The 32-bit result is stored in 4 registers RES3:RES0.

#### **EQUATION 8-1:** 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

=

- ARG1H:ARG1L \* ARG2H:ARG2L RES3:RES0 =

- (ARG1H \* ARG2H \* 2<sup>16</sup>) +

(ARG1H \* ARG2L \* 2<sup>8</sup>) +

(ARG1L \* ARG2H \* 2<sup>8</sup>) (ARG1L \* ARG2L)

+

#### EXAMPLE 8-3: 16 x 16 MULTIPLY ROUTINE

|   |                                  |                            | ; ARG1L * ARG2L -<br>; PRODH:PRODL  | > |

|---|----------------------------------|----------------------------|-------------------------------------|---|

| ; |                                  | PRODH, RES1<br>PRODL, RES0 | ;                                   |   |

| , |                                  |                            | ; ARG1H * ARG2H -<br>; PRODH:PRODL  | > |

| ; |                                  | PRODH, RES3<br>PRODL, RES2 |                                     |   |

| - | MOVFP<br>MULWF                   |                            | ; ARG1L * ARG2H -<br>; PRODH:PRODL  | > |

|   | ADDWF<br>MOVFP<br>ADDWFC         |                            | ; Add cross<br>; products<br>;      |   |

| ; | ADDWFC                           | RES3, F<br>ARG1H, WREG     | ;                                   |   |

|   | MULWF                            | ARG2L                      | ; ARG1H * ARG2L -<br>; PRODH:PRODL  | > |

|   | ADDWF<br>MOVFP<br>ADDWFC<br>CLRF |                            | ; Add cross<br>; products<br>;<br>; |   |

NOTES:

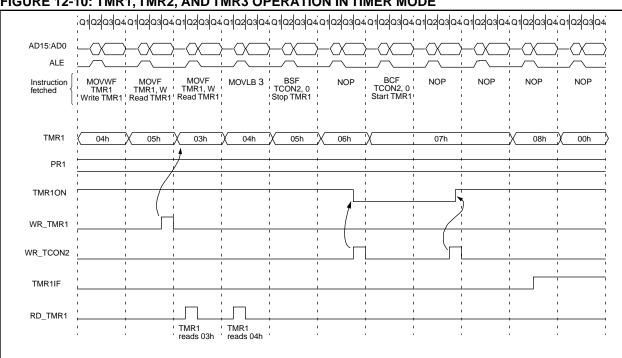

#### FIGURE 12-10: TMR1, TMR2, AND TMR3 OPERATION IN TIMER MODE

| Address       | Name      | Bit 7      | Bit 6             | Bit 5          | Bit 4     | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|-----------|------------|-------------------|----------------|-----------|---------|--------|--------|--------|-------------------------------|-----------------------------------------|

| 16h, Bank 3   | TCON1     | CA2ED1     | CA2ED0            | CA1ED1         | CA1ED0    | T16     | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                               |

| 17h, Bank 3   | TCON2     | CA2OVF     | CA10VF            | PWM2ON         | PWM1ON    | CA1/PR3 | TMR3ON | TMR2ON | TMR10N | 0000 0000                     | 0000 0000                               |

| 10h, Bank 2   | TMR1      | Timer1 reg | gister            |                |           |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 11h, Bank 2   | TMR2      | Timer2 reg | gister            |                |           |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 12h, Bank 2   | TMR3L     | TMR3 reg   | ister; low by     | te             |           |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 13h, Bank 2   | TMR3H     | TMR3 reg   | ister; high b     | yte            |           |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 16h, Bank 1   | PIR       | RBIF       | TMR3IF            | TMR2IF         | TMR1IF    | CA2IF   | CA1IF  | TXIF   | RCIF   | 0000 0010                     | 0000 0010                               |

| 17h, Bank 1   | PIE       | RBIE       | TMR3IE            | TMR2IE         | TMR1IE    | CA2IE   | CA1IE  | TXIE   | RCIE   | 0000 0000                     | 0000 0000                               |

| 07h, Unbanked | INTSTA    | PEIF       | T0CKIF            | T0IF           | INTF      | PEIE    | T0CKIE | TOIE   | INTE   | 0000 0000                     | 0000 0000                               |

| 06h, Unbanked | CPUSTA    | _          | _                 | STKAV          | GLINTD    | TO      | PD     | _      | _      | 11 11                         | 11 qq                                   |

| 14h, Bank 2   | PR1       | Timer1 pe  | riod registe      | r              |           |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 15h, Bank 2   | PR2       | Timer2 pe  | riod registe      | r              |           |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 16h, Bank 2   | PR3L/CA1L | Timer3 pe  | riod/capture      | e1 register; l | ow byte   |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 2   | PR3H/CA1H | Timer3 pe  | riod/capture      | e1 register; l | high byte |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 10h, Bank 3   | PW1DCL    | DC1        | DC0               | —              | —         | —       | —      | —      | —      | xx                            | uu                                      |

| 11h, Bank 3   | PW2DCL    | DC1        | DC0               | TM2PW2         |           | —       | _      | —      | —      | xx0                           | uu0                                     |

| 12h, Bank 3   | PW1DCH    | DC9        | DC8               | DC7            | DC6       | DC5     | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                               |

| 13h, Bank 3   | PW2DCH    | DC9        | DC8               | DC7            | DC6       | DC5     | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                               |

| 14h, Bank 3   | CA2L      | Capture2   | Capture2 low byte |                |           |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 15h, Bank 3   | CA2H      | Capture2   | high byte         |                |           |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition, shaded cells are not used by TMR1, TMR2 or TMR3.

Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset.

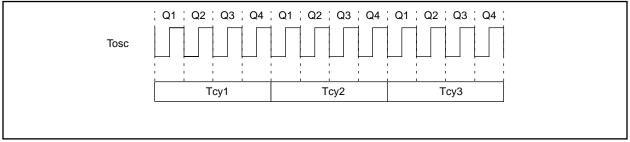

#### 15.2 <u>Q Cycle Activity</u>

Each instruction cycle (Tcy) is comprised of four Q cycles (Q1-Q4). The Q cycles provide the timing/designation for the Decode, Read, Execute, Write etc., of each instruction cycle. The following diagram shows the relationship of the Q cycles to the instruction cycle.

The 4 Q cycles that make up an instruction cycle (Tcy) can be generalized as:

- Q1: Instruction Decode Cycle or forced NOP

- Q2: Instruction Read Cycle or NOP

- Q3: Instruction Execute

- Q4: Instruction Write Cycle or NOP

Each instruction will show the detailed Q cycle operation for the instruction.

#### FIGURE 15-2: Q CYCLE ACTIVITY

| Mnemonic,<br>Operands |        | Description                                   | Cycles |      | 16-bit | Opcod | e    | Status<br>Affected | Notes |

|-----------------------|--------|-----------------------------------------------|--------|------|--------|-------|------|--------------------|-------|

|                       |        |                                               |        | MSb  |        |       | LSb  |                    |       |

| TABLWT                | t,i,f  | Table Write                                   | 2      | 1010 | 11ti   | ffff  | ffff | None               | 5     |

| TLRD                  | t,f    | Table Latch Read                              | 1      | 1010 | 00tx   | ffff  | ffff | None               |       |

| TLWT                  | t,f    | Table Latch Write                             | 1      | 1010 | 01tx   | ffff  | ffff | None               |       |

| TSTFSZ                | f      | Test f, skip if 0                             | 1 (2)  | 0011 | 0011   | ffff  | ffff | None               | 6,8   |

| XORWF                 | f,d    | Exclusive OR WREG with f                      | 1      | 0000 | 110d   | ffff  | ffff | Z                  |       |

| BIT-ORIENT            | ED FIL | E REGISTER OPERATIONS                         | 1      |      |        |       |      |                    |       |

| BCF                   | f,b    | Bit Clear f                                   | 1      | 1000 | 1bbb   | ffff  | ffff | None               |       |

| BSF                   | f,b    | Bit Set f                                     | 1      | 1000 | 0bbb   | ffff  | ffff | None               |       |

| BTFSC                 | f,b    | Bit test, skip if clear                       | 1 (2)  | 1001 | 1bbb   | ffff  | ffff | None               | 6,8   |

| BTFSS                 | f,b    | Bit test, skip if set                         | 1 (2)  | 1001 | 0bbb   | ffff  | ffff | None               | 6,8   |

| BTG                   | f,b    | Bit Toggle f                                  | 1      | 0011 | 1bbb   | ffff  | ffff | None               |       |

| LITERAL AN            | ID CO  | NTROL OPERATIONS                              |        |      |        |       |      |                    |       |

| ADDLW                 | k      | ADD literal to WREG                           | 1      | 1011 | 0001   | kkkk  | kkkk | OV,C,DC,Z          |       |

| ANDLW                 | k      | AND literal with WREG                         | 1      | 1011 | 0101   | kkkk  | kkkk | Z                  |       |

| CALL                  | k      | Subroutine Call                               | 2      | 111k | kkkk   | kkkk  | kkkk | None               | 7     |

| CLRWDT                | _      | Clear Watchdog Timer                          | 1      | 0000 | 0000   | 0000  | 0100 | TO,PD              |       |

| GOTO                  | k      | Unconditional Branch                          | 2      | 110k | kkkk   | kkkk  | kkkk | None               | 7     |

| IORLW                 | k      | Inclusive OR literal with WREG                | 1      | 1011 | 0011   | kkkk  | kkkk | Z                  |       |

| LCALL                 | k      | Long Call                                     | 2      | 1011 | 0111   | kkkk  | kkkk | None               | 4,7   |

| MOVLB                 | k      | Move literal to low nibble in BSR             | 1      | 1011 | 1000   | uuuu  | kkkk | None               |       |

| MOVLR                 | k      | Move literal to high nibble in BSR            | 1      | 1011 | 101x   | kkkk  | uuuu | None               | 9     |

| MOVLW                 | k      | Move literal to WREG                          | 1      | 1011 | 0000   | kkkk  | kkkk | None               |       |

| MULLW                 | k      | Multiply literal with WREG                    | 1      | 1011 | 1100   | kkkk  | kkkk | None               | 9     |

| RETFIE                | _      | Return from interrupt (and enable interrupts) | 2      | 0000 | 0000   | 0000  | 0101 | GLINTD             | 7     |

| RETLW                 | k      | Return literal to WREG                        | 2      | 1011 | 0110   | kkkk  | kkkk | None               | 7     |

| RETURN                | _      | Return from subroutine                        | 2      | 0000 | 0000   | 0000  | 0010 | None               | 7     |

| SLEEP                 | _      | Enter SLEEP Mode                              | 1      | 0000 | 0000   | 0000  | 0011 | TO, PD             |       |

| SUBLW                 | k      | Subtract WREG from literal                    | 1      | 1011 | 0010   | kkkk  | kkkk | OV,C,DC,Z          |       |

| XORLW                 | k      | Exclusive OR literal with WREG                | 1      | 1011 | 0100   | kkkk  | kkkk | Z                  |       |

#### TABLE 15-2: PIC17CXX INSTRUCTION SET (Cont.'d)

Legend: Refer to Table 15-1 for opcode field descriptions.

Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

- 3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

| BSF                                                                                                     | Bit Set f                                                          |                                   |        |    |                     |  |  |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------|--------|----|---------------------|--|--|

| Syntax:                                                                                                 | [ <i>label</i> ] E                                                 | [ <i>label</i> ] BSF f,b          |        |    |                     |  |  |

| Operands:                                                                                               | $\begin{array}{l} 0 \leq f \leq 25 \\ 0 \leq b \leq 7 \end{array}$ | $0 \le f \le 255$ $0 \le b \le 7$ |        |    |                     |  |  |

| Operation:                                                                                              | $1 \rightarrow (f < b >$                                           | -)                                |        |    |                     |  |  |

| Status Affected:                                                                                        | None                                                               |                                   |        |    |                     |  |  |

| Encoding:                                                                                               | 1000                                                               | 0bbb                              | fff    | f  | ffff                |  |  |

| Description:                                                                                            | Bit 'b' in re                                                      | gister 'f' is                     | s set. |    |                     |  |  |

| Words:                                                                                                  | 1                                                                  |                                   |        |    |                     |  |  |

| Cycles:                                                                                                 | 1                                                                  |                                   |        |    |                     |  |  |

| Q Cycle Activity:                                                                                       |                                                                    |                                   |        |    |                     |  |  |

| Q1                                                                                                      | Q2                                                                 | Q3                                |        | Q4 |                     |  |  |

| Decode                                                                                                  | Read<br>register 'f'                                               | Execu                             | ute    |    | Write<br>gister 'f' |  |  |

| Example:                                                                                                | BSF                                                                | FLAG_RE                           | G, 7   |    |                     |  |  |

| Example: BSF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG= 0x0A<br>After Instruction<br>FLAG_REG= 0x8A |                                                                    |                                   |        |    |                     |  |  |

| BTF                                       | SC                                                    | Bit Test, s                                                                                                                                                                                                                                                            | skip if Cle                                                         | ear    |      |  |  |

|-------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------|------|--|--|

| Synt                                      | tax:                                                  | [ <i>label</i> ] B                                                                                                                                                                                                                                                     | TFSC f,                                                             | b      |      |  |  |

| Ope                                       | rands:                                                | $0 \le f \le 253$ $0 \le b \le 7$                                                                                                                                                                                                                                      | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \end{array}$ |        |      |  |  |

| Ope                                       | ration:                                               | skip if (f <t< td=""><td>o&gt;) = 0</td><td></td><td></td></t<>                                                                                                                                                                                                        | o>) = 0                                                             |        |      |  |  |

| Stat                                      | us Affected:                                          | None                                                                                                                                                                                                                                                                   |                                                                     |        |      |  |  |

| Enc                                       | oding:                                                | 1001                                                                                                                                                                                                                                                                   | 1bbb                                                                | ffff   | ffff |  |  |

| Des                                       | cription:                                             | If bit 'b' in register 'f' is 0 then the next<br>instruction is skipped.<br>If bit 'b' is 0 then the next instruction<br>fetched during the current instruction ex<br>cution is discarded, and a NOP is exe-<br>cuted instead, making this a two-cycle<br>instruction. |                                                                     |        |      |  |  |

| Wor                                       | ds:                                                   | 1                                                                                                                                                                                                                                                                      |                                                                     |        |      |  |  |

| Cycl                                      | les:                                                  | 1(2)                                                                                                                                                                                                                                                                   |                                                                     |        |      |  |  |

| QC                                        | ycle Activity:                                        |                                                                                                                                                                                                                                                                        |                                                                     |        |      |  |  |

|                                           | Q1                                                    | Q2                                                                                                                                                                                                                                                                     | Q3                                                                  |        | Q4   |  |  |

|                                           | Decode                                                | Read<br>register 'f'                                                                                                                                                                                                                                                   | Execu                                                               | ite    | NOP  |  |  |

| lf sk                                     | ip:                                                   |                                                                                                                                                                                                                                                                        |                                                                     |        |      |  |  |

|                                           | Q1                                                    | Q2                                                                                                                                                                                                                                                                     | Q3                                                                  |        | Q4   |  |  |

|                                           | Forced NOP                                            | NOP                                                                                                                                                                                                                                                                    | Execu                                                               | ite    | NOP  |  |  |

| <u>Exa</u>                                | mple:                                                 | FALSE                                                                                                                                                                                                                                                                  | BTFSC<br>:                                                          | FLAG,1 |      |  |  |

| Before Instruction<br>PC = address (HERE) |                                                       |                                                                                                                                                                                                                                                                        |                                                                     |        |      |  |  |

|                                           | After Instructi<br>If FLAG<7<br>PC<br>If FLAG<7<br>PC | l> = 0;<br>= ac<br>l> = 1;                                                                                                                                                                                                                                             | ldress (TR                                                          |        |      |  |  |

| CPFSEQ                                         | Compare<br>skip if f =                                        | f with WREC<br>WREG                                                                                                                                                                                                    | Э,     | CPF        | SGT                                                                                                                                                                                                                                                                                       | Compare<br>skip if f >                      | f with WRE<br>WREG                             | G,      |  |

|------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------|---------|--|

| Syntax:                                        | [label]                                                       | CPFSEQ f                                                                                                                                                                                                               |        | Syn        | tax:                                                                                                                                                                                                                                                                                      | [label]                                     | [label] CPFSGT f                               |         |  |

| Operands:                                      | $0 \le f \le 255$                                             | 5                                                                                                                                                                                                                      |        | Ope        | rands:                                                                                                                                                                                                                                                                                    | $0 \le f \le 255$                           | 5                                              |         |  |

| Operation:                                     | (f) – (WRE)<br>skip if (f) =<br>(unsigned o                   | , · ·                                                                                                                                                                                                                  |        | Ope        | ration:                                                                                                                                                                                                                                                                                   | (f) – (WRE0<br>skip if (f) ><br>(unsigned o |                                                |         |  |

| Status Affected:                               | None                                                          |                                                                                                                                                                                                                        |        | Stat       | us Affected:                                                                                                                                                                                                                                                                              | None                                        |                                                |         |  |

| Encoding:                                      | 0011                                                          | 0001 fff                                                                                                                                                                                                               | f ffff | Enc        | oding:                                                                                                                                                                                                                                                                                    | 0011                                        | 0010 ff:                                       | ff ffff |  |

| Description:                                   | location 'f' t<br>performing<br>If 'f' = WRE<br>tion is disca | pares the contents of data memory<br>ion 'f' to the contents of WREG by<br>prming an unsigned subtraction.<br>= WREG then the fetched instruc-<br>is discarded and an NOP is exe-<br>d instead making this a two-cycle |        | cription:  | Compares the contents of data memo<br>location 'f' to the contents of the WRE<br>by performing an unsigned subtraction<br>If the contents of 'f' > the contents of<br>WREG then the fetched instruction is<br>discarded and an NOP is executed<br>instead making this a two-cycle instru- |                                             |                                                |         |  |

| Words:                                         | 1                                                             |                                                                                                                                                                                                                        |        | 14/0 -     | de .                                                                                                                                                                                                                                                                                      | tion.<br>1                                  |                                                |         |  |

| Cycles:                                        | 1 (2)                                                         |                                                                                                                                                                                                                        |        | Wor        |                                                                                                                                                                                                                                                                                           | -                                           |                                                |         |  |

| Q Cycle Activity:                              |                                                               |                                                                                                                                                                                                                        |        | Cyc        |                                                                                                                                                                                                                                                                                           | 1 (2)                                       |                                                |         |  |

| Q1                                             | Q2                                                            | Q3                                                                                                                                                                                                                     | Q4     | QC         | ycle Activity:<br>Q1                                                                                                                                                                                                                                                                      | Q2                                          | Q3                                             | Q4      |  |

| Decode                                         | Read<br>register 'f'                                          | Execute                                                                                                                                                                                                                | NOP    |            | Decode                                                                                                                                                                                                                                                                                    | Read                                        | Execute                                        | NOP     |  |

| If skip:                                       |                                                               |                                                                                                                                                                                                                        |        | lf sk      | in:                                                                                                                                                                                                                                                                                       | register 'f'                                |                                                |         |  |

| Q1                                             | Q2                                                            | Q3                                                                                                                                                                                                                     | Q4     |            | Q1                                                                                                                                                                                                                                                                                        | Q2                                          | Q3                                             | Q4      |  |

| Forced NOP                                     | NOP                                                           | Execute                                                                                                                                                                                                                | NOP    |            | Forced NOP                                                                                                                                                                                                                                                                                | NOP                                         | Execute                                        | NOP     |  |

| <u>Example</u> :                               | NEQUAL                                                        | CPFSEQ REG<br>:<br>:                                                                                                                                                                                                   |        | <u>Exa</u> | mple:                                                                                                                                                                                                                                                                                     | HERE<br>NGREATER<br>GREATER                 | CPFSGT RE<br>:<br>:                            | G       |  |

| Before Instru<br>PC Addre                      |                                                               |                                                                                                                                                                                                                        |        |            | Before Instru                                                                                                                                                                                                                                                                             | -                                           | ·                                              |         |  |

| WREG<br>REG                                    | ess = HE<br>= ?<br>= ?                                        | RE                                                                                                                                                                                                                     |        |            | PC<br>WREG                                                                                                                                                                                                                                                                                |                                             | dress (HERE)                                   |         |  |

| After Instruct<br>If REG<br>PC<br>If REG<br>PC | = W<br>= Ac<br>≠ W                                            | REG;<br>Idress (EQUAL<br>REG;<br>Idress (NEQUA                                                                                                                                                                         |        |            | After Instruc<br>If REG<br>PC<br>If REG<br>PC                                                                                                                                                                                                                                             | > Wi<br>= Ad<br>≤ Wi                        | REG;<br>Idress (GREAT<br>REG;<br>Idress (NGREZ |         |  |

| CPFS                                                                                                 | SLT                      |                                                                      | Compare f with WREG,<br>skip if f < WREG                                                                                                                                                                                                                                                            |         |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

| Synta                                                                                                | ax:                      | [label]                                                              | CPFSLT f                                                                                                                                                                                                                                                                                            |         |  |  |  |  |  |

| Opera                                                                                                | ands:                    | $0 \le f \le 25$                                                     | 5                                                                                                                                                                                                                                                                                                   |         |  |  |  |  |  |

| Opera                                                                                                | ation:                   | (f) – (WRE<br>skip if (f) <<br>(unsigned                             | G),<br>(WREG)<br>comparison)                                                                                                                                                                                                                                                                        |         |  |  |  |  |  |

| Statu                                                                                                | s Affected:              | None                                                                 |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

| Enco                                                                                                 | ding:                    | 0011                                                                 | 0000 ffi                                                                                                                                                                                                                                                                                            | ff ffff |  |  |  |  |  |

| Desc                                                                                                 | ription:                 | location 'f'<br>performing<br>If the conte<br>WREG, the<br>discarded | Compares the contents of data memory<br>location 'f' to the contents of WREG by<br>performing an unsigned subtraction.<br>If the contents of 'f' < the contents of<br>WREG, then the fetched instruction is<br>discarded and an NOP is executed<br>instead making this a two-cycle instruc-<br>tion |         |  |  |  |  |  |

| Word                                                                                                 | s:                       | 1                                                                    |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

| Cycle                                                                                                | es:                      | 1 (2)                                                                |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

| Q Cy                                                                                                 | cle Activity:            |                                                                      |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

|                                                                                                      | Q1                       | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                                  | Q4      |  |  |  |  |  |

|                                                                                                      | Decode                   | Read<br>register 'f'                                                 | Execute                                                                                                                                                                                                                                                                                             | NOP     |  |  |  |  |  |

| lf skip                                                                                              | o:                       |                                                                      |                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

| -                                                                                                    | Q1                       | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                                  | Q4      |  |  |  |  |  |

|                                                                                                      | Forced NOP               | NOP                                                                  | Execute                                                                                                                                                                                                                                                                                             | NOP     |  |  |  |  |  |

| <u>Exarr</u>                                                                                         | nple:                    | HERE<br>NLESS<br>LESS                                                | CPFSLT REG<br>:<br>:                                                                                                                                                                                                                                                                                |         |  |  |  |  |  |