Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 232 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42at-33i-l |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

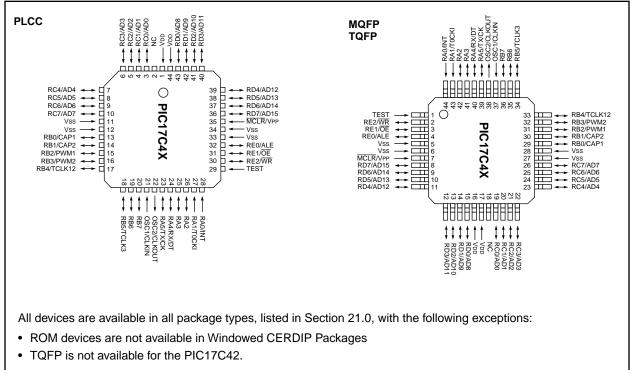

### Pin Diagrams Cont.'d

# TABLE 1-1: PIC17CXX FAMILY OF DEVICES

| Features                    | PIC17C42   | PIC17CR42            | PIC17C42A            | PIC17C43             | PIC17CR43            | PIC17C44             |                      |

|-----------------------------|------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Maximum Frequency of O      | 25 MHz     | 33 MHz               | 33 MHz               | 33 MHz               | 33 MHz               | 33 MHz               |                      |

| Operating Voltage Range     | 4.5 - 5.5V | 2.5 - 6.0V           |                      |

| Program Memory x16          | (EPROM)    | 2K                   | -                    | 2K 4K                |                      | -                    | 8K                   |

|                             | (ROM)      | -                    | 2K                   | -                    | -                    | 4K                   | -                    |

| Data Memory (bytes)         |            | 232                  | 232                  | 232                  | 454                  | 454                  | 454                  |

| Hardware Multiplier (8 x 8  | )          | -                    | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer0 (16-bit + 8-bit post | scaler)    | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer1 (8-bit)              |            | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer2 (8-bit)              |            | Yes                  | Yes                  | Yes                  | Yes                  | Yes Yes              |                      |

| Timer3 (16-bit)             |            | Yes                  | Yes                  | Yes                  | Yes Yes              |                      | Yes                  |

| Capture inputs (16-bit)     | 2          | 2                    | 2                    | 2                    | 2                    | 2                    |                      |

| PWM outputs (up to 10-bit   | t)         | 2                    | 2                    | 2                    | 2                    | 2                    | 2                    |

| USART/SCI                   |            | Yes                  | Yes                  | Yes                  | Yes                  | Yes Yes              |                      |

| Power-on Reset              |            | Yes                  | Yes                  | Yes                  | Yes Yes              |                      | Yes                  |

| Watchdog Timer              |            | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| External Interrupts         |            | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Interrupt Sources           |            | 11                   | 11                   | 11                   | 11                   | 11                   | 11                   |

| Program Memory Code P       | rotect     | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| I/O Pins                    |            | 33                   | 33                   | 33                   | 33                   | 33                   | 33                   |

| I/O High Current Capabil-   | Source     | 25 mA                |

| ity                         | Sink       | 25 mA <sup>(1)</sup> |

| Package Types               |            | 40-pin DIP           |

|                             |            | 44-pin PLCC          |

|                             |            | 44-pin MQFP          |

|                             |            |                      | 44-pin TQFP          |

Note 1: Pins RA2 and RA3 can sink up to 60 mA.

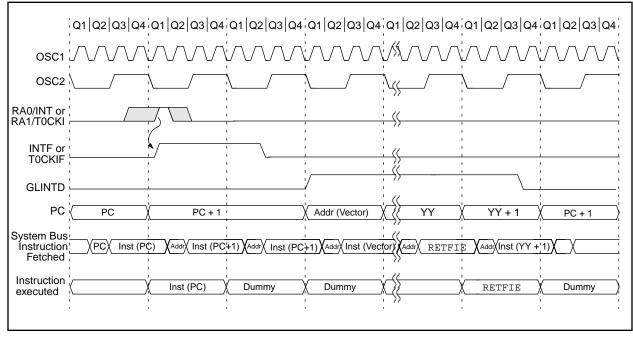

## 5.5 RA0/INT Interrupt

The external interrupt on the RA0/INT pin is edge triggered. Either the rising edge, if INTEDG bit (T0STA<7>) is set, or the falling edge, if INTEDG bit is clear. When a valid edge appears on the RA0/INT pin, the INTF bit (INTSTA<4>) is set. This interrupt can be disabled by clearing the INTE control bit (INTSTA<0>). The INT interrupt can wake the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

## 5.6 TMR0 Interrupt

An overflow (FFFFh  $\rightarrow$  0000h) in TMR0 will set the T0IF (INTSTA<5>) bit. The interrupt can be enabled/ disabled by setting/clearing the T0IE control bit (INTSTA<1>). For operation of the Timer0 module, see Section 11.0.

# 5.7 TOCKI Interrupt

The external interrupt on the RA1/T0CKI pin is edge triggered. Either the rising edge, if the T0SE bit (T0STA<6>) is set, or the falling edge, if the T0SE bit is clear. When a valid edge appears on the RA1/T0CKI pin, the T0CKIF bit (INTSTA<6>) is set. This interrupt can be disabled by clearing the T0CKIE control bit (INTSTA<2>). The T0CKI interrupt can wake up the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

## 5.8 Peripheral Interrupt

The peripheral interrupt flag indicates that at least one of the peripheral interrupts occurred (PEIF is set). The PEIF bit is a read only bit, and is a bit wise OR of all the flag bits in the PIR register AND'ed with the corresponding enable bits in the PIE register. Some of the peripheral interrupts can wake the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

# FIGURE 5-5: INT PIN / TOCKI PIN INTERRUPT TIMING

NOTES:

#### 6.4.1 INDIRECT ADDRESSING REGISTERS

The PIC17C4X has four registers for indirect addressing. These registers are:

- INDF0 and FSR0

- INDF1 and FSR1

Registers INDF0 and INDF1 are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data. The FSR is an 8-bit register and allows addressing anywhere in the 256-byte data memory address range. For banked memory, the bank of memory accessed is specified by the value in the BSR.

If file INDF0 (or INDF1) itself is read indirectly via an FSR, all '0's are read (Zero bit is set). Similarly, if INDF0 (or INDF1) is written to indirectly, the operation will be equivalent to a NOP, and the status bits are not affected.

#### 6.4.2 INDIRECT ADDRESSING OPERATION

The indirect addressing capability has been enhanced over that of the PIC16CXX family. There are two control bits associated with each FSR register. These two bits configure the FSR register to:

- Auto-decrement the value (address) in the FSR after an indirect access

- Auto-increment the value (address) in the FSR after an indirect access

- No change to the value (address) in the FSR after an indirect access

These control bits are located in the ALUSTA register. The FSR1 register is controlled by the FS3:FS2 bits and FSR0 is controlled by the FS1:FS0 bits.

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the ALUSTA register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

If the FSR register contains a value of 0h, an indirect read will read 0h (Zero bit is set) while an indirect write will be equivalent to a NOP (status bits are not affected).

Indirect addressing allows single cycle data transfers within the entire data space. This is possible with the use of the MOVPF and MOVFP instructions, where either 'p' or 'f' is specified as INDF0 (or INDF1).

If the source or destination of the indirect address is in banked memory, the location accessed will be determined by the value in the BSR. A simple program to clear RAM from 20h - FFh is shown in Example 6-1.

## EXAMPLE 6-1: INDIRECT ADDRESSING

|    | MOVLW  | 0x20        | ;           |           |

|----|--------|-------------|-------------|-----------|

|    | MOVWF  | FSR0        | ; FSR0 = 20 | h         |

|    | BCF    | ALUSTA, FS1 | ; Increment | FSR       |

|    | BSF    | ALUSTA, FSO | ; after acc | ess       |

|    | BCF    | ALUSTA, C   | ; C = 0     |           |

|    | MOVLW  | END_RAM + 1 | ;           |           |

| LP | CLRF   | INDF0       | ; Addr(FSR) | = 0       |

|    | CPFSEQ | FSR0        | ; FSRO = EN | ID_RAM+1? |

|    | GOTO   | LP          | ; NO, clear | next      |

|    | :      |             | ; YES, All  | RAM is    |

|    | :      |             | ; cleared   |           |

|    |        |             |             |           |

#### 6.5 <u>Table Pointer (TBLPTRL and</u> <u>TBLPTRH)</u>

File registers TBLPTRL and TBLPTRH form a 16-bit pointer to address the 64K program memory space. The table pointer is used by instructions TABLWT and TABLRD.

The TABLRD and the TABLWT instructions allow transfer of data between program and data space. The table pointer serves as the 16-bit address of the data word within the program memory. For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 7.0.

### 6.6 <u>Table Latch (TBLATH, TBLATL)</u>

The table latch (TBLAT) is a 16-bit register, with TBLATH and TBLATL referring to the high and low bytes of the register. It is not mapped into data or program memory. The table latch is used as a temporary holding latch during data transfer between program and data memory (see descriptions of instructions TABLRD, TABLWT, TLRD and TLWT). For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 7.0.

## 7.1 <u>Table Writes to Internal Memory</u>

A table write operation to internal memory causes a long write operation. The long write is necessary for programming the internal EPROM. Instruction execution is halted while in a long write cycle. The long write will be terminated by any enabled interrupt. To ensure that the EPROM location has been well programmed, a minimum programming time is required (see specification #D114). Having only one interrupt enabled to terminate the long write ensures that no unintentional interrupts will prematurely terminate the long write.

The sequence of events for programming an internal program memory location should be:

- 1. Disable all interrupt sources, except the source to terminate EPROM program write.

- 2. Raise MCLR/VPP pin to the programming voltage.

- 3. Clear the WDT.

- 4. Do the table write. The interrupt will terminate the long write.

- 5. Verify the memory location (table read).

- **Note:** Programming requirements must be met. See timing specification in electrical specifications for the desired device. Violating these specifications (including temperature) may result in EPROM locations that are not fully programmed and may lose their state over time.

### 7.1.1 TERMINATING LONG WRITES

An interrupt source or reset are the only events that terminate a long write operation. Terminating the long write from an interrupt source requires that the interrupt enable and flag bits are set. The GLINTD bit only enables the vectoring to the interrupt address.

If the TOCKI, RA0/INT, or TMR0 interrupt source is used to terminate the long write; the interrupt flag, of the highest priority enabled interrupt, will terminate the long write and automatically be cleared.

- **Note 1:** If an interrupt is pending, the TABLWT is aborted (an NOP is executed). The highest priority pending interrupt, from the TOCKI, RA0/INT, or TMR0 sources that is enabled, has its flag cleared.

- **Note 2:** If the interrupt is not being used for the program write timing, the interrupt should be disabled. This will ensure that the interrupt is not lost, nor will it terminate the long write prematurely.

If a peripheral interrupt source is used to terminate the long write, the interrupt enable and flag bits must be set. The interrupt flag will not be automatically cleared upon the vectoring to the interrupt vector address.

If the GLINTD bit is cleared prior to the long write, when the long write is terminated, the program will branch to the interrupt vector.

If the GLINTD bit is set prior to the long write, when the long write is terminated, the program will not vector to the interrupt address.

| Interrupt<br>Source     | GLINTD | Enable<br>Bit | Flag<br>Bit | Action                                                                                                              |

|-------------------------|--------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------|

| RA0/INT, TMR0,<br>T0CKI | 0      | 1             | 1           | Terminate long table write (to internal program<br>memory), branch to interrupt vector (branch clears<br>flag bit). |

|                         | 0      | 1             | 0           | None                                                                                                                |

|                         | 1      | 0             | x           | None                                                                                                                |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is automatically cleared).                           |

| Peripheral              | 0      | 1             | 1           | Terminate table write, branch to interrupt vector.                                                                  |

|                         | 0      | 1             | 0           | None                                                                                                                |

|                         | 1      | 0             | x           | None                                                                                                                |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is set).                                             |

## TABLE 7-1: INTERRUPT - TABLE WRITE INTERACTION

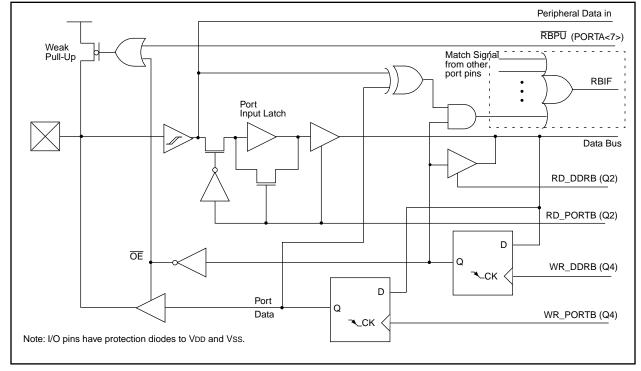

## 9.2 PORTB and DDRB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is DDRB. A '1' in DDRB configures the corresponding port pin as an input. A '0' in the DDRB register configures the corresponding port pin as an output. Reading PORTB reads the status of the pins, whereas writing to it will write to the port latch.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{\text{RBPU}}$  (PORTA<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are enabled on any reset.

PORTB also has an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB0 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB0) are compared with the value in the PORTB data latch. The "mismatch" outputs of RB7:RB0 are OR'ed together to generate the PORTB Interrupt Flag RBIF (PIR<7>). This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt by:

- a) Read-Write PORTB (such as; MOVPF PORTB, PORTB). This will end mismatch condition.

- b) Then, clear the RBIF bit.

A mismatch condition will continue to set the RBIF bit. Reading then writing PORTB will end the mismatch condition, and allow the RBIF bit to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on this port, allows easy interface to a key pad and make it possible for wake-up on key-depression. For an example, refer to AN552 in the *Embedded Control Handbook*.

The interrupt on change feature is recommended for wake-up on operations where PORTB is only used for the interrupt on change feature and key depression operation.

FIGURE 9-4: BLOCK DIAGRAM OF RB<7:4> AND RB<1:0> PORT PINS

# TABLE 9-5: PORTC FUNCTIONS

| Name    | Bit  | Buffer Type | Function                                     |

|---------|------|-------------|----------------------------------------------|

| RC0/AD0 | bit0 | TTL         | Input/Output or system bus address/data pin. |

| RC1/AD1 | bit1 | TTL         | Input/Output or system bus address/data pin. |

| RC2/AD2 | bit2 | TTL         | Input/Output or system bus address/data pin. |

| RC3/AD3 | bit3 | TTL         | Input/Output or system bus address/data pin. |

| RC4/AD4 | bit4 | TTL         | Input/Output or system bus address/data pin. |

| RC5/AD5 | bit5 | TTL         | Input/Output or system bus address/data pin. |

| RC6/AD6 | bit6 | TTL         | Input/Output or system bus address/data pin. |

| RC7/AD7 | bit7 | TTL         | Input/Output or system bus address/data pin. |

Legend: TTL = TTL input.

# TABLE 9-6: REGISTERS/BITS ASSOCIATED WITH PORTC

| Address     | Name  | Bit 7       | Bit 6         | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |  |

|-------------|-------|-------------|---------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------------------------|-----------------------------------------|--|

| 11h, Bank 1 | PORTC | RC7/<br>AD7 | RC6/<br>AD6   | RC5/<br>AD5 | RC4/<br>AD4 | RC3/<br>AD3 | RC2/<br>AD2 | RC1/<br>AD1 | RC0/<br>AD0 | xxxx xxxx                     | uuuu uuuu                               |  |

| 10h, Bank 1 | DDRC  | Data dired  | ction registe | 1111 1111   | 1111 1111   |             |             |             |             |                               |                                         |  |

Legend: x = unknown, u = unchanged.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

### 9.5 I/O Programming Considerations

#### 9.5.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. For example, the BCF and BSF instructions read the register into the CPU, execute the bit operation, and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g. bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading a port reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (BCF, BSF, BTG, etc.) on a port, the value of the port pins is read, the desired operation is performed with this value, and the value is then written to the port latch.

Example 9-5 shows the effect of two sequential read-modify-write instructions on an I/O port.

#### EXAMPLE 9-5: READ MODIFY WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORT settings: PORTB<7:4> Inputs PORTB<3:0> Outputs ; ; PORTB<7:6> have pull-ups and are ; not connected to other circuitry ; PORT latch PORT pins ; ; \_\_\_\_\_ \_\_\_\_\_ ; PORTB, 7 BCF 01pp pppp 11pp pppp BCF PORTB, 6 10pp pppp 11pp pppp ; BCF DDRB, 7 10pp pppp 11pp pppp BCF DDRB, 6 10pp pppp 10pp pppp ; ; Note that the user may have expected the ; pin values to be 00pp pppp. The 2nd BCF ; caused RB7 to be latched as the pin value ; (High).

Note: A pin actively outputting a Low or High should not be driven from external devices in order to change the level on this pin (i.e. "wired-or", "wired-and"). The resulting high output currents may damage the device.

#### 9.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 9-9). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before executing the instruction that reads the values on that I/O port. Otherwise, the previous state of that pin may be read into the CPU rather than the "new" state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

## FIGURE 9-9: SUCCESSIVE I/O OPERATION

| Instruction<br>fetched  | Q1  Q2  Q3  Q4<br>PC<br>MOVWF PORTB<br>write to<br>PORTB | PC + 1                           | Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4<br><u>PC+2</u> <u>PC+3</u><br>NOP NOP | Note:<br>This example shows a write to PORTB<br>followed by a read from PORTB.<br>Note that:<br>data setup time = (0.25 Tcy - TPD)<br>where TcY = instruction cycle.<br>TPD = propagation delay |

|-------------------------|----------------------------------------------------------|----------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB7:RB0                 |                                                          |                                  | X                                                             | Therefore, at higher clock<br>frequencies, a write followed by a                                                                                                                                |

|                         |                                                          |                                  | Port pin<br>sampled here                                      | read may be problematic.                                                                                                                                                                        |

| Instruction<br>executed |                                                          | MOVWF PORTB<br>write to<br>PORTB | MOVF PORTB,W NOP                                              |                                                                                                                                                                                                 |

|                         |                                                          |                                  | · · · · ·                                                     |                                                                                                                                                                                                 |

| Address       | Name   | Bit 7    | Bit 6                                        | Bit 5 | Bit 4     | Bit 3     | Bit 2         | Bit 1 | Bit 1 Bit 0 Power-on other |           | Value on all<br>other resets<br>(Note1) |  |  |

|---------------|--------|----------|----------------------------------------------|-------|-----------|-----------|---------------|-------|----------------------------|-----------|-----------------------------------------|--|--|

| 05h, Unbanked | TOSTA  | INTEDG   | T0SE                                         | TOCS  | PS3       | PS2       | PS1           | PS0   |                            | 0000 000- | 0000 000-                               |  |  |

| 06h, Unbanked | CPUSTA | —        | _                                            | STKAV | GLINTD    | TO        | PD            | _     | _                          | 11 11     | 11 qq                                   |  |  |

| 07h, Unbanked | INTSTA | PEIF     | TOCKIF                                       | T0IF  | INTF      | PEIE      | <b>T0CKIE</b> | TOIE  | INTE                       | 0000 0000 | 0000 0000                               |  |  |

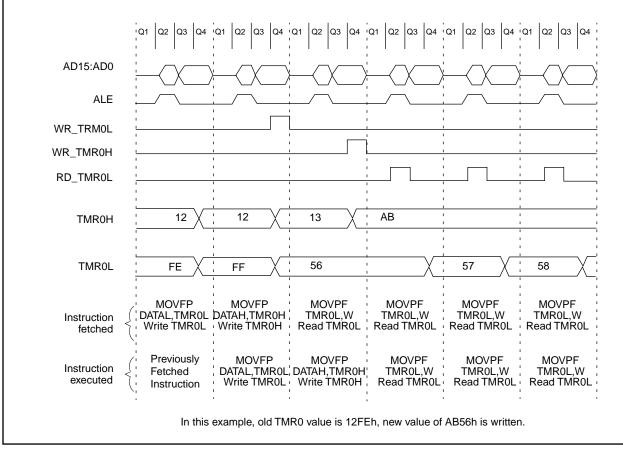

| 0Bh, Unbanked | TMR0L  | TMR0 reg | ister; low byt                               |       | xxxx xxxx | uuuu uuuu |               |       |                            |           |                                         |  |  |

| 0Ch, Unbanked | TMR0H  | TMR0 reg | TMR0 register; high byte xxxx xxxx uuuu uuuu |       |           |           |               |       |                            |           |                                         |  |  |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', g - value depends on condition, Shaded cells are not used by Timer0. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

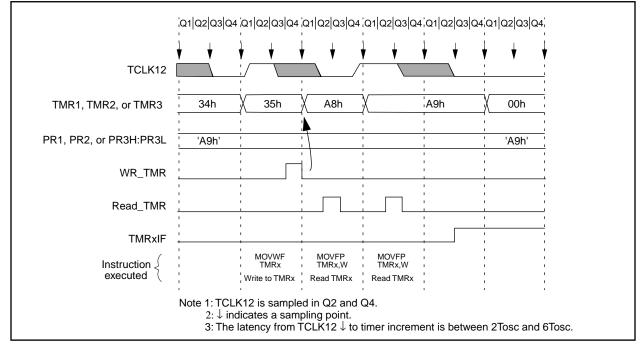

#### 12.2.3 EXTERNAL CLOCK INPUT FOR TIMER3

When TMR3CS is set, the 16-bit TMR3 increments on the falling edge of clock input TCLK3. The input on the RB5/TCLK3 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on TCLK3 to the time TMR3 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section. Figure 12-9 shows the timing diagram when operating from an external clock.

#### 12.2.4 READING/WRITING TIMER3

Since Timer3 is a 16-bit timer and only 8-bits at a time can be read or written, care should be taken when reading or writing while the timer is running. The best method to read or write the timer is to stop the timer, perform any read or write operation, and then restart Timer3 (using the TMR3ON bit). However, if it is necessary to keep Timer3 free-running, care must be taken. For writing to the 16-bit TMR3, Example 12-2 may be used. For reading the 16-bit TMR3, Example 12-3 may be used. Interrupts must be disabled during this routine.

#### EXAMPLE 12-2: WRITING TO TMR3

BSF CPUSTA, GLINTD ;Disable interrupt MOVFP RAM\_L, TMR3L ; MOVFP RAM\_H, TMR3H ; BCF CPUSTA, GLINTD ;Done,enable interrupt

#### **EXAMPLE 12-3: READING FROM TMR3**

| MOVPF TMR3L, TMPLO ;read low t<br>MOVPF TMR3H, TMPHI ;read high<br>MOVFP TMPLO, WREG ;tmplo -> w | tmr0  |

|--------------------------------------------------------------------------------------------------|-------|

| CPFSLT TMR3L, WREG ;tmr0l < wr                                                                   | eg?   |

| RETURN ;no then re                                                                               | eturn |

| MOVPF TMR3L, TMPLO ;read low t                                                                   | .mr0  |

| MOVPF TMR3H, TMPHI ;read high                                                                    | tmr0  |

| RETURN ; return                                                                                  |       |

### FIGURE 12-9: TMR1, TMR2, AND TMR3 OPERATION IN EXTERNAL CLOCK MODE

# PIC17C4X

| BAUD<br>RATE | BAUD SPBRG |        | Fosc = 2  | DSC = 25 MHz<br>SPBRG<br>value |        | _         |       | SPBRG<br>value | Fosc = 1  | SPBRG<br>value |        |           |

|--------------|------------|--------|-----------|--------------------------------|--------|-----------|-------|----------------|-----------|----------------|--------|-----------|

| (K)          | KBAUD      | %ERROR | (decimal) | KBAUD                          | %ERROR | (decimal) | KBAUD | %ERROR         | (decimal) | KBAUD          | %ERROR | (decimal) |

| 0.3          | NA         | _      | _         | NA                             | _      | _         | NA    | _              | _         | NA             |        | _         |

| 1.2          | NA         | _      | _         | NA                             | _      | _         | NA    | _              | _         | NA             | _      | _         |

| 2.4          | NA         | _      | _         | NA                             | _      | _         | NA    | _              | _         | NA             | —      | _         |

| 9.6          | NA         | —      | —         | NA                             | —      | —         | NA    | —              | —         | NA             | —      | —         |

| 19.2         | NA         | _      | —         | NA                             | —      | —         | 19.53 | +1.73          | 255       | 19.23          | +0.16  | 207       |

| 76.8         | 77.10      | +0.39  | 106       | 77.16                          | +0.47  | 80        | 76.92 | +0.16          | 64        | 76.92          | +0.16  | 51        |

| 96           | 95.93      | -0.07  | 85        | 96.15                          | +0.16  | 64        | 96.15 | +0.16          | 51        | 95.24          | -0.79  | 41        |

| 300          | 294.64     | -1.79  | 27        | 297.62                         | -0.79  | 20        | 294.1 | -1.96          | 16        | 307.69         | +2.56  | 12        |

| 500          | 485.29     | -2.94  | 16        | 480.77                         | -3.85  | 12        | 500   | 0              | 9         | 500            | 0      | 7         |

| HIGH         | 8250       | _      | 0         | 6250                           | _      | 0         | 5000  | _              | 0         | 4000           | _      | 0         |

| LOW          | 32.22      | _      | 255       | 24.41                          | _      | 255       | 19.53 | _              | 255       | 15.625         | _      | 255       |

| BAUD                                                  | Fosc = 10 M                                           | Hz                             | SPBRG                                      | FOSC = 7.159                                                | MHz                     | SPBRG                              | FOSC = 5.068                                       | MHz             | SPBRG              |

|-------------------------------------------------------|-------------------------------------------------------|--------------------------------|--------------------------------------------|-------------------------------------------------------------|-------------------------|------------------------------------|----------------------------------------------------|-----------------|--------------------|

| RATE<br>(K)                                           | KBAUD                                                 | %ERROR                         | value<br>(decimal)                         | KBAUD                                                       | %ERROR                  | value<br>(decimal)                 | KBAUD                                              | %ERROR          | value<br>(decimal) |

| 0.3                                                   | NA                                                    | _                              | _                                          | NA                                                          | _                       | _                                  | NA                                                 | _               | _                  |

| 1.2                                                   | NA                                                    | _                              | _                                          | NA                                                          | _                       | _                                  | NA                                                 | _               | _                  |

| 2.4                                                   | NA                                                    | _                              | _                                          | NA                                                          | _                       | _                                  | NA                                                 | _               | _                  |

| 9.6                                                   | 9.766                                                 | +1.73                          | 255                                        | 9.622                                                       | +0.23                   | 185                                | 9.6                                                | 0               | 131                |

| 19.2                                                  | 19.23                                                 | +0.16                          | 129                                        | 19.24                                                       | +0.23                   | 92                                 | 19.2                                               | 0               | 65                 |

| 76.8                                                  | 75.76                                                 | -1.36                          | 32                                         | 77.82                                                       | +1.32                   | 22                                 | 79.2                                               | +3.13           | 15                 |

| 96                                                    | 96.15                                                 | +0.16                          | 25                                         | 94.20                                                       | -1.88                   | 18                                 | 97.48                                              | +1.54           | 12                 |

| 300                                                   | 312.5                                                 | +4.17                          | 7                                          | 298.3                                                       | -0.57                   | 5                                  | 316.8                                              | +5.60           | 3                  |

| 500                                                   | 500                                                   | 0                              | 4                                          | NA                                                          | _                       | _                                  | NA                                                 | _               | _                  |

| HIGH                                                  | 2500                                                  | _                              | 0                                          | 1789.8                                                      | _                       | 0                                  | 1267                                               | _               | 0                  |

| LOW                                                   | 9.766                                                 | —                              | 255                                        | 6.991                                                       | —                       | 255                                | 4.950                                              | —               | 255                |

| BAUD                                                  | Fosc = 3.579                                          | MHz                            | SPBRG                                      | Fosc = 1 MH                                                 | Z                       | SPBRG                              | Fosc = 32.76                                       | 8 kHz           | SPBRG              |

| RATE                                                  |                                                       |                                |                                            |                                                             |                         |                                    |                                                    |                 |                    |

| (K)                                                   | KBAUD                                                 | %ERROR                         | value<br>(decimal)                         | KBAUD                                                       | %ERROR                  | value<br>(decimal)                 | KBAUD                                              | %ERROR          | value<br>(decimal) |

| (K)<br>0.3                                            | KBAUD<br>NA                                           | %ERROR                         |                                            | KBAUD<br>NA                                                 | %ERROR                  |                                    | KBAUD<br>0.303                                     | %ERROR<br>+1.14 |                    |

|                                                       | -                                                     | %ERROR<br>—<br>—               |                                            |                                                             | %ERROR<br>—<br>+0.16    |                                    |                                                    |                 | (decimal)          |

| 0.3                                                   | NA                                                    | %ERROR<br>                     |                                            | NA                                                          | _                       | (decimal)                          | 0.303                                              | +1.14           | (decimal)<br>26    |

| 0.3                                                   | NA<br>NA                                              | %ERROR<br>—<br>—<br>—<br>+0.23 |                                            | NA<br>1.202                                                 | <br>+0.16               | (decimal)<br>—<br>207              | 0.303<br>1.170                                     | +1.14           | (decimal)<br>26    |

| 0.3<br>1.2<br>2.4                                     | NA<br>NA<br>NA                                        | <br>                           | (decimal)<br>                              | NA<br>1.202<br>2.404                                        |                         | (decimal)<br>—<br>207<br>103       | 0.303<br>1.170<br>NA                               | +1.14           | (decimal)<br>26    |

| 0.3<br>1.2<br>2.4<br>9.6                              | NA<br>NA<br>NA<br>9.622                               | <br><br>+0.23                  | (decimal)<br>—<br>—<br>92                  | NA<br>1.202<br>2.404<br>9.615                               | +0.16<br>+0.16<br>+0.16 | (decimal)<br>—<br>207<br>103<br>25 | 0.303<br>1.170<br>NA<br>NA                         | +1.14           | (decimal)<br>26    |

| 0.3<br>1.2<br>2.4<br>9.6<br>19.2                      | NA<br>NA<br>NA<br>9.622<br>19.04                      | <br><br>+0.23<br>-0.83         | (decimal)<br>—<br>—<br>92<br>46            | NA<br>1.202<br>2.404<br>9.615<br>19.24                      |                         | (decimal)<br>                      | 0.303<br>1.170<br>NA<br>NA<br>NA                   | +1.14           | (decimal)<br>26    |

| 0.3<br>1.2<br>2.4<br>9.6<br>19.2<br>76.8              | NA<br>NA<br>9.622<br>19.04<br>74.57                   |                                | (decimal)<br><br><br>92<br>46<br>11        | NA<br>1.202<br>2.404<br>9.615<br>19.24<br>83.34             |                         | (decimal)<br>                      | 0.303<br>1.170<br>NA<br>NA<br>NA<br>NA             | +1.14           | (decimal)<br>26    |

| 0.3<br>1.2<br>2.4<br>9.6<br>19.2<br>76.8<br>96        | NA<br>NA<br>9.622<br>19.04<br>74.57<br>99.43          |                                | (decimal)<br>—<br>—<br>92<br>46<br>11<br>8 | NA<br>1.202<br>2.404<br>9.615<br>19.24<br>83.34<br>NA       |                         | (decimal)<br>                      | 0.303<br>1.170<br>NA<br>NA<br>NA<br>NA<br>NA       | +1.14           | (decimal)<br>26    |

| 0.3<br>1.2<br>2.4<br>9.6<br>19.2<br>76.8<br>96<br>300 | NA<br>NA<br>9.622<br>19.04<br>74.57<br>99.43<br>298.3 |                                | (decimal)<br>—<br>—<br>92<br>46<br>11<br>8 | NA<br>1.202<br>2.404<br>9.615<br>19.24<br>83.34<br>NA<br>NA |                         | (decimal)<br>                      | 0.303<br>1.170<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA | +1.14           | (decimal)<br>26    |

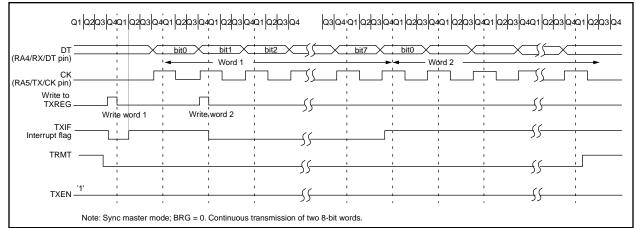

## TABLE 13-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address     | Name  | Bit 7     | Bit 6     | Bit 5    | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|-----------|-----------|----------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR   | RBIF      | TMR3IF    | TMR2IF   | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA | SPEN      | RX9       | SREN     | CREN   | —     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 16h, Bank 0 | TXREG | TX7       | TX6       | TX5      | TX4    | TX3   | TX2   | TX1   | TX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE   | RBIE      | TMR3IE    | TMR2IE   | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA | CSRC      | TX9       | TXEN     | SYNC   | —     |       | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 | SPBRG | Baud rate | generator | register |        |       |       | •     | •     | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous master transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

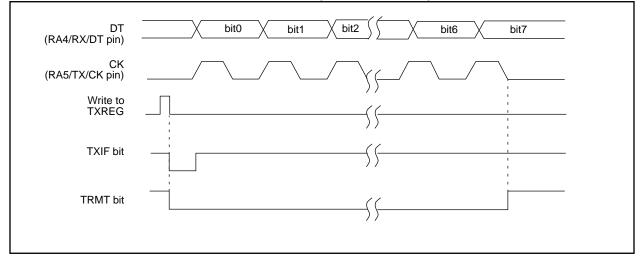

#### FIGURE 13-9: SYNCHRONOUS TRANSMISSION

#### FIGURE 13-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

# 14.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real time applications. The PIC17CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- OSC selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- · Code protection

The PIC17CXX has a Watchdog Timer which can be shut off only through EPROM bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 96 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake from SLEEP through external reset, Watchdog Timer Reset or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LF crystal option saves power. Configuration bits are used to select various options. This configuration word has the format shown in Figure 14-1.

| <u>R/P - 1</u><br>PM2 <sup>(1)</sup> | U - x                          | U - x             | U - x      | U - x        | U - x      | <u>U - x</u> | U - x   |                                                    |

|--------------------------------------|--------------------------------|-------------------|------------|--------------|------------|--------------|---------|----------------------------------------------------|

|                                      |                                |                   |            | _            |            |              | —<br>—  |                                                    |

| oit15-7                              |                                |                   |            |              |            |              | bit0    |                                                    |

| U - x                                | R/P - 1                        | U - x             | R/P - 1    | R/P - 1      | R/P - 1    | R/P - 1      | R/P - 1 |                                                    |

| _                                    | PM1                            | _                 | PM0        | WDTPS1       |            | FOSC1        | FOSC0   | R = Readable bit                                   |

| oit15-7                              |                                | 1                 |            | 11           |            | 1            | bit0    | P = Programmable bit                               |

|                                      |                                |                   |            |              |            |              |         | U = Unimplemented<br>- n = Value for Erased Device |

|                                      |                                |                   |            |              |            |              |         | (x = unknown)                                      |

| oit 15-9:                            | Unimpler                       | <b>nented</b> : R | ead as a   | '1'          |            |              |         |                                                    |

|                                      | -                              |                   |            |              | ot hito    |              |         |                                                    |

| JIL 15,6,                            | 4: <b>PMZ, PM</b><br>111 = Mic |                   |            | Mode Sele    |            |              |         |                                                    |

|                                      | 110 = Mic                      |                   |            |              |            |              |         |                                                    |

|                                      | 101 = Ext                      |                   |            | ler mode     |            |              |         |                                                    |

|                                      |                                |                   |            | controller m | ode        |              |         |                                                    |

| oit 7, 5:                            | Unimpler                       | •                 |            |              |            |              |         |                                                    |

| nit 3-2.                             | WDTPS1                         | WDTPS0            |            | stscaler Se  | elect bits |              |         |                                                    |

| 511 0 2.                             | 11 = WD                        |                   |            |              |            |              |         |                                                    |

|                                      | 10 = WD                        |                   |            |              |            |              |         |                                                    |

|                                      | 01 = WD                        | T enabled         | , postscal | er = 64      |            |              |         |                                                    |

|                                      | 00 = WD                        | T disabled        | , 16-bit o | verflow time | er         |              |         |                                                    |

| oit 1-0:                             | FOSC1:F                        | OSCO. Os          | cillator S | elect bits   |            |              |         |                                                    |

|                                      | 11 = EC (                      |                   |            |              |            |              |         |                                                    |

|                                      | 10 = XT c                      | oscillator        |            |              |            |              |         |                                                    |

|                                      | 01 = RC (                      | oscillator        |            |              |            |              |         |                                                    |

|                                      | 00 = LF o                      | scillator         |            |              |            |              |         |                                                    |

|                                      |                                |                   |            |              |            |              |         |                                                    |

|                                      | This bit do                    |                   |            |              |            |              |         |                                                    |

### FIGURE 14-1: CONFIGURATION WORD

<sup>© 1996</sup> Microchip Technology Inc.

# TABLE 15-2: PIC17CXX INSTRUCTION SET

| Mnemonic, |       | Description                           | Cycles | 16-bit Opcoo   | le   | Status    | Notes |  |

|-----------|-------|---------------------------------------|--------|----------------|------|-----------|-------|--|

| Operands  |       |                                       |        | MSb            | LSb  | Affected  |       |  |

| BYTE-ORIE |       | TILE REGISTER OPERATIONS              | •      |                |      |           | •     |  |

| ADDWF     | f,d   | ADD WREG to f                         | 1      | 0000 111d ffff | ffff | OV,C,DC,Z |       |  |

| ADDWFC    | f,d   | ADD WREG and Carry bit to f           | 1      | 0001 000d ffff | ffff | OV,C,DC,Z |       |  |

| ANDWF     | f,d   | AND WREG with f                       | 1      | 0000 101d ffff | ffff | Z         |       |  |

| CLRF      | f,s   | Clear f, or Clear f and Clear WREG    | 1      | 0010 100s ffff | ffff | None      | 3     |  |

| COMF      | f,d   | Complement f                          | 1      | 0001 001d ffff | ffff | Z         |       |  |

| CPFSEQ    | f     | Compare f with WREG, skip if f = WREG | 1 (2)  | 0011 0001 ffff | ffff | None      | 6,8   |  |

| CPFSGT    | f     | Compare f with WREG, skip if f > WREG | 1 (2)  | 0011 0010 ffff | ffff | None      | 2,6,8 |  |

| CPFSLT    | f     | Compare f with WREG, skip if f < WREG | 1 (2)  | 0011 0000 ffff | ffff | None      | 2,6,8 |  |

| DAW       | f,s   | Decimal Adjust WREG Register          | 1      | 0010 111s ffff | ffff | C         | 3     |  |

| DECF      | f,d   | Decrement f                           | 1      | 0000 011d ffff | ffff | OV,C,DC,Z |       |  |

| DECFSZ    | f,d   | Decrement f, skip if 0                | 1 (2)  | 0001 011d ffff | ffff | None      | 6,8   |  |

| DCFSNZ    | f,d   | Decrement f, skip if not 0            | 1 (2)  | 0010 011d ffff | ffff | None      | 6,8   |  |

| INCF      | f,d   | Increment f                           | 1      | 0001 010d ffff | ffff | OV,C,DC,Z |       |  |

| INCFSZ    | f,d   | Increment f, skip if 0                | 1 (2)  | 0001 111d ffff | ffff | None      | 6,8   |  |

| INFSNZ    | f,d   | Increment f, skip if not 0            | 1 (2)  | 0010 010d ffff | ffff | None      | 6,8   |  |

| IORWF     | f,d   | Inclusive OR WREG with f              | 1      | 0000 100d ffff | ffff | Z         |       |  |

| MOVFP     | f,p   | Move f to p                           | 1      | 011p pppp ffff | ffff | None      |       |  |

| MOVPF     | p,f   | Move p to f                           | 1      | 010p pppp ffff | ffff | Z         |       |  |

| MOVWF     | f     | Move WREG to f                        | 1      | 0000 0001 ffff | ffff | None      |       |  |

| MULWF     | f     | Multiply WREG with f                  | 1      | 0011 0100 ffff | ffff | None      | 9     |  |

| NEGW      | f,s   | Negate WREG                           | 1      | 0010 110s ffff | ffff | OV,C,DC,Z | 1,3   |  |

| NOP       | —     | No Operation                          | 1      | 0000 0000 0000 | 0000 | None      |       |  |

| RLCF      | f,d   | Rotate left f through Carry           | 1      | 0001 101d ffff | ffff | С         |       |  |

| RLNCF     | f,d   | Rotate left f (no carry)              | 1      | 0010 001d ffff | ffff | None      |       |  |

| RRCF      | f,d   | Rotate right f through Carry          | 1      | 0001 100d ffff | ffff | C         |       |  |

| RRNCF     | f,d   | Rotate right f (no carry)             | 1      | 0010 000d ffff | ffff | None      |       |  |

| SETF      | f,s   | Set f                                 | 1      | 0010 101s ffff | ffff | None      | 3     |  |

| SUBWF     | f,d   | Subtract WREG from f                  | 1      | 0000 010d ffff | ffff | OV,C,DC,Z | 1     |  |

| SUBWFB    | f,d   | Subtract WREG from f with Borrow      | 1      | 0000 001d ffff | ffff | OV,C,DC,Z | 1     |  |

| SWAPF     | f,d   | Swap f                                | 1      | 0001 110d ffff | ffff | None      |       |  |

| TABLRD    | t,i,f | Table Read                            | 2 (3)  | 1010 10ti ffff | ffff | None      | 7     |  |

Legend: Refer to Table 15-1 for opcode field descriptions.

- Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- 5: Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

# PIC17C4X

| BTF          | SS                                                    | Bit Test,                                                    | skip if Se                                                                                                                                                                                                                                                                | t      |      |  |  |  |  |

|--------------|-------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--|--|--|--|

| Synt         | tax:                                                  | [ <i>label</i> ] E                                           | [label] BTFSS f,b                                                                                                                                                                                                                                                         |        |      |  |  |  |  |

| Ope          | rands:                                                |                                                              | $0 \le f \le 127$                                                                                                                                                                                                                                                         |        |      |  |  |  |  |

|              |                                                       | 0≤b<7                                                        |                                                                                                                                                                                                                                                                           |        |      |  |  |  |  |

| Ope          | ration:                                               | skip if (f<                                                  | b>) = 1                                                                                                                                                                                                                                                                   |        |      |  |  |  |  |

| Stat         | us Affected:                                          | None                                                         |                                                                                                                                                                                                                                                                           |        |      |  |  |  |  |

| Enc          | oding:                                                | 1001                                                         | 0bbb                                                                                                                                                                                                                                                                      | ffff   | ffff |  |  |  |  |

| Description: |                                                       | instruction<br>If bit 'b' is f<br>fetched du<br>cution, is c | If bit 'b' in register 'f' is 1 then the next<br>instruction is skipped.<br>If bit 'b' is 1, then the next instruction<br>fetched during the current instruction exe-<br>cution, is discarded and an NOP is exe-<br>cuted instead, making this a two-cycle<br>instruction |        |      |  |  |  |  |

| Wor          | ds:                                                   | 1                                                            |                                                                                                                                                                                                                                                                           |        |      |  |  |  |  |

| Cycl         | les:                                                  | 1(2)                                                         |                                                                                                                                                                                                                                                                           |        |      |  |  |  |  |

| QC           | ycle Activity:                                        |                                                              |                                                                                                                                                                                                                                                                           |        |      |  |  |  |  |

|              | Q1                                                    | Q2                                                           | Q3                                                                                                                                                                                                                                                                        |        | Q4   |  |  |  |  |

|              | Decode                                                | Read<br>register 'f'                                         | Execu                                                                                                                                                                                                                                                                     | ite    | NOP  |  |  |  |  |

| lf sk        | ip:                                                   |                                                              |                                                                                                                                                                                                                                                                           | · · ·  |      |  |  |  |  |

|              | Q1                                                    | Q2                                                           | Q3                                                                                                                                                                                                                                                                        |        | Q4   |  |  |  |  |

|              | Forced NOP                                            | NOP                                                          | Execu                                                                                                                                                                                                                                                                     | ıte    | NOP  |  |  |  |  |

| <u>Exa</u>   | <u>mple</u> :                                         | HERE<br>FALSE<br>TRUE                                        | BTFSS<br>:<br>:                                                                                                                                                                                                                                                           | FLAG,1 |      |  |  |  |  |

|              | Before Instru<br>PC                                   |                                                              | ddress (HE                                                                                                                                                                                                                                                                | RE)    |      |  |  |  |  |

|              | After Instructi<br>If FLAG<7<br>PC<br>If FLAG<7<br>PC | > = 0;<br>= ac<br> > = 1;                                    | ddress (FA                                                                                                                                                                                                                                                                |        |      |  |  |  |  |

| BTG                 | Bit Togg                           | Bit Toggle f             |            |                   |  |  |  |  |  |

|---------------------|------------------------------------|--------------------------|------------|-------------------|--|--|--|--|--|

| Syntax:             | [ label ]                          | [ <i>label</i> ] BTG f,b |            |                   |  |  |  |  |  |

| Operands:           | 0 ≤ f ≤ 25<br>0 ≤ b < 7            |                          |            |                   |  |  |  |  |  |

| Operation:          | $(\overline{f} < b >) \rightarrow$ | → (f <b>)</b>            |            |                   |  |  |  |  |  |

| Status Affected     | : None                             |                          |            |                   |  |  |  |  |  |

| Encoding:           | 0011                               | 1bbb                     | ffff       | ffff              |  |  |  |  |  |

| Description:        | Bit 'b' in d<br>inverted.          | ata memory               | location ' | f' is             |  |  |  |  |  |

| Words:              | 1                                  |                          |            |                   |  |  |  |  |  |

| Cycles:             | 1                                  |                          |            |                   |  |  |  |  |  |

| Q Cycle Activity    | <b>/</b> :                         |                          |            |                   |  |  |  |  |  |

| Q1                  | Q2                                 | Q3                       |            | Q4                |  |  |  |  |  |

| Decode              | Read<br>register 'f'               | Execut                   | •   ·      | /rite<br>ster 'f' |  |  |  |  |  |

| Example:            | BTG                                | PORTC,                   | 4          |                   |  |  |  |  |  |

| Before Inst<br>PORT |                                    | 0101 <b>[0x7</b> 5       | 5]         |                   |  |  |  |  |  |

| After Instru        |                                    | 0101 <b>[0x6</b> 5       | -1         |                   |  |  |  |  |  |

# Applicable Devices 42 R42 42A 43 R43 44

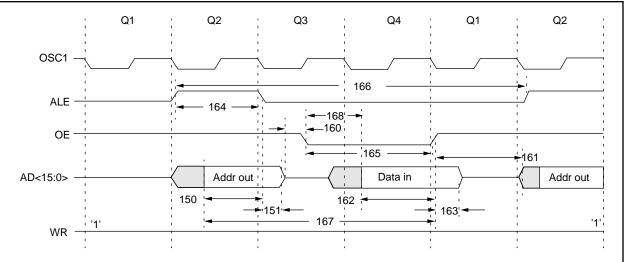

## FIGURE 17-12: MEMORY INTERFACE READ TIMING

| Parameter<br>No. | Sym      | Characteristic                                           | Min           | Тур†      | Max          | Units | Conditions |

|------------------|----------|----------------------------------------------------------|---------------|-----------|--------------|-------|------------|

| 150              | TadV2alL | AD<15:0> (address) valid to ALE↓<br>(address setup time) | 0.25Tcy - 30  |           | _            | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)          | 5*            |           | _            | ns    |            |

| 160              | TadZ2oeL | AD<15:0> high impedance to $\overline{OE}\downarrow$     | 0*            | _         | —            | ns    |            |

| 161              | ToeH2adD | OE↑ to AD<15:0> driven                                   | 0.25Tcy - 15  | _         | _            | ns    |            |

| 162              | TadV2oeH | Data in valid before OE↑<br>(data setup time)            | 35            | _         | _            | ns    |            |

| 163              | ToeH2adl | OE to data in invalid (data hold time)                   | 0             | _         | _            | ns    |            |

| 164              | TalH     | ALE pulse width                                          | —             | 0.25Tcy § | —            | ns    |            |

| 165              | ToeL     | OE pulse width                                           | 0.5Tcy - 35 § | _         | _            | ns    |            |

| 166              | TalH2alH | ALE <sup>↑</sup> to ALE <sup>↑</sup> (cycle time)        | —             | TCY §     | —            | ns    |            |

| 167              | Tacc     | Address access time                                      | —             | _         | 0.75 Tcy-40  | ns    |            |

| 168              | Тое      | Output enable access time<br>(OE low to Data Valid)      | -             | _         | 0.5 TCY - 60 | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification guaranteed by design.

| Applicable Devices | 42 | R42 | 42A | 43 | R43 | 44 |

|--------------------|----|-----|-----|----|-----|----|

|                    |    |     |     |    |     |    |

| DC CHARA  | CTERI | STICS                                                 | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature |           |           |         |                                                          |  |  |

|-----------|-------|-------------------------------------------------------|----------------------------------------------------------------------------------|-----------|-----------|---------|----------------------------------------------------------|--|--|

|           |       |                                                       | _                                                                                |           |           |         | ≤ +40°C                                                  |  |  |

|           |       |                                                       | Operating v                                                                      | oltage VD | D range a | as desc | ribed in Section 19.1                                    |  |  |

| Parameter |       |                                                       |                                                                                  |           |           |         |                                                          |  |  |

| No.       | Sym   | Characteristic                                        | Min                                                                              | Typ†      | Max       | Units   | Conditions                                               |  |  |

|           |       | Internal Program Memory<br>Programming Specs (Note 4) |                                                                                  |           |           |         |                                                          |  |  |

| D110      | VPP   | Voltage on MCLR/VPP pin                               | 12.75                                                                            | _         | 13.25     | V       | Note 5                                                   |  |  |

| D111      | Vddp  | Supply voltage during                                 | 4.75                                                                             | 5.0       | 5.25      | V       |                                                          |  |  |

| D112      | IPP   | Current into MCLR/VPP pin                             | _                                                                                | 25 ‡      | 50 ‡      | mA      |                                                          |  |  |

| D113      | Iddp  | Supply current during programming                     | -                                                                                | -         | 30 ‡      | mA      |                                                          |  |  |

| D114      | TPROG | Programming pulse width                               | 10                                                                               | 100       | 1000      | μs      | Terminated via internal/<br>external interrupt or a rese |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

Note: When using the Table Write for internal programming, the device temperature must be less than 40°C.

# PIC17C4X

# Applicable Devices 42 R42 42A 43 R43 44

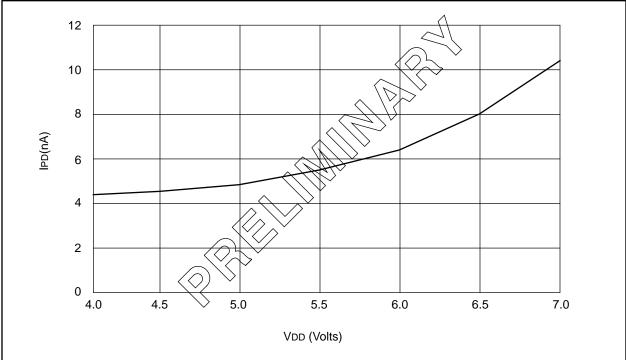

# FIGURE 20-9: TYPICAL IPD vs. VDD WATCHDOG DISABLED 25°C

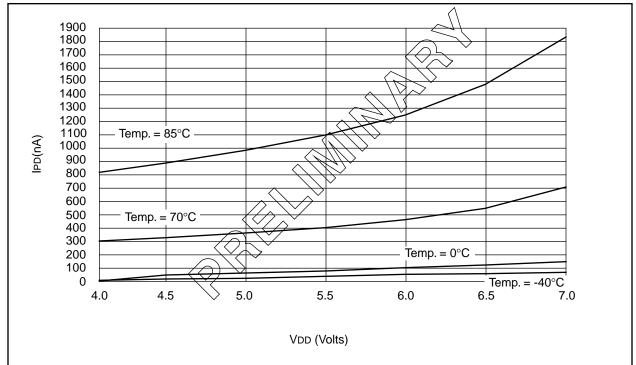

FIGURE 20-10: MAXIMUM IPD vs. VDD WATCHDOG DISABLED

# PIC17C4X

| Figure 19-2:    | External Clock Timing 184                |

|-----------------|------------------------------------------|

| Figure 19-3:    | CLKOUT and I/O Timing 185                |

| Figure 19-4:    | Reset, Watchdog Timer,                   |

| riguio 10 4.    | Oscillator Start-Up Timer, and           |

|                 |                                          |

|                 | Power-Up Timer Timing                    |

| Figure 19-5:    | Timer0 Clock Timings 187                 |

| Figure 19-6:    | Timer1, Timer2, and Timer3 Clock         |

|                 | Timings 187                              |