Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 33MHz                                                                       |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 4KB (2K x 16)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                |                                                                             |

| RAM Size                   | 232 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

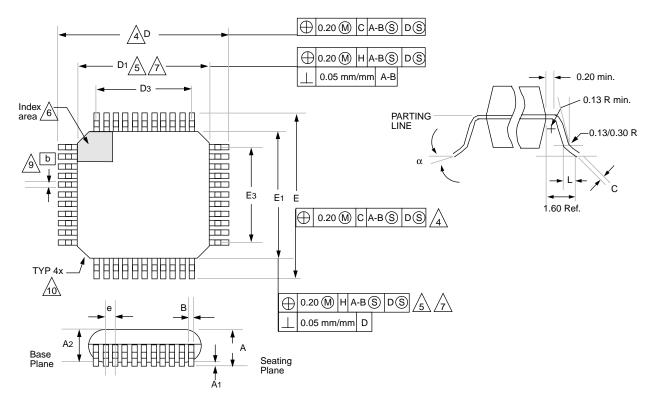

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c42at-33i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PIC17CXX FAMILY OF DEVICES

| Features                    |          | PIC17C42             | PIC17CR42            | PIC17C42A            | PIC17C43             | PIC17CR43            | PIC17C44             |

|-----------------------------|----------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Maximum Frequency of O      | peration | 25 MHz               | 33 MHz               |

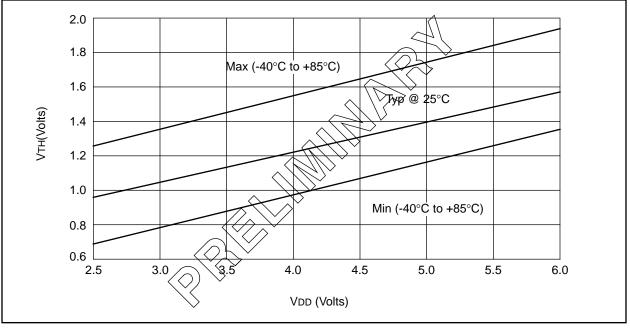

| Operating Voltage Range     |          | 4.5 - 5.5V           | 2.5 - 6.0V           |

| Program Memory x16          | (EPROM)  | 2K                   | -                    | 2K                   | 4K                   | -                    | 8K                   |

|                             | (ROM)    | -                    | 2K                   | -                    | -                    | 4K                   | -                    |

| Data Memory (bytes)         |          | 232                  | 232                  | 232                  | 454                  | 454                  | 454                  |

| Hardware Multiplier (8 x 8) |          | -                    | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer0 (16-bit + 8-bit post | scaler)  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer1 (8-bit)              |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer2 (8-bit)              |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Timer3 (16-bit)             |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Capture inputs (16-bit)     |          | 2                    | 2                    | 2                    | 2                    | 2                    | 2                    |

| PWM outputs (up to 10-bit   | t)       | 2                    | 2                    | 2                    | 2                    | 2                    | 2                    |

| USART/SCI                   |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Power-on Reset              |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Watchdog Timer              |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| External Interrupts         |          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Interrupt Sources           |          | 11                   | 11                   | 11                   | 11                   | 11                   | 11                   |

| Program Memory Code P       | rotect   | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| I/O Pins                    |          | 33                   | 33                   | 33                   | 33                   | 33                   | 33                   |

| I/O High Current Capabil-   | Source   | 25 mA                |

| ity                         | Sink     | 25 mA <sup>(1)</sup> |

| Package Types               |          | 40-pin DIP           |

|                             |          | 44-pin PLCC          |

|                             |          | 44-pin MQFP          |

|                             |          |                      | 44-pin TQFP          |

Note 1: Pins RA2 and RA3 can sink up to 60 mA.

| Addr                                                        | Unbanked                                                                                  |                                                        |                                                           |                                                               |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|

| 00h                                                         | INDF0                                                                                     |                                                        |                                                           |                                                               |

| 01h                                                         | FSR0                                                                                      |                                                        |                                                           |                                                               |

| 02h                                                         | PCL                                                                                       |                                                        |                                                           |                                                               |

| 03h                                                         | PCLATH                                                                                    |                                                        |                                                           |                                                               |

| 04h                                                         | ALUSTA                                                                                    |                                                        |                                                           |                                                               |

| 05h                                                         | TOSTA                                                                                     |                                                        |                                                           |                                                               |

| 06h                                                         | CPUSTA                                                                                    |                                                        |                                                           |                                                               |

| 07h                                                         | INTSTA                                                                                    |                                                        |                                                           |                                                               |

| 08h                                                         | INDF1                                                                                     |                                                        |                                                           |                                                               |

| 09h                                                         | FSR1                                                                                      |                                                        |                                                           |                                                               |

| 0Ah                                                         | WREG                                                                                      |                                                        |                                                           |                                                               |

| 0Bh                                                         | TMR0L                                                                                     |                                                        |                                                           |                                                               |

| 0Ch                                                         | TMR0H                                                                                     |                                                        |                                                           |                                                               |

| 0Dh                                                         | TBLPTRL                                                                                   |                                                        |                                                           |                                                               |

| 0Eh                                                         | TBLPTRH                                                                                   |                                                        |                                                           |                                                               |

| 0Fh                                                         | BSR                                                                                       |                                                        |                                                           |                                                               |

| 1                                                           |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | Bank 0                                                                                    | Bank 1 <sup>(1)</sup>                                  | Bank 2 <sup>(1)</sup>                                     | Bank 3 <sup>(1)</sup>                                         |

| 10h                                                         | Bank 0<br>PORTA                                                                           | Bank 1 <sup>(1)</sup><br>DDRC                          | Bank 2 <sup>(1)</sup><br>TMR1                             | Bank 3 <sup>(1)</sup><br>PW1DCL                               |

| 10h<br>11h                                                  |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | PORTA                                                                                     | DDRC                                                   | TMR1                                                      | PW1DCL                                                        |

| 11h                                                         | PORTA<br>DDRB                                                                             | DDRC<br>PORTC                                          | TMR1<br>TMR2                                              | PW1DCL<br>PW2DCL                                              |

| 11h<br>12h                                                  | PORTA<br>DDRB<br>PORTB                                                                    | DDRC<br>PORTC<br>DDRD                                  | TMR1<br>TMR2<br>TMR3L                                     | PW1DCL<br>PW2DCL<br>PW1DCH                                    |

| 11h<br>12h<br>13h                                           | PORTA<br>DDRB<br>PORTB<br>RCSTA                                                           | DDRC<br>PORTC<br>DDRD<br>PORTD                         | TMR1<br>TMR2<br>TMR3L<br>TMR3H                            | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH                          |

| 11h<br>12h<br>13h<br>14h                                    | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG                                                  | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE                 | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1                     | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L                  |

| 11h<br>12h<br>13h<br>14h<br>15h                             | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA                                         | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE        | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2              | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H          |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h                      | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h               | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h        | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

# FIGURE 6-5: PIC17C42 REGISTER FILE MAP

Note 1: SFR file locations 10h - 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

#### FIGURE 6-6: PIC17CR42/42A/43/R43/44 REGISTER FILE MAP

| Addr | Unbanked           |                       |                       |                       |

|------|--------------------|-----------------------|-----------------------|-----------------------|

| 00h  | INDF0              |                       |                       |                       |

| 01h  | FSR0               |                       |                       |                       |

| 02h  | PCL                |                       |                       |                       |

| 03h  | PCLATH             |                       |                       |                       |

| 04h  | ALUSTA             |                       |                       |                       |

| 05h  | TOSTA              |                       |                       |                       |

| 06h  | CPUSTA             |                       |                       |                       |

| 07h  | INTSTA             |                       |                       |                       |

| 08h  | INDF1              |                       |                       |                       |

| 09h  | FSR1               |                       |                       |                       |

| 0Ah  | WREG               |                       |                       |                       |

| 0Bh  | TMR0L              |                       |                       |                       |

| 0Ch  | TMR0H              |                       |                       |                       |

| 0Dh  | TBLPTRL            |                       |                       |                       |

| 0Eh  | TBLPTRH            |                       |                       |                       |

| 0Fh  | BSR                |                       |                       |                       |

|      | Bank 0             | Bank 1 <sup>(1)</sup> | Bank 2 <sup>(1)</sup> | Bank 3 <sup>(1)</sup> |

| 10h  | PORTA              | DDRC                  | TMR1                  | PW1DCL                |

| 11h  | DDRB               | PORTC                 | TMR2                  | PW2DCL                |

| 12h  | PORTB              | DDRD                  | TMR3L                 | PW1DCH                |

| 13h  | RCSTA              | PORTD                 | TMR3H                 | PW2DCH                |

| 14h  | RCREG              | DDRE                  | PR1                   | CA2L                  |

| 15h  | TXSTA              | PORTE                 | PR2                   | CA2H                  |

| 16h  | TXREG              | PIR                   | PR3L/CA1L             | TCON1                 |

| 17h  | SPBRG              | PIE                   | PR3H/CA1H             | TCON2                 |

| 18h  | PRODL              |                       |                       |                       |

| 19h  | PRODH              |                       |                       |                       |

| 1Ah  |                    |                       |                       |                       |

|      |                    |                       |                       |                       |

| 1Fh  |                    |                       | 1                     |                       |

| 20h  | General            | General               |                       |                       |

|      | Purpose            | Purpose               |                       |                       |

|      | RAM <sup>(2)</sup> | RAM (2)               |                       |                       |

|      |                    |                       |                       |                       |

| FFh  |                    |                       |                       |                       |

- Note 1: SFR file locations 10h 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

- 2: General Purpose Registers (GPR) locations 20h - FFh and 120h - 1FFh are banked. All other GPRs ignore the Bank Select Register (BSR) bits.

#### 6.4.1 INDIRECT ADDRESSING REGISTERS

The PIC17C4X has four registers for indirect addressing. These registers are:

- INDF0 and FSR0

- INDF1 and FSR1

Registers INDF0 and INDF1 are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data. The FSR is an 8-bit register and allows addressing anywhere in the 256-byte data memory address range. For banked memory, the bank of memory accessed is specified by the value in the BSR.

If file INDF0 (or INDF1) itself is read indirectly via an FSR, all '0's are read (Zero bit is set). Similarly, if INDF0 (or INDF1) is written to indirectly, the operation will be equivalent to a NOP, and the status bits are not affected.

#### 6.4.2 INDIRECT ADDRESSING OPERATION

The indirect addressing capability has been enhanced over that of the PIC16CXX family. There are two control bits associated with each FSR register. These two bits configure the FSR register to:

- Auto-decrement the value (address) in the FSR after an indirect access

- Auto-increment the value (address) in the FSR after an indirect access

- No change to the value (address) in the FSR after an indirect access

These control bits are located in the ALUSTA register. The FSR1 register is controlled by the FS3:FS2 bits and FSR0 is controlled by the FS1:FS0 bits.

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the ALUSTA register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

If the FSR register contains a value of 0h, an indirect read will read 0h (Zero bit is set) while an indirect write will be equivalent to a NOP (status bits are not affected).

Indirect addressing allows single cycle data transfers within the entire data space. This is possible with the use of the MOVPF and MOVFP instructions, where either 'p' or 'f' is specified as INDF0 (or INDF1).

If the source or destination of the indirect address is in banked memory, the location accessed will be determined by the value in the BSR. A simple program to clear RAM from 20h - FFh is shown in Example 6-1.

#### EXAMPLE 6-1: INDIRECT ADDRESSING

|    | MOVLW  | 0x20        | ;           |           |

|----|--------|-------------|-------------|-----------|

|    | MOVWF  | FSR0        | ; FSR0 = 20 | h         |

|    | BCF    | ALUSTA, FS1 | ; Increment | FSR       |

|    | BSF    | ALUSTA, FSO | ; after acc | ess       |

|    | BCF    | ALUSTA, C   | ; C = 0     |           |

|    | MOVLW  | END_RAM + 1 | ;           |           |

| LP | CLRF   | INDF0       | ; Addr(FSR) | = 0       |

|    | CPFSEQ | FSR0        | ; FSRO = EN | ID_RAM+1? |

|    | GOTO   | LP          | ; NO, clear | next      |

|    | :      |             | ; YES, All  | RAM is    |

|    | :      |             | ; cleared   |           |

|    |        |             |             |           |

#### 6.5 <u>Table Pointer (TBLPTRL and</u> <u>TBLPTRH)</u>

File registers TBLPTRL and TBLPTRH form a 16-bit pointer to address the 64K program memory space. The table pointer is used by instructions TABLWT and TABLRD.

The TABLRD and the TABLWT instructions allow transfer of data between program and data space. The table pointer serves as the 16-bit address of the data word within the program memory. For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 7.0.

#### 6.6 <u>Table Latch (TBLATH, TBLATL)</u>

The table latch (TBLAT) is a 16-bit register, with TBLATH and TBLATL referring to the high and low bytes of the register. It is not mapped into data or program memory. The table latch is used as a temporary holding latch during data transfer between program and data memory (see descriptions of instructions TABLRD, TABLWT, TLRD and TLWT). For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 7.0.

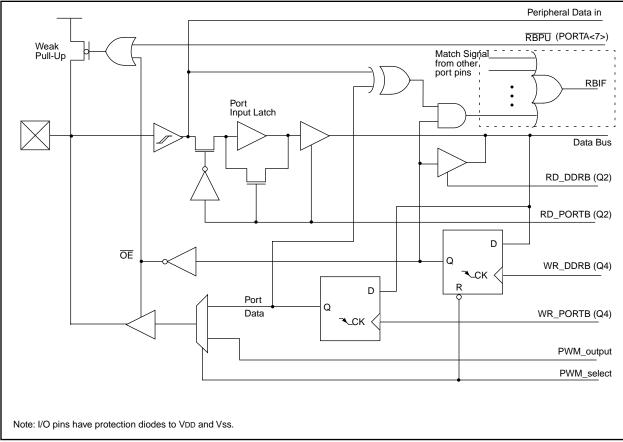

## 9.0 I/O PORTS

The PIC17C4X devices have five I/O ports, PORTA through PORTE. PORTB through PORTE have a corresponding Data Direction Register (DDR), which is used to configure the port pins as inputs or outputs. These five ports are made up of 33 I/O pins. Some of these ports pins are multiplexed with alternate functions.

PORTC, PORTD, and PORTE are multiplexed with the system bus. These pins are configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, these pins are general purpose I/O.

PORTA and PORTB are multiplexed with the peripheral features of the device. These peripheral features are:

- Timer modules

- Capture module

- PWM module

- USART/SCI module

- External Interrupt pin

When some of these peripheral modules are turned on, the port pin will automatically configure to the alternate function. The modules that do this are:

- PWM module

- USART/SCI module

When a pin is automatically configured as an output by a peripheral module, the pins data direction (DDR) bit is unknown. After disabling the peripheral module, the user should re-initialize the DDR bit to the desired configuration.

The other peripheral modules (which require an input) must have their data direction bit configured appropriately.

**Note:** A pin that is a peripheral input, can be configured as an output (DDRx<y> is cleared). The peripheral events will be determined by the action output on the port pin.

#### 9.1 PORTA Register

PORTA is a 6-bit wide latch. PORTA does not have a corresponding Data Direction Register (DDR).

Reading PORTA reads the status of the pins.

The RA1 pin is multiplexed with TMR0 clock input, and RA4 and RA5 are multiplexed with the USART functions. The control of RA4 and RA5 as outputs is automatically configured by the USART module.

9.1.1 USING RA2, RA3 AS OUTPUTS

The RA2 and RA3 pins are open drain outputs. To use the RA2 or the RA3 pin(s) as output(s), simply write to the PORTA register the desired value. A '0' will cause the pin to drive low, while a '1' will cause the pin to float (hi-impedance). An external pull-up resistor should be used to pull the pin high. Writes to PORTA will not affect the other pins.

| Note: | When using the RA2 or RA3 pin(s) as out-<br>put(s), read-modify-write instructions (such<br>as BCF, BSF, BTG) on PORTA are not rec-<br>ommended.<br>Such operations read the port pins, do the<br>desired operation, and then write this value<br>to the data latch. This may inadvertently<br>cause the RA2 or RA3 pins to switch from<br>input to output (or vice-versa).<br>It is recommended to use a shadow regis-<br>ter for PORTA. Do the bit operations on this<br>shadow register and then move it to<br>PORTA. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

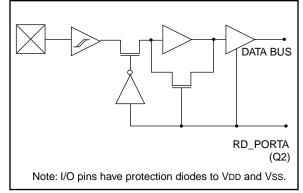

#### FIGURE 9-1: RA0 AND RA1 BLOCK DIAGRAM

#### FIGURE 9-5: BLOCK DIAGRAM OF RB3 AND RB2 PORT PINS

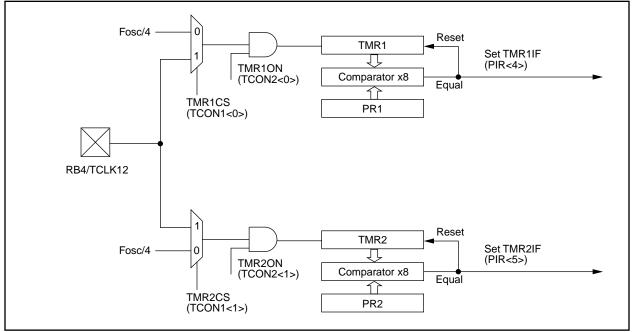

#### 12.1 <u>Timer1 and Timer2</u>

#### 12.1.1 TIMER1, TIMER2 IN 8-BIT MODE

Both Timer1 and Timer2 will operate in 8-bit mode when the T16 bit is clear. These two timers can be independently configured to increment from the internal instruction cycle clock or from an external clock source on the RB4/TCLK12 pin. The timer clock source is configured by the TMRxCS bit (x = 1 for Timer1 or = 2 for Timer2). When TMRxCS is clear, the clock source is internal and increments once every instruction cycle (Fosc/4). When TMRxCS is set, the clock source is the RB4/TCLK12 pin, and the timer will increment on every falling edge of the RB4/TCLK12 pin.

The timer increments from 00h until it equals the Period register (PRx). It then resets to 00h at the next increment cycle. The timer interrupt flag is set when the timer is reset. TMR1 and TMR2 have individual interrupt flag bits. The TMR1 interrupt flag bit is latched into TMR1IF, and the TMR2 interrupt flag bit is latched into TMR2IF.

Each timer also has a corresponding interrupt enable bit (TMRxIE). The timer interrupt can be enabled by setting this bit and disabled by clearing this bit. For peripheral interrupts to be enabled, the Peripheral Interrupt Enable bit must be enabled (PEIE is set) and global interrupts must be enabled (GLINTD is cleared).

The timers can be turned on and off under software control. When the Timerx On control bit (TMRxON) is set, the timer increments from the clock source. When TMRxON is cleared, the timer is turned off and cannot cause the timer interrupt flag to be set.

#### 12.1.1.1 EXTERNAL CLOCK INPUT FOR TIMER1 OR TIMER2

When TMRxCS is set, the clock source is the RB4/TCLK12 pin, and the timer will increment on every falling edge on the RB4/TCLK12 pin. The TCLK12 input is synchronized with internal phase clocks. This causes a delay from the time a falling edge appears on TCLK12 to the time TMR1 or TMR2 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

#### FIGURE 12-3: TIMER1 AND TIMER2 IN TWO 8-BIT TIMER/COUNTER MODE

#### 13.4 USART Synchronous Slave Mode

The synchronous slave mode differs from the master mode in the fact that the shift clock is supplied externally at the RA5/TX/CK pin (instead of being supplied internally in the master mode). This allows the device to transfer or receive data in the SLEEP mode. The slave mode is entered by clearing the CSRC (TXSTA<7>) bit.

#### 13.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the sync master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to TXREG and then the SLEEP instruction executes, the following will occur. The first word will immediately transfer to the TSR and will transmit as the shift clock is supplied. The second word will remain in TXREG. TXIF will not be set. When the first word has been shifted out of TSR, TXREG will transfer the second word to the TSR and the TXIF flag will now be set. If TXIE is enabled, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, then the program will branch to interrupt vector (0020h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting the SYNC and SPEN bits and clearing the CSRC bit.

- 2. Clear the CREN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. Start transmission by loading data to TXREG.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 7. Enable the transmission by setting TXEN.

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the reverse order.

# 13.4.2 USART SYNCHRONOUS SLAVE RECEPTION

Operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode. Also, SREN is a don't care in slave mode.

If receive is enabled (CREN) prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR will transfer the data to RCREG (setting RCIF) and if the RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0020h).

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting the SYNC and SPEN bits and clearing the CSRC bit.

- 2. If interrupts are desired, then set the RCIE bit.

- 3. If 9-bit reception is desired, then set the RX9 bit.

- 4. To enable reception, set the CREN bit.

- 5. The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- 6. Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading RCREG.

- 8. If any error occurred, clear the error by clearing the CREN bit.

Note: To abort reception, either clear the SPEN bit, the SREN bit (when in single receive mode), or the CREN bit (when in continuous receive mode). This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

#### 14.4.2 MINIMIZING CURRENT CONSUMPTION

To minimize current consumption, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should be at VDD or VSS. The contributions from on-chip pull-ups on PORTB should also be considered, and disabled when possible.

#### 14.5 <u>Code Protection</u>

The code in the program memory can be protected by selecting the microcontroller in code protected mode (PM2:PM0 = '000').

| Note: | PM2 d  | oes not | exist on th | e PIC17C42. To  |

|-------|--------|---------|-------------|-----------------|

|       | select | code    | protected   | microcontroller |

|       |        |         | 10 = 00'.   |                 |

In this mode, instructions that are in the on-chip program memory space, can continue to read or write the program memory. An instruction that is executed outside of the internal program memory range will be inhibited from writing to or reading from program memory.

**Note:** Microchip does not recommend code protecting windowed devices.

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| MOVFP                        | Move f to                 | р                                 |                                                                         | MOVLB                    | Move Lite                             | eral to low i       | nibble in BSR                 |

|------------------------------|---------------------------|-----------------------------------|-------------------------------------------------------------------------|--------------------------|---------------------------------------|---------------------|-------------------------------|

| Syntax:                      | [ <i>label</i> ] N        | IOVFP f,p                         |                                                                         | Syntax:                  | [ label ]                             | MOVLB k             |                               |

| Operands:                    | 0 ≤ f ≤ 255               | 5                                 |                                                                         | Operands:                | $0 \le k \le 15$                      | 5                   |                               |

|                              | $0 \le p \le 31$          |                                   |                                                                         | Operation:               | k  ightarrow (BSR                     | (<3:0>)             |                               |

| Operation:                   | $(f) \to (p)$             |                                   |                                                                         | Status Affected:         | None                                  |                     |                               |

| Status Affected:             | None                      |                                   |                                                                         | Encoding:                | 1011                                  | 1000 ui             | uuu kkkk                      |

| Encoding:                    | 011p                      | pppp ff                           | ff ffff                                                                 | Description:             | The four bi                           | t literal 'k' is lo | baded in the                  |

| Description:                 | to data mer<br>can be any | mory location '<br>where in the 2 | nory location 'f'<br>p'. Location 'f'<br>56 word data<br>'p' can be 00h |                          | low 4-bits of are affected is unchang | of the Bank Se      |                               |

|                              |                           | 'f' can be WR                     | EG (a useful                                                            | Words:                   | 1                                     |                     |                               |

|                              | special situ              | ,                                 | ful for transfer-                                                       | Cycles:                  | 1                                     |                     |                               |

|                              |                           |                                   | on to a periph-                                                         | Q Cycle Activity:        |                                       |                     |                               |

|                              |                           |                                   | transmit buffer                                                         | Q1                       | Q2                                    | Q3                  | Q4                            |

|                              | indirectly a              | ort). Both 'f' an<br>ddressed.    | d p can be                                                              | Decode                   | Read                                  | Execute             | Write literal                 |

| Words:                       | 1                         |                                   |                                                                         |                          | literal 'u:k'                         |                     | 'k' to<br>BSR<3:0>            |

| Cycles:                      | 1                         |                                   |                                                                         | Example:                 | MOVLB                                 | 0x5                 |                               |

| Q Cycle Activity             | :                         |                                   |                                                                         | Before Instru            | uction                                |                     |                               |

| Q1                           | Q2                        | Q3                                | Q4                                                                      | BSR reg                  | ister = 0x                            | :22                 |                               |

| Decode                       | Read<br>register 'f'      | Execute                           | Write<br>register 'p'                                                   | After Instruc<br>BSR reg |                                       | :25                 |                               |

| Example:                     | MOVFP I                   | REG1, REG2                        |                                                                         | Note: For th             | ne PIC17C42                           | 2, only the lo      | ow four bits of               |

| Before Insti<br>REG1<br>REG2 |                           | 33,<br>11                         |                                                                         |                          | BSR registe<br>ed. The uppe           |                     | sically imple-<br>ead as '0'. |

| After Instru<br>REG1         |                           | 33,                               |                                                                         |                          |                                       |                     |                               |

REG2

0x33

=

| SLEEP                                         | Enter SI                                                                                                                            | EEP mod                                                                          | de                               |                                              |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------|----------------------------------------------|--|

| Syntax:                                       | [ label ]                                                                                                                           | SLEEP                                                                            |                                  |                                              |  |

| Operands:                                     | None                                                                                                                                | None                                                                             |                                  |                                              |  |

| Operation:                                    | $\begin{array}{l} 00h \rightarrow W \\ 0 \rightarrow WD \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow \overline{PD} \end{array}$ | /DT;<br>T postsca                                                                | ler;                             |                                              |  |

| Status Affected                               | I: TO, PD                                                                                                                           |                                                                                  |                                  |                                              |  |

| Encoding:                                     | 0000                                                                                                                                | 0000                                                                             | 0000                             | 0011                                         |  |

| Description:                                  | cleared. T<br>set. Watch<br>are cleare<br>The proce                                                                                 | r down stat<br>he time-out<br>ndog Timer<br>nd.<br>essor is put<br>n the oscilla | t status I<br>and its<br>into SL | bit ( <del>TO</del> ) is<br>prescaler<br>EEP |  |

| Words:                                        | 1                                                                                                                                   |                                                                                  |                                  |                                              |  |

| Cycles:                                       | 1                                                                                                                                   |                                                                                  |                                  |                                              |  |

| Q Cycle Activit                               | y:                                                                                                                                  |                                                                                  |                                  |                                              |  |

| Q1                                            | Q2                                                                                                                                  | Q3                                                                               |                                  | Q4                                           |  |

| Decode                                        | Read<br>register<br>PCLATH                                                                                                          | Execute                                                                          | e                                | NOP                                          |  |

| Example:                                      | SLEEP                                                                                                                               |                                                                                  |                                  |                                              |  |

| Before Ins<br>TO =<br>PD =                    | ?                                                                                                                                   |                                                                                  |                                  |                                              |  |

| After Instru<br>TO =<br>PD =<br>† If WDT caus | uction<br>1 †<br>0<br>ses wake-up, t                                                                                                | his bit is c                                                                     | leared                           |                                              |  |

† If WDT causes wake-up, this bit is cleared

| SUE        | BLW                                                  | S                   | Subtr                                                                                  | act  | WREG                     | from    | ı Lit | teral            |

|------------|------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------|------|--------------------------|---------|-------|------------------|

| Synt       | tax:                                                 | [                   | [ <i>label</i> ] SUBLW k                                                               |      |                          |         |       |                  |

| Ope        | rands:                                               | 0                   | $0 \le k \le 255$                                                                      |      |                          |         |       |                  |

| Ope        | ration:                                              | k                   | – (V                                                                                   | VRE  | $\Xi G) \rightarrow (N)$ | VRE     | G)    |                  |

| Stat       | us Affected:                                         | C                   | OV, C, DC, Z                                                                           |      |                          |         |       |                  |

| Enc        | oding:                                               | Γ                   | 101                                                                                    | 1    | 0010                     | kkł     | k     | kkkk             |

| Des        | cription:                                            | li                  | WREG is subtracted from the eight bir<br>literal 'k'. The result is placed in<br>WREG. |      |                          |         |       |                  |

| Words:     |                                                      | 1                   |                                                                                        |      |                          |         |       |                  |

| Cycl       | les:                                                 | 1                   |                                                                                        |      |                          |         |       |                  |

| QC         | ycle Activity:                                       |                     |                                                                                        |      |                          |         |       |                  |

|            | Q1                                                   |                     | Q2                                                                                     |      | Q3                       |         |       | Q4               |

|            | Decode                                               | -                   | Read<br>eral 'k                                                                        | ۲'   | Execu                    | ite     |       | Vrite to<br>WREG |

| Exa        | <u>mple 1</u> :                                      | S                   | UBLW                                                                                   | 1 (  | Ox02                     |         |       |                  |

|            | Before Instru<br>WREG<br>C<br>After Instruct<br>WREG | =<br>=              | ר<br>1<br>?<br>1                                                                       |      |                          |         |       |                  |

| <u>Exa</u> | C<br>Z<br>mple <u>2</u> :                            | =                   | 1<br>0                                                                                 | ; re | esult is po              | ositive |       |                  |

|            | Before Instru<br>WREG<br>C                           | ictior<br>=<br>=    | ר<br>2<br>?                                                                            |      |                          |         |       |                  |

| <u>Exa</u> | After Instruct<br>WREG<br>C<br>Z<br>mple <u>3</u> :  | tion<br>=<br>=<br>= | 0<br>1<br>1                                                                            | ; re | esult is ze              | ero     |       |                  |

|            | Before Instru<br>WREG<br>C                           | ictior<br>=<br>=    | ר<br>3<br>?                                                                            |      |                          |         |       |                  |

|            | After Instruct<br>WREG<br>C<br>Z                     | tion<br>=<br>=<br>= | FF<br>0<br>1                                                                           |      | 's comple<br>esult is ne |         | ·     |                  |

| TABLRD            | Table R     | ead      |           |

|-------------------|-------------|----------|-----------|

| Example1:         | TABLRD      | 1, 1,    | REG ;     |

| Before Instruc    | ction       |          |           |

| REG               |             | =        | 0x53      |

| TBLATH            |             | =        | 0xAA      |

| TBLATL            |             | =        | 0x55      |

| TBLPTR            |             | =        |           |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

| After Instruction | on (table v | write co | mpletion) |

| REG               |             | =        | 0xAA      |

| TBLATH            |             | =        | 0x12      |

| TBLATL            |             | =        | 0x34      |

| TBLPTR            |             |          | 0xA357    |

| MEMORY            | (TBLPTR)    | =        | 0x5678    |

| Example2:         | TABLRD      | 0, 0,    | REG ;     |

| Before Instruc    | ction       |          |           |

| REG               |             | =        | 0x53      |

| TBLATH            |             | =        | 0xAA      |

| TBLATL            |             | =        | 0x55      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

| After Instruction | on (table v | write co | mpletion) |

| REG               |             | =        | 0x55      |

| TBLATH            |             | =        | 0x12      |

| TBLATL            |             | =        | 0x34      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

|                   |             |          |           |

|                   |             |          |           |

|                   |             |          |           |

|                   |             |          |           |

|                   |             |          |           |

| TABLWT                                       | Table Write                                                                                                                                      |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                      | [label] TABLWT t,i,f                                                                                                                             |

| Operands:                                    | 0 ≤ f ≤ 255<br>i ∈ [0,1]<br>t ∈ [0,1]                                                                                                            |

| Operation:                                   | $f \in [0, 1]$<br>If $f = 0$ ,                                                                                                                   |

| e per au e m                                 | $f \rightarrow TBLATL;$                                                                                                                          |

|                                              | If t = 1,<br>f $\rightarrow$ TBLATH;                                                                                                             |

|                                              | TBLAT $\rightarrow$ Prog Mem (TBLPTF                                                                                                             |

|                                              | If i = 1,<br>TBLPTR + 1 $\rightarrow$ TBLPTR                                                                                                     |

| Status Affected:                             | None                                                                                                                                             |

| Encoding:                                    | 1010 11ti ffff ffff                                                                                                                              |

| Description:                                 | 1. Load value in 'f' into 16-bit table                                                                                                           |

|                                              | latch (TBLAT)<br>If t = 0: load into low byte;                                                                                                   |

|                                              | If t = 1: load into high byte                                                                                                                    |

|                                              | 2. The contents of TBLAT is written to the program memory location                                                                               |

|                                              | pointed to by TBLPTR                                                                                                                             |

|                                              | If TBLPTR points to external<br>program memory location, then                                                                                    |

|                                              | the instruction takes two-cycle                                                                                                                  |

|                                              | If TBLPTR points to an internal                                                                                                                  |

|                                              | EPROM location, then the<br>instruction is terminated when                                                                                       |

|                                              | an interrupt is received.                                                                                                                        |

|                                              | LR/VPP pin must be at the programmir<br>for successful programming of intern                                                                     |

| If MCLR                                      | /VPP = VDD                                                                                                                                       |

|                                              | gramming sequence of internal memore<br>executed, but will not be successf                                                                       |

| (althoug                                     | h the internal memory location may b                                                                                                             |

| disturbe                                     | -7                                                                                                                                               |

|                                              | <ol> <li>The TBLPTR can be automati-<br/>cally incremented</li> </ol>                                                                            |

|                                              |                                                                                                                                                  |

|                                              | If i = 0; TBLPTR is not                                                                                                                          |

|                                              | incremented                                                                                                                                      |

| Words:                                       |                                                                                                                                                  |

|                                              | incremented<br>If i = 1; TBLPTR is incremented                                                                                                   |

| Cycles:                                      | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip                                                            |

| Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1 | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip<br>EPROM program memory)<br>Q2 Q3 Q4                       |

| Cycles:<br>Q Cycle Activity:                 | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip<br>EPROM program memory)<br>Q2 Q3 Q4<br>Read Execute Write |

| Cycles:<br>Q Cycle Activity:<br>Q1           | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip<br>EPROM program memory)<br>Q2 Q3 Q4                       |

| TABLWT            | Table Wr    | ite      |         |                |

|-------------------|-------------|----------|---------|----------------|

| Example1:         | TABLWT      | 0, 1,    | REG     |                |

| Before Instruc    | ction       |          |         |                |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA356  |                |

| MEMORY            | (TBLPTR)    | =        | 0xFFFI  | F              |

| After Instruction | on (table v | vrite co | mpletio | n)             |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0x53    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA357  | 7              |

| MEMORY            | (TBLPTR -   | 1) =     | 0x5355  | 5              |

| Example 2:        | TABLWT      | 1, 0,    | REG     |                |

| Before Instruc    | ction       |          |         |                |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA356  | 6              |

| MEMORY            | (TBLPTR)    | =        | 0xFFFI  | F              |

| After Instruction | on (table v | vrite co | mpletio | n)             |

| REG               | ,           | =        | 0x53    | ,              |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x53    |                |

| TBLPTR            |             | =        | 0xA356  | 6              |

| MEMORY            | (TBLPTR)    | =        | 0xAA5   | 3              |

|                   |             |          |         |                |

|                   | <br>ר       |          | г       |                |

| Program<br>Memory | 15          |          | 0       | Data<br>Memory |

|                   |             |          |         | wentory        |

|                   | 1 ( 5       | TBLPTR   |         |                |

|                                       | TBLPTR       |

|---------------------------------------|--------------|

| · · · · · · · · · · · · · · · · · · · |              |

| 16 bits                               | TBLAT 8 bits |

| TLR                   | D                 | Table Late                                                                 | ch Read                                                                                                                                                               |                       |  |  |  |  |

|-----------------------|-------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| Synt                  | ax:               | [label] T                                                                  | [label] TLRD t,f                                                                                                                                                      |                       |  |  |  |  |

| Ope                   | rands:            | $\begin{array}{l} 0 \leq f \leq 255 \\ t \in \left[0,1\right] \end{array}$ |                                                                                                                                                                       |                       |  |  |  |  |

| Ope                   | ration:           | If t = 0,<br>TBLATL $\rightarrow$ f;                                       |                                                                                                                                                                       |                       |  |  |  |  |

|                       |                   | If $t = 1$ ,<br>TBLATH $\rightarrow f$                                     |                                                                                                                                                                       |                       |  |  |  |  |

| Status Affected: None |                   |                                                                            |                                                                                                                                                                       |                       |  |  |  |  |

| Enco                  | oding:            | 1010                                                                       | 1010 00tx ffff ffff                                                                                                                                                   |                       |  |  |  |  |

| Deso                  | cription:         | (TBLAT) into<br>is unaffecte<br>If t = 1; high                             | Read data from 16-bit table latch<br>(TBLAT) into file register 'f'. Table Latch<br>is unaffected.<br>If $t = 1$ ; high byte is read<br>If $t = 0$ ; low byte is read |                       |  |  |  |  |

|                       |                   | with TABLR                                                                 | tion is used ir<br>□ to transfer c<br>ory to data me                                                                                                                  | lata from pro-        |  |  |  |  |

| Word                  | ds:               | 1                                                                          |                                                                                                                                                                       |                       |  |  |  |  |

| Cycl                  | es:               | 1                                                                          |                                                                                                                                                                       |                       |  |  |  |  |

| QC                    | cle Activity:     |                                                                            |                                                                                                                                                                       |                       |  |  |  |  |

|                       | Q1                | Q2                                                                         | Q3                                                                                                                                                                    | Q4                    |  |  |  |  |

|                       | Decode            | Read<br>register<br>TBLATH or<br>TBLATL                                    | Execute                                                                                                                                                               | Write<br>register 'f' |  |  |  |  |

| <u>Exar</u>           | <u>mple</u> :     | TLRD t                                                                     | , RAM                                                                                                                                                                 |                       |  |  |  |  |

|                       | Before Instru     | iction                                                                     |                                                                                                                                                                       |                       |  |  |  |  |

|                       | t<br>RAM          | = 0<br>= ?                                                                 |                                                                                                                                                                       |                       |  |  |  |  |

|                       | TBLAT             | = ?<br>= 0x00AF                                                            | (TBLATH =<br>(TBLATL =                                                                                                                                                |                       |  |  |  |  |

|                       | After Instruct    | tion                                                                       |                                                                                                                                                                       |                       |  |  |  |  |

|                       | RAM<br>TBLAT      | = 0xAF<br>= 0x00AF                                                         | (TBLATH =<br>(TBLATL =                                                                                                                                                | ,                     |  |  |  |  |

|                       | Before Instru     | iction                                                                     |                                                                                                                                                                       |                       |  |  |  |  |

|                       | t<br>RAM          | = 1<br>= ?                                                                 |                                                                                                                                                                       |                       |  |  |  |  |

|                       | TBLAT             | = ?<br>= 0x00AF                                                            | (TBLATH =<br>(TBLATL =                                                                                                                                                | ,                     |  |  |  |  |

| After Instruction     |                   |                                                                            |                                                                                                                                                                       |                       |  |  |  |  |

|                       | RAM<br>TBLAT      | = 0x00<br>= 0x00AF                                                         | (TBLATH =<br>(TBLATL =                                                                                                                                                | ,                     |  |  |  |  |

|                       | Program<br>Memory | 15                                                                         | 0                                                                                                                                                                     | Data<br>Memory        |  |  |  |  |

|                       |                   |                                                                            |                                                                                                                                                                       |                       |  |  |  |  |

| • - •                 |                   |                                                                            | . (                                                                                                                                                                   | ÷                     |  |  |  |  |

|                       | 16 bits           |                                                                            | BLAT                                                                                                                                                                  | 8 bits                |  |  |  |  |

### Applicable Devices 42 R42 42A 43 R43 44

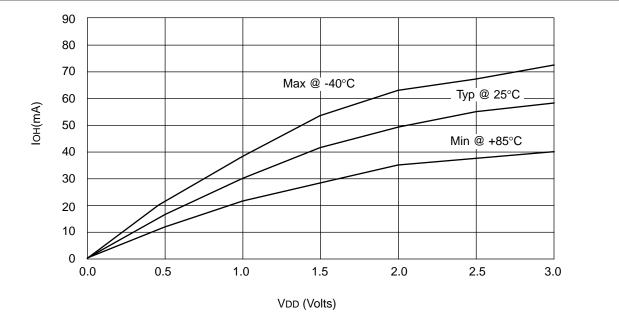

FIGURE 18-16: IOL vs. VOL, VDD = 3V

## Applicable Devices 42 R42 42A 43 R43 44

### FIGURE 18-17: IOL vs. VOL, VDD = 5V

### Applicable Devices 42 R42 42A 43 R43 44

|                                                                                                                    |       |                                                  | Standard C<br>Operating te |                                                      |          | ns (ur                | nless otherwise stated)                                                                                     |

|--------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------|----------------------------|------------------------------------------------------|----------|-----------------------|-------------------------------------------------------------------------------------------------------------|