Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 8KB (4K x 16)                                                           |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 454 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-16-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

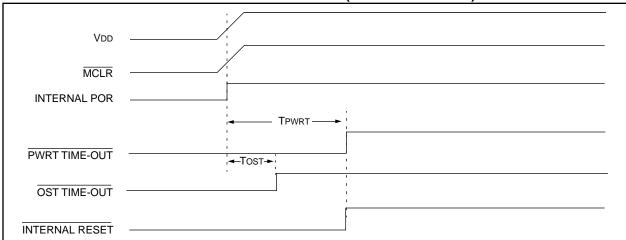

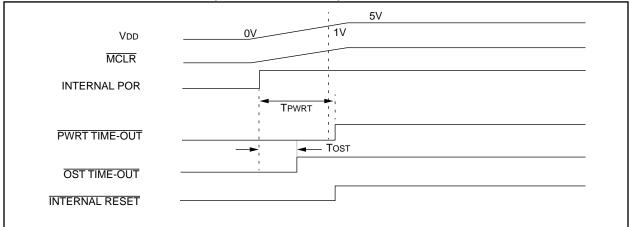

FIGURE 4-2: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

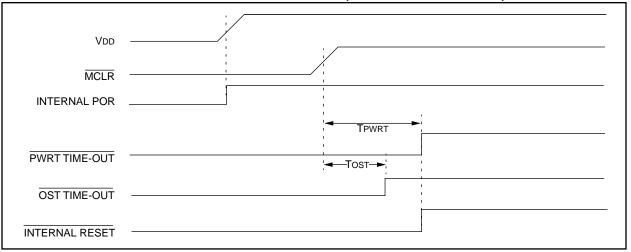

#### FIGURE 4-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD)

#### FIGURE 4-4: SLOW RISE TIME (MCLR TIED TO VDD)

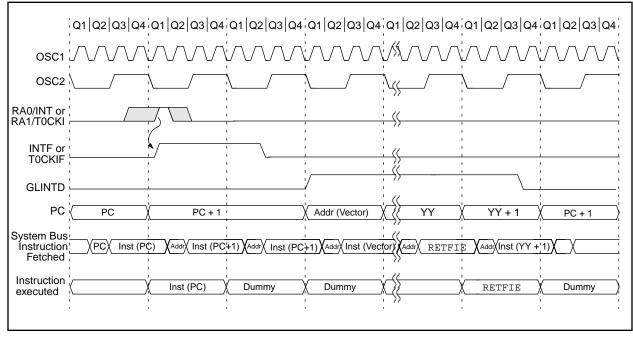

#### 5.5 RA0/INT Interrupt

The external interrupt on the RA0/INT pin is edge triggered. Either the rising edge, if INTEDG bit (T0STA<7>) is set, or the falling edge, if INTEDG bit is clear. When a valid edge appears on the RA0/INT pin, the INTF bit (INTSTA<4>) is set. This interrupt can be disabled by clearing the INTE control bit (INTSTA<0>). The INT interrupt can wake the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

#### 5.6 TMR0 Interrupt

An overflow (FFFFh  $\rightarrow$  0000h) in TMR0 will set the T0IF (INTSTA<5>) bit. The interrupt can be enabled/ disabled by setting/clearing the T0IE control bit (INTSTA<1>). For operation of the Timer0 module, see Section 11.0.

#### 5.7 TOCKI Interrupt

The external interrupt on the RA1/T0CKI pin is edge triggered. Either the rising edge, if the T0SE bit (T0STA<6>) is set, or the falling edge, if the T0SE bit is clear. When a valid edge appears on the RA1/T0CKI pin, the T0CKIF bit (INTSTA<6>) is set. This interrupt can be disabled by clearing the T0CKIE control bit (INTSTA<2>). The T0CKI interrupt can wake up the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

#### 5.8 Peripheral Interrupt

The peripheral interrupt flag indicates that at least one of the peripheral interrupts occurred (PEIF is set). The PEIF bit is a read only bit, and is a bit wise OR of all the flag bits in the PIR register AND'ed with the corresponding enable bits in the PIE register. Some of the peripheral interrupts can wake the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

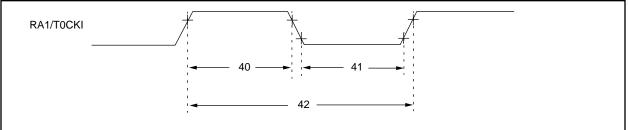

## FIGURE 5-5: INT PIN / TOCKI PIN INTERRUPT TIMING

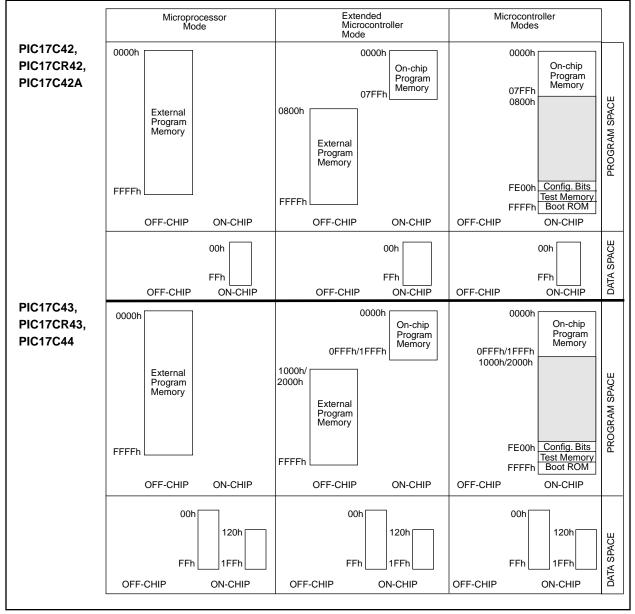

## TABLE 6-1: MODE MEMORY ACCESS

| Operating<br>Mode            | Internal<br>Program<br>Memory | Configuration Bits,<br>Test Memory,<br>Boot ROM |  |  |  |

|------------------------------|-------------------------------|-------------------------------------------------|--|--|--|

| Microprocessor               | No Access                     | No Access                                       |  |  |  |

| Microcontroller              | Access                        | Access                                          |  |  |  |

| Extended<br>Microcontroller  | Access                        | No Access                                       |  |  |  |

| Protected<br>Microcontroller | Access                        | Access                                          |  |  |  |

The PIC17C4X can operate in modes where the program memory is off-chip. They are the microprocessor and extended microcontroller modes. The microprocessor mode is the default for an unprogrammed device.

Regardless of the processor mode, data memory is always on-chip.

#### FIGURE 6-2: MEMORY MAP IN DIFFERENT MODES

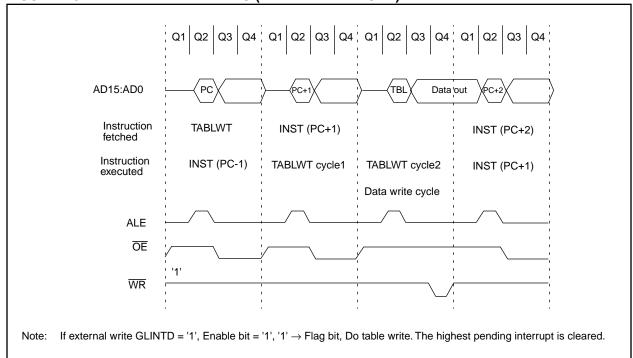

#### 7.2 <u>Table Writes to External Memory</u>

Table writes to external memory are always two-cycle instructions. The second cycle writes the data to the external memory location. The sequence of events for an external memory write are the same for an internal write.

| Note: | If an interrupt is pending or occurs during the TABLWT, the two cycle table write |

|-------|-----------------------------------------------------------------------------------|

|       | completes. The RA0/INT, TMR0, or T0CKI                                            |

|       | interrupt flag is automatically cleared or                                        |

|       | the pending peripheral interrupt is                                               |

|       | acknowledged.                                                                     |

7.2.2 TABLE WRITE CODE

The "i" operand of the TABLWT instruction can specify that the value in the 16-bit TBLPTR register is automatically incremented for the next write. In Example 7-1, the TBLPTR register is not automatically incremented.

#### EXAMPLE 7-1: TABLE WRITE

| CLRWDT |                 | ; | Clear WDT      |

|--------|-----------------|---|----------------|

| MOVLW  | HIGH (TBL_ADDR) | ; | Load the Table |

| MOVWF  | TBLPTRH         | ; | address        |

| MOVLW  | LOW (TBL_ADDR)  | ; |                |

| MOVWF  | TBLPTRL         | ; |                |

| MOVLW  | HIGH (DATA)     | ; | Load HI byte   |

| TLWT   | 1, WREG         | ; | in TABLATCH    |

| MOVLW  | LOW (DATA)      | ; | Load LO byte   |

| TABLWT | 0,0,WREG        | ; | in TABLATCH    |

|        |                 | ; | and write to   |

|        |                 | ; | program memory |

|        |                 | ; | (Ext. SRAM)    |

|        |                 |   |                |

#### FIGURE 7-5: TABLWT WRITE TIMING (EXTERNAL MEMORY)

#### 12.1.3.3.1 MAX RESOLUTION/FREQUENCY FOR EXTERNAL CLOCK INPUT

The use of an external clock for the PWM time-base (Timer1 or Timer2) limits the PWM output to a maximum resolution of 8-bits. The PWxDCL<7:6> bits must be kept cleared. Use of any other value will distort the PWM output. All resolutions are supported when internal clock mode is selected. The maximum attainable frequency is also lower. This is a result of the timing requirements of an external clock input for a timer (see the Electrical Specification section). The maximum PWM frequency, when the timers clock source is the RB4/TCLK12 pin, is shown in Table 12-3 (standard resolution mode).

#### 12.2 <u>Timer3</u>

Timer3 is a 16-bit timer consisting of the TMR3H and TMR3L registers. TMR3H is the high byte of the timer and TMR3L is the low byte. This timer has an associated 16-bit period register (PR3H/CA1H:PR3L/CA1L). This period register can be software configured to be a second 16-bit capture register.

When the TMR3CS bit (TCON1<2>) is clear, the timer increments every instruction cycle (Fosc/4). When TMR3CS is set, the timer increments on every falling edge of the RB5/TCLK3 pin. In either mode, the TMR3ON bit must be set for the timer to increment. When TMR3ON is clear, the timer will not increment or set the TMR3IF bit.

Timer3 has two modes of operation, depending on the CA1/PR3 bit (TCON2<3>). These modes are:

- · One capture and one period register mode

- Dual capture register mode

The PIC17C4X has up to two 16-bit capture registers that capture the 16-bit value of TMR3 when events are detected on capture pins. There are two capture pins (RB0/CAP1 and RB1/CAP2), one for each capture register. The capture pins are multiplexed with PORTB pins. An event can be:

- · a rising edge

- a falling edge

- every 4th rising edge

- every 16th rising edge

Each 16-bit capture register has an interrupt flag associated with it. The flag is set when a capture is made. The capture module is truly part of the Timer3 block. Figure 12-7 and Figure 12-8 show the block diagrams for the two modes of operation.

| Address       | Name   | Bit 7      | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets<br>(Note1) |

|---------------|--------|------------|--------|--------|--------|---------|--------|--------|--------|-------------------------------|--------------------------------------------|

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0 | CA1ED1 | CA1ED0 | T16     | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                                  |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF | PWM2ON | PWM10N | CA1/PR3 | TMR3ON | TMR2ON | TMR10N | 0000 0000                     | 0000 0000                                  |

| 10h, Bank 2   | TMR1   | Timer1 reg | ister  |        |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                                  |

| 11h, Bank 2   | TMR2   | Timer2 reg | ister  |        |        |         |        |        |        | XXXX XXXX                     | uuuu uuuu                                  |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF | TMR2IF | TMR1IF | CA2IF   | CA1IF  | TXIF   | RCIF   | 0000 0010                     | 0000 0010                                  |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE | TMR2IE | TMR1IE | CA2IE   | CA1IE  | TXIE   | RCIE   | 0000 0000                     | 0000 0000                                  |

| 07h, Unbanked | INTSTA | PEIF       | T0CKIF | T0IF   | INTF   | PEIE    | TOCKIE | TOIE   | INTE   | 0000 0000                     | 0000 0000                                  |

| 06h, Unbanked | CPUSTA | —          | _      | STKAV  | GLINTD | TO      | PD     | —      | _      | 11 11                         | 11 qq                                      |

| 10h, Bank 3   | PW1DCL | DC1        | DC0    | —      | —      | —       |        |        | _      | xx                            | uu                                         |

| 11h, Bank 3   | PW2DCL | DC1        | DC0    | TM2PW2 | _      | —       |        |        | _      | xx0                           | uu0                                        |

| 12h, Bank 3   | PW1DCH | DC9        | DC8    | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                                  |

| 13h, Bank 3   | PW2DCH | DC9        | DC8    | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | XXXX XXXX                     | uuuu uuuu                                  |

#### TABLE 12-4: REGISTERS/BITS ASSOCIATED WITH PWM

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on conditions, shaded cells are not used by PWM.

## 15.0 INSTRUCTION SET SUMMARY

The PIC17CXX instruction set consists of 58 instructions. Each instruction is a 16-bit word divided into an OPCODE and one or more operands. The opcode specifies the instruction type, while the operand(s) further specify the operation of the instruction. The PIC17CXX instruction set can be grouped into three types:

- byte-oriented

- bit-oriented

- literal and control operations.

These formats are shown in Figure 15-1.

Table 15-1 shows the field descriptions for the opcodes. These descriptions are useful for understanding the opcodes in Table 15-2 and in each specific instruction descriptions.

**byte-oriented instructions**, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' = '0', the result is placed in the WREG register. If 'd' = '1', the result is placed in the file register specified by the instruction.

**bit-oriented instructions**, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

**literal and control operations**, 'k' represents an 8- or 11-bit constant or literal value.

The instruction set is highly orthogonal and is grouped into:

- · byte-oriented operations

- bit-oriented operations

- · literal and control operations

All instructions are executed within one single instruction cycle, unless:

- a conditional test is true

- the program counter is changed as a result of an instruction

- a table read or a table write instruction is executed (in this case, the execution takes two instruction cycles with the second cycle executed as a NOP)

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 25 MHz, the normal instruction execution time is 160 ns. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 320 ns.

#### TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                                                                                                                                                                                                                                                                                                                                                  |

| Register file address (00h to FFh)                                                                                                                                                                                                                                                                                                                           |

| Peripheral register file address (00h to 1Fh)                                                                                                                                                                                                                                                                                                                |

| Table pointer control $i = 0'$ (do not change)<br>i = '1' (increment after instruction execution)                                                                                                                                                                                                                                                            |

| Table byte select t = '0' (perform operation on lower                                                                                                                                                                                                                                                                                                        |

| byte)<br>t = '1' (perform operation on upper byte literal field,<br>constant data)                                                                                                                                                                                                                                                                           |

| Working register (accumulator)                                                                                                                                                                                                                                                                                                                               |

| Bit address within an 8-bit file register                                                                                                                                                                                                                                                                                                                    |

| Literal field, constant data or label                                                                                                                                                                                                                                                                                                                        |

| Don't care location (= '0' or '1')<br>The assembler will generate code with $x = '0'$ . It is<br>the recommended form of use for compatibility with<br>all Microchip software tools.                                                                                                                                                                         |

| Destination select<br>0 = store result in WREG<br>1 = store result in file register f<br>Default is d = '1'                                                                                                                                                                                                                                                  |

| Unused, encoded as '0'                                                                                                                                                                                                                                                                                                                                       |

| Destination select<br>0 = store result in file register f and in the WREG<br>1 = store result in file register f<br>Default is s = '1'                                                                                                                                                                                                                       |

| Label name                                                                                                                                                                                                                                                                                                                                                   |

| ALU status bits Carry, Digit Carry, Zero, Overflow                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                              |

| Global Interrupt Disable bit (CPUSTA<4>)                                                                                                                                                                                                                                                                                                                     |

| Global Interrupt Disable bit (CPUSTA<4>)<br>Table Pointer (16-bit)                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                              |

| Table Pointer (16-bit)         Table Latch (16-bit) consists of high byte (TBLATH)                                                                                                                                                                                                                                                                           |

| Table Pointer (16-bit)<br>Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)                                                                                                                                                                                                                                                       |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)and low byte (TBLATL)Table Latch low byte                                                                                                                                                                                                                                           |

| Table Pointer (16-bit)         Table Latch (16-bit) consists of high byte (TBLATH)         and low byte (TBLATL)         Table Latch low byte         Table Latch high byte                                                                                                                                                                                  |

| Table Pointer (16-bit)<br>Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)<br>Table Latch low byte<br>Table Latch high byte<br>Top of Stack                                                                                                                                                                                      |

| Table Pointer (16-bit)<br>Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)<br>Table Latch low byte<br>Table Latch high byte<br>Top of Stack<br>Program Counter                                                                                                                                                                   |

| Table Pointer (16-bit)<br>Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)<br>Table Latch low byte<br>Table Latch high byte<br>Top of Stack<br>Program Counter<br>Bank Select Register                                                                                                                                           |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer Counter                                                                                                                                                 |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer CounterTime-out bit                                                                                                                                 |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer CounterTime-out bitPower-down bitDestination either the WREG register or the speci-                                                                 |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer CounterTime-out bitPower-down bitDestination either the WREG register or the specified register file location                                       |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer CounterTime-out bitPower-down bitDestination either the WREG register or the specified register file locationOptions                                    |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer CounterTime-out bitPower-down bitDestination either the WREG register or the specified register file locationOptionsContents                        |

| Table Pointer (16-bit) Table Latch (16-bit) consists of high byte (TBLATH) and low byte (TBLATL) Table Latch low byte Table Latch high byte Top of Stack Program Counter Bank Select Register Watchdog Timer Counter Time-out bit Power-down bit Destination either the WREG register or the speci- fied register file location Options Contents Assigned to |

|                                                                                                                                                                                                                                                                                                                                                              |

## TABLE 15-2: PIC17CXX INSTRUCTION SET

| Mnemonic,<br>Operands |       | Description                           |       | 16-bit Opcoo   | le   | Status    |       |

|-----------------------|-------|---------------------------------------|-------|----------------|------|-----------|-------|

|                       |       |                                       |       | MSb            | LSb  | Affected  |       |

| BYTE-ORIE             |       | TILE REGISTER OPERATIONS              | •     |                |      |           | •     |

| ADDWF                 | f,d   | ADD WREG to f                         | 1     | 0000 111d ffff | ffff | OV,C,DC,Z |       |

| ADDWFC                | f,d   | ADD WREG and Carry bit to f           | 1     | 0001 000d ffff | ffff | OV,C,DC,Z |       |

| ANDWF                 | f,d   | AND WREG with f                       | 1     | 0000 101d ffff | ffff | Z         |       |

| CLRF                  | f,s   | Clear f, or Clear f and Clear WREG    | 1     | 0010 100s ffff | ffff | None      | 3     |

| COMF                  | f,d   | Complement f                          | 1     | 0001 001d ffff | ffff | Z         |       |

| CPFSEQ                | f     | Compare f with WREG, skip if f = WREG | 1 (2) | 0011 0001 ffff | ffff | None      | 6,8   |

| CPFSGT                | f     | Compare f with WREG, skip if f > WREG | 1 (2) | 0011 0010 ffff | ffff | None      | 2,6,8 |

| CPFSLT                | f     | Compare f with WREG, skip if f < WREG | 1 (2) | 0011 0000 ffff | ffff | None      | 2,6,8 |

| DAW                   | f,s   | Decimal Adjust WREG Register          | 1     | 0010 111s ffff | ffff | C         | 3     |

| DECF                  | f,d   | Decrement f                           | 1     | 0000 011d ffff | ffff | OV,C,DC,Z |       |

| DECFSZ                | f,d   | Decrement f, skip if 0                | 1 (2) | 0001 011d ffff | ffff | None      | 6,8   |

| DCFSNZ                | f,d   | Decrement f, skip if not 0            | 1 (2) | 0010 011d ffff | ffff | None      | 6,8   |

| INCF                  | f,d   | Increment f                           | 1     | 0001 010d ffff | ffff | OV,C,DC,Z |       |

| INCFSZ                | f,d   | Increment f, skip if 0                | 1 (2) | 0001 111d ffff | ffff | None      | 6,8   |

| INFSNZ                | f,d   | Increment f, skip if not 0            | 1 (2) | 0010 010d ffff | ffff | None      | 6,8   |

| IORWF                 | f,d   | Inclusive OR WREG with f              | 1     | 0000 100d ffff | ffff | Z         |       |

| MOVFP                 | f,p   | Move f to p                           | 1     | 011p pppp ffff | ffff | None      |       |

| MOVPF                 | p,f   | Move p to f                           | 1     | 010p pppp ffff | ffff | Z         |       |

| MOVWF                 | f     | Move WREG to f                        | 1     | 0000 0001 ffff | ffff | None      |       |

| MULWF                 | f     | Multiply WREG with f                  | 1     | 0011 0100 ffff | ffff | None      | 9     |

| NEGW                  | f,s   | Negate WREG                           | 1     | 0010 110s ffff | ffff | OV,C,DC,Z | 1,3   |

| NOP                   | —     | No Operation                          | 1     | 0000 0000 0000 | 0000 | None      |       |

| RLCF                  | f,d   | Rotate left f through Carry           | 1     | 0001 101d ffff | ffff | С         |       |

| RLNCF                 | f,d   | Rotate left f (no carry)              | 1     | 0010 001d ffff | ffff | None      |       |

| RRCF                  | f,d   | Rotate right f through Carry          | 1     | 0001 100d ffff | ffff | C         |       |

| RRNCF                 | f,d   | Rotate right f (no carry)             | 1     | 0010 000d ffff | ffff | None      |       |

| SETF                  | f,s   | Set f                                 | 1     | 0010 101s ffff | ffff | None      | 3     |

| SUBWF                 | f,d   | Subtract WREG from f                  | 1     | 0000 010d ffff | ffff | OV,C,DC,Z | 1     |

| SUBWFB                | f,d   | Subtract WREG from f with Borrow      | 1     | 0000 001d ffff | ffff | OV,C,DC,Z | 1     |

| SWAPF                 | f,d   | Swap f                                | 1     | 0001 110d ffff | ffff | None      |       |

| TABLRD                | t,i,f | Table Read                            | 2 (3) | 1010 10ti ffff | ffff | None      | 7     |

Legend: Refer to Table 15-1 for opcode field descriptions.

- Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- 5: Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

| SLEEP Enter SLEEP mode                                                                |                                                      |                                                                                                                                                                                                                                          |       |    |      |  |  |  |

|---------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----|------|--|--|--|

| Syntax:                                                                               | [label] S                                            | [label] SLEEP                                                                                                                                                                                                                            |       |    |      |  |  |  |

| Operands:                                                                             | None                                                 |                                                                                                                                                                                                                                          |       |    |      |  |  |  |

| Operation:                                                                            |                                                      |                                                                                                                                                                                                                                          |       |    |      |  |  |  |

| Status Affected:                                                                      | TO, PD                                               |                                                                                                                                                                                                                                          |       |    |      |  |  |  |

| Encoding:                                                                             | 0000                                                 | 0000                                                                                                                                                                                                                                     | 000   | 0  | 0011 |  |  |  |

| Description:                                                                          | cleared. Th<br>set. Watch<br>are cleare<br>The proce | The power down status bit $(\overline{PD})$ is<br>cleared. The time-out status bit $(\overline{TO})$ is<br>set. Watchdog Timer and its prescaler<br>are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |       |    |      |  |  |  |

| Words:                                                                                | 1                                                    | 1                                                                                                                                                                                                                                        |       |    |      |  |  |  |

| Cycles:                                                                               | 1                                                    | 1                                                                                                                                                                                                                                        |       |    |      |  |  |  |

| Q Cycle Activity:                                                                     |                                                      |                                                                                                                                                                                                                                          |       |    |      |  |  |  |

| Q1                                                                                    | Q2                                                   | Q3                                                                                                                                                                                                                                       |       | (  | Q4   |  |  |  |

| Decode                                                                                | Read<br>register<br>PCLATH                           | Execu                                                                                                                                                                                                                                    | te    | N  | OP   |  |  |  |

| Example:                                                                              | SLEEP                                                |                                                                                                                                                                                                                                          |       |    |      |  |  |  |

| Before Instruction<br>$\overline{TO} = ?$<br>$\overline{PD} = ?$<br>After Instruction |                                                      |                                                                                                                                                                                                                                          |       |    |      |  |  |  |

| TO =<br>PD =<br>† If WDT causes                                                       | 1†<br>0                                              | nie hit ie                                                                                                                                                                                                                               | clear | be |      |  |  |  |

† If WDT causes wake-up, this bit is cleared

| SUE        | BLW                                                  | S                   | Subtract WREG from Literal |       |                          |     |    |                    |  |

|------------|------------------------------------------------------|---------------------|----------------------------|-------|--------------------------|-----|----|--------------------|--|

| Synt       | tax:                                                 | [                   | labe                       | /] :  | SUBLW                    | k   |    |                    |  |

| Ope        | rands:                                               | 0                   | $\leq k$                   | ≤ 2   | 55                       |     |    |                    |  |

| Ope        | ration:                                              | k                   | – (V                       | VRE   | $\Xi G) \rightarrow (N)$ | VRE | G) |                    |  |

| Stat       | us Affected:                                         | C                   | DV, C                      | , D   | C, Z                     |     |    |                    |  |

| Enc        | oding:                                               | Γ                   | 101                        | 1     | 0010                     | kkł | k  | kkkk               |  |

| Des        | cription:                                            | li                  |                            | k'. T | subtracte<br>he result   |     |    | e eight bit<br>⊢in |  |

| Wor        | ds:                                                  | 1                   |                            |       |                          |     |    |                    |  |

| Cycl       | les:                                                 | 1                   |                            |       |                          |     |    |                    |  |

| QC         | ycle Activity:                                       |                     |                            |       |                          |     |    |                    |  |

|            | Q1                                                   |                     | Q2                         |       | Q3                       |     |    | Q4                 |  |

|            | Decode                                               | -                   | Read<br>eral 'k            | ۲'    | Execu                    | ite |    | Vrite to<br>WREG   |  |

| Exa        | <u>mple 1</u> :                                      | S                   | UBLW                       | 1 (   | Ox02                     |     |    |                    |  |

|            | Before Instru<br>WREG<br>C<br>After Instruct<br>WREG | =<br>=              | ר<br>1<br>?<br>1           |       |                          |     |    |                    |  |

| <u>Exa</u> | C<br>Z<br>mple <u>2</u> :                            | =                   | 4 14 14                    |       |                          |     |    |                    |  |

|            | Before Instru<br>WREG<br>C                           | ictior<br>=<br>=    | ר<br>2<br>?                |       |                          |     |    |                    |  |

| <u>Exa</u> | After Instruct<br>WREG<br>C<br>Z<br>mple <u>3</u> :  | tion<br>=<br>=<br>= | 0<br>1<br>1                | ; re  | esult is ze              | ero |    |                    |  |

|            | Before Instru<br>WREG<br>C                           | ictior<br>=<br>=    | ר<br>3<br>?                |       |                          |     |    |                    |  |

|            | After Instruct<br>WREG<br>C<br>Z                     | tion<br>=<br>=<br>= | FF<br>0<br>1               |       | 's comple<br>esult is ne |     | ·  |                    |  |

| SUBWF                                   | Sub                              | otrac                          | t WREG                                           | from             | f                |                       |          |  |  |  |

|-----------------------------------------|----------------------------------|--------------------------------|--------------------------------------------------|------------------|------------------|-----------------------|----------|--|--|--|

| Syntax:                                 | [ lab                            | oel]                           | SUBWF                                            | f,d              |                  |                       | -        |  |  |  |

| Operands:                               | -                                | 0 ≤ f ≤ 255<br>d ∈ [0,1]       |                                                  |                  |                  |                       |          |  |  |  |

| Operation:                              | (f) –                            | $(f) - (W) \rightarrow (dest)$ |                                                  |                  |                  |                       |          |  |  |  |

| Status Affected:                        | OV,                              | OV, C, DC, Z                   |                                                  |                  |                  |                       |          |  |  |  |

| Encoding:                               | 00                               | 00                             | 010d                                             | fff              | f                | ffff                  | :        |  |  |  |

| Description:                            | com<br>resu                      | pleme<br>It is si              | VREG fro<br>ent metho<br>tored in W<br>tored bac | d). If '<br>/REG | d' is<br>. If 'c | 0 the<br>I' is 1 the  | l        |  |  |  |

| Words:                                  | 1                                |                                |                                                  |                  |                  |                       |          |  |  |  |

| Cycles:                                 | 1                                |                                |                                                  |                  |                  |                       | ,        |  |  |  |

| Q Cycle Activity:                       |                                  |                                |                                                  |                  |                  |                       |          |  |  |  |

| Q1                                      | Qź                               |                                | Q3                                               | 3                |                  | Q4                    |          |  |  |  |

| Decode                                  | Rea<br>registe                   |                                | Execu                                            | ute              |                  | Vrite to<br>stination |          |  |  |  |

|                                         |                                  |                                | DECI                                             | 1                | ue               | Sunation              |          |  |  |  |

| Example 1:                              | SUB                              | M F.                           | REG1,                                            | T                |                  |                       |          |  |  |  |

| Before Instru<br>REG1<br>WREG<br>C      | Iction<br>= 3<br>= 2<br>= ?      |                                |                                                  |                  |                  |                       | <u> </u> |  |  |  |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= 1<br>= 2<br>= 1<br>= 0 | ;                              | result is p                                      | oositiv          | е                |                       |          |  |  |  |

| Example 2:                              |                                  |                                |                                                  |                  |                  |                       |          |  |  |  |

| Before Instru<br>REG1<br>WREG<br>C      | uction<br>= 2<br>= 2<br>= ?      |                                |                                                  |                  |                  |                       | <u> </u> |  |  |  |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= 0<br>= 2<br>= 1<br>= 1 | ;                              | result is z                                      | zero             |                  |                       |          |  |  |  |

| Example 3:                              |                                  |                                |                                                  |                  |                  |                       |          |  |  |  |

| Before Instru<br>REG1<br>WREG<br>C      | uction<br>= 1<br>= 2<br>= ?      |                                |                                                  |                  |                  |                       | ļ        |  |  |  |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= F<br>= 2<br>= 0<br>= 0 |                                | result is r                                      | negativ          | ve               |                       |          |  |  |  |

| SUBWFB                            |                | Subtract WREG from f with                  |                                                                    |                                |                       |                       |  |

|-----------------------------------|----------------|--------------------------------------------|--------------------------------------------------------------------|--------------------------------|-----------------------|-----------------------|--|

| Syntax:                           |                | Borrow [ label ] SUBWFB f,d                |                                                                    |                                |                       |                       |  |

| Operands:                         |                | $0 \le f \le 2$                            |                                                                    | , u                            |                       |                       |  |

| Operands.                         |                | d ∈ [0,1                                   | ]                                                                  |                                |                       |                       |  |

| Operation:                        |                | (f) – (W)                                  | $) - \overline{C} \rightarrow (0)$                                 | dest)                          |                       |                       |  |

| Status Affect                     | ed:            | OV, C, E                                   | DC, Z                                                              |                                |                       |                       |  |

| Encoding:                         |                | 0000                                       | 001d                                                               | fff                            | f                     | ffff                  |  |

| Description:                      |                | (borrow)<br>ment me<br>stored in           | WREG an<br>from regis<br>thod). If 'd'<br>WREG. If<br>ack in regis | ter 'f'<br>is 0 tl<br>'d' is ´ | (2's<br>he r<br>1 the | comple-<br>esult is   |  |

| Words:                            |                | 1                                          |                                                                    |                                |                       |                       |  |

| Cycles:                           |                | 1                                          |                                                                    |                                |                       |                       |  |

| Q Cycle Activ                     | /ity:          |                                            |                                                                    |                                |                       |                       |  |

| Q1                                |                | Q2                                         | Q3                                                                 |                                |                       | Q4                    |  |

| Decod                             | -              | Read<br>egister 'f'                        | Execu                                                              | ıte                            |                       | Vrite to<br>stination |  |

| Example 1:                        |                | SUBWFB                                     | REG1,                                                              | 1                              |                       |                       |  |

| Before Ir                         | nstructio      | on                                         |                                                                    |                                |                       |                       |  |

| REG<br>WRE<br>C                   |                | 0x19<br>0x0D<br>1                          | (0001<br>(0000                                                     |                                | '                     |                       |  |

| After Ins                         | truction       | 1                                          |                                                                    |                                |                       |                       |  |

| REG<br>WRE<br>C                   | EG =<br>=      | 0x0D (0000 1101)<br>1 ; result is positive |                                                                    |                                |                       |                       |  |

| Z                                 | =              | 0                                          |                                                                    |                                |                       |                       |  |

| Example2:                         |                | UBWFB                                      | REG1,0                                                             |                                |                       |                       |  |

| Before Ir<br>REG<br>WRE<br>C      | 61 =           | 0x1B                                       | (0001<br>(0001                                                     |                                | ,                     |                       |  |

| After Ins                         | truction       | 1                                          |                                                                    |                                |                       |                       |  |

| REG                               |                | 0x1B                                       | (0001                                                              | 101                            | 1)                    |                       |  |

| WRE<br>C<br>Z                     | EG =<br>=<br>= | 0x00<br>1<br>1                             | ; resul                                                            | t is ze                        | ro                    |                       |  |

| Example3:                         | S              | UBWFB                                      | REG1,1                                                             |                                |                       |                       |  |

| Before Ir                         |                | on                                         |                                                                    |                                |                       |                       |  |

| REG<br>WRE<br>C                   |                | 0x03<br>0x0E<br>1                          | (0000<br>(0000                                                     |                                |                       |                       |  |

| After Ins<br>REG<br>WRE<br>C<br>Z | 61 =           | 0xF5<br>0x0E<br>0<br>0                     | (1111<br>(0000<br>; <b>resul</b> t                                 | 110                            | 1)                    | ?'s comp]<br>ve       |  |

| DC CHARACTERISTICS |                |                                                                   | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +40^{\circ}C$ Operating voltage VDD range as described in Section 17.1 |           |               |          |                                                            |  |  |  |

|--------------------|----------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|----------|------------------------------------------------------------|--|--|--|

| Parameter<br>No.   | Characteristic | Min                                                               | Typ†                                                                                                                                                                         | Max       | Units         |          |                                                            |  |  |  |

|                    |                | Internal Program Memory<br>Programming Specs (Note 4)             |                                                                                                                                                                              |           |               |          |                                                            |  |  |  |

| D110<br>D111       | Vpp<br>Vddp    | Voltage on MCLR/VPP pin<br>Supply voltage during<br>programming   | 12.75<br>4.75                                                                                                                                                                | _<br>5.0  | 13.25<br>5.25 | V<br>V   | Note 5                                                     |  |  |  |

| D112<br>D113       | Ipp<br>Iddp    | Current into MCLR/VPP pin<br>Supply current during<br>programming |                                                                                                                                                                              | 25 ‡<br>_ | 50 ‡<br>30 ‡  | mA<br>mA |                                                            |  |  |  |

| D114               |                | Programming pulse width                                           | 10                                                                                                                                                                           | 100       | 1000          | μs       | Terminated via internal/exter-<br>nal interrupt or a reset |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

**Note:** When using the Table Write for internal programming, the device temperature must be less than 40°C.

#### FIGURE 17-5: TIMER0 CLOCK TIMINGS

#### TABLE 17-5: TIMER0 CLOCK REQUIREMENTS

| Parameter<br>No. | Sum  | Characteristic         |                | Min               | Tunt | Мах   | Unito | Conditions         |

|------------------|------|------------------------|----------------|-------------------|------|-------|-------|--------------------|

| NO.              | Sym  | Characteristic         |                | IVIIII            | Typ† | IVIAX | Units | Conditions         |

| 40               | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5TCY + 20 §     | —    | _     | ns    |                    |

|                  |      |                        | With Prescaler | 10*               | —    | —     | ns    |                    |

| 41               | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5Tcy + 20 §     | —    | —     | ns    |                    |

|                  |      |                        | With Prescaler | 10*               | —    | —     | ns    |                    |

| 42               | Tt0P | T0CKI Period           | •              | <u>Tcy + 40</u> § | —    | —     | ns    | N = prescale value |

|                  |      |                        |                | N                 |      |       |       | (1, 2, 4,, 256)    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

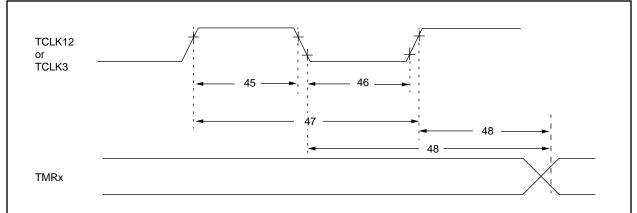

#### FIGURE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK TIMINGS

## TABLE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK REQUIREMENTS

| Parameter |           |                                                               |                        | Тур |          |       |                                    |

|-----------|-----------|---------------------------------------------------------------|------------------------|-----|----------|-------|------------------------------------|

| No.       | Sym       | Characteristic                                                | Min                    | †   | Max      | Units | Conditions                         |

| 45        | Tt123H    | TCLK12 and TCLK3 high time                                    | 0.5 TCY + 20 §         |     | _        | ns    |                                    |

| 46        | Tt123L    | TCLK12 and TCLK3 low time                                     | 0.5 TCY + 20 §         |     |          | ns    |                                    |

| 47        | Tt123P    | TCLK12 and TCLK3 input period                                 | <u>Tcy + 40</u> §<br>N |     |          | ns    | N = prescale value<br>(1, 2, 4, 8) |

| 48        | TckE2tmrl | Delay from selected External Clock Edge to<br>Timer increment | 2Tosc §                |     | 6 Tosc § | _     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

# Applicable Devices 42 R42 42A 43 R43 44

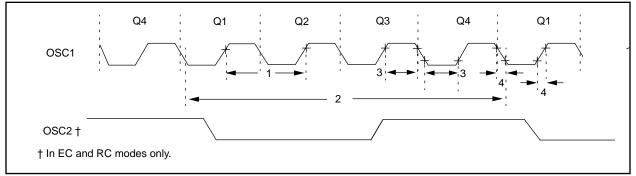

## 19.5 <u>Timing Diagrams and Specifications</u>

#### FIGURE 19-2: EXTERNAL CLOCK TIMING

#### TABLE 19-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                     | Min   | Тур†   | Max   | Units | Conditions                                        |

|--------------|-------|------------------------------------|-------|--------|-------|-------|---------------------------------------------------|

|              | Fosc  | External CLKIN Frequency           | DC    | _      | 8     | MHz   | EC osc mode - 08 devices (8 MHz devices)          |

|              |       | (Note 1)                           | DC    | _      | 16    | MHz   | - 16 devices (16 MHz devices)                     |

|              |       | (                                  | DC    | _      | 25    | MHz   | - 25 devices (25 MHz devices)                     |

|              |       |                                    | DC    | —      | 33    | MHz   | - 33 devices (33 MHz devices)                     |

|              |       | Oscillator Frequency               | DC    | _      | 4     | MHz   | RC osc mode                                       |

|              |       | (Note 1)                           | 1     | _      | 8     | MHz   | XT osc mode - 08 devices (8 MHz devices)          |

|              |       |                                    | 1     | _      | 16    | MHz   | - 16 devices (16 MHz devices)                     |

|              |       |                                    | 1     | _      | 25    | MHz   | - 25 devices (25 MHz devices)                     |

|              |       |                                    | 1     | _      | 33    | MHz   | - 33 devices (33 MHz devices)                     |

|              |       |                                    | DC    | —      | 2     | MHz   | LF osc mode                                       |

| 1            | Tosc  | External CLKIN Period              | 125   | _      | —     | ns    | EC osc mode - 08 devices (8 MHz devices)          |

|              |       | (Note 1)                           | 62.5  | _      | —     | ns    | - 16 devices (16 MHz devices)                     |

|              |       |                                    | 40    | _      | —     | ns    | - 25 devices (25 MHz devices)                     |

|              |       |                                    | 30.3  | —      | —     | ns    | - 33 devices (33 MHz devices)                     |

|              |       | Oscillator Period                  | 250   | _      | —     | ns    | RC osc mode                                       |

|              |       | (Note 1)                           | 125   | _      | 1,000 | ns    | XT osc mode - 08 devices (8 MHz devices)          |

|              |       |                                    | 62.5  | _      | 1,000 | ns    | - 16 devices (16 MHz devices)                     |

|              |       |                                    | 40    | —      | 1,000 | ns    | <ul> <li>- 25 devices (25 MHz devices)</li> </ul> |

|              |       |                                    | 30.3  | —      | 1,000 | ns    | - 33 devices (33 MHz devices)                     |

|              |       |                                    | 500   | —      | —     | ns    | LF osc mode                                       |

| 2            | Тсү   | Instruction Cycle Time<br>(Note 1) | 121.2 | 4/Fosc | DC    | ns    |                                                   |

| 3            | TosL, | Clock in (OSC1)                    | 10 ±  | _      | _     | ns    | EC oscillator                                     |

|              | TosH  | high or low time                   | · '   |        |       |       |                                                   |

| 4            | TosR, | Clock in (OSC1)                    | _     | _      | 5‡    | ns    | EC oscillator                                     |

|              | TosF  | rise or fall time                  |       |        |       |       |                                                   |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

## Applicable Devices 42 R42 42A 43 R43 44

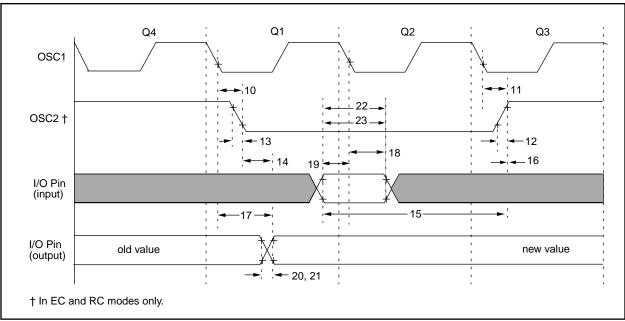

#### FIGURE 19-3: CLKOUT AND I/O TIMING

| TABLE 19-3: | <b>CLKOUT AND I/O TIMING REQUIREMENTS</b> |

|-------------|-------------------------------------------|

|             |                                           |

| Parameter<br>No. | Sym      | Characteristic                                         |                              | Min            | Тур† | Max           | Units  | Conditions |

|------------------|----------|--------------------------------------------------------|------------------------------|----------------|------|---------------|--------|------------|

| 10               | TosH2ckL | OSC1↓ to CLKOUT                                        | —                            | 15‡            | 30 ‡ | ns            | Note 1 |            |

| 11               | TosH2ckH | OSC1↓ to CLKOUT                                        | $\uparrow$                   | —              | 15‡  | 30 ‡          | ns     | Note 1     |

| 12               | TckR     | CLKOUT rise time                                       |                              | —              | 5‡   | 15 ‡          | ns     | Note 1     |

| 13               | TckF     | CLKOUT fall time                                       |                              | —              | 5‡   | 15 ‡          | ns     | Note 1     |

| 14               | TckH2ioV | CLKOUT ↑ to Port PIC17CR42/42A/43/<br>out valid R43/44 |                              | —              | —    | 0.5TCY + 20 ‡ | ns     | Note 1     |

|                  |          |                                                        | PIC17LCR42/42A/43/<br>R43/44 | —              | —    | 0.5TCY + 50 ‡ | ns     | Note 1     |

| 15               | TioV2ckH | Port in valid before<br>CLKOUT↑                        | PIC17CR42/42A/43/<br>R43/44  | 0.25Tcy + 25 ‡ | _    | —             | ns     | Note 1     |

|                  |          |                                                        | PIC17LCR42/42A/43/<br>R43/44 | 0.25Tcy + 50 ‡ | —    |               | ns     | Note 1     |

| 16               | TckH2iol | Port in hold after CL                                  | KOUT                         | 0 ‡            | —    | —             | ns     | Note 1     |

| 17               | TosH2ioV | OSC1↓ (Q1 cycle) t                                     | o Port out valid             | —              | —    | 100 ‡         | ns     |            |

| 18               | TosH2iol | OSC1↓ (Q2 cycle) t<br>(I/O in hold time)               | 0‡                           | —              |      | ns            |        |            |

| 19               | TioV2osH | Port input valid to O<br>(I/O in setup time)           | 30 ‡                         | —              |      | ns            |        |            |

| 20               | TioR     | Port output rise time                                  | —                            | 10 ‡           | 35 ‡ | ns            |        |            |

| 21               | TioF     | Port output fall time                                  | —                            | 10 ‡           | 35 ‡ | ns            |        |            |

| 22               | TinHL    | INT pin high or low                                    | 25 *                         | —              | —    | ns            |        |            |

| 23               | TrbHL    | RB7:RB0 change IN                                      | 25 *                         | —              | —    | ns            |        |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Measurements are taken in EC Mode where CLKOUT output is 4 x Tosc.

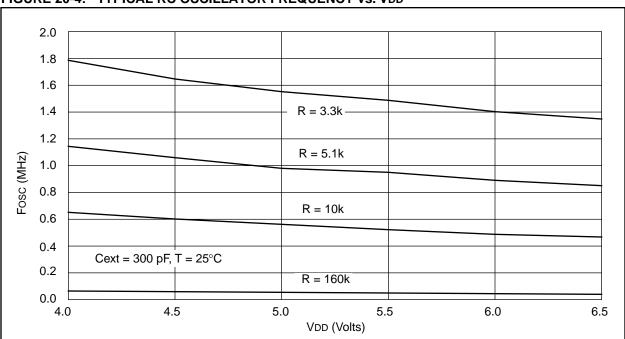

#### FIGURE 20-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

#### TABLE 20-2: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average<br>Fosc @ 5V, 25°C |       |  |  |  |

|--------|------|----------------------------|-------|--|--|--|

| 22 pF  | 10k  | 3.33 MHz                   | ± 12% |  |  |  |

|        | 100k | 353 kHz                    | ± 13% |  |  |  |

| 100 pF | 3.3k | 3.54 MHz                   | ± 10% |  |  |  |

|        | 5.1k | 2.43 MHz                   | ± 14% |  |  |  |

|        | 10k  | 1.30 MHz                   | ± 17% |  |  |  |

|        | 100k | 129 kHz                    | ± 10% |  |  |  |

| 300 pF | 3.3k | 1.54 MHz                   | ± 14% |  |  |  |

|        | 5.1k | 980 kHz                    | ± 12% |  |  |  |

|        | 10k  | 564 kHz                    | ± 16% |  |  |  |

|        | 160k | 35 kHz                     | ± 18% |  |  |  |

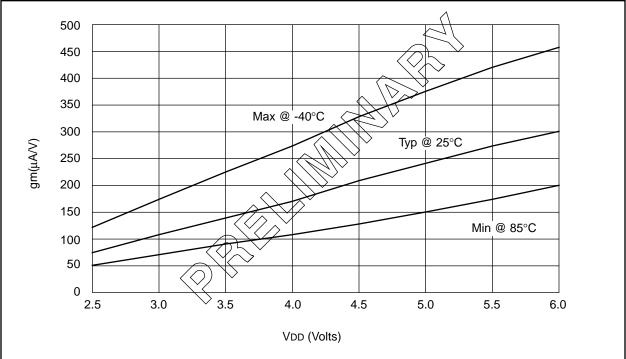

FIGURE 20-6: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

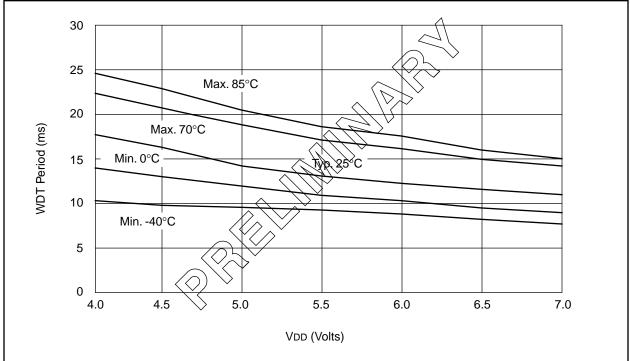

## FIGURE 20-13: WDT TIMER TIME-OUT PERIOD vs. VDD

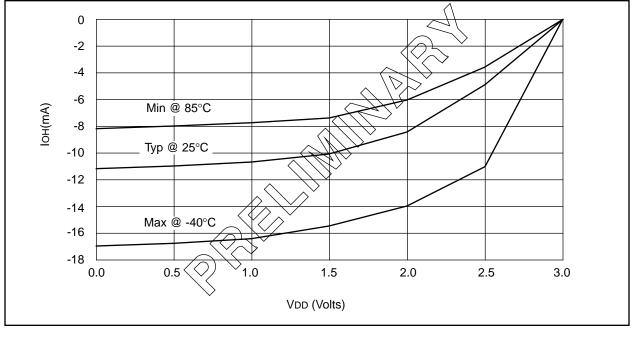

FIGURE 20-14: IOH vs. VOH, VDD = 3V

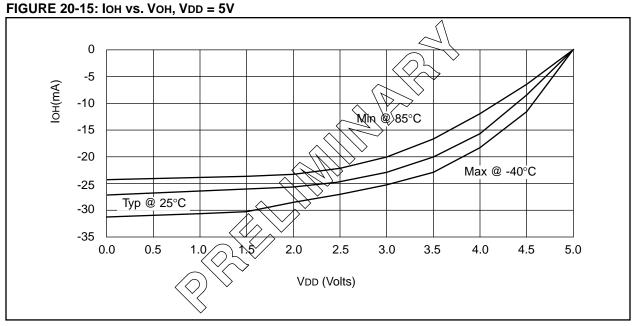

## Applicable Devices 42 R42 42A 43 R43 44

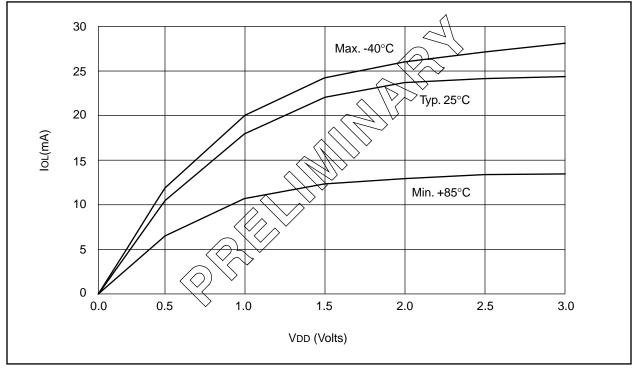

FIGURE 20-16: IOL vs. VOL, VDD = 3V

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoq® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.