Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 8KB (4K × 16)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | <u>.</u>                                                                 |

| RAM Size                   | 454 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

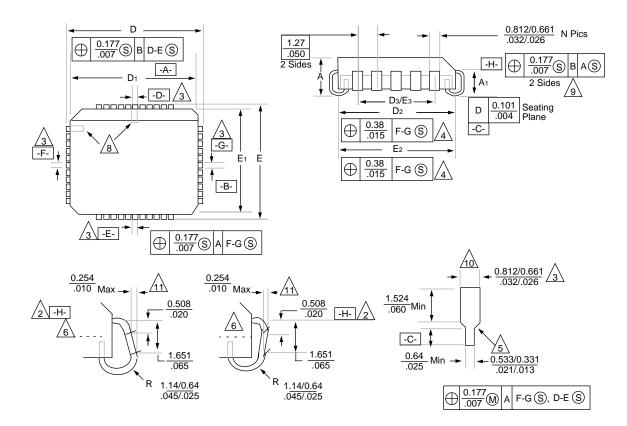

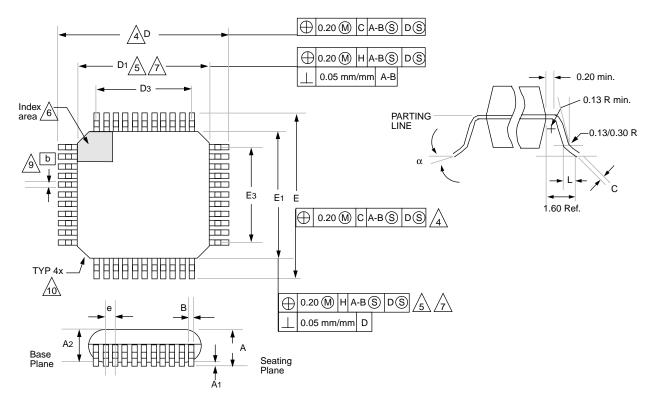

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-16-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.3 <u>Peripheral Interrupt Request Register</u> (PIR)

This register contains the individual flag bits for the peripheral interrupts.

**Note:** These bits will be set by the specified condition, even if the corresponding interrupt enable bit is cleared (interrupt disabled), or the GLINTD bit is set (all interrupts disabled). Before enabling an interrupt, the user may wish to clear the interrupt flag to ensure that the program does not immediately branch to the peripheral interrupt service routine.

# FIGURE 5-4: PIR REGISTER (ADDRESS: 16h, BANK 1)

|        | 0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 R-0                                                                                                                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBIF   |                                                                                                                                                                                                                                                                              |

| bit7   | bit0 W = Writable bit<br>-n = Value at POR reset                                                                                                                                                                                                                             |

| bit 7: | <b>RBIF</b> : PORTB Interrupt on Change Flag bit<br>1 = One of the PORTB inputs changed (Software must end the mismatch condition)<br>0 = None of the PORTB inputs have changed                                                                                              |

| bit 6: | TMR3IF: Timer3 Interrupt Flag bit<br>If Capture1 is enabled (CA1/PR3 = 1)<br>1 = Timer3 overflowed<br>0 = Timer3 did not overflow                                                                                                                                            |

|        | If Capture1 is disabled (CA1/ $\overline{PR3}$ = 0)<br>1 = Timer3 value has rolled over to 0000h from equalling the period register (PR3H:PR3L) value<br>0 = Timer3 value has not rolled over to 0000h from equalling the period register (PR3H:PR3L) value                  |

| bit 5: | <b>TMR2IF</b> : Timer2 Interrupt Flag bit<br>1 = Timer2 value has rolled over to 0000h from equalling the period register (PR2) value<br>0 = Timer2 value has not rolled over to 0000h from equalling the period register (PR2) value                                        |

| bit 4: | <b>TMR1IF</b> : Timer1 Interrupt Flag bit<br>If Timer1 is in 8-bit mode (T16 = 0)<br>1 = Timer1 value has rolled over to 0000h from equalling the period register (PR) value<br>0 = Timer1 value has not rolled over to 0000h from equalling the period register (PR2) value |

|        | If Timer1 is in 16-bit mode (T16 = 1)<br>1 = TMR1:TMR2 value has rolled over to 0000h from equalling the period register (PR1:PR2) value<br>0 = TMR1:TMR2 value has not rolled over to 0000h from equalling the period register (PR1:PR2) value                              |

| bit 3: | <b>CA2IF</b> : Capture2 Interrupt Flag bit<br>1 = Capture event occurred on RB1/CAP2 pin<br>0 = Capture event did not occur on RB1/CAP2 pin                                                                                                                                  |

| bit 2: | <b>CA1IF</b> : Capture1 Interrupt Flag bit<br>1 = Capture event occurred on RB0/CAP1 pin<br>0 = Capture event did not occur on RB0/CAP1 pin                                                                                                                                  |

| bit 1: | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = Transmit buffer is empty<br>0 = Transmit buffer is full                                                                                                                                                               |

| bit 0: | RCIF: USART Receive Interrupt Flag bit<br>1 = Receive buffer is full<br>0 = Receive buffer is empty                                                                                                                                                                          |

# TABLE 6-1: MODE MEMORY ACCESS

| Operating<br>Mode            | Internal<br>Program<br>Memory | Configuration Bits,<br>Test Memory,<br>Boot ROM |  |  |

|------------------------------|-------------------------------|-------------------------------------------------|--|--|

| Microprocessor               | No Access                     | No Access                                       |  |  |

| Microcontroller              | Access                        | Access                                          |  |  |

| Extended<br>Microcontroller  | Access                        | No Access                                       |  |  |

| Protected<br>Microcontroller | Access                        | Access                                          |  |  |

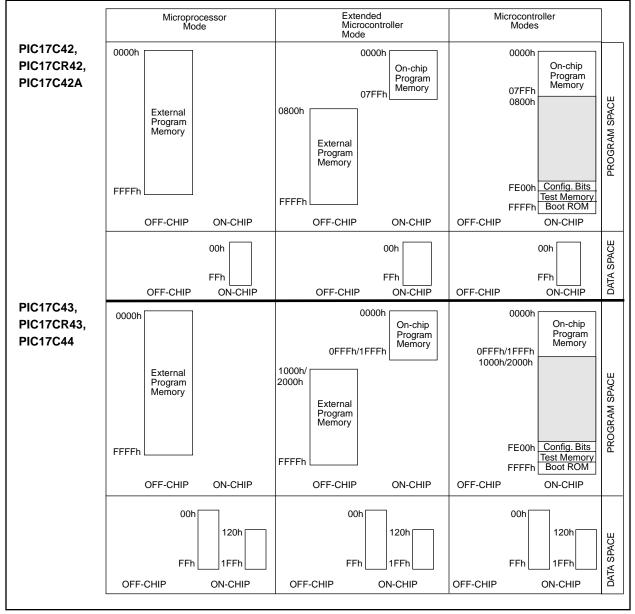

The PIC17C4X can operate in modes where the program memory is off-chip. They are the microprocessor and extended microcontroller modes. The microprocessor mode is the default for an unprogrammed device.

Regardless of the processor mode, data memory is always on-chip.

#### FIGURE 6-2: MEMORY MAP IN DIFFERENT MODES

| Addr                                                        | Unbanked                                                                                  |                                                        |                                                           |                                                               |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|

| 00h                                                         | INDF0                                                                                     |                                                        |                                                           |                                                               |

| 01h                                                         | FSR0                                                                                      |                                                        |                                                           |                                                               |

| 02h                                                         | PCL                                                                                       |                                                        |                                                           |                                                               |

| 03h                                                         | PCLATH                                                                                    |                                                        |                                                           |                                                               |

| 04h                                                         | ALUSTA                                                                                    |                                                        |                                                           |                                                               |

| 05h                                                         | TOSTA                                                                                     |                                                        |                                                           |                                                               |

| 06h                                                         | CPUSTA                                                                                    |                                                        |                                                           |                                                               |

| 07h                                                         | INTSTA                                                                                    |                                                        |                                                           |                                                               |

| 08h                                                         | INDF1                                                                                     |                                                        |                                                           |                                                               |

| 09h                                                         | FSR1                                                                                      |                                                        |                                                           |                                                               |

| 0Ah                                                         | WREG                                                                                      |                                                        |                                                           |                                                               |

| 0Bh                                                         | TMR0L                                                                                     |                                                        |                                                           |                                                               |

| 0Ch                                                         | TMR0H                                                                                     |                                                        |                                                           |                                                               |

| 0Dh                                                         | TBLPTRL                                                                                   |                                                        |                                                           |                                                               |

| 0Eh                                                         | TBLPTRH                                                                                   |                                                        |                                                           |                                                               |

| 0Fh                                                         | BSR                                                                                       |                                                        |                                                           |                                                               |

| 1                                                           |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | Bank 0                                                                                    | Bank 1 <sup>(1)</sup>                                  | Bank 2 <sup>(1)</sup>                                     | Bank 3 <sup>(1)</sup>                                         |

| 10h                                                         | Bank 0<br>PORTA                                                                           | Bank 1 <sup>(1)</sup><br>DDRC                          | Bank 2 <sup>(1)</sup><br>TMR1                             | Bank 3 <sup>(1)</sup><br>PW1DCL                               |

| 10h<br>11h                                                  |                                                                                           |                                                        |                                                           |                                                               |

|                                                             | PORTA                                                                                     | DDRC                                                   | TMR1                                                      | PW1DCL                                                        |

| 11h                                                         | PORTA<br>DDRB                                                                             | DDRC<br>PORTC                                          | TMR1<br>TMR2                                              | PW1DCL<br>PW2DCL                                              |

| 11h<br>12h                                                  | PORTA<br>DDRB<br>PORTB                                                                    | DDRC<br>PORTC<br>DDRD                                  | TMR1<br>TMR2<br>TMR3L                                     | PW1DCL<br>PW2DCL<br>PW1DCH                                    |

| 11h<br>12h<br>13h                                           | PORTA<br>DDRB<br>PORTB<br>RCSTA                                                           | DDRC<br>PORTC<br>DDRD<br>PORTD                         | TMR1<br>TMR2<br>TMR3L<br>TMR3H                            | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH                          |

| 11h<br>12h<br>13h<br>14h                                    | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG                                                  | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE                 | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1                     | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L                  |

| 11h<br>12h<br>13h<br>14h<br>15h                             | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA                                         | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE        | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2              | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H          |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h                      | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h               | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG                                | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h        | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General            | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

| 11h<br>12h<br>13h<br>14h<br>15h<br>16h<br>17h<br>18h<br>1Fh | PORTA<br>DDRB<br>PORTB<br>RCSTA<br>RCREG<br>TXSTA<br>TXREG<br>SPBRG<br>General<br>Purpose | DDRC<br>PORTC<br>DDRD<br>PORTD<br>DDRE<br>PORTE<br>PIR | TMR1<br>TMR2<br>TMR3L<br>TMR3H<br>PR1<br>PR2<br>PR3L/CA1L | PW1DCL<br>PW2DCL<br>PW1DCH<br>PW2DCH<br>CA2L<br>CA2H<br>TCON1 |

# FIGURE 6-5: PIC17C42 REGISTER FILE MAP

Note 1: SFR file locations 10h - 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

#### FIGURE 6-6: PIC17CR42/42A/43/R43/44 REGISTER FILE MAP

| Addr | Unbanked           |                       |                       |                       |

|------|--------------------|-----------------------|-----------------------|-----------------------|

| 00h  | INDF0              |                       |                       |                       |

| 01h  | FSR0               |                       |                       |                       |

| 02h  | PCL                |                       |                       |                       |

| 03h  | PCLATH             |                       |                       |                       |

| 04h  | ALUSTA             |                       |                       |                       |

| 05h  | TOSTA              |                       |                       |                       |

| 06h  | CPUSTA             |                       |                       |                       |

| 07h  | INTSTA             |                       |                       |                       |

| 08h  | INDF1              |                       |                       |                       |

| 09h  | FSR1               |                       |                       |                       |

| 0Ah  | WREG               |                       |                       |                       |

| 0Bh  | TMR0L              |                       |                       |                       |

| 0Ch  | TMR0H              |                       |                       |                       |

| 0Dh  | TBLPTRL            |                       |                       |                       |

| 0Eh  | TBLPTRH            |                       |                       |                       |

| 0Fh  | BSR                |                       |                       |                       |

|      | Bank 0             | Bank 1 <sup>(1)</sup> | Bank 2 <sup>(1)</sup> | Bank 3 <sup>(1)</sup> |

| 10h  | PORTA              | DDRC                  | TMR1                  | PW1DCL                |

| 11h  | DDRB               | PORTC                 | TMR2                  | PW2DCL                |

| 12h  | PORTB              | DDRD                  | TMR3L                 | PW1DCH                |

| 13h  | RCSTA              | PORTD                 | TMR3H                 | PW2DCH                |

| 14h  | RCREG              | DDRE                  | PR1                   | CA2L                  |

| 15h  | TXSTA              | PORTE                 | PR2                   | CA2H                  |

| 16h  | TXREG              | PIR                   | PR3L/CA1L             | TCON1                 |

| 17h  | SPBRG              | PIE                   | PR3H/CA1H             | TCON2                 |

| 18h  | PRODL              |                       |                       |                       |

| 19h  | PRODH              |                       |                       |                       |

| 1Ah  |                    |                       |                       |                       |

|      |                    |                       |                       |                       |

| 1Fh  |                    |                       | 1                     |                       |

| 20h  | General            | General               |                       |                       |

|      | Purpose            | Purpose               |                       |                       |

|      | RAM <sup>(2)</sup> | RAM (2)               |                       |                       |

|      |                    |                       |                       |                       |

| FFh  |                    |                       |                       |                       |

- Note 1: SFR file locations 10h 17h are banked. All other SFRs ignore the Bank Select Register (BSR) bits.

- 2: General Purpose Registers (GPR) locations 20h - FFh and 120h - 1FFh are banked. All other GPRs ignore the Bank Select Register (BSR) bits.

| TABLE 6-3: | SPECIAL FUNCTION REGISTERS |

|------------|----------------------------|

|------------|----------------------------|

| Address            | Name          | Bit 7        | Bit 6                                | Bit 5         | Bit 4        | Bit 3        | Bit 2           | Bit 1          | Bit 0           | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|---------------|--------------|--------------------------------------|---------------|--------------|--------------|-----------------|----------------|-----------------|-------------------------------|-------------------------------------|

| Unbank             | ed            | •            |                                      |               |              | •            |                 |                | •               |                               |                                     |

| 00h                | INDF0         | Uses con     | tents of FSI                         |               |              |              |                 |                |                 |                               |                                     |

| 01h                | FSR0          | Indirect d   | ata memory                           | address po    | inter 0      |              |                 |                |                 | XXXX XXXX                     | uuuu uuuu                           |

| 02h                | PCL           | Low orde     | r 8-bits of P                        | С             |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | PCLATH        | Holding re   | egister for u                        | pper 8-bits o | of PC        |              |                 |                |                 | 0000 0000                     | uuuu uuuu                           |

| 04h                | ALUSTA        | FS3          | FS2                                  | FS1           | FS0          | OV           | Z               | DC             | С               | 1111 xxxx                     | 1111 uuuu                           |

| 05h                | TOSTA         | INTEDG       | TOSE                                 | TOCS          | PS3          | PS2          | PS1             | PS0            | —               | 0000 000-                     | 0000 000-                           |

| 06h <b>(2)</b>     | CPUSTA        | _            | _                                    | STKAV         | GLINTD       | TO           | PD              | _              | _               | 11 11                         | 11 qq                               |

| 07h                | INTSTA        | PEIF         | TOCKIF                               | T0IF          | INTF         | PEIE         | TOCKIE          | TOIE           | INTE            | 0000 0000                     | 0000 0000                           |

| 08h                | INDF1         | Uses con     | tents of FSI                         | R1 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 09h                | FSR1          | Indirect d   | ata memory                           | address po    | inter 1      |              | , ,             |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ah                | WREG          | Working r    | egister                              |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Bh                | TMR0L         | TMR0 reg     | gister; low b                        | yte           |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ch                | TMR0H         | TMR0 reg     | gister; high I                       | oyte          |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Dh                | TBLPTRL       | Low byte     | of program                           | memory tab    | le pointer   |              |                 |                |                 | (4)                           | (4)                                 |

| 0Eh                | TBLPTRH       | High byte    | of program                           | memory tal    | ole pointer  |              |                 |                |                 | (4)                           | (4)                                 |

| 0Fh                | BSR           | Bank sele    | ect register                         |               |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| Bank 0             |               | 1            |                                      |               |              |              |                 |                |                 | I                             |                                     |

| 10h                | PORTA         | RBPU         | _                                    | RA5           | RA4          | RA3          | RA2             | RA1/T0CKI      | RA0/INT         | 0-xx xxxx                     | 0-uu uuuu                           |

| 11h                | DDRB          | Data dire    | ction registe                        | er for PORTE  | 3            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 12h                | PORTB         | PORTB d      | ata latch                            |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | RCSTA         | SPEN         | RX9                                  | SREN          | CREN         | —            | FERR            | OERR           | RX9D            | 0000 -00x                     | 0000 -00u                           |

| 14h                | RCREG         | Serial por   | t receive re                         | gister        |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | TXSTA         | CSRC         | TX9                                  | TXEN          | SYNC         | —            | —               | TRMT           | TX9D            | 00001x                        | 00001u                              |

| 16h                | TXREG         | Serial por   | t transmit re                        | egister       |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | SPBRG         | Baud rate    | generator                            | register      |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| Bank 1             |               |              |                                      |               |              |              |                 |                |                 |                               |                                     |

| 10h                | DDRC          | Data dire    | ction registe                        | er for PORT   | 2            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 11h                | PORTC         | RC7/<br>AD7  | RC6/<br>AD6                          | RC5/<br>AD5   | RC4/<br>AD4  | RC3/<br>AD3  | RC2/<br>AD2     | RC1/<br>AD1    | RC0/<br>AD0     | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | DDRD          | Data dire    | ction registe                        | er for PORTI  | )            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 4.01-              | PORTD         | RD7/<br>AD15 | RD6/<br>AD14                         | RD5/<br>AD13  | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10    | RD1/<br>AD9    | RD0/<br>AD8     | xxxx xxxx                     | uuuu uuuu                           |

| 13h                |               | Data dira    | Data direction register for PORTE111 |               |              |              |                 |                |                 |                               |                                     |

| 13h<br>14h         | DDRE          | Data dire    |                                      |               |              |              |                 | -              |                 |                               |                                     |

|                    | DDRE<br>PORTE | Data dire    | _                                    | _             | _            | _            | RE2/WR          | RE1/OE         | RE0/ALE         | xxx                           | uuu                                 |

| 14h                |               | RBIF         | —<br>TMR3IF                          | —<br>TMR2IF   | —<br>TMR1IF  | —<br>CA2IF   | RE2/WR<br>CA1IF | RE1/OE<br>TXIF | RE0/ALE<br>RCIF | xxx<br>0000 0010              | uuu<br>0000 0010                    |

x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated Legend: Note 1:

from or transferred to the upper byte of the program counter. The TO and PD status bits in CPUSTA are not affected by a MCLR reset. 2:

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

4:

The following values are for both TBLPTRL and TBLPTRH: All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000) except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu)

5: The PRODL and PRODH registers are not implemented on the PIC17C42.

# 8.0 HARDWARE MULTIPLIER

All PIC17C4X devices except the PIC17C42, have an 8 x 8 hardware multiplier included in the ALU of the device. By making the multiply a hardware operation, it completes in a single instruction cycle. This is an unsigned multiply that gives a 16-bit result. The result is stored into the 16-bit PRODuct register (PRODH:PRODL). The multiplier does not affect any flags in the ALUSTA register.

Making the 8 x 8 multiplier execute in a single cycle gives the following advantages:

- Higher computational throughput

- Reduces code size requirements for multiply algorithms

The performance increase allows the device to be used in applications previously reserved for Digital Signal Processors.

Table 8-1 shows a performance comparison between the PIC17C42 and all other PIC17CXX devices, which have the single cycle hardware multiply.

Example 8-1 shows the sequence to do an 8 x 8 unsigned multiply. Only one instruction is required when one argument of the multiply is already loaded in the WREG register.

Example 8-2 shows the sequence to do an  $8 \times 8$  signed multiply. To account for the sign bits of the arguments, each argument's most significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 8-1: 8 x 8 MULTIPLY ROUTINE

| MOVFP | ARG1, | WREG |   |      |    |        |    |

|-------|-------|------|---|------|----|--------|----|

| MULWF | ARG2  |      | ; | ARG1 | *  | ARG2   | -> |

|       |       |      | ; | PRO  | DD | H:PROI | ЪГ |

#### EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVFP | ARG1, WREG |                  |

|-------|------------|------------------|

| MULWF | ARG2       | ; ARG1 * ARG2 -> |

|       |            | ; PRODH:PRODL    |

| BTFSC | ARG2, SB   | ; Test Sign Bit  |

| SUBWF | PRODH, F   | ; PRODH = PRODH  |

|       |            | ; – ARG1         |

| MOVFP | ARG2, WREG |                  |

| BTFSC | ARG1, SB   | ; Test Sign Bit  |

| SUBWF | PRODH, F   | ; PRODH = PRODH  |

|       |            | ; – ARG2         |

| Routine          | Device                     | Program Memory |              | Time                                          |          |  |

|------------------|----------------------------|----------------|--------------|-----------------------------------------------|----------|--|

| Routine          | Device                     | (Words)        | Cycles (Max) | @ 25 MHz<br>11.04 μs<br>160 ns<br>—<br>960 ns | @ 33 MHz |  |

| 8 x 8 unsigned   | PIC17C42                   | 13             | 69           | 11.04 μs                                      | N/A      |  |

|                  | All other PIC17CXX devices | 1              | 1            | 160 ns                                        | 121 ns   |  |

| 8 x 8 signed     | PIC17C42                   | _              |              | _                                             | N/A      |  |

|                  | All other PIC17CXX devices | 6              | 6            | 960 ns                                        | 727 ns   |  |

| 16 x 16 unsigned | PIC17C42                   | 21             | 242          | 38.72 μs                                      | N/A      |  |

|                  | All other PIC17CXX devices | 24             | 24           | 3.84 μs                                       | 2.91 μs  |  |

| 16 x 16 signed   | PIC17C42                   | 52             | 254          | 40.64 μs                                      | N/A      |  |

|                  | All other PIC17CXX devices | 36             | 36           | 5.76 μs                                       | 4.36 µs  |  |

#### TABLE 8-1: PERFORMANCE COMPARISON

# TABLE 9-7: PORTD FUNCTIONS

| Name     | Bit  | Buffer Type | Function                                     |

|----------|------|-------------|----------------------------------------------|

| RD0/AD8  | bit0 | TTL         | Input/Output or system bus address/data pin. |

| RD1/AD9  | bit1 | TTL         | Input/Output or system bus address/data pin. |

| RD2/AD10 | bit2 | TTL         | Input/Output or system bus address/data pin. |

| RD3/AD11 | bit3 | TTL         | Input/Output or system bus address/data pin. |

| RD4/AD12 | bit4 | TTL         | Input/Output or system bus address/data pin. |

| RD5/AD13 | bit5 | TTL         | Input/Output or system bus address/data pin. |

| RD6/AD14 | bit6 | TTL         | Input/Output or system bus address/data pin. |

| RD7/AD15 | bit7 | TTL         | Input/Output or system bus address/data pin. |

Legend: TTL = TTL input.

# TABLE 9-8: REGISTERS/BITS ASSOCIATED WITH PORTD

| Address     | Name  | Bit 7        | Bit 6                             | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0       | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|--------------|-----------------------------------|--------------|--------------|--------------|--------------|-------------|-------------|-------------------------------|-----------------------------------------|

| 13h, Bank 1 | PORTD | RD7/<br>AD15 | RD6/<br>AD14                      | RD5/<br>AD13 | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10 | RD1/<br>AD9 | RD0/<br>AD8 | XXXX XXXX                     | uuuu uuuu                               |

| 12h, Bank 1 | DDRD  | Data direc   | Data direction register for PORTD |              |              |              |              |             | 1111 1111   | 1111 1111                     |                                         |

Legend: x = unknown, u = unchanged.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

# 10.0 OVERVIEW OF TIMER RESOURCES

The PIC17C4X has four timer modules. Each module can generate an interrupt to indicate that an event has occurred. These timers are called:

- Timer0 16-bit timer with programmable 8-bit

- prescaler

- Timer1 8-bit timer

- Timer2 8-bit timer

- Timer3 16-bit timer

For enhanced time-base functionality, two input Captures and two Pulse Width Modulation (PWM) outputs are possible. The PWMs use the TMR1 and TMR2 resources and the input Captures use the TMR3 resource.

#### 10.1 <u>Timer0 Overview</u>

The Timer0 module is a simple 16-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock.

The Timer0 module also has a programmable prescaler option. The PS3:PS0 bits (T0STA<4:1>) determine the prescaler value. TMR0 can increment at the following rates: 1:1, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, 1:256.

When TImer0's clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

#### 10.2 <u>Timer1 Overview</u>

The TImer0 module is an 8-bit timer/counter with an 8bit period register (PR1). When the TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the Timer2 module.

TMR1 can be concatenated to TMR2 to form a 16-bit timer. The TMR1 register is the LSB and TMR2 is the MSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled.

### 10.3 <u>Timer2 Overview</u>

The TMR2 module is an 8-bit timer/counter with an 8bit period register (PR2). When the TMR2 value rolls over from the period match value to 0h, the TMR2IF flag is set, and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the TMR1 module.

TMR1 can be concatenated to TMR2 to form a 16-bit timer. The TMR2 register is the MSB and TMR1 is the LSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled.

#### 10.4 <u>Timer3 Overview</u>

The TImer3 module is a 16-bit timer/counter with a 16bit period register. When the TMR3H:TMR3L value rolls over to 0h, the TMR3IF bit is set and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB5/TCLK3 pin.

When operating in the dual capture mode, the period registers become the second 16-bit capture register.

### 10.5 Role of the Timer/Counters

The timer modules are general purpose, but have dedicated resources associated with them. Tlmer1 and Timer2 are the time-bases for the two Pulse Width Modulation (PWM) outputs, while Timer3 is the timebase for the two input captures.

© 1996 Microchip Technology Inc.

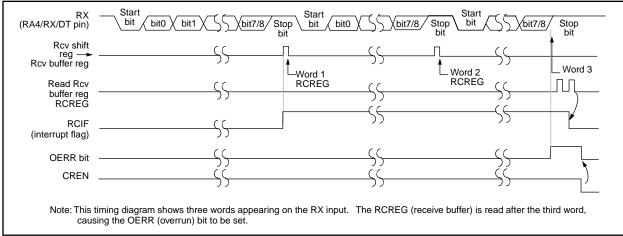

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

#### FIGURE 13-8: ASYNCHRONOUS RECEPTION

| <b>TABLE 13-6:</b> | <b>REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION</b> |

|--------------------|---------------------------------------------------------|

|                    |                                                         |

| Address     | Name                                   | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|----------------------------------------|-------|--------|--------|--------|-------|-------|-------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR                                    | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF      | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA                                  | SPEN  | RX9    | SREN   | CREN   | —     | FERR  | OERR  | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0 | RCREG                                  | RX7   | RX6    | RX5    | RX4    | RX3   | RX2   | RX1   | RX0       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE                                    | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE      | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA                                  | CSRC  | TX9    | TXEN   | SYNC   | —     | —     | TRMT  | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 | k 0 SPBRG Baud rate generator register |       |        |        |        |       |       |       | xxxx xxxx | uuuu uuuu                     |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous reception. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

#### 14.1 Configuration Bits

The PIC17CXX has up to seven configuration locations (Table 14-1). These locations can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. Any write to a configuration location, regardless of the data, will program that configuration bit. A TABLWT instruction is required to write to program memory locations. The configuration bits can be read by using the TABLRD instructions. Reading any configuration location between FE00h and FE07h will read the low byte of the configuration word (Figure 14-1) into the TABLATL register. The TABLATH register will be FFh. Reading a configuration location between FE08h and FE0Fh will read the high byte of the configuration word into the TABLATL register. The TABLATH register will be FFh.

Addresses FE00h thorough FE0Fh are only in the program memory space for microcontroller and code protected microcontroller modes. A device programmer will be able to read the configuration word in any processor mode. See programming specifications for more detail.

#### TABLE 14-1: CONFIGURATION LOCATIONS

| Bit                | Address              |

|--------------------|----------------------|

| FOSC0              | FE00h                |

| FOSC1              | FE01h                |

| WDTPS0             | FE02h                |

| WDTPS1             | FE03h                |

| PM0                | FE04h                |

| PM1                | FE06h                |

| PM2 <sup>(1)</sup> | FE0Fh <sup>(1)</sup> |

Note 1: This location does not exist on the PIC17C42.

| Note: | When programming the desired configura-    |        |          |      |         |

|-------|--------------------------------------------|--------|----------|------|---------|

|       | tion locations, they must be programmed in |        |          |      |         |

|       | ascending                                  | order. | Starting | with | address |

|       | FE00h.                                     |        |          |      |         |

#### 14.2 Oscillator Configurations

#### 14.2.1 OSCILLATOR TYPES

The PIC17CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LF: Low Power Crystal

- XT: Crystal/Resonator

- EC: External Clock Input

- RC: Resistor/Capacitor

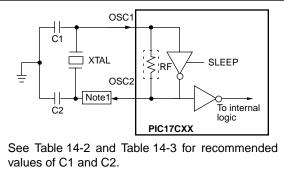

# 14.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT or LF modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 14-2). The PIC17CXX Oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications.

For frequencies above 20 MHz, it is common for the crystal to be an overtone mode crystal. Use of overtone mode crystals require a tank circuit to attenuate the gain at the fundamental frequency. Figure 14-3 shows an example of this.

#### FIGURE 14-2: CRYSTAL OR CERAMIC RESONATOR OPERATION (XT OR LF OSC CONFIGURATION)

Note 1: A series resistor may be required for AT strip cut crystals.

#### 14.4 Power-down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction. This clears the Watchdog Timer and postscaler (if enabled). The  $\overrightarrow{PD}$  bit is cleared and the  $\overrightarrow{TO}$  bit is set (in the CPUSTA register). In SLEEP mode, the oscillator driver is turned off. The I/O ports maintain their status (driving high, low, or hi-impedance).

The  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level (VIHMC). A WDT time-out RESET does not drive the  $\overline{\text{MCLR}}/\text{VPP}$  pin low.

#### 14.4.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- A POR reset

- External reset input on MCLR/VPP pin

- WDT Reset (if WDT was enabled)

- Interrupt from RA0/INT pin, RB port change, T0CKI interrupt, or some Peripheral Interrupts

The following peripheral interrupts can wake-up from SLEEP:

- · Capture1 interrupt

- Capture2 interrupt

- · USART synchronous slave transmit interrupt

- · USART synchronous slave receive interrupt

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

Any reset event will cause a device reset. Any interrupt event is considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the CPUSTA register can be used to determine the cause of device reset. The

$\overline{PD}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{TO}$  bit is cleared if WDT time-out occurred (and caused wake-up).

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GLINTD bit. If the GLINTD bit is set (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GLINTD bit is clear (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt vector address. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

Note: If the global interrupts are disabled (GLINTD is set), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from sleep. The TO bit is set, and the PD bit is cleared.

The WDT is cleared when the device wake from SLEEP, regardless of the source of wake-up.

14.4.1.1 WAKE-UP DELAY

When the oscillator type is configured in XT or LF mode, the Oscillator Start-up Timer (OST) is activated on wake-up. The OST will keep the device in reset for 1024Tosc. This needs to be taken into account when considering the interrupt response time when coming out of SLEEP.

#### FIGURE 14-9: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                                                                                                                                                                                                                                                                                                                                                        | Q1   Q2   Q3   Q4                     | Q1   Q2   Q3   Q4 | Q1   Q2   | Q3   Q4 | Q1   Q2  | Q3   Q4                | Q1   Q2   Q3   Q4                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|-----------|---------|----------|------------------------|----------------------------------------------|

| OSC1                                                                                                                                                                                                                                                                                                                                                   |                                       |                   |           |         |          | $\frown \frown \frown$ |                                              |

| CLKOUT(4)                                                                                                                                                                                                                                                                                                                                              |                                       | /                 |           | Tost(2) | \/<br>\/ |                        |                                              |

| INT                                                                                                                                                                                                                                                                                                                                                    |                                       |                   |           |         | I<br>I   |                        |                                              |

| (RA0/INT pin)                                                                                                                                                                                                                                                                                                                                          | ı ı                                   |                   | : (       |         | 1        |                        | <u>1                                    </u> |

| INTF flag                                                                                                                                                                                                                                                                                                                                              |                                       |                   | <u>`</u>  |         | I        |                        | Interrupt Latency (2)                        |

| GLINTD bit                                                                                                                                                                                                                                                                                                                                             | 1<br>11                               |                   | · ·       |         | I        |                        | ·                                            |

|                                                                                                                                                                                                                                                                                                                                                        | , , , , , , , , , , , , , , , , , , , |                   | Processor |         | 1        |                        | 1 I                                          |

| INSTRUCTION                                                                                                                                                                                                                                                                                                                                            | FLOW                                  |                   | in SLEEP  |         | 1<br>1   |                        | I I<br>I I                                   |

| PC                                                                                                                                                                                                                                                                                                                                                     | C PC                                  | PC+1              |           | +2      | × 0004   | h                      | × <u>0005h</u>                               |

| Instruction (<br>fetched                                                                                                                                                                                                                                                                                                                               | Inst (PC) = SLEEP                     | Inst (PC+1)       |           |         | Inst (PC | +2)                    |                                              |

| Instruction {                                                                                                                                                                                                                                                                                                                                          | Inst (PC-1)                           | SLEEP             |           |         | Inst (PC | +1)                    | Dummy Cycle                                  |

| Note 1: XT or LF oscillator mode assumed.<br>2: Tost = 1024Tosc (drawing not to scale). This delay will not be there for RC osc mode.<br>3: When GLINTD = 0 processor jumps to interrupt routine after wake-up. If GLINTD = 1, execution will continue in line.<br>4: CLKOUT is not available in these osc modes, but shown here for timing reference. |                                       |                   |           |         |          |                        |                                              |

NOTES:

# PIC17C4X

## Applicable Devices 42 R42 42A 43 R43 44

#### 17.2 DC CHARACTERISTICS:

#### PIC17C42-16 (Commercial, Industrial) PIC17C42-25 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated) Operating temperature

#### DC CHARACTERISTICS

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and  $0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

Operating voltage VDD range as described in Section 17.1 Parameter No. Sym Characteristic Min Typ† Max Units Conditions Input Low Voltage VIL I/O ports D030 with TTL buffer Vss 0.8 V D031 with Schmitt Trigger buffer Vss 0.2VDD V \_ D032 MCLR, OSC1 (in EC and RC Vss 0.2Vdd V Note1 \_ mode) D033 OSC1 (in XT, and LF mode) 0.5VDD V \_ Input High Voltage Vн I/O ports V D040 2.0 with TTL buffer \_ Vdd D041 with Schmitt Trigger buffer 0.8VDD Vdd V \_ D042 MCLR 0.8Vdd Vdd Note1 V D043 OSC1 (XT, and LF mode) 0.5VDD V D050 Hysteresis of 0.15VDD\* VHYS V \_ \_ Schmitt Trigger inputs Input Leakage Current (Notes 2, 3) D060 lı∟ I/O ports (except RA2, RA3)  $Vss \leq VPIN \leq VDD$ , ±1 μΑ I/O Pin at hi-impedance PORTB weak pull-ups disabled MCLR D061 <u>+2</u> μA VPIN = Vss or VPIN = VDD D062 **RA2, RA3** ±2 μΑ  $Vss \leq VRA2$ ,  $VRA3 \leq 12V$ D063 OSC1, TEST ±1 μΑ  $Vss \le VPIN \le VDD$

D070 IPURB PORTB weak pull-up current 60 These parameters are characterized but not tested.

MCLR

D064

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only t and are not tested.

200

10

400

μA

μΑ

These parameters are for design guidance only and are not tested, nor characterized. t

Design guidance to attain the AC timing specifications. These loads are not tested. ++

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/Vpp pin may be kept in this range at times other than programming, but this is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

VMCLR = VPP = 12V

(when not programming)

VPIN = Vss.  $\overline{RBPU} = 0$

# PIC17C4X

# Applicable Devices 42 R42 42A 43 R43 44

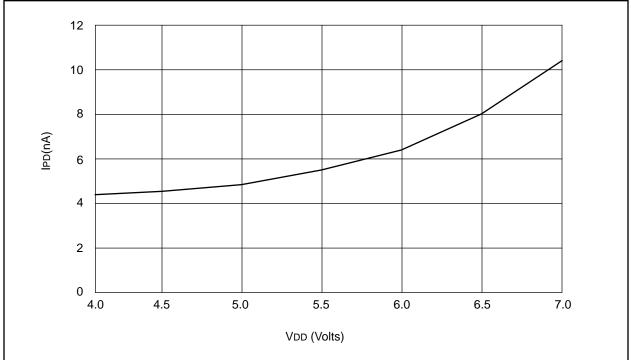

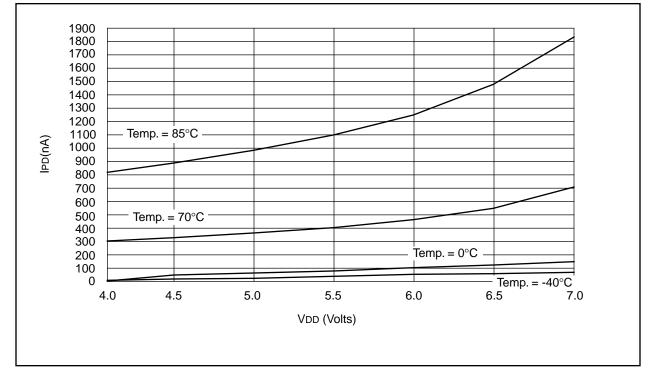

# FIGURE 18-9: TYPICAL IPD vs. VDD WATCHDOG DISABLED 25°C

FIGURE 18-10: MAXIMUM IPD vs. VDD WATCHDOG DISABLED

# Applicable Devices 42 R42 42A 43 R43 44

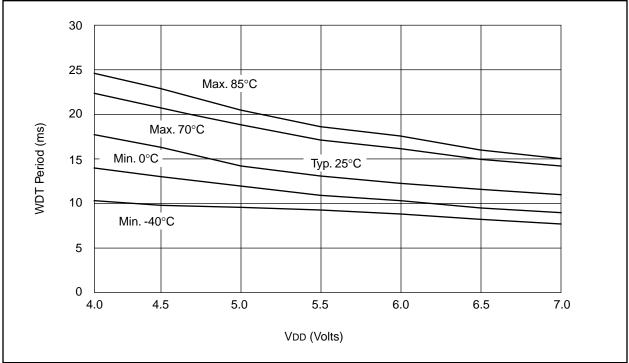

# FIGURE 18-13: WDT TIMER TIME-OUT PERIOD vs. VDD

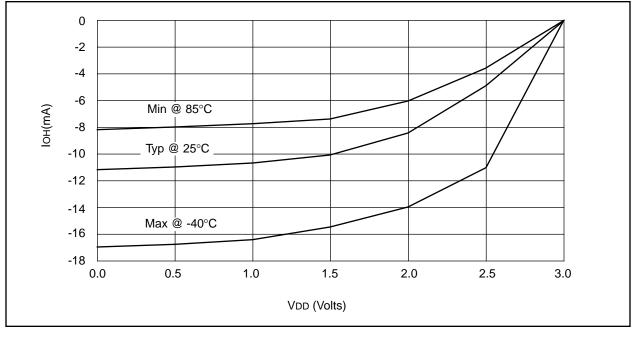

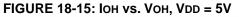

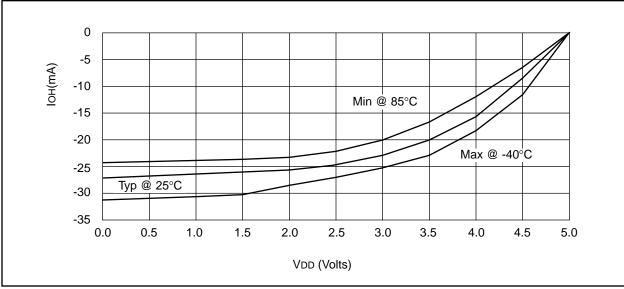

FIGURE 18-14: IOH vs. VOH, VDD = 3V

# PIC17C4X

# Applicable Devices 42 R42 42A 43 R43 44

FIGURE 18-16: IOL vs. VOL, VDD = 3V

#### Applicable Devices 42 R42 42A 43 R43 44

#### 19.3 DC CHARACTERISTICS:

#### PIC17CR42/42A/43/R43/44-16 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-25 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-33 (Commercial, Industrial) PIC17LCR42/42A/43/R43/44-08 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated) Operating temperature

#### DC CHARACTERISTICS

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and 0°C  $\leq$  TA  $\leq$  +70°C for commercial

|           |       |                                         | Operating  | oltago \/r | 0°C       |       | ≤ +70°C for commercial<br>cribed in Section 19.1                                |

|-----------|-------|-----------------------------------------|------------|------------|-----------|-------|---------------------------------------------------------------------------------|

| Parameter | 1     |                                         |            | ollage vi  | D lange a |       |                                                                                 |

| No.       | Sym   | Characteristic                          | Min        | Тур†       | Мах       | Units | Conditions                                                                      |

|           |       | Input Low Voltage                       |            |            |           |       |                                                                                 |

|           | VIL   | I/O ports                               |            |            |           |       |                                                                                 |

| D030      |       | with TTL buffer                         | Vss        | _          | 0.8       | V     | $4.5V \le VDD \le 5.5V$                                                         |

|           |       |                                         | Vss        | _          | 0.2Vdd    | V     | $2.5V \le VDD \le 4.5V$                                                         |

| D031      |       | with Schmitt Trigger buffer             | Vss        | -          | 0.2Vdd    | V     |                                                                                 |

| D032      |       | MCLR, OSC1 (in EC and RC mode)          | Vss        | -          | 0.2Vdd    | V     | Note1                                                                           |

| D033      |       | OSC1 (in XT, and LF mode)               | -          | 0.5Vdd     | _         | V     |                                                                                 |

|           |       | Input High Voltage                      |            |            |           |       |                                                                                 |

|           | VIH   | I/O ports                               |            |            |           |       |                                                                                 |

| D040      |       | with TTL buffer                         | 2.0        | -          | Vdd       | V     | $4.5V \le VDD \le 5.5V$                                                         |

|           |       |                                         | 1 + 0.2VDD | -          | Vdd       | V     | $2.5V \le VDD \le 4.5V$                                                         |

| D041      |       | with Schmitt Trigger buffer             | 0.8Vdd     | -          | Vdd       | V     |                                                                                 |

| D042      |       | MCLR                                    | 0.8Vdd     | _          | Vdd       | V     | Note1                                                                           |

| D043      |       | OSC1 (XT, and LF mode)                  | -          | 0.5Vdd     | _         | V     |                                                                                 |

| D050      | VHYS  | Hysteresis of<br>Schmitt Trigger inputs | 0.15Vdd *  | -          | -         | V     |                                                                                 |

|           |       | Input Leakage Current<br>(Notes 2, 3)   |            |            |           |       |                                                                                 |

| D060      | lı∟   | I/O ports (except RA2, RA3)             | _          | _          | ±1        | μA    | Vss ≤ VPIN ≤ VDD,<br>I/O Pin at hi-impedance<br>PORTB weak pull-ups<br>disabled |

| D061      |       | MCLR                                    | _          | -          | ±2        | μA    | VPIN = Vss or VPIN = VDD                                                        |

| D062      |       | RA2, RA3                                |            |            | ±2        | μΑ    | $Vss \le Vra2$ , $Vra3 \le 12V$                                                 |

| D063      |       | OSC1, TEST (EC, RC modes)               | -          | _          | ±1        | μΑ    | $Vss \le VPIN \le VDD$                                                          |

| D063B     |       | OSC1, TEST (XT, LF modes)               | -          | -          | VPIN      | μA    | RF ≥ 1 MΩ, see Figure 14.2                                                      |

| D064      |       | MCLR                                    | -          | -          | 10        | μA    | VMCLR = VPP = 12V<br>(when not programming)                                     |

| D070      | IPURB | PORTB weak pull-up current              | 60         | 200        | 400       | μA    | VPIN = VSS, $\overline{\text{RBPU}} = 0$<br>4.5V $\leq$ VDD $\leq$ 6.0V         |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

Negative current is defined as coming out of the pin.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

# Applicable Devices 42 R42 42A 43 R43 44

|           |       |                                                  | Standard C<br>Operating te |           |              | ns (ur | nless otherwise stated)                                                                                     |

|-----------|-------|--------------------------------------------------|----------------------------|-----------|--------------|--------|-------------------------------------------------------------------------------------------------------------|

| DC CHARA  | CTERI | STICS                                            |                            | ·         | -40°C<br>0°C |        | ≤ +85°C for industrial and<br>≤ +70°C for commercial                                                        |

|           |       |                                                  | Operating v                | oltage Vi | DD range a   | s desc | ribed in Section 19.1                                                                                       |

| Parameter |       |                                                  |                            |           |              |        |                                                                                                             |

| No.       | Sym   | Characteristic                                   | Min                        | Тур†      | Max          | Units  | Conditions                                                                                                  |

|           |       | Output Low Voltage                               |                            |           |              |        |                                                                                                             |

| D080      | VOL   | I/O ports (except RA2 and RA3)                   |                            |           |              |        | IOL = VDD/1.250 mA                                                                                          |

|           |       |                                                  | _                          | _         | 0.1Vdd       | V      | $4.5V \le VDD \le 6.0V$                                                                                     |

|           |       |                                                  | _                          | _         | 0.1Vdd *     | V      | VDD = 2.5V                                                                                                  |

| D081      |       | with TTL buffer                                  | -                          | _         | 0.4          | V      | IOL = 6 mA, VDD = 4.5V<br>Note 6                                                                            |

| D082      |       | RA2 and RA3                                      | _                          | _         | 3.0          | V      | IOL = 60.0 mA, VDD = 6.0V                                                                                   |

| D083      |       | OSC2/CLKOUT                                      | _                          | _         | 0.4          | V      | IOL = 1 mA, VDD = 4.5V                                                                                      |

| D084      |       | (RC and EC osc modes)                            | _                          | _         | 0.1Vdd *     | V      | IOL = VDD/5 mA                                                                                              |

|           |       |                                                  |                            |           |              |        | (PIC17LC43/LC44 only)                                                                                       |

|           |       | Output High Voltage (Note 3)                     |                            |           |              |        |                                                                                                             |

| D090      | Vон   | I/O ports (except RA2 and RA3)                   |                            |           |              |        | IOH = -VDD/2.500  mA                                                                                        |

|           |       |                                                  | 0.9Vdd                     | _         | -            | V      | $4.5V \le VDD \le 6.0V$                                                                                     |

|           |       |                                                  | 0.9Vdd *                   | -         | -            | V      | VDD = 2.5V                                                                                                  |

| D091      |       | with TTL buffer                                  | 2.4                        | _         | _            | V      | IOH = -6.0 mA, VDD=4.5V<br>Note 6                                                                           |

| D092      |       | RA2 and RA3                                      | -                          | _         | 12           | V      | Pulled-up to externally applied voltage                                                                     |

| D093      |       | OSC2/CLKOUT                                      | 2.4                        | _         | _            | v      | IOH = -5  mA,  VDD = 4.5  V                                                                                 |

| D094      |       | (RC and EC osc modes)                            | 0.9Vdd *                   | _         | _            | V      | IOH = -VDD/5 mA                                                                                             |

|           |       | ,<br>,<br>,                                      |                            |           |              |        | (PIC17LC43/LC44 only)                                                                                       |

|           |       | Capacitive Loading Specs<br>on Output Pins       |                            |           |              |        |                                                                                                             |

| D100      | Cosc2 | OSC2/CLKOUT pin                                  | _                          | _         | 25           | pF     | In EC or RC osc modes<br>when OSC2 pin is outputting<br>CLKOUT.<br>external clock is used to<br>drive OSC1. |

| D101      | Сю    | All I/O pins and OSC2<br>(in RC mode)            | _                          | _         | 50           | pF     |                                                                                                             |

| D102      | CAD   | System Interface Bus<br>(PORTC, PORTD and PORTE) | _                          | _         | 50           | pF     | In Microprocessor or<br>Extended Microcontroller<br>mode                                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.