Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 454 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-16e-pq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

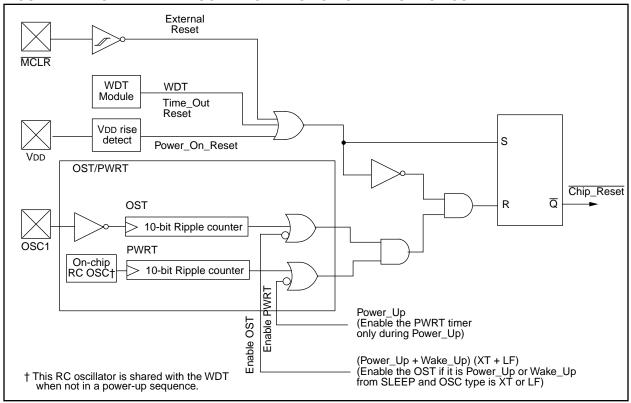

# 4.0 RESET

The PIC17CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- WDT Reset (normal operation)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are forced to a "reset state" on Power-on Reset (POR), on  $\overline{\text{MCLR}}$  or WDT Reset and on  $\overline{\text{MCLR}}$  reset during SLEEP. They are not affected by a WDT Reset during SLEEP, since this reset is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations as indicated in Table 4-3. These bits are used in software to determine the nature of reset. See Table 4-4 for a full description of reset states of all registers.

**Note:** While the device is in a reset state, the internal phase clock is held in the Q1 state. Any processor mode that allows external execution will force the RE0/ALE pin as a low output and the RE1/OE and RE2/WR pins as high outputs.

A simplified block diagram of the on-chip reset circuit is shown in Figure 4-1.

### 4.1 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT), and Oscillator Start-up</u> <u>Timer (OST)</u>

### 4.1.1 POWER-ON RESET (POR)

The Power-on Reset circuit holds the device in reset until VDD is above the trip point (in the range of 1.4V -2.3V). The PIC17C42 does not produce an internal reset when VDD declines. All other devices will produce an internal reset for both rising and falling VDD. To take advantage of the POR, just tie the MCLR/VPP pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD is required. See Electrical Specifications for details.

### 4.1.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 96 ms time-out (nominal) on power-up. This occurs from rising edge of the POR signal and after the first rising edge of  $\overline{\text{MCLR}}$  (detected high). The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. In most cases the PWRT delay allows the VDD to rise to an acceptable level.

The power-up time delay will vary from chip to chip and to VDD and temperature. See DC parameters for details.

### FIGURE 4-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

© 1996 Microchip Technology Inc.

| TABLE 6-3: | SPECIAL FUNCTION REGISTERS |

|------------|----------------------------|

|------------|----------------------------|

| Address            | Name          | Bit 7        | Bit 6                             | Bit 5         | Bit 4        | Bit 3        | Bit 2           | Bit 1          | Bit 0           | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|---------------|--------------|-----------------------------------|---------------|--------------|--------------|-----------------|----------------|-----------------|-------------------------------|-------------------------------------|

| Unbank             | ed            | •            |                                   |               |              | •            |                 |                | •               |                               |                                     |

| 00h                | INDF0         | Uses con     | tents of FSI                      | R0 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 01h                | FSR0          | Indirect d   | ata memory                        | address po    | inter 0      |              |                 |                |                 | XXXX XXXX                     | uuuu uuuu                           |

| 02h                | PCL           | Low orde     | r 8-bits of P                     | С             |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | PCLATH        | Holding re   | egister for u                     | pper 8-bits o | of PC        |              |                 |                |                 | 0000 0000                     | uuuu uuuu                           |

| 04h                | ALUSTA        | FS3          | FS2                               | FS1           | FS0          | OV           | Z               | DC             | С               | 1111 xxxx                     | 1111 uuuu                           |

| 05h                | TOSTA         | INTEDG       | TOSE                              | TOCS          | PS3          | PS2          | PS1             | PS0            | —               | 0000 000-                     | 0000 000-                           |

| 06h <b>(2)</b>     | CPUSTA        | _            | _                                 | STKAV         | GLINTD       | TO           | PD              | _              | _               | 11 11                         | 11 qq                               |

| 07h                | INTSTA        | PEIF         | TOCKIF                            | T0IF          | INTF         | PEIE         | TOCKIE          | TOIE           | INTE            | 0000 0000                     | 0000 0000                           |

| 08h                | INDF1         | Uses con     | tents of FSI                      | R1 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 09h                | FSR1          | Indirect d   | ata memory                        | address po    | inter 1      |              | , ,             |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ah                | WREG          | Working r    | egister                           |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Bh                | TMR0L         | TMR0 reg     | gister; low b                     | yte           |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ch                | TMR0H         | TMR0 reg     | gister; high I                    | oyte          |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Dh                | TBLPTRL       | Low byte     | of program                        | memory tab    | le pointer   |              |                 |                |                 | (4)                           | (4)                                 |

| 0Eh                | TBLPTRH       | High byte    | of program                        | memory tal    | ole pointer  |              |                 |                |                 | (4)                           | (4)                                 |

| 0Fh                | BSR           | Bank sele    | ect register                      |               |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| Bank 0             |               | 1            |                                   |               |              |              |                 |                |                 | I                             |                                     |

| 10h                | PORTA         | RBPU         | _                                 | RA5           | RA4          | RA3          | RA2             | RA1/T0CKI      | RA0/INT         | 0-xx xxxx                     | 0-uu uuuu                           |

| 11h                | DDRB          | Data dire    | ction registe                     | er for PORTE  | 3            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 12h                | PORTB         | PORTB d      | ata latch                         |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | RCSTA         | SPEN         | RX9                               | SREN          | CREN         | —            | FERR            | OERR           | RX9D            | 0000 -00x                     | 0000 -00u                           |

| 14h                | RCREG         | Serial por   | t receive re                      | gister        |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | TXSTA         | CSRC         | TX9                               | TXEN          | SYNC         | —            | —               | TRMT           | TX9D            | 00001x                        | 0000lu                              |

| 16h                | TXREG         | Serial por   | t transmit re                     | egister       |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | SPBRG         | Baud rate    | generator                         | register      |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| Bank 1             |               |              |                                   |               |              |              |                 |                |                 |                               |                                     |

| 10h                | DDRC          | Data dire    | ction registe                     | er for PORT   | 2            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 11h                | PORTC         | RC7/<br>AD7  | RC6/<br>AD6                       | RC5/<br>AD5   | RC4/<br>AD4  | RC3/<br>AD3  | RC2/<br>AD2     | RC1/<br>AD1    | RC0/<br>AD0     | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | DDRD          | Data dire    | ction registe                     | er for PORTI  | )            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 4.01-              | PORTD         | RD7/<br>AD15 | RD6/<br>AD14                      | RD5/<br>AD13  | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10    | RD1/<br>AD9    | RD0/<br>AD8     | xxxx xxxx                     | uuuu uuuu                           |

| 13h                |               | Data dira    | -                                 |               |              | 1            |                 | 111            | 111             |                               |                                     |

| 13h<br>14h         | DDRE          | Data dire    | Data direction register for PORTE |               |              |              |                 |                |                 |                               |                                     |

|                    | DDRE<br>PORTE | Data dire    | _                                 | _             | _            | _            | RE2/WR          | RE1/OE         | RE0/ALE         | xxx                           | uuu                                 |

| 14h                |               | RBIF         | —<br>TMR3IF                       | —<br>TMR2IF   | —<br>TMR1IF  | —<br>CA2IF   | RE2/WR<br>CA1IF | RE1/OE<br>TXIF | RE0/ALE<br>RCIF | xxx<br>0000 0010              | uuu<br>0000 0010                    |

x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated Legend: Note 1:

from or transferred to the upper byte of the program counter. The TO and PD status bits in CPUSTA are not affected by a MCLR reset. 2:

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

4:

The following values are for both TBLPTRL and TBLPTRH: All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000) except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu)

5: The PRODL and PRODH registers are not implemented on the PIC17C42.

#### 6.2.2.3 TMR0 STATUS/CONTROL REGISTER (T0STA)

This register contains various control bits. Bit7 (INTEDG) is used to control the edge upon which a signal on the RA0/INT pin will set the RB0/INT interrupt flag. The other bits configure the Timer0 prescaler and clock source. (Figure 11-1).

### FIGURE 6-9: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

| R/W - 0        | R/W - 0                                                            | R/W - 0                                          | R/W - 0                                                            | R/W - 0                    | R/W - 0                  | R/W - 0     | U - 0 |                                                                                                       |

|----------------|--------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------|----------------------------|--------------------------|-------------|-------|-------------------------------------------------------------------------------------------------------|

| INTEDG<br>bit7 | TOSE                                                               | TOCS                                             | PS3                                                                | PS2                        | PS1                      | PS0         | bit0  | R = Readable bit<br>W = Writable bit<br>U = Unimplemented,<br>reads as '0'<br>-n = Value at POR reset |

| bit 7:         | INTEDG: R<br>This bit sele<br>1 = Rising e<br>0 = Falling e        | ects the ed<br>edge of RA                        | ge upon w<br>0/INT pin g                                           | hich the in<br>generates i | terrupt is d<br>nterrupt | etected.    |       |                                                                                                       |

| bit 6:         |                                                                    | ects the ed<br>S = 0<br>edge of RA<br>edge of RA | ge upon w<br>1/T0CKI pi                                            | hich TMRC                  | nts TMR0 a               | and/or gene |       | CKIF interrupt<br>CKIF interrupt                                                                      |

| bit 5:         | <b>TOCS</b> : Time<br>This bit sele<br>1 = Internal<br>0 = TOCKI   | ects the clo<br>instruction                      | ock source                                                         | for Timer0                 |                          |             |       |                                                                                                       |

| bit 4-1:       | PS3:PS0: 7<br>These bits                                           |                                                  |                                                                    |                            | ner0.                    |             |       |                                                                                                       |

|                | PS3:PS0                                                            | Pre                                              | scale Valu                                                         | е                          |                          |             |       |                                                                                                       |

|                | 0000<br>001<br>0010<br>010<br>0100<br>0101<br>0110<br>0111<br>1xxx |                                                  | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 |                            |                          |             |       |                                                                                                       |

| bit 0:         | Unimplem                                                           | <b>ented</b> : Rea                               | id as '0'                                                          |                            |                          |             |       |                                                                                                       |

#### 6.4.1 INDIRECT ADDRESSING REGISTERS

The PIC17C4X has four registers for indirect addressing. These registers are:

- INDF0 and FSR0

- INDF1 and FSR1

Registers INDF0 and INDF1 are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data. The FSR is an 8-bit register and allows addressing anywhere in the 256-byte data memory address range. For banked memory, the bank of memory accessed is specified by the value in the BSR.

If file INDF0 (or INDF1) itself is read indirectly via an FSR, all '0's are read (Zero bit is set). Similarly, if INDF0 (or INDF1) is written to indirectly, the operation will be equivalent to a NOP, and the status bits are not affected.

#### 6.4.2 INDIRECT ADDRESSING OPERATION

The indirect addressing capability has been enhanced over that of the PIC16CXX family. There are two control bits associated with each FSR register. These two bits configure the FSR register to:

- Auto-decrement the value (address) in the FSR after an indirect access

- Auto-increment the value (address) in the FSR after an indirect access

- No change to the value (address) in the FSR after an indirect access

These control bits are located in the ALUSTA register. The FSR1 register is controlled by the FS3:FS2 bits and FSR0 is controlled by the FS1:FS0 bits.

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the ALUSTA register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

If the FSR register contains a value of 0h, an indirect read will read 0h (Zero bit is set) while an indirect write will be equivalent to a NOP (status bits are not affected).

Indirect addressing allows single cycle data transfers within the entire data space. This is possible with the use of the MOVPF and MOVFP instructions, where either 'p' or 'f' is specified as INDF0 (or INDF1).

If the source or destination of the indirect address is in banked memory, the location accessed will be determined by the value in the BSR. A simple program to clear RAM from 20h - FFh is shown in Example 6-1.

### EXAMPLE 6-1: INDIRECT ADDRESSING

|    | MOVLW  | 0x20        | ;           |           |

|----|--------|-------------|-------------|-----------|

|    | MOVWF  | FSR0        | ; FSR0 = 20 | h         |

|    | BCF    | ALUSTA, FS1 | ; Increment | FSR       |

|    | BSF    | ALUSTA, FSO | ; after acc | ess       |

|    | BCF    | ALUSTA, C   | ; C = 0     |           |

|    | MOVLW  | END_RAM + 1 | ;           |           |

| LP | CLRF   | INDF0       | ; Addr(FSR) | = 0       |

|    | CPFSEQ | FSR0        | ; FSRO = EN | ID_RAM+1? |

|    | GOTO   | LP          | ; NO, clear | next      |

|    | :      |             | ; YES, All  | RAM is    |

|    | :      |             | ; cleared   |           |

|    |        |             |             |           |

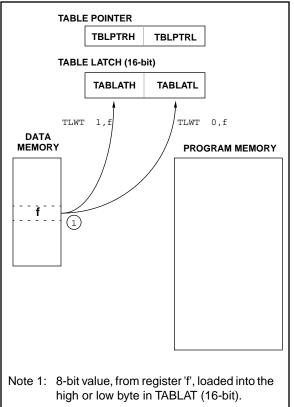

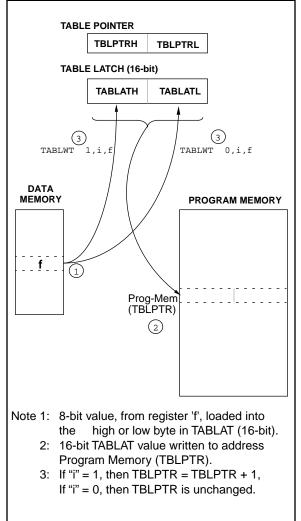

#### 6.5 <u>Table Pointer (TBLPTRL and</u> <u>TBLPTRH)</u>

File registers TBLPTRL and TBLPTRH form a 16-bit pointer to address the 64K program memory space. The table pointer is used by instructions TABLWT and TABLRD.

The TABLRD and the TABLWT instructions allow transfer of data between program and data space. The table pointer serves as the 16-bit address of the data word within the program memory. For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 7.0.

### 6.6 <u>Table Latch (TBLATH, TBLATL)</u>

The table latch (TBLAT) is a 16-bit register, with TBLATH and TBLATL referring to the high and low bytes of the register. It is not mapped into data or program memory. The table latch is used as a temporary holding latch during data transfer between program and data memory (see descriptions of instructions TABLRD, TABLWT, TLRD and TLWT). For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 7.0.

## 7.0 TABLE READS AND TABLE WRITES

The PIC17C4X has four instructions that allow the processor to move data from the data memory space to the program memory space, and vice versa. Since the program memory space is 16-bits wide and the data memory space is 8-bits wide, two operations are required to move 16-bit values to/from the data memory.

The TLWT t,f and TABLWT t,i,f instructions are used to write data from the data memory space to the program memory space. The TLRD t,f and TABLRD t,i,f instructions are used to write data from the program memory space to the data memory space.

The program memory can be internal or external. For the program memory access to be external, the device needs to be operating in extended microcontroller or microprocessor mode.

Figure 7-1 through Figure 7-4 show the operation of these four instructions.

### FIGURE 7-2: TABLWT INSTRUCTION OPERATION

© 1996 Microchip Technology Inc.

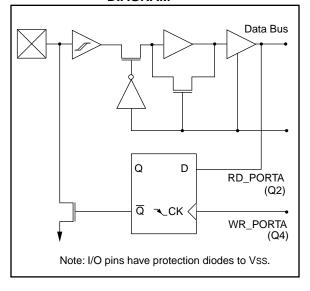

FIGURE 9-2: RA2 AND RA3 BLOCK DIAGRAM

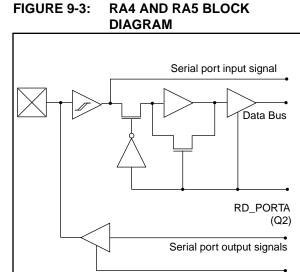

$\overline{OE}$  = SPEN,SYNC,TXEN,  $\overline{CREN}$ ,  $\overline{SREN}$  for RA4  $\overline{OE}$  = SPEN ( $\overline{SYNC}$ +SYNC, $\overline{CSRC}$ ) for RA5

Note: I/O pins have protection diodes to VDD and VSS.

| TABLE 9-1: | PO | RTA FUNCTI | ONS |

|------------|----|------------|-----|

|            |    |            |     |

. . . . .

\_ \_ \_ \_ \_ . . . . . . . . . . . . . .

| Name      | Bit0 | Buffer Type | Function                                                                            |

|-----------|------|-------------|-------------------------------------------------------------------------------------|

| RA0/INT   | bit0 | ST          | Input or external interrupt input.                                                  |

| RA1/T0CKI | bit1 | ST          | Input or clock input to the TMR0 timer/counter, and/or an external interrupt input. |

| RA2       | bit2 | ST          | Input/Output. Output is open drain type.                                            |

| RA3       | bit3 | ST          | Input/Output. Output is open drain type.                                            |

| RA4/RX/DT | bit4 | ST          | Input or USART Asynchronous Receive or USART Synchronous Data.                      |

| RA5/TX/CK | bit5 | ST          | Input or USART Asynchronous Transmit or USART Synchronous Clock.                    |

| RBPU      | bit7 |             | Control bit for PORTB weak pull-ups.                                                |

Legend: ST = Schmitt Trigger input.

### TABLE 9-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address       | Name  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|-------|--------|-------|-------|-------|-------|-------|-----------|---------|-------------------------------|-----------------------------------------|

| 10h, Bank 0   | PORTA | RBPU   | _     | RA5   | RA4   | RA3   | RA2   | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                               |

| 05h, Unbanked | TOSTA | INTEDG | T0SE  | TOCS  | PS3   | PS2   | PS1   | PS0       | _       | 0000 000-                     | 0000 000-                               |

| 13h, Bank 0   | RCSTA | SPEN   | RC9   | SREN  | CREN  | —     | FERR  | OERR      | RC9D    | 0000 -00x                     | 0000 -00u                               |

| 15h, Bank 0   | TXSTA | CSRC   | TX9   | TXEN  | SYNC  | _     | —     | TRMT      | TX9D    | 00001x                        | 0000lu                                  |

Legend: x = unknown, u = unchanged, - = unimplemented reads as '0'. Shaded cells are not used by PORTA. Note 1: Other (non power-up) resets include: external reset through  $\overline{MCLR}$  and the Watchdog Timer Reset.

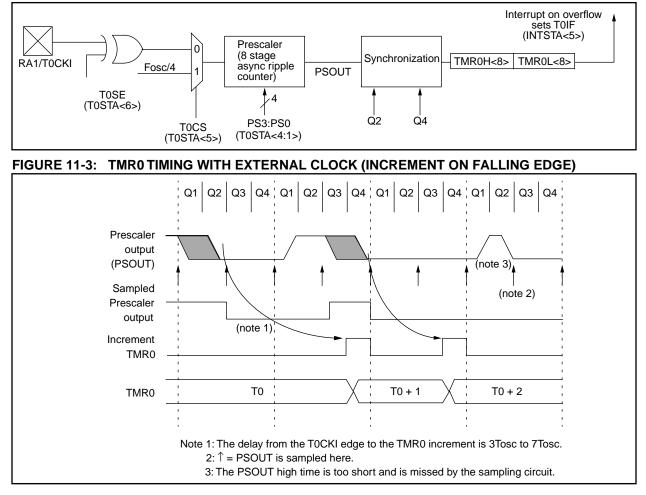

### 11.1 <u>Timer0 Operation</u>

When the TOCS (TOSTA<5>) bit is set, TMR0 increments on the internal clock. When TOCS is clear, TMR0 increments on the external clock (RA1/T0CKI pin). The external clock edge can be configured in software. When the TOSE (TOSTA<6>) bit is set, the timer will increment on the rising edge of the RA1/T0CKI pin. When T0SE is clear, the timer will increment on the falling edge of the RA1/T0CKI pin. The prescaler can be programmed to introduce a prescale of 1:1 to 1:256. The timer increments from 0000h to FFFFh and rolls over to 0000h. On overflow, the TMR0 Interrupt Flag bit (T0IF) is set. The TMR0 interrupt can be masked by clearing the corresponding TMR0 Interrupt Enable bit (T0IE). The TMR0 Interrupt Flag bit (T0IF) is automatically cleared when vectoring to the TMR0 interrupt vector.

### 11.2 Using Timer0 with External Clock

When the external clock input is used for Timer0, it is synchronized with the internal phase clocks. Figure 11-3 shows the synchronization of the external clock. This synchronization is done after the prescaler. The output of the prescaler (PSOUT) is sampled twice in every instruction cycle to detect a rising or a falling edge. The timing requirements for the external clock are detailed in the electrical specification section for the desired device.

### 11.2.1 DELAY FROM EXTERNAL CLOCK EDGE

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time TMR0 is actually incremented. Figure 11-3 shows that this delay is between 3Tosc and 7Tosc. Thus, for example, measuring the interval between two edges (e.g. period) will be accurate within  $\pm$ 4Tosc ( $\pm$ 121 ns @ 33 MHz).

### FIGURE 11-2: TIMER0 MODULE BLOCK DIAGRAM

| ADD         | WFC                                                                                     | ADD WRE                                               | G and C                     | Carry bit            | to f                     |

|-------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------|----------------------|--------------------------|

| Synt        | ax:                                                                                     | [ <i>label</i> ] A[                                   | DDWFC                       | f,d                  |                          |

| Ope         | rands:                                                                                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]                              | 5                           |                      |                          |

| Ope         | ration:                                                                                 | (WREG) +                                              | - (f) + C -                 | $\rightarrow$ (dest) |                          |

| Statu       | us Affected:                                                                            | OV, C, DC                                             | , Z                         |                      |                          |

| Enco        | oding:                                                                                  | 0001                                                  | 000d                        | ffff                 | ffff                     |

| Desc        | cription:                                                                               | Add WREG<br>memory loc<br>placed in W<br>placed in da | ation 'f'. If<br>REG. If 'c | 'd' is 0, the        | e result is<br>result is |

| Word        | ds:                                                                                     | 1                                                     |                             |                      |                          |

| Cycl        | es:                                                                                     | 1                                                     |                             |                      |                          |

| QC          | cle Activity:                                                                           |                                                       |                             |                      |                          |

|             | Q1                                                                                      | Q2                                                    | Q3                          |                      | Q4                       |

|             | Decode                                                                                  | Read<br>register 'f'                                  | Execut                      |                      | rite to<br>tination      |

| <u>Exar</u> | <u>mple</u> :                                                                           | ADDWFC                                                | REG                         | 0                    |                          |

|             | Before Instru<br>Carry bit<br>REG<br>WREG<br>After Instruct<br>Carry bit<br>REG<br>WREG | = 1<br>= 0x02<br>= 0x4D                               |                             |                      |                          |

| ANDLW                 | And Lite            | ral with WRI           | EG                               |

|-----------------------|---------------------|------------------------|----------------------------------|

| Syntax:               | [label] A           | ANDLW k                |                                  |

| Operands:             | $0 \le k \le 25$    | 55                     |                                  |

| Operation:            | (WREG)              | .AND. (k) $ ightarrow$ | (WREG)                           |

| Status Affected:      | Z                   |                        |                                  |

| Encoding:             | 1011                | 0101 kk                | kk kkkk                          |

| Description:          |                     |                        | re AND'ed with sult is placed in |

| Words:                | 1                   |                        |                                  |

| Cycles:               | 1                   |                        |                                  |

| Q Cycle Activity:     |                     |                        |                                  |

| Q1                    | Q2                  | Q3                     | Q4                               |

| Decode                | Read literal<br>'k' | Execute                | Write to<br>WREG                 |

| Example:              | ANDLW               | 0x5F                   |                                  |

| Before Instru<br>WREG | uction<br>= 0xA3    |                        |                                  |

| After Instruc<br>WREG | tion<br>= 0x03      |                        |                                  |

| ANDWF                                                  | AND WRE                                                  | EG with                     | f                    |                       |

|--------------------------------------------------------|----------------------------------------------------------|-----------------------------|----------------------|-----------------------|

| Syntax:                                                | [ <i>label</i> ] A                                       | NDWF                        | f,d                  |                       |

| Operands:                                              | $0 \le f \le 255$ $d \in [0,1]$                          | 5                           |                      |                       |

| Operation:                                             | (WREG) .                                                 | AND. (f)                    | $\rightarrow$ (dest) | )                     |

| Status Affected:                                       | Z                                                        |                             |                      |                       |

| Encoding:                                              | 0000                                                     | 101d                        | ffff                 | ffff                  |

| Description:                                           | The conten<br>register 'f'.<br>in WREG. I<br>back in reg | lf 'd' is 0<br>f 'd' is 1 t | the result           | is stored             |

| Words:                                                 | 1                                                        |                             |                      |                       |

| Cycles:                                                | 1                                                        |                             |                      |                       |

| Q Cycle Activity:                                      |                                                          |                             |                      |                       |

| Q1                                                     | Q2                                                       | Q3                          | 3                    | Q4                    |

| Decode                                                 | Read<br>register 'f'                                     | Execu                       |                      | Vrite to<br>stination |

| Example:                                               | ANDWF                                                    | REG, 1                      |                      |                       |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG | = 0x17<br>= 0xC2                                         |                             |                      |                       |

| BCF            |            | Bit Clear                        | f                                 |       |     |                     |  |  |

|----------------|------------|----------------------------------|-----------------------------------|-------|-----|---------------------|--|--|

| Syntax:        |            | [label] E                        | BCF f,I                           | С     |     |                     |  |  |

| Operand        | s:         | $0 \le f \le 25$ $0 \le b \le 7$ | $0 \le f \le 255$ $0 \le b \le 7$ |       |     |                     |  |  |

| Operatio       | n:         | $0 \rightarrow (f < b >$         | -)                                |       |     |                     |  |  |

| Status A       | ffected:   | None                             |                                   |       |     |                     |  |  |

| Encoding       | g:         | 1000                             | 1bbb                              | fff   | f   | ffff                |  |  |

| Descripti      | ion:       | Bit 'b' in re                    | gister 'f' is                     | clear | ed. |                     |  |  |

| Words:         |            | 1                                |                                   |       |     |                     |  |  |

| Cycles:        |            | 1                                |                                   |       |     |                     |  |  |

| Q Cycle        | Activity:  |                                  |                                   |       |     |                     |  |  |

|                | Q1         | Q2                               | Q3                                |       | C   |                     |  |  |

| D              | ecode      | Read<br>register 'f'             | Execu                             | ute   |     | Write<br>gister 'f' |  |  |

| <u>Example</u> | :          | BCF                              | FLAG_R                            | EG,   | 7   |                     |  |  |

|                | r Instruct | EG = 0xC7                        |                                   |       |     |                     |  |  |

|                |            | 20 - 0,47                        |                                   |       |     |                     |  |  |

| DCF       | SNZ                                                          | Decreme                                                                           | ent f, skij                                                                                                                                                                                                                                                                                                                     | o if no                   | ot O                 |  |  |  |  |

|-----------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|--|--|--|--|

| Synt      | tax:                                                         | [ <i>label</i> ] D                                                                | CFSNZ                                                                                                                                                                                                                                                                                                                           | f,d                       |                      |  |  |  |  |

| Operands: |                                                              | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                                           | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                               |                           |                      |  |  |  |  |

| Ope       | ration:                                                      | .,                                                                                | (f) $-1 \rightarrow$ (dest);<br>skip if not 0                                                                                                                                                                                                                                                                                   |                           |                      |  |  |  |  |

| Stat      | us Affected:                                                 | None                                                                              |                                                                                                                                                                                                                                                                                                                                 |                           |                      |  |  |  |  |

| Enc       | oding:                                                       | 0010                                                                              | 011d                                                                                                                                                                                                                                                                                                                            | ffff                      | ffff                 |  |  |  |  |

| Des       | cription:                                                    | mented. If<br>WREG. If<br>back in reg<br>If the resul<br>which is al<br>and an NC | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'.<br>If the result is not 0, the next instruction,<br>which is already fetched, is discarded,<br>and an NOP is executed instead mak-<br>ing it a two-cycle instruction. |                           |                      |  |  |  |  |

| Wor       | ds:                                                          | 1                                                                                 |                                                                                                                                                                                                                                                                                                                                 |                           |                      |  |  |  |  |

| Cycl      | es:                                                          | 1(2)                                                                              |                                                                                                                                                                                                                                                                                                                                 |                           |                      |  |  |  |  |

| QC        | ycle Activity:                                               |                                                                                   |                                                                                                                                                                                                                                                                                                                                 |                           |                      |  |  |  |  |

|           | Q1                                                           | Q2                                                                                | Q2 Q3                                                                                                                                                                                                                                                                                                                           |                           | Q4                   |  |  |  |  |

|           | Decode                                                       | Read<br>register 'f'                                                              | Execu                                                                                                                                                                                                                                                                                                                           | ıte                       | Write to destination |  |  |  |  |

| lf sk     | ip:                                                          |                                                                                   |                                                                                                                                                                                                                                                                                                                                 |                           |                      |  |  |  |  |

|           | Q1                                                           | Q2                                                                                | Q3                                                                                                                                                                                                                                                                                                                              |                           | Q4                   |  |  |  |  |

|           | Forced NOP                                                   | NOP                                                                               | Execu                                                                                                                                                                                                                                                                                                                           | ute                       | NOP                  |  |  |  |  |

| Example:  |                                                              | HERE<br>ZERO<br>NZERO                                                             | DCFSNZ<br>:<br>:                                                                                                                                                                                                                                                                                                                | TEMP                      | P, 1                 |  |  |  |  |

|           | Before Instru<br>TEMP_V                                      |                                                                                   | ?                                                                                                                                                                                                                                                                                                                               |                           |                      |  |  |  |  |

|           | After Instruct<br>TEMP_V<br>If TEMP_<br>PC<br>If TEMP_<br>PC | ALUE =<br>VALUE =<br>=                                                            | 0;<br>Addre:<br>0;                                                                                                                                                                                                                                                                                                              | _VALU<br>ss (ze<br>ss (nz | RO)                  |  |  |  |  |

| Syntax:<br>Operand | de.         | [ label ]                                           | 0010                                                                                                                                                                                                               |      |      |  |  |  |

|--------------------|-------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--|--|--|

| Operand            | 18.         | 0 < k < 8191                                        |                                                                                                                                                                                                                    |      |      |  |  |  |

|                    |             |                                                     | •                                                                                                                                                                                                                  |      |      |  |  |  |

| Operatio           | on:         | k<12:8> -                                           | $\begin{array}{l} k \rightarrow PC < 12:0 >;\\ k < 12:8 > \rightarrow PCLATH < 4:0 >,\\ PC < 15:13 > \rightarrow PCLATH < 7:5 > \end{array}$                                                                       |      |      |  |  |  |

| Status A           | Affected:   | None                                                |                                                                                                                                                                                                                    |      |      |  |  |  |

| Encodin            | ig:         | 110k                                                | kkkk                                                                                                                                                                                                               | kkkk | kkkl |  |  |  |

| Description:       |             | The thirtee<br>loaded into<br>upper eigh<br>PCLATH. | anywhere within an 8K page boundar.<br>The thirteen bit immediate value is<br>loaded into PC bits <12:0>. Then the<br>upper eight bits of PC are loaded into<br>PCLATH. GOTO is always a two-cycle<br>instruction. |      |      |  |  |  |

| Words:             |             | 1                                                   |                                                                                                                                                                                                                    |      |      |  |  |  |

| Cycles:            |             | 2                                                   |                                                                                                                                                                                                                    |      |      |  |  |  |

| Q Cycle            | Activity:   |                                                     |                                                                                                                                                                                                                    |      |      |  |  |  |

|                    | Q1          | Q2                                                  | Q3                                                                                                                                                                                                                 | 5    | Q4   |  |  |  |

| E                  | Decode      | Read literal<br>'k'<7:0>                            | Execu                                                                                                                                                                                                              | ute  | NOP  |  |  |  |

| For                | ced NOP     | NOP                                                 | Execu                                                                                                                                                                                                              | ute  | NOP  |  |  |  |

| Example            | <u>e</u> :  | GOTO THE                                            | RE                                                                                                                                                                                                                 |      |      |  |  |  |

| Afte               | er Instruct | tion                                                |                                                                                                                                                                                                                    |      |      |  |  |  |

|                    | PC =        | Address (TH                                         | HERE )                                                                                                                                                                                                             |      |      |  |  |  |

# 16.0 DEVELOPMENT SUPPORT

### 16.1 <u>Development Tools</u>

The PIC16/17 microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB-SIM Software Simulator

- MPLAB-C (C Compiler)

- Fuzzy logic development system (fuzzyTECH<sup>®</sup>–MP)

### 16.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX and PIC17CXX families. PICMASTER is supplied with the MPLAB<sup>TM</sup> Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

### 16.3 ICEPIC: Low-cost PIC16CXXX In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT<sup>®</sup> through Pentium<sup>™</sup> based machines under Windows 3.x environment. ICEPIC features real time, non-intrusive emulation.

### 16.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC16C5X, PIC16CXXX, PIC17CXX and PIC14000 devices. It can also set configuration and code-protect bits in this mode.

### 16.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923 and PIC16C924 may be supported with an adapter socket.

## Applicable Devices 42 R42 42A 43 R43 44

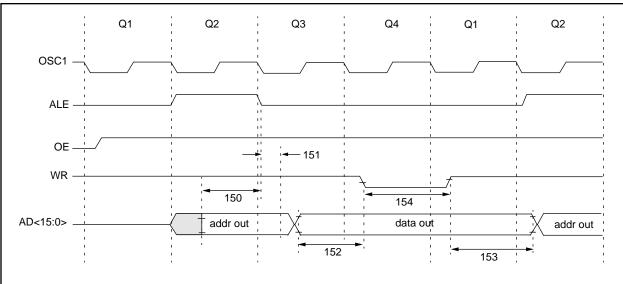

### FIGURE 17-11: MEMORY INTERFACE WRITE TIMING

### TABLE 17-11: MEMORY INTERFACE WRITE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                | Min          | Тур†      | Max | Units | Conditions |

|------------------|----------|---------------------------------------------------------------|--------------|-----------|-----|-------|------------|

| 150              | TadV2alL | AD<15:0> (address) valid to ALE↓<br>(address setup time)      | 0.25Tcy - 30 |           |     | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)               | 0            | _         | _   | ns    |            |

| 152              | TadV2wrL | Data out valid to $\overline{WR}\downarrow$ (data setup time) | 0.25Tcy - 40 | —         | —   | ns    |            |

| 153              | TwrH2adl | WR↑ to data out invalid<br>(data hold time)                   | _            | 0.25Tcy § | _   | ns    |            |

| 154              | TwrL     | WR pulse width                                                | _            | 0.25Tcy § | _   | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification is guaranteed by design.

# Applicable Devices 42 R42 42A 43 R43 44

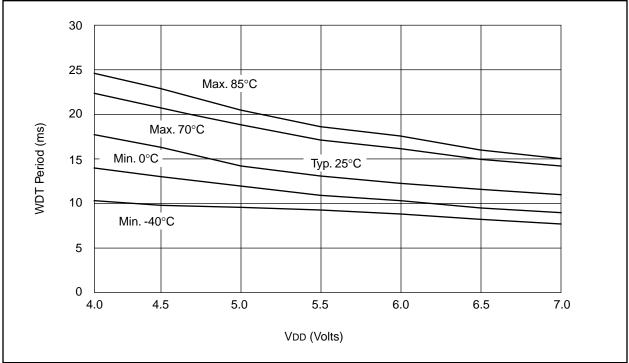

## FIGURE 18-13: WDT TIMER TIME-OUT PERIOD vs. VDD

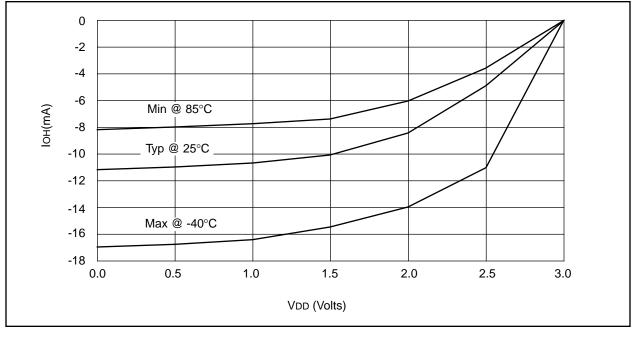

FIGURE 18-14: IOH vs. VOH, VDD = 3V

## Applicable Devices 42 R42 42A 43 R43 44

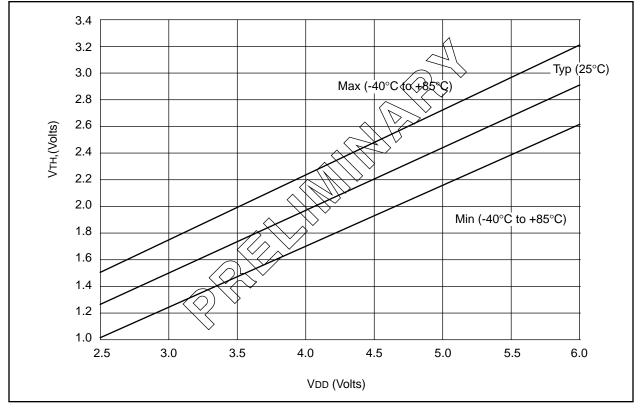

### Applicable Devices 42 R42 42A 43 R43 44

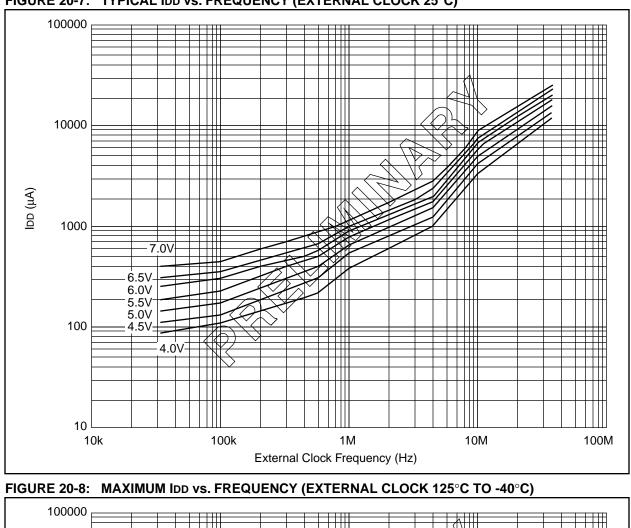

### 19.3 DC CHARACTERISTICS:

### PIC17CR42/42A/43/R43/44-16 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-25 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-33 (Commercial, Industrial) PIC17LCR42/42A/43/R43/44-08 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated) Operating temperature

### DC CHARACTERISTICS

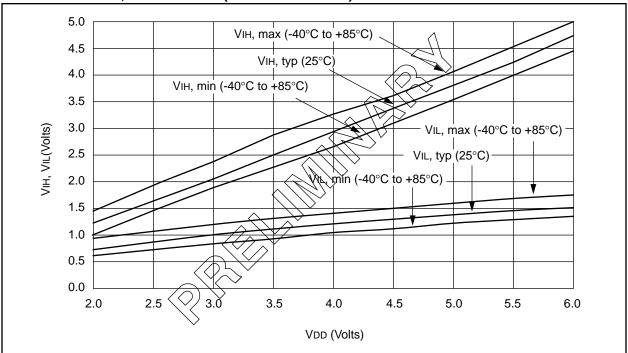

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and 0°C  $\leq$  TA  $\leq$  +70°C for commercial

| $0^{\circ}C = \leq TA \leq +70^{\circ}C$ for commercial<br>Operating voltage VDD range as described in Section 19.1 |       |                                         |            |           |           |       |                                                                                 |

|---------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------|------------|-----------|-----------|-------|---------------------------------------------------------------------------------|

| Parameter                                                                                                           | 1     |                                         |            | ollage vi | D lange a |       |                                                                                 |

| No.                                                                                                                 | Sym   | Characteristic                          | Min        | Тур†      | Мах       | Units | Conditions                                                                      |

|                                                                                                                     |       | Input Low Voltage                       |            |           |           |       |                                                                                 |

|                                                                                                                     | VIL   | I/O ports                               |            |           |           |       |                                                                                 |

| D030                                                                                                                |       | with TTL buffer                         | Vss        | _         | 0.8       | V     | $4.5V \le VDD \le 5.5V$                                                         |

|                                                                                                                     |       |                                         | Vss        | _         | 0.2Vdd    | V     | $2.5V \le VDD \le 4.5V$                                                         |

| D031                                                                                                                |       | with Schmitt Trigger buffer             | Vss        | -         | 0.2Vdd    | V     |                                                                                 |

| D032                                                                                                                |       | MCLR, OSC1 (in EC and RC mode)          | Vss        | -         | 0.2Vdd    | V     | Note1                                                                           |

| D033                                                                                                                |       | OSC1 (in XT, and LF mode)               | -          | 0.5Vdd    | _         | V     |                                                                                 |

|                                                                                                                     |       | Input High Voltage                      |            |           |           |       |                                                                                 |

|                                                                                                                     | VIH   | I/O ports                               |            |           |           |       |                                                                                 |

| D040                                                                                                                |       | with TTL buffer                         | 2.0        | -         | Vdd       | V     | $4.5V \le VDD \le 5.5V$                                                         |

|                                                                                                                     |       |                                         | 1 + 0.2VDD | -         | Vdd       | V     | $2.5V \le VDD \le 4.5V$                                                         |

| D041                                                                                                                |       | with Schmitt Trigger buffer             | 0.8Vdd     | -         | Vdd       | V     |                                                                                 |

| D042                                                                                                                |       | MCLR                                    | 0.8Vdd     | _         | Vdd       | V     | Note1                                                                           |

| D043                                                                                                                |       | OSC1 (XT, and LF mode)                  | -          | 0.5Vdd    | _         | V     |                                                                                 |

| D050                                                                                                                | VHYS  | Hysteresis of<br>Schmitt Trigger inputs | 0.15Vdd *  | -         | -         | V     |                                                                                 |

|                                                                                                                     |       | Input Leakage Current<br>(Notes 2, 3)   |            |           |           |       |                                                                                 |

| D060                                                                                                                | lı∟   | I/O ports (except RA2, RA3)             | _          | _         | ±1        | μA    | Vss ≤ VPIN ≤ VDD,<br>I/O Pin at hi-impedance<br>PORTB weak pull-ups<br>disabled |

| D061                                                                                                                |       | MCLR                                    | _          | -         | ±2        | μA    | VPIN = Vss or VPIN = VDD                                                        |

| D062                                                                                                                |       | RA2, RA3                                |            |           | ±2        | μΑ    | $Vss \le Vra2$ , $Vra3 \le 12V$                                                 |

| D063                                                                                                                |       | OSC1, TEST (EC, RC modes)               | -          | _         | ±1        | μΑ    | $Vss \le VPIN \le VDD$                                                          |

| D063B                                                                                                               |       | OSC1, TEST (XT, LF modes)               | -          | -         | VPIN      | μA    | RF ≥ 1 MΩ, see Figure 14.2                                                      |

| D064                                                                                                                |       | MCLR                                    | -          | -         | 10        | μA    | VMCLR = VPP = 12V<br>(when not programming)                                     |

| D070                                                                                                                | IPURB | PORTB weak pull-up current              | 60         | 200       | 400       | μA    | VPIN = VSS, $\overline{\text{RBPU}} = 0$<br>4.5V $\leq$ VDD $\leq$ 6.0V         |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

Negative current is defined as coming out of the pin.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

# Applicable Devices 42 R42 42A 43 R43 44

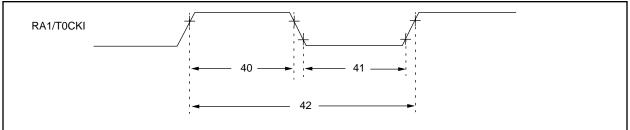

### FIGURE 19-5: TIMER0 CLOCK TIMINGS

### TABLE 19-5: TIMER0 CLOCK REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic         |                | Min                                            | Тур† | Max | Units | Conditions                            |

|------------------|------|------------------------|----------------|------------------------------------------------|------|-----|-------|---------------------------------------|

| 40               | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5Tcy + 20 §                                  | -    | —   | ns    |                                       |

|                  |      |                        | With Prescaler | 10*                                            | -    | _   | ns    |                                       |

| 41               | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5TCY + 20 §                                  | -    | —   | ns    |                                       |

|                  |      |                        | With Prescaler | 10*                                            | -    | —   | ns    |                                       |

| 42               | Tt0P | T0CKI Period           |                | Greater of:<br>20 ns or <u>Tcy + 40 §</u><br>N | -    | _   |       | N = prescale value<br>(1, 2, 4,, 256) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

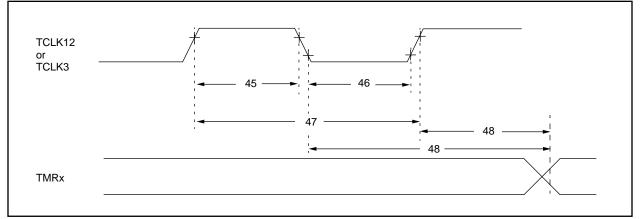

### FIGURE 19-6: TIMER1, TIMER2, AND TIMER3 CLOCK TIMINGS

### TABLE 19-6: TIMER1, TIMER2, AND TIMER3 CLOCK REQUIREMENTS

| Parameter |           |                                                               |                        | Тур |         |       |                                 |

|-----------|-----------|---------------------------------------------------------------|------------------------|-----|---------|-------|---------------------------------|

| No.       | Sym       | Characteristic                                                | Min                    | †   | Max     | Units | Conditions                      |

| 45        | Tt123H    | TCLK12 and TCLK3 high time                                    | 0.5TCY + 20 §          | -   | —       | ns    |                                 |

| 46        | Tt123L    | TCLK12 and TCLK3 low time                                     | 0.5Tcy + 20 §          | _   | —       | ns    |                                 |

| 47        | Tt123P    | TCLK12 and TCLK3 input period                                 | <u>Tcy + 40</u> §<br>N |     | _       |       | N = prescale value (1, 2, 4, 8) |

| 48        | TckE2tmrl | Delay from selected External Clock Edge to<br>Timer increment | 2Tosc §                |     | 6Tosc § |       |                                 |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

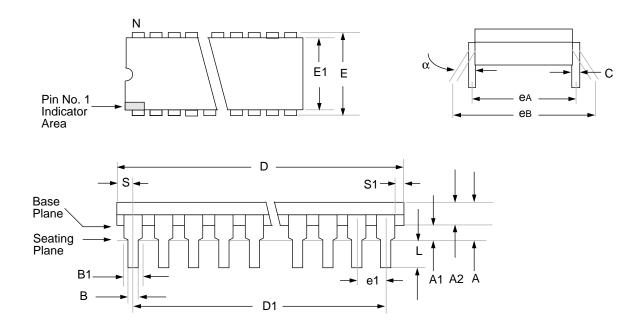

# 21.2 <u>40-Lead Plastic Dual In-line (600 mil)</u>

| Package Group: Plastic Dual In-Line (PLA) |             |        |           |             |       |           |  |        |  |

|-------------------------------------------|-------------|--------|-----------|-------------|-------|-----------|--|--------|--|

|                                           | Millimeters |        |           | Millimeters |       |           |  | Inches |  |

| Symbol                                    | Min         | Мах    | Notes     | Min         | Max   | Notes     |  |        |  |

| α                                         | 0°          | 10°    |           | 0°          | 10°   |           |  |        |  |

| Α                                         | _           | 5.080  |           | _           | 0.200 |           |  |        |  |

| A1                                        | 0.381       | _      |           | 0.015       | _     |           |  |        |  |

| A2                                        | 3.175       | 4.064  |           | 0.125       | 0.160 |           |  |        |  |

| В                                         | 0.355       | 0.559  |           | 0.014       | 0.022 |           |  |        |  |

| B1                                        | 1.270       | 1.778  | Typical   | 0.050       | 0.070 | Typical   |  |        |  |

| С                                         | 0.203       | 0.381  | Typical   | 0.008       | 0.015 | Typical   |  |        |  |

| D                                         | 51.181      | 52.197 |           | 2.015       | 2.055 |           |  |        |  |

| D1                                        | 48.260      | 48.260 | Reference | 1.900       | 1.900 | Reference |  |        |  |

| E                                         | 15.240      | 15.875 |           | 0.600       | 0.625 |           |  |        |  |

| E1                                        | 13.462      | 13.970 |           | 0.530       | 0.550 |           |  |        |  |

| e1                                        | 2.489       | 2.591  | Typical   | 0.098       | 0.102 | Typical   |  |        |  |

| eA                                        | 15.240      | 15.240 | Reference | 0.600       | 0.600 | Reference |  |        |  |

| eB                                        | 15.240      | 17.272 |           | 0.600       | 0.680 |           |  |        |  |

| L                                         | 2.921       | 3.683  |           | 0.115       | 0.145 |           |  |        |  |

| N                                         | 40          | 40     |           | 40          | 40    |           |  |        |  |

| S                                         | 1.270       | _      |           | 0.050       | _     |           |  |        |  |

| S1                                        | 0.508       | -      |           | 0.020       | _     |           |  |        |  |

## INDEX

# Α

| ADDLW                            | 112<br>113 |

|----------------------------------|------------|

|                                  | -          |

| ALU STATUS Register (ALUSTA)     |            |

| ALUSTA                           | , ,        |