Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 454 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-16i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.2 <u>Peripheral Interrupt Enable Register</u> (PIE)

This register contains the individual flag bits for the Peripheral interrupts.

# FIGURE 5-3: PIE REGISTER (ADDRESS: 17h, BANK 1)

| RBIE   | 0 R/W - 0 R/W<br>TMR3IE TMR2IE TMR1IE CA2IE CA1IE TXIE R0                                              | CIE R = Readable bit                             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| bit7   |                                                                                                                                                | bit0 W = Writable bit<br>-n = Value at POR reset |

| bit 7: | <b>RBIE</b> : PORTB Interrupt on Change Enable bit<br>1 = Enable PORTB interrupt on change<br>0 = Disable PORTB interrupt on change            |                                                  |

| bit 6: | <b>TMR3IE</b> : Timer3 Interrupt Enable bit<br>1 = Enable Timer3 interrupt<br>0 = Disable Timer3 interrupt                                     |                                                  |

| bit 5: | <b>TMR2IE</b> : Timer2 Interrupt Enable bit<br>1 = Enable Timer2 interrupt<br>0 = Disable Timer2 interrupt                                     |                                                  |

| bit 4: | <b>TMR1IE</b> : Timer1 Interrupt Enable bit<br>1 = Enable Timer1 interrupt<br>0 = Disable Timer1 interrupt                                     |                                                  |

| bit 3: | <b>CA2IE</b> : Capture2 Interrupt Enable bit<br>1 = Enable Capture interrupt on RB1/CAP2 pin<br>0 = Disable Capture interrupt on RB1/CAP2 pin  |                                                  |

| bit 2: | <b>CA1IE</b> : Capture1 Interrupt Enable bit<br>1 = Enable Capture interrupt on RB2/CAP1 pin<br>0 = Disable Capture interrupt on RB2/CAP1 pin  |                                                  |

| bit 1: | <b>TXIE</b> : USART Transmit Interrupt Enable bit<br>1 = Enable Transmit buffer empty interrupt<br>0 = Disable Transmit buffer empty interrupt |                                                  |

| bit 0: | <b>RCIE</b> : USART Receive Interrupt Enable bit<br>1 = Enable Receive buffer full interrupt<br>0 = Disable Receive buffer full interrupt      |                                                  |

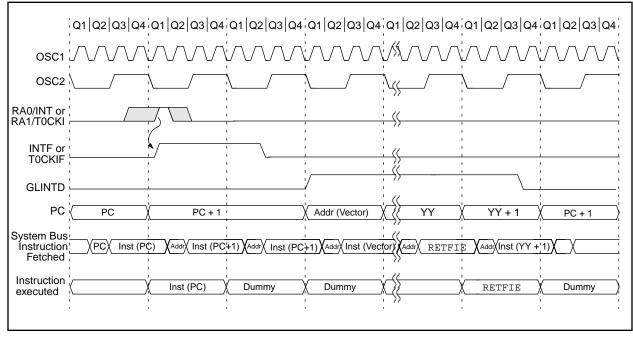

## 5.5 RA0/INT Interrupt

The external interrupt on the RA0/INT pin is edge triggered. Either the rising edge, if INTEDG bit (T0STA<7>) is set, or the falling edge, if INTEDG bit is clear. When a valid edge appears on the RA0/INT pin, the INTF bit (INTSTA<4>) is set. This interrupt can be disabled by clearing the INTE control bit (INTSTA<0>). The INT interrupt can wake the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

## 5.6 TMR0 Interrupt

An overflow (FFFFh  $\rightarrow$  0000h) in TMR0 will set the T0IF (INTSTA<5>) bit. The interrupt can be enabled/ disabled by setting/clearing the T0IE control bit (INTSTA<1>). For operation of the Timer0 module, see Section 11.0.

## 5.7 TOCKI Interrupt

The external interrupt on the RA1/T0CKI pin is edge triggered. Either the rising edge, if the T0SE bit (T0STA<6>) is set, or the falling edge, if the T0SE bit is clear. When a valid edge appears on the RA1/T0CKI pin, the T0CKIF bit (INTSTA<6>) is set. This interrupt can be disabled by clearing the T0CKIE control bit (INTSTA<2>). The T0CKI interrupt can wake up the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

## 5.8 Peripheral Interrupt

The peripheral interrupt flag indicates that at least one of the peripheral interrupts occurred (PEIF is set). The PEIF bit is a read only bit, and is a bit wise OR of all the flag bits in the PIR register AND'ed with the corresponding enable bits in the PIE register. Some of the peripheral interrupts can wake the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

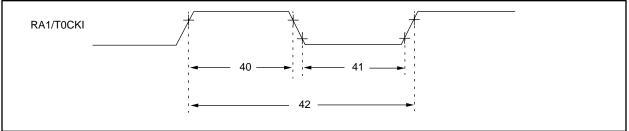

## FIGURE 5-5: INT PIN / TOCKI PIN INTERRUPT TIMING

## 9.5 I/O Programming Considerations

#### 9.5.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. For example, the BCF and BSF instructions read the register into the CPU, execute the bit operation, and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g. bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading a port reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (BCF, BSF, BTG, etc.) on a port, the value of the port pins is read, the desired operation is performed with this value, and the value is then written to the port latch.

Example 9-5 shows the effect of two sequential read-modify-write instructions on an I/O port.

#### EXAMPLE 9-5: READ MODIFY WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORT settings: PORTB<7:4> Inputs PORTB<3:0> Outputs ; ; PORTB<7:6> have pull-ups and are ; not connected to other circuitry ; PORT latch PORT pins ; ; \_\_\_\_\_ \_\_\_\_\_ ; PORTB, 7 BCF 01pp pppp 11pp pppp BCF PORTB, 6 10pp pppp 11pp pppp ; BCF DDRB, 7 10pp pppp 11pp pppp BCF DDRB, 6 10pp pppp 10pp pppp ; ; Note that the user may have expected the ; pin values to be 00pp pppp. The 2nd BCF ; caused RB7 to be latched as the pin value ; (High).

Note: A pin actively outputting a Low or High should not be driven from external devices in order to change the level on this pin (i.e. "wired-or", "wired-and"). The resulting high output currents may damage the device.

### 9.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 9-9). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before executing the instruction that reads the values on that I/O port. Otherwise, the previous state of that pin may be read into the CPU rather than the "new" state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

## FIGURE 9-9: SUCCESSIVE I/O OPERATION

| Instruction<br>fetched  | Q1  Q2  Q3  Q4<br>PC<br>MOVWF PORTB<br>write to<br>PORTB | PC + 1                           | Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4<br><u>PC+2</u> <u>PC+3</u><br>NOP NOP | Note:<br>This example shows a write to PORTB<br>followed by a read from PORTB.<br>Note that:<br>data setup time = (0.25 Tcy - TPD)<br>where TcY = instruction cycle.<br>TPD = propagation delay |

|-------------------------|----------------------------------------------------------|----------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB7:RB0                 |                                                          |                                  | X                                                             | Therefore, at higher clock<br>frequencies, a write followed by a                                                                                                                                |

|                         |                                                          |                                  | Port pin<br>sampled here                                      | read may be problematic.                                                                                                                                                                        |

| Instruction<br>executed |                                                          | MOVWF PORTB<br>write to<br>PORTB | MOVF PORTB,W NOP                                              |                                                                                                                                                                                                 |

|                         |                                                          |                                  | · · · · ·                                                     |                                                                                                                                                                                                 |

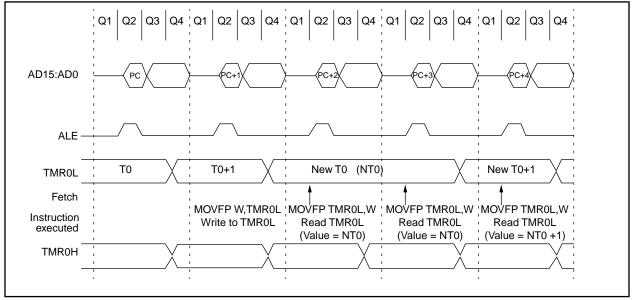

## 11.3 Read/Write Consideration for TMR0

Although TMR0 is a 16-bit timer/counter, only 8-bits at a time can be read or written during a single instruction cycle. Care must be taken during any read or write.

#### 11.3.1 READING 16-BIT VALUE

The problem in reading the entire 16-bit value is that after reading the low (or high) byte, its value may change from FFh to 00h.

Example 11-1 shows a 16-bit read. To ensure a proper read, interrupts must be disabled during this routine.

## EXAMPLE 11-1: 16-BIT READ

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

|--------|--------|-------|-----------------|

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| MOVFP  | TMPLO, | WREG  | ;tmplo -> wreg  |

| CPFSLT | TMR0L  |       | ;tmr0l < wreg?  |

| RETURN |        |       | ;no then return |

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| RETURN |        |       | ;return         |

#### 11.3.2 WRITING A 16-BIT VALUE TO TMR0

Since writing to either TMR0L or TMR0H will effectively inhibit increment of that half of the TMR0 in the next cycle (following write), but not inhibit increment of the other half, the user must write to TMR0L first and TMR0H next in two consecutive instructions, as shown in Example 11-2. The interrupt must be disabled. Any write to either TMR0L or TMR0H clears the prescaler.

#### EXAMPLE 11-2: 16-BIT WRITE

BSF CPUSTA, GLINTD ; Disable interrupt MOVFP RAM\_L, TMROL ; MOVFP RAM\_H, TMROH ; BCF CPUSTA, GLINTD ; Done, enable interrupt

### 11.4 Prescaler Assignments

Timer0 has an 8-bit prescaler. The prescaler assignment is fully under software control; i.e., it can be changed "on the fly" during program execution. When changing the prescaler assignment, clearing the prescaler is recommended before changing assignment. The value of the prescaler is "unknown," and assigning a value that is less then the present value makes it difficult to take this unknown time into account.

### FIGURE 11-4: TMR0 TIMING: WRITE HIGH OR LOW BYTE

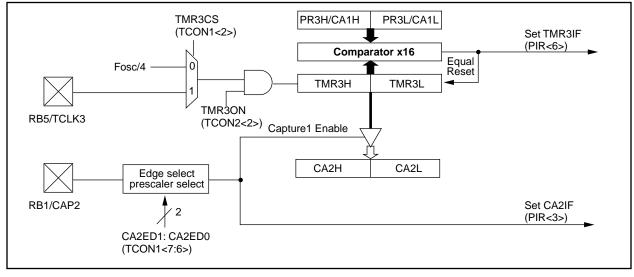

#### 12.2.1 ONE CAPTURE AND ONE PERIOD REGISTER MODE

In this mode registers PR3H/CA1H and PR3L/CA1L constitute a 16-bit period register. A block diagram is shown in Figure 12-7. The timer increments until it equals the period register and then resets to 0000h. TMR3 Interrupt Flag bit (TMR3IF) is set at this point. This interrupt can be disabled by clearing the TMR3 Interrupt Enable bit (TMR3IE). TMR3IF must be cleared in software.

This mode is selected if control bit CA1/PR3 is clear. In this mode, the Capture1 register, consisting of high byte (PR3H/CA1H) and low byte (PR3L/CA1L), is configured as the period control register for TMR3. Capture1 is disabled in this mode, and the corresponding Interrupt bit CA1IF is never set. TMR3 increments until it equals the value in the period register and then resets to 0000h.

Capture2 is active in this mode. The CA2ED1 and CA2ED0 bits determine the event on which capture will occur. The possible events are:

- · Capture on every falling edge

- Capture on every rising edge

- · Capture every 4th rising edge

- · Capture every 16th rising edge

When a capture takes place, an interrupt flag is latched into the CA2IF bit. This interrupt can be enabled by setting the corresponding mask bit CA2IE. The Peripheral Interrupt Enable bit (PEIE) must be set and the Global Interrupt Disable bit (GLINTD) must be cleared for the interrupt to be acknowledged. The CA2IF interrupt flag bit must be cleared in software.

When the capture prescale select is changed, the prescaler is not reset and an event may be generated. Therefore, the first capture after such a change will be ambiguous. However, it sets the time-base for the next capture. The prescaler is reset upon chip reset. Capture pin RB1/CAP2 is a multiplexed pin. When used as a port pin, Capture2 is not disabled. However, the user can simply disable the Capture2 interrupt by clearing CA2IE. If RB1/CAP2 is used as an output pin, the user can activate a capture by writing to the port pin. This may be useful during development phase to emulate a capture interrupt.

The input on capture pin RB1/CAP2 is synchronized internally to internal phase clocks. This imposes certain restrictions on the input waveform (see the Electrical Specification section for timing).

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the Timer3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The recommended sequence to read capture registers and capture overflow flag bits is shown in Example 12-1.

### EXAMPLE 12-1: SEQUENCE TO READ CAPTURE REGISTERS

| MOVLB 3              | ;Select Bank 3          |

|----------------------|-------------------------|

| MOVPF CA2L,LO_BYTE   | ;Read Capture2 low      |

|                      | ;byte, store in LO_BYTE |

| MOVPF CA2H, HI_BYTE  | ;Read Capture2 high     |

|                      | ;byte, store in HI_BYTE |

| MOVPF TCON2,STAT_VAL | ;Read TCON2 into file   |

|                      | ;STAT_VAL               |

### FIGURE 12-7: TIMER3 WITH ONE CAPTURE AND ONE PERIOD REGISTER BLOCK DIAGRAM

# 14.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real time applications. The PIC17CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- OSC selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- · Code protection

The PIC17CXX has a Watchdog Timer which can be shut off only through EPROM bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 96 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake from SLEEP through external reset, Watchdog Timer Reset or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LF crystal option saves power. Configuration bits are used to select various options. This configuration word has the format shown in Figure 14-1.

| <u>R/P - 1</u><br>PM2 <sup>(1)</sup> | U - x                                                       | U - x                                  | <u>U-x</u>                             | U - x       | U - x   | <u>U-x</u> | U - x         |                                                                                                                 |

|--------------------------------------|-------------------------------------------------------------|----------------------------------------|----------------------------------------|-------------|---------|------------|---------------|-----------------------------------------------------------------------------------------------------------------|

| bit15-7                              |                                                             |                                        | _                                      |             |         |            | bit0          |                                                                                                                 |

| U - x                                | R/P - 1                                                     | U - x                                  | <u>R/P - 1</u>                         | R/P - 1     | R/P - 1 | R/P - 1    | R/P - 1       | R = Readable bit                                                                                                |

| <br>bit15-7                          | PM1                                                         |                                        | PM0                                    | WDTPS1      | WDTPS0  | FOSC1      | FOSC0<br>bit0 | P = Programmable bit $P = Programmable bit$ $U = Unimplemented$ $- n = Value for Erased Device$ $(x = unknown)$ |

| bit 15-9:                            | Unimpler                                                    | nented: R                              | ead as a                               | '1'         |         |            |               |                                                                                                                 |

|                                      |                                                             | rocontrolle<br>ended mic<br>de protect | er mode<br>crocontrol<br>ed microc     | ontroller m | ode     |            |               |                                                                                                                 |

| bit 7, 5:                            | Unimpler                                                    | nented: R                              | ead as a                               | '0'         |         |            |               |                                                                                                                 |

| bit 3-2:                             | 11 = WD<br>10 = WD<br>01 = WD                               | Γ enabled<br>Γ enabled<br>Γ enabled    | , postscal<br>, postscal<br>, postscal | er = 256    |         |            |               |                                                                                                                 |

| bit 1-0:                             | FOSC1:F<br>11 = EC (<br>10 = XT (<br>01 = RC (<br>00 = LF ( | oscillator<br>oscillator<br>oscillator | scillator S                            | elect bits  |         |            |               |                                                                                                                 |

|                                      |                                                             |                                        |                                        |             |         |            |               |                                                                                                                 |

## FIGURE 14-1: CONFIGURATION WORD

<sup>© 1996</sup> Microchip Technology Inc.

# 15.0 INSTRUCTION SET SUMMARY

The PIC17CXX instruction set consists of 58 instructions. Each instruction is a 16-bit word divided into an OPCODE and one or more operands. The opcode specifies the instruction type, while the operand(s) further specify the operation of the instruction. The PIC17CXX instruction set can be grouped into three types:

- byte-oriented

- bit-oriented

- literal and control operations.

These formats are shown in Figure 15-1.

Table 15-1 shows the field descriptions for the opcodes. These descriptions are useful for understanding the opcodes in Table 15-2 and in each specific instruction descriptions.

**byte-oriented instructions**, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' = '0', the result is placed in the WREG register. If 'd' = '1', the result is placed in the file register specified by the instruction.

**bit-oriented instructions**, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

**literal and control operations**, 'k' represents an 8- or 11-bit constant or literal value.

The instruction set is highly orthogonal and is grouped into:

- · byte-oriented operations

- bit-oriented operations

- · literal and control operations

All instructions are executed within one single instruction cycle, unless:

- a conditional test is true

- the program counter is changed as a result of an instruction

- a table read or a table write instruction is executed (in this case, the execution takes two instruction cycles with the second cycle executed as a NOP)

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 25 MHz, the normal instruction execution time is 160 ns. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 320 ns.

### TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                                                                                                                                                                                                                                                                                                                                                  |

| Register file address (00h to FFh)                                                                                                                                                                                                                                                                                                                           |

| Peripheral register file address (00h to 1Fh)                                                                                                                                                                                                                                                                                                                |

| Table pointer control $i = 0'$ (do not change)<br>i = '1' (increment after instruction execution)                                                                                                                                                                                                                                                            |

| Table byte select t = '0' (perform operation on lower                                                                                                                                                                                                                                                                                                        |

| byte)<br>t = '1' (perform operation on upper byte literal field,<br>constant data)                                                                                                                                                                                                                                                                           |

| Working register (accumulator)                                                                                                                                                                                                                                                                                                                               |

| Bit address within an 8-bit file register                                                                                                                                                                                                                                                                                                                    |

| Literal field, constant data or label                                                                                                                                                                                                                                                                                                                        |

| Don't care location (= '0' or '1')<br>The assembler will generate code with $x = '0'$ . It is<br>the recommended form of use for compatibility with<br>all Microchip software tools.                                                                                                                                                                         |

| Destination select<br>0 = store result in WREG<br>1 = store result in file register f<br>Default is d = '1'                                                                                                                                                                                                                                                  |

| Unused, encoded as '0'                                                                                                                                                                                                                                                                                                                                       |

| Destination select<br>0 = store result in file register f and in the WREG<br>1 = store result in file register f<br>Default is s = '1'                                                                                                                                                                                                                       |

| Label name                                                                                                                                                                                                                                                                                                                                                   |

| ALU status bits Carry, Digit Carry, Zero, Overflow                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                              |

| Global Interrupt Disable bit (CPUSTA<4>)                                                                                                                                                                                                                                                                                                                     |

| Global Interrupt Disable bit (CPUSTA<4>)<br>Table Pointer (16-bit)                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                              |

| Table Pointer (16-bit)         Table Latch (16-bit) consists of high byte (TBLATH)                                                                                                                                                                                                                                                                           |

| Table Pointer (16-bit)<br>Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)                                                                                                                                                                                                                                                       |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)and low byte (TBLATL)Table Latch low byte                                                                                                                                                                                                                                           |

| Table Pointer (16-bit)         Table Latch (16-bit) consists of high byte (TBLATH)         and low byte (TBLATL)         Table Latch low byte         Table Latch high byte                                                                                                                                                                                  |

| Table Pointer (16-bit)<br>Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)<br>Table Latch low byte<br>Table Latch high byte<br>Top of Stack                                                                                                                                                                                      |

| Table Pointer (16-bit)<br>Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)<br>Table Latch low byte<br>Table Latch high byte<br>Top of Stack<br>Program Counter                                                                                                                                                                   |

| Table Pointer (16-bit)<br>Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)<br>Table Latch low byte<br>Table Latch high byte<br>Top of Stack<br>Program Counter<br>Bank Select Register                                                                                                                                           |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer Counter                                                                                                                                                 |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer CounterTime-out bit                                                                                                                                 |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer CounterTime-out bitPower-down bitDestination either the WREG register or the speci-                                                                 |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer CounterTime-out bitPower-down bitDestination either the WREG register or the specified register file location                                       |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer CounterTime-out bitPower-down bitDestination either the WREG register or the specified register file locationOptions                                    |

| Table Pointer (16-bit)Table Latch (16-bit) consists of high byte (TBLATH)<br>and low byte (TBLATL)Table Latch low byteTable Latch high byteTop of StackProgram CounterBank Select RegisterWatchdog Timer CounterTime-out bitPower-down bitDestination either the WREG register or the specified register file locationOptionsContents                        |

| Table Pointer (16-bit) Table Latch (16-bit) consists of high byte (TBLATH) and low byte (TBLATL) Table Latch low byte Table Latch high byte Top of Stack Program Counter Bank Select Register Watchdog Timer Counter Time-out bit Power-down bit Destination either the WREG register or the speci- fied register file location Options Contents Assigned to |

|                                                                                                                                                                                                                                                                                                                                                              |

| XORLW             | Exclusive OR Literal with                                                                       | XORWF                                                                                                                                                                  | Exclusive OR WREG with f                          |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

|                   | WREG                                                                                            | Syntax:                                                                                                                                                                | [label] XORWF f,d                                 |  |  |  |  |

| Syntax:           | [ <i>label</i> ] XORLW k                                                                        | Operands:                                                                                                                                                              | $0 \le f \le 255$                                 |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                               |                                                                                                                                                                        | d ∈ [0,1]                                         |  |  |  |  |

| Operation:        | (WREG) .XOR. $k \rightarrow (WREG)$                                                             | Operation:                                                                                                                                                             | (WREG) .XOR. (f) $\rightarrow$ (dest)             |  |  |  |  |

| Status Affected:  | Z                                                                                               | Status Affected:                                                                                                                                                       | Z                                                 |  |  |  |  |

| Encoding:         | Encoding: 1011 0100 kkkk kkkk End                                                               |                                                                                                                                                                        | 0000 110d ffff ffff                               |  |  |  |  |

| Description:      | The contents of WREG are XOR'ed<br>with the 8-bit literal 'k'. The result is<br>placed in WREG. | Description: Exclusive OR the contents of WRE<br>with register 'f'. If 'd' is 0 the result<br>stored in WREG. If 'd' is 1 the resu<br>stored back in the register 'f'. |                                                   |  |  |  |  |

| Words:            | 1                                                                                               | Words:                                                                                                                                                                 | 1                                                 |  |  |  |  |

| Cycles:           | 1                                                                                               | Cycles:                                                                                                                                                                | 1                                                 |  |  |  |  |

| Q Cycle Activity: |                                                                                                 | Q Cycle Activity:                                                                                                                                                      |                                                   |  |  |  |  |

| Q1                | Q2 Q3 Q4                                                                                        | Q1                                                                                                                                                                     | Q2 Q3 Q4                                          |  |  |  |  |

| Decode            | ReadExecuteWrite toliteral 'k'WREG                                                              | Decode                                                                                                                                                                 | Read Execute Write to<br>register 'f' destination |  |  |  |  |

| Example:          | XORLW 0xAF                                                                                      | L                                                                                                                                                                      |                                                   |  |  |  |  |

| Before Instruc    | ction                                                                                           | Example:                                                                                                                                                               | XORWF REG, 1                                      |  |  |  |  |

| After Instructi   | = 0xB5<br>on<br>= 0x1A                                                                          | Before Instru<br>REG<br>WREG                                                                                                                                           | ction<br>= 0xAF<br>= 0xB5                         |  |  |  |  |

|                   |                                                                                                 | After Instruct<br>REG<br>WREG                                                                                                                                          | ion<br>= 0x1A<br>= 0xB5                           |  |  |  |  |

NOTES:

# Applicable Devices 42 R42 42A 43 R43 44

## FIGURE 17-5: TIMER0 CLOCK TIMINGS

## TABLE 17-5: TIMER0 CLOCK REQUIREMENTS

| Parameter |      |                        |                |                   |      |     |       |                    |

|-----------|------|------------------------|----------------|-------------------|------|-----|-------|--------------------|

| No.       | Sym  | Characteristic         |                | Min               | Тур† | Max | Units | Conditions         |

| 40        | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5TCY + 20 §     | —    | _   | ns    |                    |

|           |      |                        | With Prescaler | 10*               | —    | —   | ns    |                    |

| 41        | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5Tcy + 20 §     | —    | —   | ns    |                    |

|           |      |                        | With Prescaler | 10*               | —    | —   | ns    |                    |

| 42        | Tt0P | T0CKI Period           | ·              | <u>Tcy + 40</u> § | —    | —   | ns    | N = prescale value |

|           |      |                        |                | N                 |      |     |       | (1, 2, 4,, 256)    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

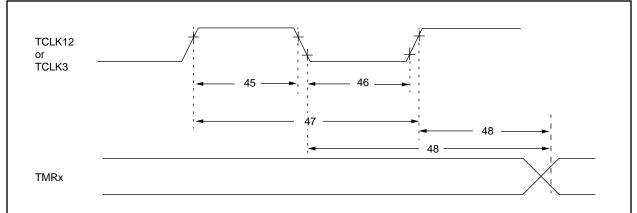

## FIGURE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK TIMINGS

## TABLE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK REQUIREMENTS

| Parameter |           |                                                               |                        | Тур |          |       |                                    |

|-----------|-----------|---------------------------------------------------------------|------------------------|-----|----------|-------|------------------------------------|

| No.       | Sym       | Characteristic                                                | Min                    | †   | Max      | Units | Conditions                         |

| 45        | Tt123H    | TCLK12 and TCLK3 high time                                    | 0.5 TCY + 20 §         |     | _        | ns    |                                    |

| 46        | Tt123L    | TCLK12 and TCLK3 low time                                     | 0.5 TCY + 20 §         |     |          | ns    |                                    |

| 47        | Tt123P    | TCLK12 and TCLK3 input period                                 | <u>Tcy + 40</u> §<br>N |     |          | ns    | N = prescale value<br>(1, 2, 4, 8) |

| 48        | TckE2tmrl | Delay from selected External Clock Edge to<br>Timer increment | 2Tosc §                |     | 6 Tosc § | _     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

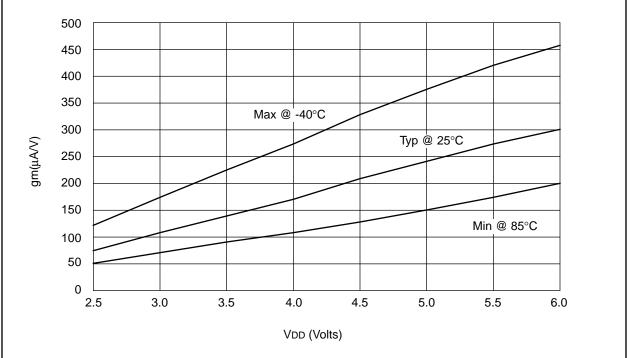

# Applicable Devices 42 R42 42A 43 R43 44

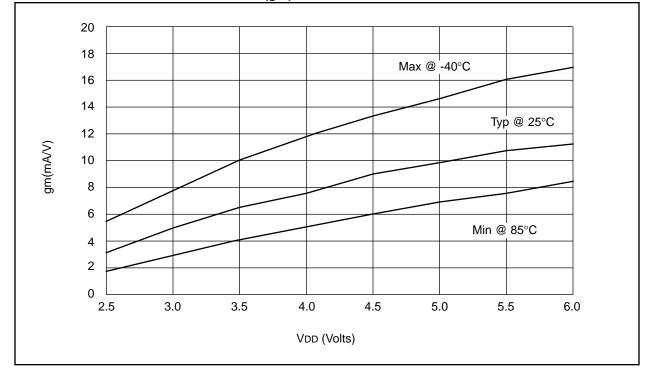

FIGURE 18-6: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

## Applicable Devices 42 R42 42A 43 R43 44

# Applicable Devices 42 R42 42A 43 R43 44

## 19.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2 | opS                                  | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|----------|--------------------------------------|-----------|----------------------------------------|

| 2. TppS  |                                      | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т        |                                      |           |                                        |

| F        | Frequency                            | Т         | Time                                   |

| Lowerc   | ase symbols (pp) and their meanings: |           |                                        |

| рр       |                                      |           |                                        |

| ad       | Address/Data                         | ost       | Oscillator Start-Up Timer              |

| al       | ALE                                  | pwrt      | Power-Up Timer                         |

| сс       | Capture1 and Capture2                | rb        | PORTB                                  |

| ck       | CLKOUT or clock                      | rd        | RD                                     |

| dt       | Data in                              | rw        | RD or WR                               |

| in       | INT pin                              | tO        | TOCKI                                  |

| io       | I/O port                             | t123      | TCLK12 and TCLK3                       |

| mc       | MCLR                                 | wdt       | Watchdog Timer                         |

| oe       | ŌĒ                                   | wr        | WR                                     |

| os       | OSC1                                 |           |                                        |

| Upperc   | ase symbols and their meanings:      |           |                                        |

| S        |                                      |           |                                        |

| D        | Driven                               | L         | Low                                    |

| E        | Edge                                 | P         | Period                                 |

| F        | Fall                                 | R         | Rise                                   |

| Н        | High                                 | V         | Valid                                  |

|          | Invalid (Hi-impedance)               | Z         | Hi-impedance                           |

## Applicable Devices 42 R42 42A 43 R43 44

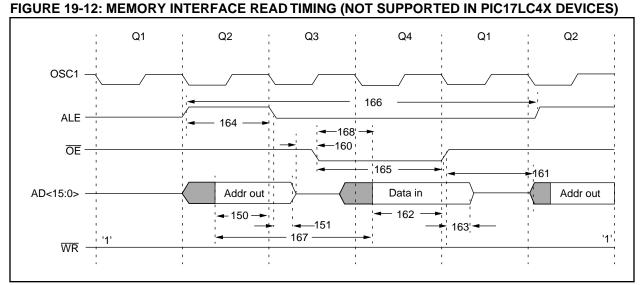

# TABLE 19-12: MEMORY INTERFACE READ REQUIREMENTS (NOT SUPPORTED IN PIC17LC4X DEVICES)

| Parameter<br>No. | Sym      | Characteristic                                            | Min           | Тур†      | Max          | Units | Conditions |

|------------------|----------|-----------------------------------------------------------|---------------|-----------|--------------|-------|------------|

| 150              | TadV2alL | AD15:AD0 (address) valid to ALE↓<br>(address setup time)  | 0.25Tcy - 10  | _         | _            | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)           | 5*            |           | _            | ns    |            |

| 160              | TadZ2oeL | AD15:AD0 hi-impedance to $\overline{\text{OE}}\downarrow$ | 0*            | _         | —            | ns    |            |

| 161              | ToeH2adD | OE↑ to AD15:AD0 driven                                    | 0.25Tcy - 15  | _         | _            | ns    |            |

| 162              | TadV2oeH | Data in valid before OE↑<br>(data setup time)             | 35            | _         | _            | ns    |            |

| 163              | ToeH2adI | OE <sup>↑</sup> to data in invalid (data hold time)       | 0             | _         | _            | ns    |            |

| 164              | TalH     | ALE pulse width                                           | —             | 0.25Tcy § | —            | ns    |            |

| 165              | ToeL     | OE pulse width                                            | 0.5Tcy - 35 § | _         | _            | ns    |            |

| 166              | TalH2alH | ALE↑ to ALE↑(cycle time)                                  | —             | TCY §     | _            | ns    |            |

| 167              | Tacc     | Address access time                                       | _             | _         | 0.75Tcy - 30 | ns    |            |

| 168              | Тое      | Output enable access time<br>(OE low to Data Valid)       | _             | _         | 0.5Tcy - 45  | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

\*

Applicable Devices 42 R42 42A 43 R43 44

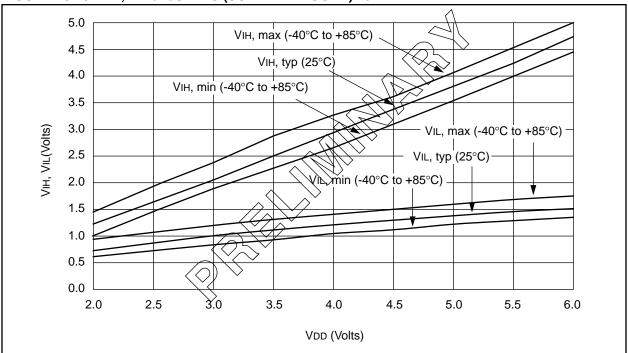

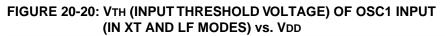

# 20.0 PIC17CR42/42A/43/R43/44 DC AND AC CHARACTERISTICS

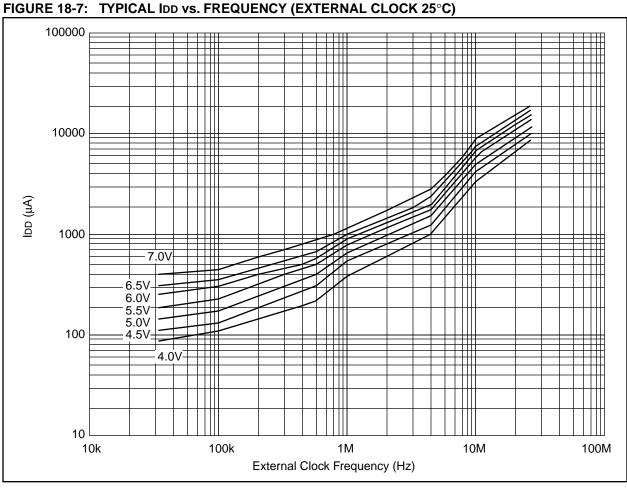

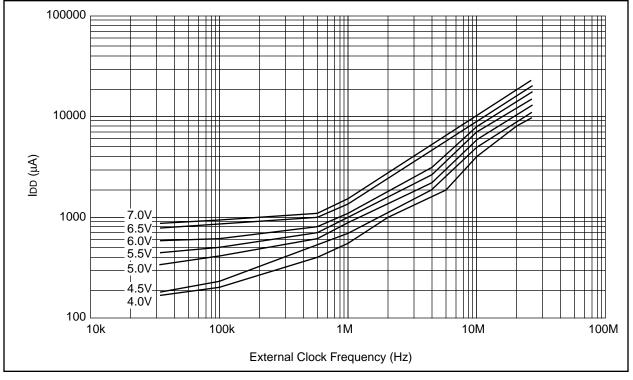

The graphs and tables provided in this section are for design guidance and are not tested nor guaranteed. In some graphs or tables the data presented is outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are ensured to operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

## TABLE 20-1: PIN CAPACITANCE PER PACKAGE TYPE

| Din Nama                               |            | Typical Capacitance (pF) |             |             |  |  |

|----------------------------------------|------------|--------------------------|-------------|-------------|--|--|

| Pin Name                               | 40-pin DIP | 44-pin PLCC              | 44-pin MQFP | 44-pin TQFP |  |  |

| All pins, except MCLR,<br>VDD, and Vss | 10         | 10                       | 10          | 10          |  |  |

| MCLR pin                               | 20         | 20                       | 20          | 20          |  |  |

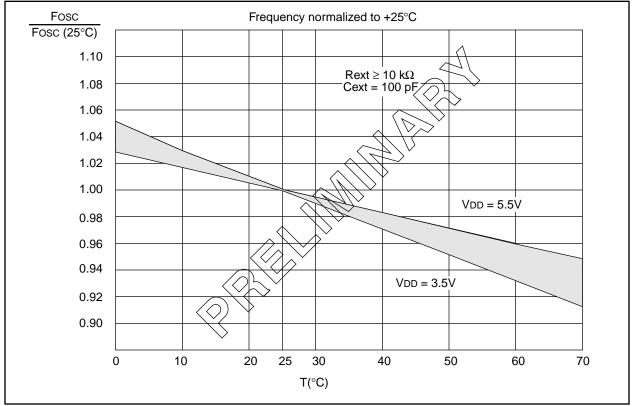

## FIGURE 20-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

# Applicable Devices 42 R42 42A 43 R43 44

# E.2 PIC16C5X Family of Devices

|              |       |           |            | 0        | Clock Mer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Memory   | Perip         | Peripherals | Features                                                                                                                |

|--------------|-------|-----------|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|-------------|-------------------------------------------------------------------------------------------------------------------------|

|              |       |           |            | CAN USE  | Course will a course of the co |          |               |             |                                                                                                                         |

|              |       | 1084<br>1 | to Toliani |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (s)      |               | ., N SOL    | 454                                                                                                                     |

|              | Terry | Unus      | 101.       | Mr.      | BOW SOUND SUNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | SUID OI       | o sequent   | Sebersed                                                                                                                |

| PIC16C52     | 4     | 384       |            | 25       | TMRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12       | 2.5-6.25      | 33          | 18-pin DIP, SOIC                                                                                                        |

| PIC16C54     | 20    | 512       | I          | 25       | TMR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12       | 2.5-6.25      | 33          | 18-pin DIP, SOIC; 20-pin SSOP                                                                                           |

| PIC16C54A    | 20    | 512       |            | 25       | TMR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12       | 2.0-6.25      | 33          | 18-pin DIP, SOIC; 20-pin SSOP                                                                                           |

| PIC16CR54A   | 20    | I         | 512        | 25       | TMR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12       | 2.0-6.25      | 33          | 18-pin DIP, SOIC; 20-pin SSOP                                                                                           |

| PIC16C55     | 20    | 512       |            | 24       | TMR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20       | 2.5-6.25      | 33          | 28-pin DIP, SOIC, SSOP                                                                                                  |

| PIC16C56     | 20    | ź         | I          | 25       | TMR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12       | 2.5-6.25      | 33          | 18-pin DIP, SOIC; 20-pin SSOP                                                                                           |