#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 454 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-16i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Overview                                                               | 5   |

|-------|------------------------------------------------------------------------|-----|

| 2.0   | PIC17C4X Device Varieties                                              | 7   |

| 3.0   | Architectural Overview                                                 | 9   |

| 4.0   | Reset                                                                  | 15  |

| 5.0   | Interrupts                                                             | 21  |

| 6.0   | Memory Organization                                                    | 29  |

| 7.0   | Table Reads and Table Writes                                           | 43  |

| 8.0   | Hardware Multiplier                                                    | 49  |

| 9.0   | I/O Ports                                                              | 53  |

| 10.0  | Overview of Timer Resources                                            |     |

| 11.0  | Timer0                                                                 |     |

| 12.0  | Timer1, Timer2, Timer3, PWMs and Captures                              |     |

| 13.0  | Universal Synchronous Asynchronous Receiver Transmitter (USART) Module | 83  |

| 14.0  | Special Features of the CPU                                            | 99  |

| 15.0  | Instruction Set Summary                                                | 107 |

| 16.0  | Development Support                                                    | 143 |

| 17.0  | PIC17C42 Electrical Characteristics                                    |     |

| 18.0  | PIC17C42 DC and AC Characteristics                                     |     |

| 19.0  | PIC17CR42/42A/43/R43/44 Electrical Characteristics                     | 175 |

| 20.0  | PIC17CR42/42A/43/R43/44 DC and AC Characteristics                      |     |

| 21.0  | Packaging Information                                                  | 205 |

| 111-  | dix A: Modifications                                                   |     |

|       | dix B: Compatibility                                                   |     |

| Appen | dix C: What's New                                                      | 212 |

| Appen | dix D: What's Changed                                                  | 212 |

|       | dix E: PIC16/17 Microcontrollers                                       |     |

|       | dix F: Errata for PIC17C42 Silicon                                     |     |

|       |                                                                        |     |

| PIC17 | C4X Product Identification System                                      | 237 |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. For example, the legend below shows that some features of only the PIC17C43, PIC17C43, PIC17C44 are described in this section.

#### Applicable Devices 42 R42 42A 43 R43 44

## To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error from the previous version of the PIC17C4X Data Sheet (Literature Number DS30412B), please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

To assist you in the use of this document, Appendix C contains a list of new information in this data sheet, while Appendix D contains information that has changed

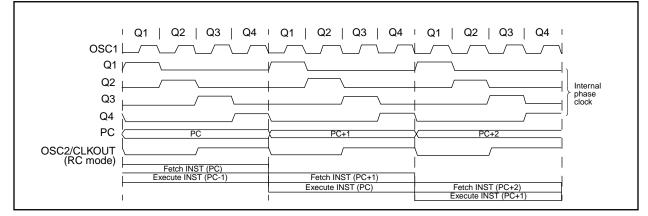

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-3.

#### 3.2 Instruction Flow/Pipelining

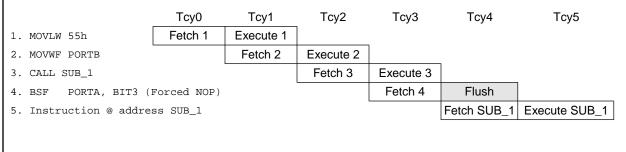

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g.GOTO) then two cycles are required to complete the instruction (Example 3-2).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-2: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### 5.3 <u>Peripheral Interrupt Request Register</u> (PIR)

This register contains the individual flag bits for the peripheral interrupts.

**Note:** These bits will be set by the specified condition, even if the corresponding interrupt enable bit is cleared (interrupt disabled), or the GLINTD bit is set (all interrupts disabled). Before enabling an interrupt, the user may wish to clear the interrupt flag to ensure that the program does not immediately branch to the peripheral interrupt service routine.

### FIGURE 5-4: PIR REGISTER (ADDRESS: 16h, BANK 1)

|        | 0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 R-0                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| RBIF   |                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| bit7   | bit0 W = Writable bit<br>-n = Value at POR reset                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| bit 7: | <b>RBIF</b> : PORTB Interrupt on Change Flag bit<br>1 = One of the PORTB inputs changed (Software must end the mismatch condition)<br>0 = None of the PORTB inputs have changed                                                                                              |  |  |  |  |  |  |  |  |

| bit 6: | TMR3IF: Timer3 Interrupt Flag bit<br>If Capture1 is enabled (CA1/PR3 = 1)<br>1 = Timer3 overflowed<br>0 = Timer3 did not overflow                                                                                                                                            |  |  |  |  |  |  |  |  |

|        | If Capture1 is disabled (CA1/ $\overline{PR3}$ = 0)<br>1 = Timer3 value has rolled over to 0000h from equalling the period register (PR3H:PR3L) value<br>0 = Timer3 value has not rolled over to 0000h from equalling the period register (PR3H:PR3L) value                  |  |  |  |  |  |  |  |  |

| bit 5: | <b>TMR2IF</b> : Timer2 Interrupt Flag bit<br>1 = Timer2 value has rolled over to 0000h from equalling the period register (PR2) value<br>0 = Timer2 value has not rolled over to 0000h from equalling the period register (PR2) value                                        |  |  |  |  |  |  |  |  |

| bit 4: | <b>TMR1IF</b> : Timer1 Interrupt Flag bit<br>If Timer1 is in 8-bit mode (T16 = 0)<br>1 = Timer1 value has rolled over to 0000h from equalling the period register (PR) value<br>0 = Timer1 value has not rolled over to 0000h from equalling the period register (PR2) value |  |  |  |  |  |  |  |  |

|        | If Timer1 is in 16-bit mode (T16 = 1)<br>1 = TMR1:TMR2 value has rolled over to 0000h from equalling the period register (PR1:PR2) value<br>0 = TMR1:TMR2 value has not rolled over to 0000h from equalling the period register (PR1:PR2) value                              |  |  |  |  |  |  |  |  |

| bit 3: | <b>CA2IF</b> : Capture2 Interrupt Flag bit<br>1 = Capture event occurred on RB1/CAP2 pin<br>0 = Capture event did not occur on RB1/CAP2 pin                                                                                                                                  |  |  |  |  |  |  |  |  |

| bit 2: | <b>CA1IF</b> : Capture1 Interrupt Flag bit<br>1 = Capture event occurred on RB0/CAP1 pin<br>0 = Capture event did not occur on RB0/CAP1 pin                                                                                                                                  |  |  |  |  |  |  |  |  |

| bit 1: | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = Transmit buffer is empty<br>0 = Transmit buffer is full                                                                                                                                                               |  |  |  |  |  |  |  |  |

| bit 0: | RCIF: USART Receive Interrupt Flag bit<br>1 = Receive buffer is full<br>0 = Receive buffer is empty                                                                                                                                                                          |  |  |  |  |  |  |  |  |

### TABLE 6-1: MODE MEMORY ACCESS

| Operating<br>Mode            | Internal<br>Program<br>Memory | Configuration Bits,<br>Test Memory,<br>Boot ROM |  |  |

|------------------------------|-------------------------------|-------------------------------------------------|--|--|

| Microprocessor               | No Access                     | No Access                                       |  |  |

| Microcontroller              | Access                        | Access                                          |  |  |

| Extended<br>Microcontroller  | Access                        | No Access                                       |  |  |

| Protected<br>Microcontroller | Access                        | Access                                          |  |  |

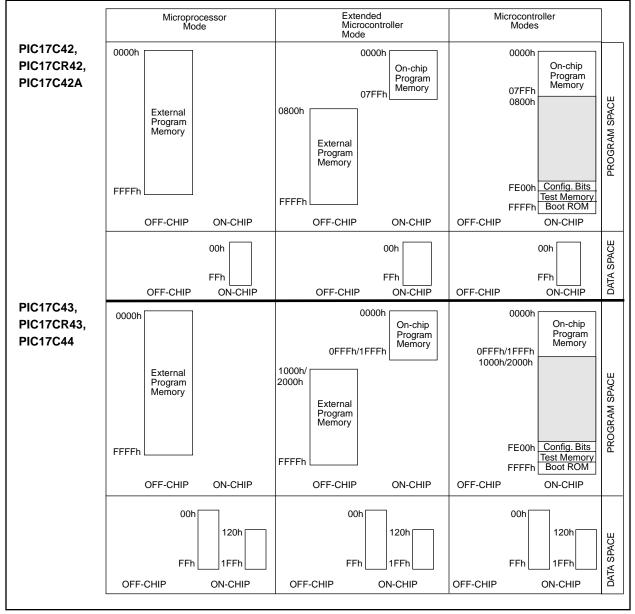

The PIC17C4X can operate in modes where the program memory is off-chip. They are the microprocessor and extended microcontroller modes. The microprocessor mode is the default for an unprogrammed device.

Regardless of the processor mode, data memory is always on-chip.

#### FIGURE 6-2: MEMORY MAP IN DIFFERENT MODES

#### 6.2 Data Memory Organization

Data memory is partitioned into two areas. The first is the General Purpose Registers (GPR) area, while the second is the Special Function Registers (SFR) area. The SFRs control the operation of the device.

Portions of data memory are banked, this is for both areas. The GPR area is banked to allow greater than 232 bytes of general purpose RAM. SFRs are for the registers that control the peripheral functions. Banking requires the use of control bits for bank selection. These control bits are located in the Bank Select Register (BSR). If an access is made to a location outside this banked region, the BSR bits are ignored. Figure 6-5 shows the data memory map organization for the PIC17C42 and Figure 6-6 for all of the other PIC17C4X devices.

Instructions MOVPF and MOVFP provide the means to move values from the peripheral area ("P") to any location in the register file ("F"), and vice-versa. The definition of the "P" range is from 0h to 1Fh, while the "F" range is 0h to FFh. The "P" range has six more locations than peripheral registers (eight locations for the PIC17C42 device) which can be used as General Purpose Registers. This can be useful in some applications where variables need to be copied to other locations in the general purpose RAM (such as saving status information during an interrupt).

The entire data memory can be accessed either directly or indirectly through file select registers FSR0 and FSR1 (Section 6.4). Indirect addressing uses the appropriate control bits of the BSR for accesses into the banked areas of data memory. The BSR is explained in greater detail in Section 6.8.

#### 6.2.1 GENERAL PURPOSE REGISTER (GPR)

All devices have some amount of GPR area. The GPRs are 8-bits wide. When the GPR area is greater than 232, it must be banked to allow access to the additional memory space.

Only the PIC17C43 and PIC17C44 devices have banked memory in the GPR area. To facilitate switching between these banks, the MOVLR bank instruction has been added to the instruction set. GPRs are not initialized by a Power-on Reset and are unchanged on all other resets.

#### 6.2.2 SPECIAL FUNCTION REGISTERS (SFR)

The SFRs are used by the CPU and peripheral functions to control the operation of the device (Figure 6-5 and Figure 6-6). These registers are static RAM.

The SFRs can be classified into two sets, those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described here, while those related to a peripheral feature are described in the section for each peripheral feature.

The peripheral registers are in the banked portion of memory, while the core registers are in the unbanked region. To facilitate switching between the peripheral banks, the MOVLB bank instruction has been provided.

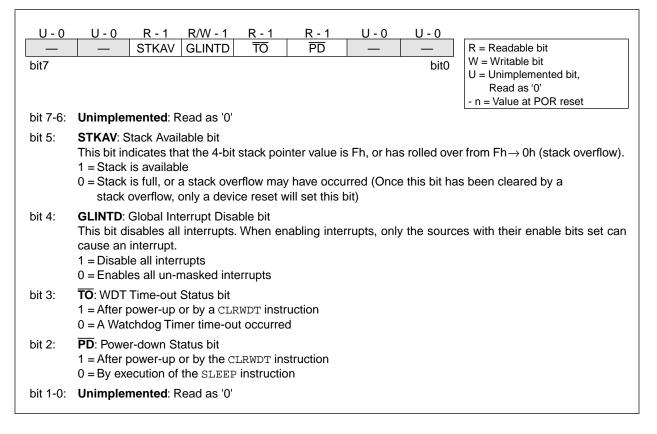

#### 6.2.2.2 CPU STATUS REGISTER (CPUSTA)

The CPUSTA register contains the status and control bits for the CPU. This register is used to globally enable/disable interrupts. If only a specific interrupt is desired to be enabled/disabled, please refer to the INTerrupt STAtus (INTSTA) register and the Peripheral Interrupt Enable (PIE) register. This register also indicates if the stack is available and contains the Power-down (PD) and Time-out (TO) bits. The TO, PD, and STKAV bits are not writable. These bits are set and cleared according to device logic. Therefore, the result of an instruction with the CPUSTA register as destination may be different than intended.

#### FIGURE 6-8: CPUSTA REGISTER (ADDRESS: 06h, UNBANKED)

#### 12.1.3 USING PULSE WIDTH MODULATION (PWM) OUTPUTS WITH TMR1 AND TMR2

Two high speed pulse width modulation (PWM) outputs are provided. The PWM1 output uses Timer1 as its time-base, while PWM2 may be software configured to use either Timer1 or Timer2 as the time-base. The PWM outputs are on the RB2/PWM1 and RB3/PWM2 pins.

Each PWM output has a maximum resolution of 10-bits. At 10-bit resolution, the PWM output frequency is 24.4 kHz (@ 25 MHz clock) and at 8-bit resolution the PWM output frequency is 97.7 kHz. The duty cycle of the output can vary from 0% to 100%.

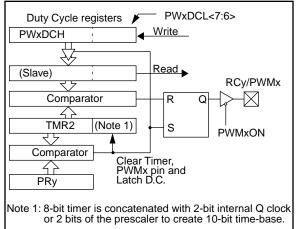

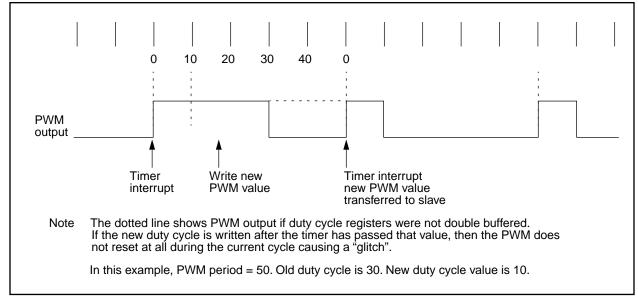

Figure 12-5 shows a simplified block diagram of the PWM module. The duty cycle register is double buffered for glitch free operation. Figure 12-6 shows how a glitch could occur if the duty cycle registers were not double buffered.

The user needs to set the PWM1ON bit (TCON2<4>) to enable the PWM1 output. When the PWM1ON bit is set, the RB2/PWM1 pin is configured as PWM1 output and forced as an output irrespective of the data direction bit (DDRB<2>). When the PWM1ON bit is clear, the pin behaves as a port pin and its direction is controlled by its data direction bit (DDRB<2>). Similarly, the PWM2ON (TCON2<5>) bit controls the configuration of the RB3/PWM2 pin.

#### FIGURE 12-5: SIMPLIFIED PWM BLOCK DIAGRAM

#### FIGURE 12-6: PWM OUTPUT

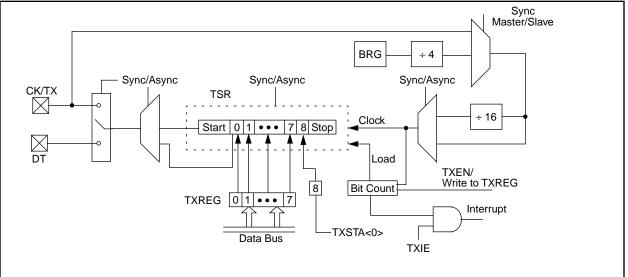

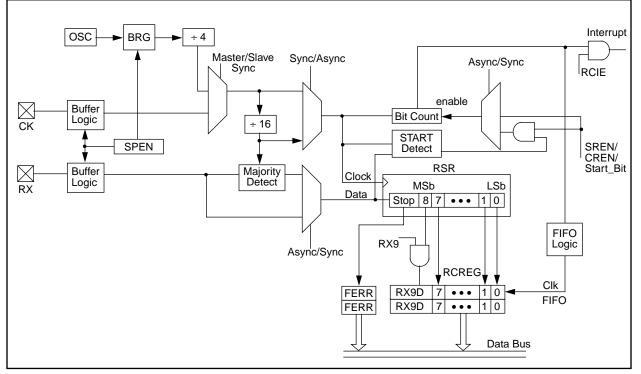

#### FIGURE 13-3: USART TRANSMIT

#### 13.2 USART Asynchronous Mode

In this mode, the USART uses standard nonreturn-to-zero (NRZ) format (one start bit, eight or nine data bits, and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock x64 of the bit shift rate. Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

The asynchronous mode is selected by clearing the SYNC bit (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

#### 13.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 13-3. The heart of the transmitter is the transmit shift register (TSR). The shift register obtains its data from the read/write transmit buffer (TXREG). TXREG is loaded with data in software. The TSR is not loaded until the stop bit has been transmitted from the previous load. As soon as the stop bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one TCY at the end of the current BRG cycle), the TXREG is empty and an interrupt bit, TXIF (PIR<1>) is set. This interrupt can be enabled or disabled by the TXIE bit (PIE<1>). TXIF will be set regardless of TXIE and cannot be reset in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of the TXREG, the TRMT (TXSTA<1>) bit shows the status of the TSR. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty.

| Note: | The TSR is not mapped in data memory, |

|-------|---------------------------------------|

|       | so it is not available to the user.   |

Transmission enabled setting is by the TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 13-5). The transmission can also be started by first loading TXREG and then setting TXEN. Normally when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to TSR resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 13-6). Clearing TXEN during a transmission will cause the transmission to be aborted. This will reset the transmitter and the RA5/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty).

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. Load data to the TXREG register.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 7. Enable the transmission by setting TXEN (starts transmission).

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the opposite order.

Note: To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

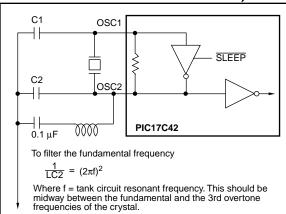

#### FIGURE 14-3: CRYSTAL OPERATION, OVERTONE CRYSTALS (XT OSC CONFIGURATION)

#### TABLE 14-2: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Oscillator<br>Type | Resonator<br>Frequency         | Capacitor Range<br>C1 = C2               |

|--------------------|--------------------------------|------------------------------------------|

| LF                 | 455 kHz<br>2.0 MHz             | 15 - 68 pF<br>10 - 33 pF                 |

| ХТ                 | 4.0 MHz<br>8.0 MHz<br>16.0 MHz | 22 - 68 pF<br>33 - 100 pF<br>33 - 100 pF |

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### **Resonators Used:**

| 455 kHz                                           | Panasonic EFO-A455K04B        | ± 0.3% |  |  |  |  |

|---------------------------------------------------|-------------------------------|--------|--|--|--|--|

| 2.0 MHz                                           | Murata Erie CSA2.00MG         | ± 0.5% |  |  |  |  |

| 4.0 MHz                                           | Murata Erie CSA4.00MG         | ± 0.5% |  |  |  |  |

| 8.0 MHz                                           | 8.0 MHz Murata Erie CSA8.00MT |        |  |  |  |  |

| 16.0 MHz                                          | Murata Erie CSA16.00MX        | ± 0.5% |  |  |  |  |

| Resonators used did not have built-in capacitors. |                               |        |  |  |  |  |

## TABLE 14-3:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR

| Osc<br>Type | Freq                  | C1               | C2               |

|-------------|-----------------------|------------------|------------------|

| LF          | 32 kHz <sup>(1)</sup> | 100-150 pF       | 100-150 pF       |

|             | 1 MHz                 | 10-33 pF         | 10-33 pF         |

|             | 2 MHz                 | 10-33 pF         | 10-33 pF         |

| XT          | 2 MHz                 | 47-100 pF        | 47-100 pF        |

|             | 4 MHz                 | 15-68 pF         | 15-68 pF         |

|             | 8 MHz <sup>(2)</sup>  | 15-47 pF         | 15-47 pF         |

|             | 16 MHz                | TBD              | TBD              |

|             | 25 MHz                | 15-47 pF         | 15-47 pF         |

|             | 32 MHz <sup>(3)</sup> | <sub>0</sub> (3) | <sub>0</sub> (3) |

Higher capacitance increases the stability of the oscillator but also increases the start-up time and the oscillator current. These values are for design guidance only. Rs may be required in XT mode to avoid overdriving the crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values for external components.

- Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

- Rs of 330Ω is required for a capacitor combination of 15/15 pF.

- 3: Only the capacitance of the board was present.

#### **Crystals Used:**

| 32.768 kHz | Epson C-001R32.768K-A | ± 20 PPM     |

|------------|-----------------------|--------------|

| 1.0 MHz    | ECS-10-13-1           | $\pm$ 50 PPM |

| 2.0 MHz    | ECS-20-20-1           | $\pm$ 50 PPM |

| 4.0 MHz    | ECS-40-20-1           | ± 50 PPM     |

| 8.0 MHz    | ECS ECS-80-S-4        | ± 50 PPM     |

|            | ECS-80-18-1           |              |

| 16.0 MHz   | ECS-160-20-1          | TBD          |

| 25 MHz     | CTS CTS25M            | $\pm$ 50 PPM |

| 32 MHz     | CRYSTEK HF-2          | $\pm$ 50 PPM |

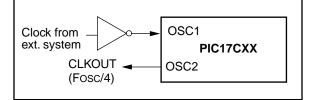

#### 14.2.3 EXTERNAL CLOCK OSCILLATOR

In the EC oscillator mode, the OSC1 input can be driven by CMOS drivers. In this mode, the OSC1/CLKIN pin is hi-impedance and the OSC2/CLK-OUT pin is the CLKOUT output (4 Tosc).

#### FIGURE 14-4: EXTERNAL CLOCK INPUT OPERATION (EC OSC CONFIGURATION)

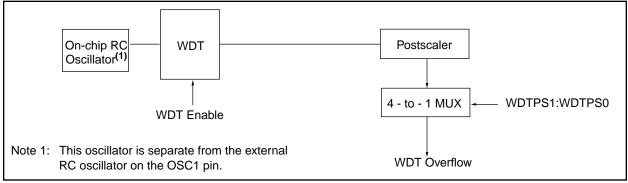

#### FIGURE 14-8: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 14-4: REGISTERS/BITS ASSOCIATED WITH THE WATCHDOG TIMER

| Address       | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------|-------|-------|-------|--------|--------|--------|-------|-------|-------------------------------|-----------------------------------------|

| —             | Config | -     | PM1   | -     | PM0    | WDTPS1 | WDTPS0 | FOSC1 | FOSC0 | (Note 2)                      | (Note 2)                                |

| 06h, Unbanked | CPUSTA |       |       | STKAV | GLINTD | TO     | PD     |       | —     | 11 11                         | 11 qq                                   |

Legend: - = unimplemented read as '0', q - value depends on condition, shaded cells are not used by the WDT.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

2: This value will be as the device was programmed, or if unprogrammed, will read as all '1's.

| ANDWF AND WREG with f                                  |                                                          |                             |                      |                       |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------|-----------------------------|----------------------|-----------------------|--|--|--|

| Syntax:                                                | [ <i>label</i> ] A                                       | NDWF                        | f,d                  |                       |  |  |  |

| Operands:                                              | $0 \le f \le 255$ $d \in [0,1]$                          | 5                           |                      |                       |  |  |  |

| Operation:                                             | (WREG) .                                                 | AND. (f)                    | $\rightarrow$ (dest) | )                     |  |  |  |

| Status Affected:                                       | Z                                                        |                             |                      |                       |  |  |  |

| Encoding:                                              | 0000                                                     | 101d                        | ffff                 | ffff                  |  |  |  |

| Description:                                           | The conten<br>register 'f'.<br>in WREG. I<br>back in reg | lf 'd' is 0<br>f 'd' is 1 t | the result           | is stored             |  |  |  |

| Words:                                                 | 1                                                        | 1                           |                      |                       |  |  |  |

| Cycles:                                                | 1                                                        |                             |                      |                       |  |  |  |

| Q Cycle Activity:                                      |                                                          |                             |                      |                       |  |  |  |

| Q1                                                     | Q2                                                       | Q3                          | 3                    | Q4                    |  |  |  |

| Decode                                                 | Read<br>register 'f'                                     | Execu                       |                      | Vrite to<br>stination |  |  |  |

| Example:                                               | ANDWF                                                    | REG, 1                      |                      |                       |  |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG | = 0x17<br>= 0xC2                                         |                             |                      |                       |  |  |  |

| BCF             |            | Bit Clear                        | f                                 |       |     |                     |  |  |

|-----------------|------------|----------------------------------|-----------------------------------|-------|-----|---------------------|--|--|

| Syntax:         |            | [label] E                        | BCF f,I                           | С     |     |                     |  |  |

| Operand         | s:         | $0 \le f \le 25$ $0 \le b \le 7$ | $0 \le f \le 255$ $0 \le b \le 7$ |       |     |                     |  |  |

| Operatio        | n:         | $0 \rightarrow (f < b >$         | -)                                |       |     |                     |  |  |

| Status A        | ffected:   | None                             |                                   |       |     |                     |  |  |

| Encoding        | g:         | 1000                             | 1bbb                              | fff   | f   | ffff                |  |  |

| Descripti       | ion:       | Bit 'b' in re                    | gister 'f' is                     | clear | ed. |                     |  |  |

| Words:          |            | 1                                |                                   |       |     |                     |  |  |

| Cycles:         |            | 1                                |                                   |       |     |                     |  |  |

| Q Cycle         | Activity:  |                                  |                                   |       |     |                     |  |  |

|                 | Q1         | Q2                               | Q3                                |       | Q4  |                     |  |  |

| D               | ecode      | Read<br>register 'f'             | Execu                             | ute   |     | Write<br>gister 'f' |  |  |

| <u>Example</u>  | :          | BCF                              | FLAG_R                            | EG,   | 7   |                     |  |  |

|                 | r Instruct | EG = 0xC7<br>tion                |                                   |       |     |                     |  |  |

| FLAG_REG = 0x47 |            |                                  |                                   |       |     |                     |  |  |

| BTF                                                                                                    | BTFSS Bit Test, skip if Set |                                                                                                                                                                                                                                                                            |                   |        |      |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------|------|--|--|--|--|

| Synt                                                                                                   | tax:                        | [ <i>label</i> ] E                                                                                                                                                                                                                                                         | [label] BTFSS f,b |        |      |  |  |  |  |

| Ope                                                                                                    | rands:                      |                                                                                                                                                                                                                                                                            | $0 \le f \le 127$ |        |      |  |  |  |  |

|                                                                                                        |                             | 0≤b<7                                                                                                                                                                                                                                                                      |                   |        |      |  |  |  |  |

| Ope                                                                                                    | ration:                     | skip if (f<                                                                                                                                                                                                                                                                | b>) = 1           |        |      |  |  |  |  |

| Stat                                                                                                   | us Affected:                | None                                                                                                                                                                                                                                                                       |                   |        |      |  |  |  |  |

| Enc                                                                                                    | oding:                      | 1001                                                                                                                                                                                                                                                                       | 0bbb              | ffff   | ffff |  |  |  |  |

| Des                                                                                                    | cription:                   | If bit 'b' in register 'f' is 1 then the next<br>instruction is skipped.<br>If bit 'b' is 1, then the next instruction<br>fetched during the current instruction exe-<br>cution, is discarded and an NOP is exe-<br>cuted instead, making this a two-cycle<br>instruction. |                   |        |      |  |  |  |  |

| Wor                                                                                                    | ds:                         | 1                                                                                                                                                                                                                                                                          | 1                 |        |      |  |  |  |  |

| Cycl                                                                                                   | les:                        | 1(2)                                                                                                                                                                                                                                                                       | 1(2)              |        |      |  |  |  |  |

| QC                                                                                                     | ycle Activity:              |                                                                                                                                                                                                                                                                            |                   |        |      |  |  |  |  |

|                                                                                                        | Q1                          | Q2                                                                                                                                                                                                                                                                         | Q3                |        | Q4   |  |  |  |  |

|                                                                                                        | Decode                      | Read<br>register 'f'                                                                                                                                                                                                                                                       | Execu             | ite    | NOP  |  |  |  |  |

| lf sk                                                                                                  | ip:                         |                                                                                                                                                                                                                                                                            |                   | · · ·  |      |  |  |  |  |

|                                                                                                        | Q1                          | Q2                                                                                                                                                                                                                                                                         | Q3                |        | Q4   |  |  |  |  |

|                                                                                                        | Forced NOP                  | NOP                                                                                                                                                                                                                                                                        | Execu             | ıte    | NOP  |  |  |  |  |

| Example:                                                                                               |                             | HERE<br>FALSE<br>TRUE                                                                                                                                                                                                                                                      | BTFSS<br>:<br>:   | FLAG,1 |      |  |  |  |  |

|                                                                                                        | Before Instru<br>PC         |                                                                                                                                                                                                                                                                            | ddress (HE        | RE)    |      |  |  |  |  |

| After Instruction<br>If FLAG<1> = 0;<br>PC = address (FALSE)<br>If FLAG<1> = 1;<br>PC = address (TRUE) |                             |                                                                                                                                                                                                                                                                            |                   |        |      |  |  |  |  |

| BTG                 | Bit Togg                  | le f                                                             |       |                   |  |  |  |

|---------------------|---------------------------|------------------------------------------------------------------|-------|-------------------|--|--|--|

| Syntax:             | [ label ]                 | BTG f,b                                                          |       |                   |  |  |  |

| Operands:           | •=•==                     | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b < 7 \end{array}$ |       |                   |  |  |  |

| Operation:          | ( <del>Ī<b></b></del> ) → | → (f <b>)</b>                                                    |       |                   |  |  |  |

| Status Affected     | : None                    |                                                                  |       |                   |  |  |  |

| Encoding:           | 0011                      | 1bbb                                                             | ffff  | ffff              |  |  |  |

| Description:        | Bit 'b' in d<br>inverted. | Bit 'b' in data memory location 'f' is inverted.                 |       |                   |  |  |  |

| Words:              | 1                         |                                                                  |       |                   |  |  |  |

| Cycles:             | 1                         |                                                                  |       |                   |  |  |  |

| Q Cycle Activity    | <b>/</b> :                |                                                                  |       |                   |  |  |  |

| Q1                  | Q2                        | Q3                                                               |       | Q4                |  |  |  |

| Decode              | Read<br>register 'f'      | Execut                                                           | •   · | /rite<br>ster 'f' |  |  |  |

| Example:            | BTG                       | PORTC,                                                           | 4     |                   |  |  |  |

| Before Inst<br>PORT |                           | 0101 <b>[0x7</b> 5                                               | 5]    |                   |  |  |  |

| After Instru        |                           | 0101 <b>[0x6</b> 5                                               | -1    |                   |  |  |  |

| SUBWF                                   | Sub                              | otrac             | t WREG                                           | from             | f                |                       |          |

|-----------------------------------------|----------------------------------|-------------------|--------------------------------------------------|------------------|------------------|-----------------------|----------|

| Syntax:                                 | [ lab                            | oel]              | SUBWF                                            | f,d              |                  |                       | -        |

| Operands:                               | -                                | f ≤ 25<br>[0,1]   | 55                                               |                  |                  |                       | :        |

| Operation:                              | (f) –                            | · (W)             | $\rightarrow$ (dest                              | )                |                  |                       |          |

| Status Affected:                        | OV,                              | C, D              | C, Z                                             |                  |                  |                       | (        |

| Encoding:                               | 00                               | 00                | 010d                                             | fff              | f                | ffff                  | :        |

| Description:                            | com<br>resu                      | pleme<br>It is si | VREG fro<br>ent metho<br>tored in W<br>tored bac | d). If '<br>/REG | d' is<br>. If 'c | 0 the<br>I' is 1 the  | l        |

| Words:                                  | 1                                |                   |                                                  |                  |                  |                       |          |

| Cycles:                                 | 1                                |                   |                                                  |                  |                  |                       | ,        |

| Q Cycle Activity:                       |                                  |                   |                                                  |                  |                  |                       |          |

| Q1                                      | Qź                               |                   | Q3                                               | 3                |                  | Q4                    |          |

| Decode                                  | Rea<br>registe                   |                   | Execu                                            | ute              |                  | Vrite to<br>stination |          |

|                                         |                                  |                   | DECI                                             | 1                | ue               | Sunation              |          |

| Example 1:                              | SUB                              | M F.              | REG1,                                            | T                |                  |                       |          |

| Before Instru<br>REG1<br>WREG<br>C      | Iction<br>= 3<br>= 2<br>= ?      |                   |                                                  |                  |                  |                       | <u> </u> |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= 1<br>= 2<br>= 1<br>= 0 | ;                 | result is p                                      | oositiv          | е                |                       |          |

| Example 2:                              |                                  |                   |                                                  |                  |                  |                       |          |

| Before Instru<br>REG1<br>WREG<br>C      | uction<br>= 2<br>= 2<br>= ?      |                   |                                                  |                  |                  |                       | <u> </u> |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= 0<br>= 2<br>= 1<br>= 1 | ;                 | result is z                                      | zero             |                  |                       |          |

| Example 3:                              |                                  |                   |                                                  |                  |                  |                       |          |

| Before Instru<br>REG1<br>WREG<br>C      | uction<br>= 1<br>= 2<br>= ?      |                   |                                                  |                  |                  |                       | ļ        |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= F<br>= 2<br>= 0<br>= 0 |                   | result is r                                      | negativ          | ve               |                       |          |

| SUBWFB                            |                | Subtract WREG from f with        |                                                                    |                                |                       |                       |  |

|-----------------------------------|----------------|----------------------------------|--------------------------------------------------------------------|--------------------------------|-----------------------|-----------------------|--|

| Syntax:                           |                | Borrow [ label ] SUBWFB f,d      |                                                                    |                                |                       |                       |  |

| Operands:                         |                | $0 \le f \le 2$                  |                                                                    | , u                            |                       |                       |  |

| Operands.                         |                | d ∈ [0,1                         | ]                                                                  |                                |                       |                       |  |

| Operation:                        |                | (f) – (W)                        | $) - \overline{C} \rightarrow (0)$                                 | dest)                          |                       |                       |  |

| Status Affect                     | ed:            | OV, C, E                         | DC, Z                                                              |                                |                       |                       |  |

| Encoding:                         |                | 0000                             | 001d                                                               | fff                            | f                     | ffff                  |  |

| Description:                      |                | (borrow)<br>ment me<br>stored in | WREG an<br>from regis<br>thod). If 'd'<br>WREG. If<br>ack in regis | ter 'f'<br>is 0 tl<br>'d' is ´ | (2's<br>he r<br>1 the | comple-<br>esult is   |  |

| Words:                            |                | 1                                |                                                                    |                                |                       |                       |  |

| Cycles:                           |                | 1                                |                                                                    |                                |                       |                       |  |

| Q Cycle Activ                     | /ity:          |                                  |                                                                    |                                |                       |                       |  |

| Q1                                |                | Q2                               | Q3                                                                 |                                |                       | Q4                    |  |

| Decod                             | -              | Read<br>egister 'f'              | Execu                                                              | ıte                            |                       | Vrite to<br>stination |  |

| Example 1:                        |                | SUBWFB                           | REG1,                                                              | 1                              |                       |                       |  |

| Before Ir                         | nstructio      | on                               |                                                                    |                                |                       |                       |  |

| REG<br>WRE<br>C                   |                | 0x19<br>0x0D<br>1                | (0001<br>(0000                                                     |                                | '                     |                       |  |

| After Ins                         | truction       | 1                                |                                                                    |                                |                       |                       |  |

| REG<br>WRE<br>C                   | EG =<br>=      | 0x0C<br>0x0D<br>1                | (0000<br>(0000<br>; <b>resul</b> t                                 | 110                            | 1)                    | e                     |  |

| Z                                 | =              | 0                                |                                                                    |                                |                       |                       |  |

| Example2:                         |                | UBWFB                            | REG1,0                                                             |                                |                       |                       |  |

| Before Ir<br>REG<br>WRE<br>C      | 61 =           | 0x1B                             | (0001<br>(0001                                                     |                                | ,                     |                       |  |

| After Ins                         | truction       | 1                                |                                                                    |                                |                       |                       |  |

| REG                               |                | 0x1B                             | (0001                                                              | 101                            | 1)                    |                       |  |

| WRE<br>C<br>Z                     | EG =<br>=<br>= | 0x00<br>1<br>1                   | ; resul                                                            | t is ze                        | ro                    |                       |  |

| Example3:                         | S              | UBWFB                            | REG1,1                                                             |                                |                       |                       |  |

| Before Ir                         |                | on                               |                                                                    |                                |                       |                       |  |

| REG<br>WRE<br>C                   |                | 0x03<br>0x0E<br>1                | (0000<br>(0000                                                     |                                |                       |                       |  |

| After Ins<br>REG<br>WRE<br>C<br>Z | 61 =           | 0xF5<br>0x0E<br>0<br>0           | (1111<br>(0000<br>; <b>resul</b> t                                 | 110                            | 1)                    | ?'s comp]<br>ve       |  |

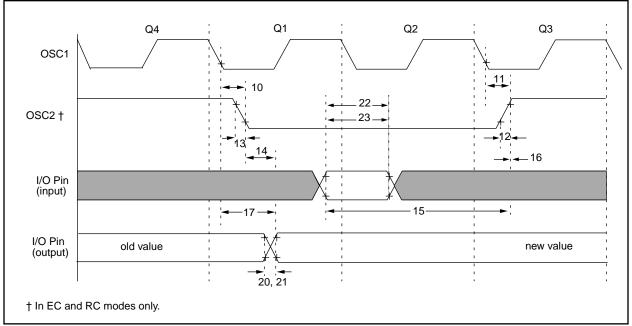

#### FIGURE 17-3: CLKOUT AND I/O TIMING

#### TABLE 17-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                 | Min            | Тур† | Max          | Units | Conditions |

|------------------|----------|------------------------------------------------|----------------|------|--------------|-------|------------|

| 10               | TosH2ckL | OSC1↑ to CLKOUT↓                               |                | 15 ‡ | 30 ‡         | ns    | Note 1     |

| 11               | TosH2ckH | OSC1↑ to CLKOUT↑                               | —              | 15‡  | 30 ‡         | ns    | Note 1     |

| 12               | TckR     | CLKOUT rise time                               | —              | 5‡   | 15 ‡         | ns    | Note 1     |

| 13               | TckF     | CLKOUT fall time                               | —              | 5‡   | 15 ‡         | ns    | Note 1     |

| 14               | TckH2ioV | CLKOUT <sup>↑</sup> to Port out valid          | —              | —    | 0.5Tcy + 20‡ | ns    | Note 1     |

| 15               | TioV2ckH | Port in valid before CLKOUT                    | 0.25Tcy + 25 ‡ | —    | —            | ns    | Note 1     |

| 16               | TckH2iol | Port in hold after CLKOUT                      | 0 ‡            | —    | —            | ns    | Note 1     |

| 17               | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid | —              | —    | 100 ‡        | ns    |            |

| 20               | TioR     | Port output rise time                          | —              | 10 ‡ | 35 ‡         | ns    |            |

| 21               | TioF     | Port output fall time                          | —              | 10 ‡ | 35 ‡         | ns    |            |

| 22               | TinHL    | INT pin high or low time                       | 25 *           | —    | —            | ns    |            |

| 23               | TrbHL    | RB7:RB0 change INT high or low time            | 25 *           | —    | —            | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Measurements are taken in EC Mode where OSC2 output = 4 x Tosc = Tcy.

## Applicable Devices 42 R42 42A 43 R43 44

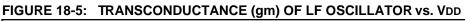

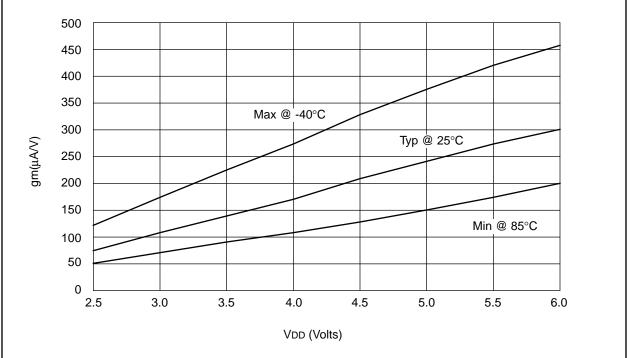

FIGURE 18-6: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

## 19.1 DC CHARACTERISTICS:

#### PIC17CR42/42A/43/R43/44-16 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-25 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-33 (Commercial, Industrial)

| DC CHARACT       | CDIETI |                                                                  | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature |      |      |       |                                           |  |

|------------------|--------|------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|-------|-------------------------------------------|--|

|                  | ERISTI | 63                                                               |                                                                                  |      |      | -40°C |                                           |  |

|                  |        | i                                                                |                                                                                  |      |      | 0°C   | $\leq$ TA $\leq$ +70°C for commercial     |  |

| Parameter<br>No. | Sym    | Characteristic                                                   | Min                                                                              | Тур† | Мах  | Units | Conditions                                |  |

| D001             | Vdd    | Supply Voltage                                                   | 4.5                                                                              | _    | 6.0  | V     |                                           |  |

| D002             | Vdr    | RAM Data Retention<br>Voltage (Note 1)                           | 1.5 *                                                                            | _    | —    | V     | Device in SLEEP mode                      |  |

| D003             | VPOR   | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | _                                                                                | Vss  | -    | V     | See section on Power-on Reset for details |  |

| D004             | SVDD   | VDD rise rate to<br>ensure internal<br>Power-on Reset signal     | 0.060 *                                                                          | _    | _    | mV/ms | See section on Power-on Reset for details |  |

| D010             | IDD    | Supply Current                                                   | -                                                                                | 3    | 6    | mA    | Fosc = 4 MHz (Note 4)                     |  |

| D011             |        | (Note 2)                                                         | -                                                                                | 6    | 12 * | mA    | Fosc = 8 MHz                              |  |

| D012             |        |                                                                  | -                                                                                | 11   | 24 * | mA    | Fosc = 16 MHz                             |  |

| D013             |        |                                                                  | -                                                                                | 19   | 38   | mA    | Fosc = 25 MHz                             |  |

| D015             |        |                                                                  | -                                                                                | 25   | 50   | mA    | Fosc = 33 MHz                             |  |

| D014             |        |                                                                  | -                                                                                | 95   | 150  | μA    | Fosc = 32 kHz,                            |  |

|                  |        |                                                                  |                                                                                  |      |      |       | WDT enabled (EC osc configuration)        |  |

| D020             | IPD    | Power-down                                                       | _                                                                                | 10   | 40   | μA    | VDD = 5.5V, WDT enabled                   |  |

| D021             |        | Current (Note 3)                                                 | -                                                                                | < 1  | 5    | μA    | VDD = 5.5V, WDT disabled                  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD or VSS, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

Current consumed from the oscillator and I/O's driving external capacitive or resistive loads needs to be considered.

For the RC oscillator, the current through the external pull-up resistor (R) can be estimated as:  $VDD / (2 \bullet R)$ . For capacitive loads, the current can be estimated (for an individual I/O pin) as (CL • VDD) • f

CL = Total capacitive load on the I/O pin; f = average frequency the I/O pin switches.

The capacitive currents are most significant when the device is configured for external execution (includes extended microcontroller mode).

- 3: The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VbD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IR = VDD/2Rext (mA) with Rext in kOhm.

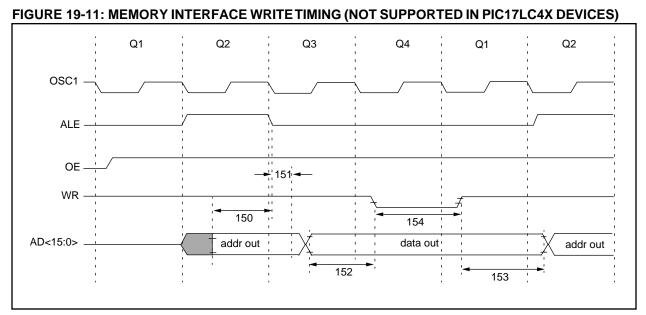

## TABLE 19-11: MEMORY INTERFACE WRITE REQUIREMENTS (NOT SUPPORTED IN PIC17LC4X DEVICES)

| Parameter<br>No. | Sym      | Characteristic                                                 | Min          | Тур†      | Мах | Units | Conditions |

|------------------|----------|----------------------------------------------------------------|--------------|-----------|-----|-------|------------|

| 150              | TadV2alL | AD<15:0> (address) valid to ALE↓<br>(address setup time)       | 0.25Tcy - 10 |           | _   | ns    |            |

| 151              | TalL2adI | ALE↓ to address out invalid<br>(address hold time)             | 0            | _         | —   | ns    |            |

| 152              | TadV2wrL | Data out valid to $\overline{WR} \downarrow$ (data setup time) | 0.25Tcy - 40 | _         | _   | ns    |            |

| 153              | TwrH2adl | WR↑ to data out invalid<br>(data hold time)                    | _            | 0.25Tcy § | _   | ns    |            |

| 154              | TwrL     | WR pulse width                                                 | —            | 0.25Tcy § | —   | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

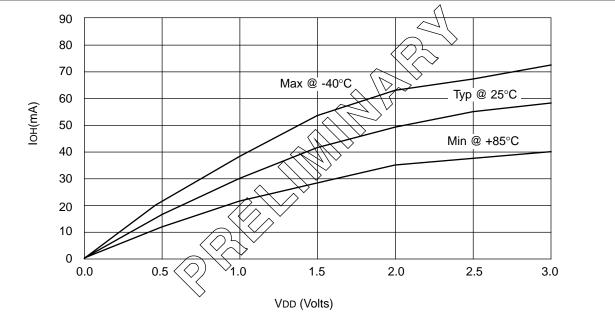

### FIGURE 20-17: IOL vs. VOL, VDD = 5V

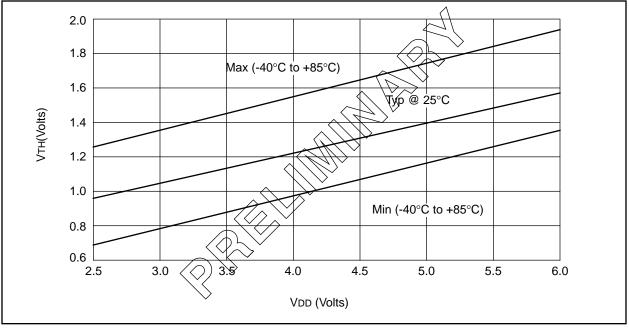

#### FIGURE 20-18: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS (TTL) VS. VDD

| MP-C C Compiler          | 145 |

|--------------------------|-----|

| MPSIM Software Simulator |     |

| MULLW                    | 129 |

| Multiply Examples        |     |

| 16 x 16 Routine          | 50  |

| 16 x 16 Signed Routine   | 51  |

| 8 x 8 Routine            | 49  |

| 8 x 8 Signed Routine     | 49  |

| MULWF                    | 129 |

## Ν

| NEGW    | ) |

|---------|---|

| NOP 130 | ` |

| NOP     | ' |

## 0

| OERR                                       | 84       |

|--------------------------------------------|----------|

| Opcode Field Descriptions                  | 107      |

| OSC Selection                              |          |

| Oscillator                                 |          |

| Configuration                              | 100      |

| Crystal                                    |          |

| External Clock                             | 101      |

| External Crystal Circuit                   | 102      |

| External Parallel Resonant Crystal Circuit | 102      |

| External Series Resonant Crystal Circuit   | 102      |

| RC                                         |          |

| RC Frequencies                             | 165, 195 |

| Oscillator Start-up Time (Figure)          |          |

| Oscillator Start-up Timer (OST)            | 15, 99   |

| OST                                        |          |

| OV                                         |          |

| Overflow (OV)                              | 9        |

## Ρ

| Package Marking Information                       |             |

|---------------------------------------------------|-------------|

| Packaging Information                             |             |

| Parameter Measurement Information                 |             |

| PC (Program Counter)                              |             |

| PCH                                               |             |

| PCL                                               | 34, 41, 108 |

| PCLATH                                            |             |

| PD                                                |             |

| PEIE                                              |             |

| PEIF                                              |             |

| Peripheral Bank                                   |             |

| Peripheral Interrupt Enable                       | 23          |

| Peripheral Interrupt Request (PIR)                | 24          |

| PICDEM-1 Low-Cost PIC16/17 Demo Board             | 143, 144    |

| PICDEM-2 Low-Cost PIC16CXX Demo Board             | 143, 144    |

| PICDEM-3 Low-Cost PIC16C9XXX Demo Boar            | d144        |

| PICMASTER <sup>®</sup> RT In-Circuit Emulator     |             |

| PICSTART <sup>®</sup> Low-Cost Development System |             |

| PIE                                               |             |

| Pin Compatible Devices                            |             |

| PIR                                               |             |

| PM0                                               |             |

| PM1                                               |             |

| POP                                               |             |

| POR                                               |             |

| PORTA                                             | 19, 34, 53  |

| PORTB                                             | 19, 34, 55  |

| PORTC                                             | 19, 34, 58  |

| PORTD                                      |       |     |    |

|--------------------------------------------|-------|-----|----|

| PORTE                                      | 19,   | 34, | 62 |

| Power-down Mode                            |       | 1   | 05 |

| Power-on Reset (POR)                       |       |     |    |

| Power-up Timer (PWRT)                      |       |     |    |

| PR1                                        |       |     |    |

| PR2                                        |       |     |    |

| PR3/CA1H                                   |       |     |    |

| PR3/CA1L                                   |       |     |    |

| PR3H/CA1H                                  |       |     |    |

|                                            |       |     |    |

| PR3L/CA1L                                  |       |     |    |

| Prescaler Assignments                      | ••••• |     | 69 |

| PRO MATE <sup>®</sup> Universal Programmer |       |     |    |

| PRODH                                      |       |     |    |

| PRODL                                      |       |     |    |

| Program Counter (PC)                       | ••••• |     | 41 |

| Program Memory                             |       |     |    |

| External Access Waveforms                  |       |     |    |

| External Connection Diagram                |       |     | 31 |

| Мар                                        |       |     | 29 |

| Modes                                      |       |     |    |

| Extended Microcontroller                   |       |     | 29 |

| Microcontroller                            |       |     |    |

| Microprocessor                             |       |     |    |

| Protected Microcontroller                  |       |     |    |

| Operation                                  |       |     |    |

| Organization                               |       |     |    |

| Transfers from Data Memory                 |       |     |    |

|                                            |       |     |    |

| Protected Microcontroller                  |       |     |    |

| PS0                                        |       |     |    |

| PS1                                        |       |     |    |

| PS2                                        |       |     |    |

| PS3                                        |       |     |    |

| PUSH                                       |       |     |    |

| PW1DCH                                     |       | 20, | 35 |

| PW1DCL                                     |       | 20, | 35 |

| PW2DCH                                     |       |     |    |

| PW2DCL                                     |       | 20, | 35 |

| PWM                                        |       | 71, | 75 |

| Duty Cycle                                 |       |     | 76 |

| External Clock Source                      |       |     |    |

| Frequency vs. Resolution                   |       |     |    |

| Interrupts                                 |       |     |    |

| Max Resolution/Frequency for External      |       |     |    |

| Clock Input                                |       |     | 77 |

| Output                                     |       |     | 75 |

| Periods                                    |       |     |    |

|                                            |       |     | -  |

| PWM1                                       |       |     |    |

| PWM10N                                     |       |     |    |

| PWM2                                       |       |     |    |

| PWM2ON                                     |       |     |    |

| PWRT                                       |       | 15, | 99 |

## R

| RA1/T0CKI pin             |                        |

|---------------------------|------------------------|

| RBIE                      |                        |

| RBIF                      |                        |

| RBPU                      |                        |

| RC Oscillator             |                        |

| RC Oscillator Frequencies |                        |

| RCIE                      |                        |

| RCIF                      |                        |

| RCREG                     | 19, 34, 91, 92, 96, 97 |

| RCSTA                     |                        |

| Reading 16-bit Value      |                        |

| 0                         |                        |