Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 25MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 454 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

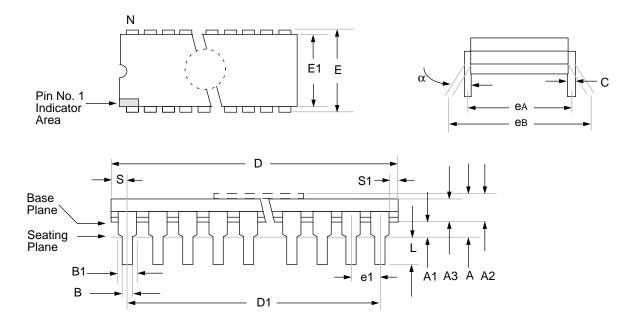

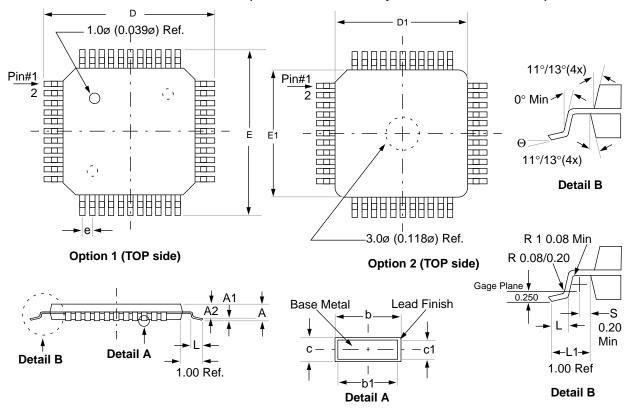

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-25e-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

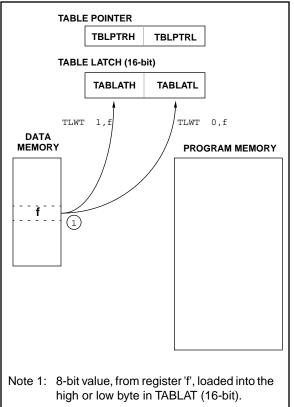

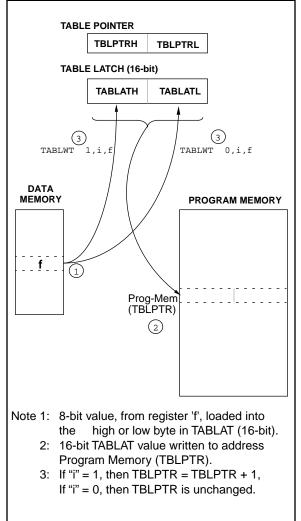

### 7.0 TABLE READS AND TABLE WRITES

The PIC17C4X has four instructions that allow the processor to move data from the data memory space to the program memory space, and vice versa. Since the program memory space is 16-bits wide and the data memory space is 8-bits wide, two operations are required to move 16-bit values to/from the data memory.

The TLWT t,f and TABLWT t,i,f instructions are used to write data from the data memory space to the program memory space. The TLRD t,f and TABLRD t,i,f instructions are used to write data from the program memory space to the data memory space.

The program memory can be internal or external. For the program memory access to be external, the device needs to be operating in extended microcontroller or microprocessor mode.

Figure 7-1 through Figure 7-4 show the operation of these four instructions.

#### FIGURE 7-2: TABLWT INSTRUCTION OPERATION

© 1996 Microchip Technology Inc.

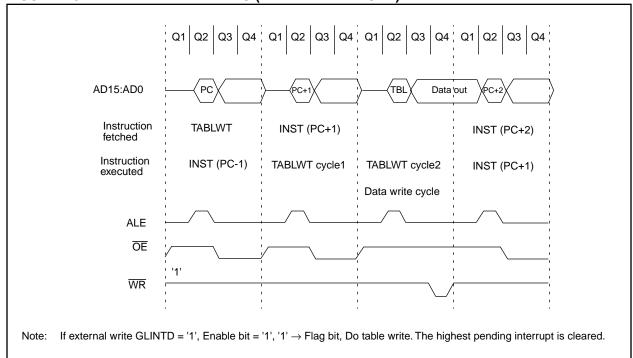

#### 7.2 <u>Table Writes to External Memory</u>

Table writes to external memory are always two-cycle instructions. The second cycle writes the data to the external memory location. The sequence of events for an external memory write are the same for an internal write.

| Note: | If an interrupt is pending or occurs during the TABLWT, the two cycle table write |  |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | completes. The RA0/INT, TMR0, or T0CKI                                            |  |  |  |  |  |  |  |

|       | interrupt flag is automatically cleared or                                        |  |  |  |  |  |  |  |

|       | the pending peripheral interrupt is                                               |  |  |  |  |  |  |  |

|       | acknowledged.                                                                     |  |  |  |  |  |  |  |

7.2.2 TABLE WRITE CODE

The "i" operand of the TABLWT instruction can specify that the value in the 16-bit TBLPTR register is automatically incremented for the next write. In Example 7-1, the TBLPTR register is not automatically incremented.

#### EXAMPLE 7-1: TABLE WRITE

| CLRWDT |                 | ; | Clear WDT      |

|--------|-----------------|---|----------------|

| MOVLW  | HIGH (TBL_ADDR) | ; | Load the Table |

| MOVWF  | TBLPTRH         | ; | address        |

| MOVLW  | LOW (TBL_ADDR)  | ; |                |

| MOVWF  | TBLPTRL         | ; |                |

| MOVLW  | HIGH (DATA)     | ; | Load HI byte   |

| TLWT   | 1, WREG         | ; | in TABLATCH    |

| MOVLW  | LOW (DATA)      | ; | Load LO byte   |

| TABLWT | 0,0,WREG        | ; | in TABLATCH    |

|        |                 | ; | and write to   |

|        |                 | ; | program memory |

|        |                 | ; | (Ext. SRAM)    |

|        |                 |   |                |

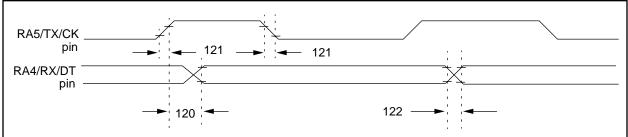

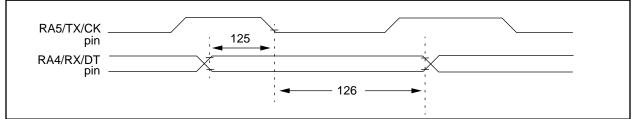

#### FIGURE 7-5: TABLWT WRITE TIMING (EXTERNAL MEMORY)

# FIGURE 13-2: RCSTA REGISTER (ADDRESS: 13h, BANK 0)

| SPEN   | N.W0         R/W - 0         R/W - 0         U - 0         R - 0         R - 0         R - x           RX9         SREN         CREN         —         FERR         OERR         RX9D         R = Readable bit                                                                                                                                             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit7   | bit 0<br>W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)                                                                                                                                                                                                                                                                                      |

| bit 7: | <b>SPEN</b> : Serial Port Enable bit<br>1 = Configures RA5/RX/DT and RA4/TX/CK pins as serial port pins<br>0 = Serial port disabled                                                                                                                                                                                                                        |

| bit 6: | <b>RX9</b> : 9-bit Receive Enable bit<br>1 = Selects 9-bit reception<br>0 = Selects 8-bit reception                                                                                                                                                                                                                                                        |

| bit 5: | SREN: Single Receive Enable bit         This bit enables the reception of a single byte. After receiving the byte, this bit is automatically cleared.         Synchronous mode:         1 = Enable reception         0 = Disable reception         Note: This bit is ignored in synchronous slave reception.         Asynchronous mode:         Don't care |

| bit 4: | CREN: Continuous Receive Enable bit<br>This bit enables the continuous reception of serial data.<br><u>Asynchronous mode:</u><br>1 = Enable reception<br>0 = Disables reception<br><u>Synchronous mode:</u><br>1 = Enables continuous reception until CREN is cleared (CREN overrides SREN)<br>0 = Disables continuous reception                           |

| bit 3: | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                 |

| bit 2: | FERR: Framing Error bit<br>1 = Framing error (Updated by reading RCREG)<br>0 = No framing error                                                                                                                                                                                                                                                            |

| bit 1: | OERR: Overrun Error bit<br>1 = Overrun (Cleared by clearing CREN)<br>0 = No overrun error                                                                                                                                                                                                                                                                  |

| bit 0: | <b>RX9D</b> : 9th bit of receive data (can be the software calculated parity bit)                                                                                                                                                                                                                                                                          |

# 14.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real time applications. The PIC17CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- OSC selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- · Code protection

The PIC17CXX has a Watchdog Timer which can be shut off only through EPROM bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 96 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake from SLEEP through external reset, Watchdog Timer Reset or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LF crystal option saves power. Configuration bits are used to select various options. This configuration word has the format shown in Figure 14-1.

| <u>R/P - 1</u><br>PM2 <sup>(1)</sup>                                                                                                                                                                                  | U - x                                                       | U - x                                  | <u>U-x</u>                         | U - x       | U - x   | <u>U-x</u> | U - x         |                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------|------------------------------------|-------------|---------|------------|---------------|-----------------------------------------------------------------------------------------------------------------|

| bit15-7                                                                                                                                                                                                               |                                                             |                                        | _                                  |             |         |            | bit0          |                                                                                                                 |

| U - x                                                                                                                                                                                                                 | R/P - 1                                                     | U - x                                  | <u>R/P - 1</u>                     | R/P - 1     | R/P - 1 | R/P - 1    | R/P - 1       | R = Readable bit                                                                                                |

| <br>bit15-7                                                                                                                                                                                                           | PM1                                                         |                                        | PM0                                | WDTPS1      | WDTPS0  | FOSC1      | FOSC0<br>bit0 | P = Programmable bit $P = Programmable bit$ $U = Unimplemented$ $- n = Value for Erased Device$ $(x = unknown)$ |

| bit 15-9:                                                                                                                                                                                                             | Unimpler                                                    | nented: R                              | ead as a                           | '1'         |         |            |               |                                                                                                                 |

|                                                                                                                                                                                                                       |                                                             | rocontrolle<br>ended mic<br>de protect | er mode<br>crocontrol<br>ed microc | ontroller m | ode     |            |               |                                                                                                                 |

| bit 7, 5:                                                                                                                                                                                                             | Unimpler                                                    | nented: R                              | ead as a                           | '0'         |         |            |               |                                                                                                                 |

| bit 3-2: <b>WDTPS1:WDTPS0</b> , WDT Postscaler Select bits<br>11 = WDT enabled, postscaler = 1<br>10 = WDT enabled, postscaler = 256<br>01 = WDT enabled, postscaler = 64<br>00 = WDT disabled, 16-bit overflow timer |                                                             |                                        |                                    |             |         |            |               |                                                                                                                 |

| bit 1-0:                                                                                                                                                                                                              | FOSC1:F<br>11 = EC (<br>10 = XT (<br>01 = RC (<br>00 = LF ( | oscillator<br>oscillator<br>oscillator | scillator S                        | elect bits  |         |            |               |                                                                                                                 |

|                                                                                                                                                                                                                       |                                                             |                                        |                                    |             |         |            |               |                                                                                                                 |

#### FIGURE 14-1: CONFIGURATION WORD

<sup>© 1996</sup> Microchip Technology Inc.

| ADD         | WFC                                                                                     | ADD WRE                                               | G and C                            | Carry bit            | to f                     |  |  |  |

|-------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------|----------------------|--------------------------|--|--|--|

| Synt        | ax:                                                                                     | [ <i>label</i> ] A[                                   | [ label ] ADDWFC f,d               |                      |                          |  |  |  |

| Ope         | rands:                                                                                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]                              | $0 \le f \le 255$<br>$d \in [0,1]$ |                      |                          |  |  |  |

| Ope         | ration:                                                                                 | (WREG) +                                              | - (f) + C -                        | $\rightarrow$ (dest) |                          |  |  |  |

| Statu       | us Affected:                                                                            | OV, C, DC                                             | , Z                                |                      |                          |  |  |  |

| Enco        | oding:                                                                                  | 0001                                                  | 000d                               | ffff                 | ffff                     |  |  |  |

| Desc        | cription:                                                                               | Add WREG<br>memory loc<br>placed in W<br>placed in da | ation 'f'. If<br>REG. If 'c        | 'd' is 0, the        | e result is<br>result is |  |  |  |

| Word        | ds:                                                                                     | 1                                                     |                                    |                      |                          |  |  |  |

| Cycl        | es:                                                                                     | 1                                                     |                                    |                      |                          |  |  |  |

| QC          | cle Activity:                                                                           |                                                       |                                    |                      |                          |  |  |  |

|             | Q1                                                                                      | Q2                                                    | Q3                                 |                      | Q4                       |  |  |  |

|             | Decode                                                                                  | Read<br>register 'f'                                  | Execut                             |                      | rite to<br>tination      |  |  |  |

| <u>Exar</u> | <u>mple</u> :                                                                           | ADDWFC                                                | REG                                | 0                    |                          |  |  |  |

|             | Before Instru<br>Carry bit<br>REG<br>WREG<br>After Instruct<br>Carry bit<br>REG<br>WREG | = 1<br>= 0x02<br>= 0x4D                               |                                    |                      |                          |  |  |  |

| ANDLW                 | And Lite                                                                                                | ral with WRI             | EG               |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------|--------------------------|------------------|--|--|--|--|

| Syntax:               | [label] A                                                                                               | [ <i>label</i> ] ANDLW k |                  |  |  |  |  |

| Operands:             | $0 \le k \le 25$                                                                                        | 55                       |                  |  |  |  |  |

| Operation:            | (WREG)                                                                                                  | .AND. (k) $ ightarrow$   | (WREG)           |  |  |  |  |

| Status Affected:      | Z                                                                                                       |                          |                  |  |  |  |  |

| Encoding:             | 1011                                                                                                    | 0101 kk                  | kk kkkk          |  |  |  |  |

| Description:          | Description: The contents of WREG are AND'ed wi<br>the 8-bit literal 'k'. The result is placed<br>WREG. |                          |                  |  |  |  |  |

| Words:                | 1                                                                                                       |                          |                  |  |  |  |  |

| Cycles:               | 1                                                                                                       |                          |                  |  |  |  |  |

| Q Cycle Activity:     |                                                                                                         |                          |                  |  |  |  |  |

| Q1                    | Q2                                                                                                      | Q3                       | Q4               |  |  |  |  |

| Decode                | Read literal<br>'k'                                                                                     | Execute                  | Write to<br>WREG |  |  |  |  |

| Example:              | ANDLW                                                                                                   | 0x5F                     |                  |  |  |  |  |

| Before Instru<br>WREG | uction<br>= 0xA3                                                                                        |                          |                  |  |  |  |  |

| After Instruc<br>WREG | tion<br>= 0x03                                                                                          |                          |                  |  |  |  |  |

| INC          | F                               | Inc                 | cremer              | nt f                        |                                               |                       |

|--------------|---------------------------------|---------------------|---------------------|-----------------------------|-----------------------------------------------|-----------------------|

| Synt         | tax:                            | [ <i>l</i> a        | abel]               | INCF f                      | ,d                                            |                       |

| Ope          | rands:                          |                     | ≤ f ≤ 25<br>₌ [0,1] | 5                           |                                               |                       |

| Ope          | ration:                         | (f)                 | + 1 $\rightarrow$   | (dest)                      |                                               |                       |

| Stat         | us Affected:                    | O\                  | /, C, D0            | C, Z                        |                                               |                       |

| Enco         | oding:                          | (                   | 0001                | 010d                        | ffff                                          | ffff                  |

| Description: |                                 |                     | ented. If           | 'd' is 0 the<br>d' is 1 the | ister 'f' are<br>e result is<br>e result is p | placed in             |

| Wor          | ds:                             | 1                   |                     |                             |                                               |                       |

| Cycl         | es:                             | 1                   |                     |                             |                                               |                       |

| QC           | ycle Activity:                  |                     |                     |                             |                                               |                       |

|              | Q1                              |                     | Q2                  | Q                           | 3                                             | Q4                    |

|              | Decode                          |                     | tead<br>ister 'f'   | Exect                       |                                               | Vrite to<br>stination |

| <u>Exa</u>   | <u>mple</u> :                   | IN                  | CF                  | CNT,                        | 1                                             |                       |

|              | Before Instru                   | iction              | 1                   |                             |                                               |                       |

|              | CNT                             | =                   | 0xFF                |                             |                                               |                       |

|              | Z<br>C                          | =                   | 0<br>?              |                             |                                               |                       |

|              | After Instruct<br>CNT<br>Z<br>C | tion<br>=<br>=<br>= | 0x00<br>1<br>1      |                             |                                               |                       |

| INCFSZ                                                                                                         | Incremen                                                                                                                                                                                                                                                                                                                  | t f, skip if (                                                    | )                    |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|--|--|--|--|

| Syntax:                                                                                                        | [ label ]                                                                                                                                                                                                                                                                                                                 | [label] INCFSZ f,d                                                |                      |  |  |  |  |

| Operands:                                                                                                      | 0 ≤ f ≤ 255<br>d ∈ [0,1]                                                                                                                                                                                                                                                                                                  | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |                      |  |  |  |  |

| Operation:                                                                                                     | (f) + 1 $\rightarrow$ (skip if resu                                                                                                                                                                                                                                                                                       |                                                                   |                      |  |  |  |  |

| Status Affected:                                                                                               | None                                                                                                                                                                                                                                                                                                                      |                                                                   |                      |  |  |  |  |

| Encoding:                                                                                                      | 0001                                                                                                                                                                                                                                                                                                                      | 111d f:                                                           | fff ffff             |  |  |  |  |

| Description:                                                                                                   | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded,<br>and an NOP is executed instead making<br>it a two-cycle instruction. |                                                                   |                      |  |  |  |  |

| Words:                                                                                                         | 1                                                                                                                                                                                                                                                                                                                         |                                                                   |                      |  |  |  |  |

| Cycles:                                                                                                        | 1(2)                                                                                                                                                                                                                                                                                                                      | 1(2)                                                              |                      |  |  |  |  |

| Q Cycle Activity:                                                                                              |                                                                                                                                                                                                                                                                                                                           |                                                                   |                      |  |  |  |  |

| Q1                                                                                                             | Q2                                                                                                                                                                                                                                                                                                                        | Q3                                                                | Q4                   |  |  |  |  |

| Decode                                                                                                         | Read<br>register 'f'                                                                                                                                                                                                                                                                                                      | Execute                                                           | Write to destination |  |  |  |  |

| lf skip:                                                                                                       |                                                                                                                                                                                                                                                                                                                           |                                                                   |                      |  |  |  |  |

| Q1                                                                                                             | Q2                                                                                                                                                                                                                                                                                                                        | Q3                                                                | Q4                   |  |  |  |  |

| Forced NOP                                                                                                     | NOP                                                                                                                                                                                                                                                                                                                       | Execute                                                           | NOP                  |  |  |  |  |

| Example:                                                                                                       | NZERO                                                                                                                                                                                                                                                                                                                     | INCFSZ C<br>:<br>:                                                | 'NT, 1               |  |  |  |  |

| Before Instr                                                                                                   |                                                                                                                                                                                                                                                                                                                           |                                                                   |                      |  |  |  |  |

|                                                                                                                | PC = Address (HERE)                                                                                                                                                                                                                                                                                                       |                                                                   |                      |  |  |  |  |

| After Instruction<br>CNT = CNT + 1 If CNT = 0;<br>$PC = Address(ZERO)$ If CNT $\neq$ 0;<br>PC = Address(NZERO) |                                                                                                                                                                                                                                                                                                                           |                                                                   |                      |  |  |  |  |

| TABLWT            | Table Wr    | ite      |         |                |

|-------------------|-------------|----------|---------|----------------|

| Example1:         | TABLWT      | 0, 1,    | REG     |                |

| Before Instruc    | tion        |          |         |                |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA356  |                |

| MEMORY            | (TBLPTR)    | =        | 0xFFFI  | F              |

| After Instruction | on (table v | vrite co | mpletio | n)             |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0x53    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA357  | 7              |

| MEMORY            | (TBLPTR -   | 1) =     | 0x5355  | 5              |

| Example 2:        | TABLWT      | 1, 0,    | REG     |                |

| Before Instruc    | tion        |          |         |                |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA356  | 6              |

| MEMORY            | (TBLPTR)    | =        | 0xFFFI  | F              |

| After Instruction | on (table v | vrite co | mpletio | n)             |

| REG               | ,           | =        | 0x53    | ,              |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x53    |                |

| TBLPTR            |             | =        | 0xA356  | 6              |

| MEMORY            | (TBLPTR)    | =        | 0xAA5   | 3              |

|                   |             |          |         |                |

|                   | 1           |          | г       |                |

| Program<br>Memory | 15          |          | 0       | Data<br>Momory |

| Wiethory          |             |          |         | Memory         |

|                   | ( 🖳         | TBLPTR   |         |                |

|                                       | TBLPTR       |

|---------------------------------------|--------------|

| · · · · · · · · · · · · · · · · · · · |              |

| 16 bits                               | TBLAT 8 bits |

| TLR   | D                 | Table Lat                                                                      | ch Read                                                                                                                                                                                                                                                    |                |  |  |  |  |

|-------|-------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|

| Synt  | ax:               | [ label ]                                                                      | ΓLRD t,f                                                                                                                                                                                                                                                   |                |  |  |  |  |

| Ope   | rands:            | 0 ≤ f ≤ 25<br>t ∈ [0,1]                                                        | $0 \le f \le 255$<br>t $\in [0,1]$                                                                                                                                                                                                                         |                |  |  |  |  |

| Ope   | ration:           | lf t = 0,<br>TBLAT                                                             | $L \rightarrow f;$                                                                                                                                                                                                                                         |                |  |  |  |  |

|       |                   | lf t = 1,<br>TBLAT                                                             | $H \to f$                                                                                                                                                                                                                                                  |                |  |  |  |  |

| State | us Affected:      | None                                                                           |                                                                                                                                                                                                                                                            |                |  |  |  |  |

| Enco  | oding:            | 1010                                                                           | 00tx ff                                                                                                                                                                                                                                                    | ff ffff        |  |  |  |  |

| Des   | cription:         | (TBLAT) in<br>is unaffected<br>If t = 1; high<br>If t = 0; low<br>This instrue | Read data from 16-bit table latch<br>(TBLAT) into file register 'f'. Table Latch<br>is unaffected.<br>If $t = 1$ ; high byte is read<br>If $t = 0$ ; low byte is read<br>This instruction is used in conjunction<br>with TABLRD to transfer data from pro- |                |  |  |  |  |

| Wor   | de                | 1                                                                              |                                                                                                                                                                                                                                                            | mory.          |  |  |  |  |

| Cycl  |                   | 1                                                                              |                                                                                                                                                                                                                                                            |                |  |  |  |  |

|       | ycle Activity:    | 1                                                                              |                                                                                                                                                                                                                                                            |                |  |  |  |  |

| QU    | Q1                | Q2                                                                             | Q3                                                                                                                                                                                                                                                         | Q4             |  |  |  |  |

|       | Decode            | Read                                                                           | Execute                                                                                                                                                                                                                                                    | Write          |  |  |  |  |

|       |                   | register<br>TBLATH or<br>TBLATL                                                |                                                                                                                                                                                                                                                            | register 'f'   |  |  |  |  |

| Exar  | <u>mple</u> :     | TLRD                                                                           | t, RAM                                                                                                                                                                                                                                                     |                |  |  |  |  |

|       | Before Instru     | uction                                                                         |                                                                                                                                                                                                                                                            |                |  |  |  |  |

|       | t                 | = 0                                                                            |                                                                                                                                                                                                                                                            |                |  |  |  |  |

|       | RAM<br>TBLAT      | = ?<br>= 0x00AF                                                                | (TBLATH =<br>(TBLATL =                                                                                                                                                                                                                                     | ,              |  |  |  |  |

|       | After Instruct    | tion                                                                           | ·                                                                                                                                                                                                                                                          |                |  |  |  |  |

|       | RAM<br>TBLAT      | = 0xAF<br>= 0x00AF                                                             | (TBLATH =<br>(TBLATL =                                                                                                                                                                                                                                     | ,              |  |  |  |  |

|       | Before Instru     | uction                                                                         | ·                                                                                                                                                                                                                                                          |                |  |  |  |  |

|       | t                 | = 1                                                                            |                                                                                                                                                                                                                                                            |                |  |  |  |  |

|       | RAM<br>TBLAT      | = ?<br>= 0x00AF                                                                | (TBLATH =<br>(TBLATL =                                                                                                                                                                                                                                     | ,              |  |  |  |  |

|       | After Instruct    | tion                                                                           |                                                                                                                                                                                                                                                            |                |  |  |  |  |

|       | RAM<br>TBLAT      | = 0x00<br>= 0x00AF                                                             | (TBLATH =<br>(TBLATL =                                                                                                                                                                                                                                     | ,              |  |  |  |  |

|       | Program<br>Memory | 15                                                                             | 0                                                                                                                                                                                                                                                          | Data<br>Memory |  |  |  |  |

|       |                   | -   ( <sup>m</sup>                                                             | BLPTR                                                                                                                                                                                                                                                      |                |  |  |  |  |

| ·     |                   | -1_                                                                            |                                                                                                                                                                                                                                                            | ÷              |  |  |  |  |

|       | 16 bits           |                                                                                | BLAT                                                                                                                                                                                                                                                       | 8 bits         |  |  |  |  |

| XORLW             | Exclusive OR Literal with                                                                       | XORWF                         | Exclusive OR WREG with f                                                                                                                                           |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                   | WREG                                                                                            | Syntax:                       | [label] XORWF f,d                                                                                                                                                  |  |  |  |  |

| Syntax:           | [ <i>label</i> ] XORLW k                                                                        | Operands:                     | $0 \le f \le 255$                                                                                                                                                  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                               |                               | d ∈ [0,1]                                                                                                                                                          |  |  |  |  |

| Operation:        | (WREG) .XOR. $k \rightarrow (WREG)$                                                             | Operation:                    | (WREG) .XOR. (f) $\rightarrow$ (dest)                                                                                                                              |  |  |  |  |

| Status Affected:  | Z                                                                                               | Status Affected:              | Z                                                                                                                                                                  |  |  |  |  |

| Encoding:         | 1011 0100 kkkk kkkk                                                                             | Encoding:                     | 0000 110d ffff ffff                                                                                                                                                |  |  |  |  |

| Description:      | The contents of WREG are XOR'ed<br>with the 8-bit literal 'k'. The result is<br>placed in WREG. | Description:                  | Exclusive OR the contents of WREG<br>with register 'f'. If 'd' is 0 the result is<br>stored in WREG. If 'd' is 1 the result is<br>stored back in the register 'f'. |  |  |  |  |

| Words:            | 1                                                                                               | Words:                        | 1                                                                                                                                                                  |  |  |  |  |

| Cycles:           | 1                                                                                               | Cycles:                       | 1                                                                                                                                                                  |  |  |  |  |

| Q Cycle Activity: |                                                                                                 | Q Cycle Activity:             |                                                                                                                                                                    |  |  |  |  |

| Q1                | Q2 Q3 Q4                                                                                        | Q1                            | Q2 Q3 Q4                                                                                                                                                           |  |  |  |  |

| Decode            | ReadExecuteWrite toliteral 'k'WREG                                                              | Decode                        | Read Execute Write to<br>register 'f' destination                                                                                                                  |  |  |  |  |

| Example:          | XORLW 0xAF                                                                                      | L                             |                                                                                                                                                                    |  |  |  |  |

| Before Instruc    | ction                                                                                           | Example:                      | XORWF REG, 1                                                                                                                                                       |  |  |  |  |

| After Instructi   | = 0xB5<br>on<br>= 0x1A                                                                          | Before Instru<br>REG<br>WREG  | ction<br>= 0xAF<br>= 0xB5                                                                                                                                          |  |  |  |  |

|                   |                                                                                                 | After Instruct<br>REG<br>WREG | ion<br>= 0x1A<br>= 0xB5                                                                                                                                            |  |  |  |  |

# TABLE 17-1:CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS<br/>AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| OSC | PIC17C42-16                              | PIC17C42-25                              |

|-----|------------------------------------------|------------------------------------------|

| RC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 6 mA max.                           | IDD: 6 mA max.                           |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 4 MHz max.                         | Freq: 4 MHz max.                         |

| XT  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| EC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| LF  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 150 μA max. at 32 kHz (WDT enabled) | IDD: 150 μA max. at 32 kHz (WDT enabled) |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 2 MHz max.                         | Freq: 2 MHz max.                         |

### 17.1 DC CHARACTERISTICS:

### PIC17C42-16 (Commercial, Industrial) PIC17C42-25 (Commercial, Industrial)

| DC CHARA         | CTERIS | STICS                                                            | Standard<br>Operating | -    | -    |       | ns (unless otherwise stated)                        |

|------------------|--------|------------------------------------------------------------------|-----------------------|------|------|-------|-----------------------------------------------------|

|                  |        |                                                                  |                       |      |      | -40°C |                                                     |

|                  |        | 1                                                                | 1                     |      |      | 0°C   | $\leq$ TA $\leq$ +70°C for commercial               |

| Parameter<br>No. | Sym    | Characteristic                                                   | Min                   | Тур† | Max  | Units | Conditions                                          |

| D001             | Vdd    | Supply Voltage                                                   | 4.5                   | _    | 5.5  | V     |                                                     |

| D002             | Vdr    | RAM Data Retention<br>Voltage (Note 1)                           | 1.5 *                 | -    | -    | V     | Device in SLEEP mode                                |

| D003             | VPOR   | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | -                     | Vss  | -    | V     | See section on Power-on Reset for details           |

| D004             | SVDD   | VDD rise rate to<br>ensure internal<br>Power-on Reset signal     | 0.060*                | _    | _    | mV/ms | See section on Power-on Reset for details           |

| D010             | IDD    | Supply Current                                                   | _                     | 3    | 6    | mA    | Fosc = 4 MHz (Note 4)                               |

| D011             |        | (Note 2)                                                         | -                     | 6    | 12 * | mA    | Fosc = 8 MHz                                        |

| D012             |        |                                                                  | -                     | 11   | 24 * | mA    | Fosc = 16 MHz                                       |

| D013             |        |                                                                  | -                     | 19   | 38   | mA    | Fosc = 25 MHz                                       |

| D014             |        |                                                                  | -                     | 95   | 150  | μA    | Fosc = 32 kHz<br>WDT enabled (EC osc configuration) |

| D020             | IPD    | Power-down Current                                               | _                     | 10   | 40   | μA    | VDD = 5.5V, WDT enabled                             |

| D021             |        | (Note 3)                                                         | -                     | < 1  | 5    | μA    | VDD = 5.5V, WDT disabled                            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD or VSS, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

Current consumed from the oscillator and I/O's driving external capacitive or resistive loads need to be considered.

For the RC oscillator, the current through the external pull-up resistor (R) can be estimated as:  $VDD / (2 \cdot R)$ . For capacitive loads, The current can be estimated (for an individual I/O pin) as (CL  $\cdot VDD$ )  $\cdot f$

CL = Total capacitive load on the I/O pin; f = average frequency on the I/O pin switches.

The capacitive currents are most significant when the device is configured for external execution (includes extended microcontroller mode).

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, all I/O pins in hi-impedance state and tied to VDD or Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IR = VDD/2Rext (mA) with Rext in kOhm.

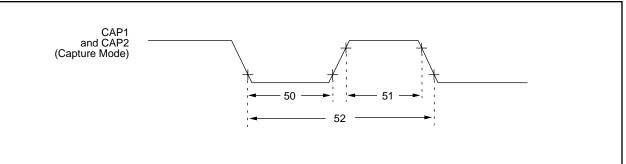

#### FIGURE 17-7: CAPTURE TIMINGS

#### TABLE 17-7: CAPTURE REQUIREMENTS

| Parameter |      |                                       |                     |      |     |       |                                 |

|-----------|------|---------------------------------------|---------------------|------|-----|-------|---------------------------------|

| No.       | Sym  | Characteristic                        | Min                 | Тур† | Max | Units | Conditions                      |

| 50        | TccL | Capture1 and Capture2 input low time  | 10 *                | —    | —   | ns    |                                 |

| 51        | TccH | Capture1 and Capture2 input high time | 10 *                | —    | _   | ns    |                                 |

| 52        | TccP | Capture1 and Capture2 input period    | <u>2 Tcy</u> §<br>N | —    | —   | ns    | N = prescale value<br>(4 or 16) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

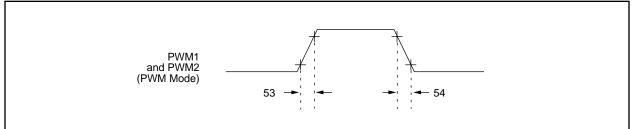

#### FIGURE 17-8: PWM TIMINGS

#### TABLE 17-8: PWM REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                 | Min | Тур† | Max   | Units | Conditions |

|------------------|------|--------------------------------|-----|------|-------|-------|------------|

| 53               | TccR | PWM1 and PWM2 output rise time |     | 10 * | 35 *§ | ns    |            |

| 54               | TccF | PWM1 and PWM2 output fall time | —   | 10 * | 35 *§ | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

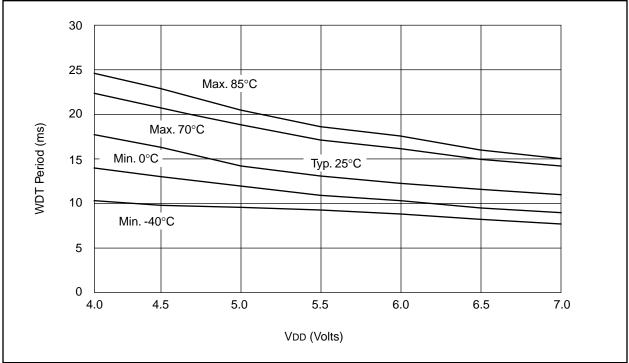

### FIGURE 18-13: WDT TIMER TIME-OUT PERIOD vs. VDD

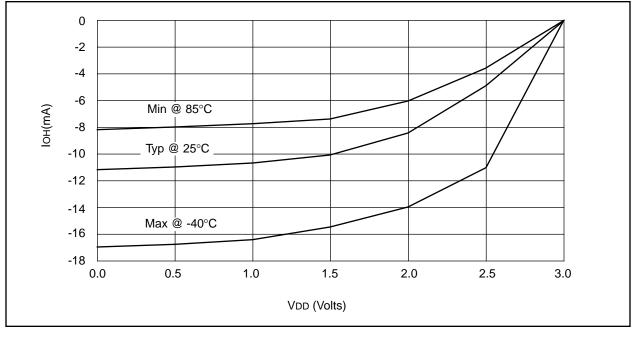

FIGURE 18-14: IOH vs. VOH, VDD = 3V

#### 19.2 **DC CHARACTERISTICS:**

#### PIC17LC42A/43/LC44 (Commercial, Industrial) PIC17LCR42/43 (Commercial, Industrial)

| DC CHARACTERISTICSOperating temperature $-40^{\circ}C$ $\leq TA \leq +8$ $0^{\circ}C$ $\leq TA \leq +7$ |      |                                                                  |         |      |      |       | s (unless otherwise stated)<br>$\leq TA \leq +85^{\circ}C$ for industrial and<br>$\leq TA \leq +70^{\circ}C$ for commercial |

|---------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------|---------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------|

| Parameter<br>No.                                                                                        | Sym  | Characteristic                                                   | Min     | Тур† | Мах  | Units | Conditions                                                                                                                  |

| D001                                                                                                    | Vdd  | Supply Voltage                                                   | 2.5     | _    | 6.0  | V     |                                                                                                                             |

| D002                                                                                                    | Vdr  | RAM Data Retention<br>Voltage (Note 1)                           | 1.5 *   | -    | Ι    | V     | Device in SLEEP mode                                                                                                        |

| D003                                                                                                    | VPOR | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | _       | Vss  | _    | V     | See section on Power-on Reset for details                                                                                   |

| D004                                                                                                    | SVDD | VDD rise rate to<br>ensure internal<br>Power-on Reset signal     | 0.060 * | _    | Ι    | mV/ms | See section on Power-on Reset for details                                                                                   |

| D010                                                                                                    | IDD  | Supply Current                                                   | -       | 3    | 6    | mA    | Fosc = 4 MHz (Note 4)                                                                                                       |

| D011                                                                                                    |      | (Note 2)                                                         | -       | 6    | 12 * | mA    | Fosc = 8 MHz                                                                                                                |

| D014                                                                                                    |      |                                                                  | -       | 95   | 150  | μA    | Fosc = 32 kHz,                                                                                                              |

|                                                                                                         |      |                                                                  |         |      |      |       | WDT disabled (EC osc configuration)                                                                                         |

| D020                                                                                                    | IPD  | Power-down                                                       | -       | 10   | 40   | μA    | VDD = 5.5V, WDT enabled                                                                                                     |

| D021                                                                                                    |      | Current (Note 3)                                                 | -       | < 1  | 5    | μA    | VDD = 5.5V, WDT disabled                                                                                                    |

These parameters are characterized but not tested.

+ Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1=external square wave, from rail to rail; all I/O pins tristated, pulled to VDD or VSS, TOCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

Current consumed from the oscillator and I/O's driving external capacitive or resistive loads needs to be considered.

For the RC oscillator, the current through the external pull-up resistor (R) can be estimated as: VbD / (2 • R). For capacitive loads, the current can be estimated (for an individual I/O pin) as (CL • VDD) • f

CL = Total capacitive load on the I/O pin; f = average frequency the I/O pin switches.

The capacitive currents are most significant when the device is configured for external execution (includes extended microcontroller mode).

- 3: The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IR = VDD/2Rext (mA) with Rext in kOhm.

Standard Operating Conditions (unloss otherwise stated)

## Applicable Devices 42 R42 42A 43 R43 44

|           |       |                                                  | Standard C<br>Operating te |           |              | ns (ur | nless otherwise stated)                                                                                     |

|-----------|-------|--------------------------------------------------|----------------------------|-----------|--------------|--------|-------------------------------------------------------------------------------------------------------------|

| DC CHARA  | CTERI | STICS                                            |                            | ·         | -40°C<br>0°C |        | ≤ +85°C for industrial and<br>≤ +70°C for commercial                                                        |

|           |       |                                                  | Operating v                | oltage Vi | DD range a   | s desc | ribed in Section 19.1                                                                                       |

| Parameter |       |                                                  |                            |           |              |        |                                                                                                             |

| No.       | Sym   | Characteristic                                   | Min                        | Тур†      | Max          | Units  | Conditions                                                                                                  |

|           |       | Output Low Voltage                               |                            |           |              |        |                                                                                                             |

| D080      | VOL   | I/O ports (except RA2 and RA3)                   |                            |           |              |        | IOL = VDD/1.250 mA                                                                                          |

|           |       |                                                  | _                          | _         | 0.1Vdd       | V      | $4.5V \le VDD \le 6.0V$                                                                                     |

|           |       |                                                  | _                          | _         | 0.1Vdd *     | V      | VDD = 2.5V                                                                                                  |

| D081      |       | with TTL buffer                                  | -                          | _         | 0.4          | V      | IOL = 6 mA, VDD = 4.5V<br>Note 6                                                                            |

| D082      |       | RA2 and RA3                                      | _                          | _         | 3.0          | V      | IOL = 60.0  mA, VDD = 6.0 V                                                                                 |

| D083      |       | OSC2/CLKOUT                                      | _                          | _         | 0.4          | V      | IOL = 1 mA, VDD = 4.5V                                                                                      |

| D084      |       | (RC and EC osc modes)                            | _                          | _         | 0.1Vdd *     | V      | IOL = VDD/5 mA                                                                                              |

|           |       |                                                  |                            |           |              |        | (PIC17LC43/LC44 only)                                                                                       |

|           |       | Output High Voltage (Note 3)                     |                            |           |              |        |                                                                                                             |