Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore ProcessorPCCore Size8-BitSpeedSoM42ConnectivityUART/USARTPropheralsPOR, PWM, WDTNumber of I/O33Program Memory SizeRKB (4K × 16)Program Memory TypeOTPERROM Size-Nufage Supply (Vcc/Vdd)454 × 8Voltage Supply (Vcc/Vdd)-Operating Type-Operating Type- <t< th=""><th></th><th></th></t<> |                            |                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

| Core Size8-BitSpeed25MHzConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O33Program Memory Size8KB (4K x 16)Program Memory TypeOTPEEPROM Size-AtM Size454 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Operating Temperature-40°C ~ 125°C (TA)Mounting Type40-DIP (0.600°, 15.24mm)Supplier Device Package40-DIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Product Status             | Obsolete                                                                 |

| Speed25MHzSpeed25MHzConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O33Program Memory Size8KB (4K x 16)Program Memory TypeOTPEEPROM Size-RAM Size454 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Operating Temperature-40°C ~ 125°C (TA)Mounting TypeHrough HolePackage / Case40-DIP (0.600°, 15.24mm)Supplier Device Package40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Core Processor             | PIC                                                                      |

| ConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O33Program Memory Size8KB (4K x 16)Program Memory TypeOTPEEPROM Size-RAM Size454 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeThrough HolePackage / Case40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Core Size                  | 8-Bit                                                                    |

| PeripheralsPOR, PWM, WDTNumber of I/O33Program Memory Size8KB (4K x 16)Program Memory TypeOTPEEPROM Size-RAM Size454 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeThrough HolePackage / Case40-DIP (0.600", 15.24mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Speed                      | 25MHz                                                                    |

| Number of I/O33Program Memory Size8KB (4K × 16)Program Memory TypeOTPEEPROM Size-RAM Size454 × 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeThrough HolePackage / Case40-DIP (0.600", 15.24mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Connectivity               | UART/USART                                                               |

| Program Memory Size8KB (4K x 16)Program Memory TypeOTPEEPROM Size-RAM Size454 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting Typethrough HolePackage / Case40-PDIP (0.600", 15.24mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Peripherals                | POR, PWM, WDT                                                            |

| Program Memory TypeOTPEEPROM Size-RAM Size454 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeThrough HolePackage / Case40-DIP (0.600", 15.24mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Number of I/O              | 33                                                                       |

| EEPROM Size-RAM Size454 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeThrough HolePackage / Case40-DIP (0.600", 15.24mm)Supplier Device Package40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Program Memory Size        | 8KB (4K x 16)                                                            |

| RAM Size454 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeThrough HolePackage / Case40-DIP (0.600", 15.24mm)Supplier Device Package40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Program Memory Type        | OTP                                                                      |

| Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeThrough HolePackage / Case40-DIP (0.600", 15.24mm)Supplier Device Package40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EEPROM Size                | -                                                                        |

| Data Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeThrough HolePackage / Case40-DIP (0.600", 15.24mm)Supplier Device Package40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RAM Size                   | 454 x 8                                                                  |

| Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeThrough HolePackage / Case40-DIP (0.600", 15.24mm)Supplier Device Package40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                |

| Operating Temperature-40°C ~ 125°C (TA)Mounting TypeThrough HolePackage / Case40-DIP (0.600", 15.24mm)Supplier Device Package40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Data Converters            | -                                                                        |

| Mounting Type     Through Hole       Package / Case     40-DIP (0.600", 15.24mm)       Supplier Device Package     40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Oscillator Type            | External                                                                 |

| Package / Case     40-DIP (0.600", 15.24mm)       Supplier Device Package     40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Mounting Type              | Through Hole                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Purchase LIRI https://www.a.vfl.com/product.detail/microchip.tochpalagy/pic17c42.25a.p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supplier Device Package    | 40-PDIP                                                                  |

| https://www.e-xii.com/product-detail/inicrochip-technology/pic1/45-25e-p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-25e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 3-1. | PINOUT DESCRIPTIONS |                      |                 |               |                |                                                                                                                                                                             |  |

|------------|---------------------|----------------------|-----------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name       | DIP<br>No.          | PLCC<br>No.          | QFP<br>No.      | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                 |  |

|            |                     |                      |                 |               |                | PORTD is a bi-directional I/O Port.                                                                                                                                         |  |

| RD0/AD8    | 40                  | 43                   | 15              | I/O           | TTL            | This is also the upper byte of the 16-bit system bus in                                                                                                                     |  |

| RD1/AD9    | 39                  | 42                   | 14              | I/O           | TTL            | microprocessor mode or extended microprocessor mode                                                                                                                         |  |

| RD2/AD10   | 38                  | 41                   | 13              | I/O           | TTL            | or extended microcontroller mode. In multiplexed system                                                                                                                     |  |

| RD3/AD11   | 37                  | 40                   | 12              | I/O           | TTL            | bus configuration these pins are address output as well as data input or output.                                                                                            |  |

| RD4/AD12   | 36                  | 39                   | 11              | I/O           | TTL            |                                                                                                                                                                             |  |

| RD5/AD13   | 35                  | 38                   | 10              | I/O           | TTL            |                                                                                                                                                                             |  |

| RD6/AD14   | 34                  | 37                   | 9               | I/O           | TTL            |                                                                                                                                                                             |  |

| RD7/AD15   | 33                  | 36                   | 8               | I/O           | TTL            |                                                                                                                                                                             |  |

|            |                     |                      |                 |               |                | PORTE is a bi-directional I/O Port.                                                                                                                                         |  |

| RE0/ALE    | 30                  | 32                   | 4               | I/O           | TTL            | In microprocessor mode or extended microcontroller<br>mode, it is the Address Latch Enable (ALE) output.<br>Address should be latched on the falling edge of ALE<br>output. |  |

| RE1/OE     | 29                  | 31                   | 3               | I/O           | TTL            | In microprocessor or extended microcontroller mode, it is the Output Enable ( $\overline{OE}$ ) control output (active low).                                                |  |

| RE2/WR     | 28                  | 30                   | 2               | I/O           | TTL            | In microprocessor or extended microcontroller mode, it is the Write Enable (WR) control output (active low).                                                                |  |

| TEST       | 27                  | 29                   | 1               | I             | ST             | Test mode selection control input. Always tie to Vss for nor-<br>mal operation.                                                                                             |  |

| Vss        | 10,<br>31           | 11,<br>12,<br>33, 34 | 5, 6,<br>27, 28 | Р             |                | Ground reference for logic and I/O pins.                                                                                                                                    |  |

| Vdd        | 1                   | 1, 44                | 16, 17          | Р             |                | Positive supply for logic and I/O pins.                                                                                                                                     |  |

| TABLE 3-1: | PINOUT DESCRIPTIONS |

|------------|---------------------|

|------------|---------------------|

Legend: I = Input only; O = Output only; I/O = Input/Output; P = Power; — = Not Used; TTL = TTL input; ST = Schmitt Trigger input.

## 4.0 RESET

The PIC17CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- WDT Reset (normal operation)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are forced to a "reset state" on Power-on Reset (POR), on  $\overline{\text{MCLR}}$  or WDT Reset and on  $\overline{\text{MCLR}}$  reset during SLEEP. They are not affected by a WDT Reset during SLEEP, since this reset is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations as indicated in Table 4-3. These bits are used in software to determine the nature of reset. See Table 4-4 for a full description of reset states of all registers.

**Note:** While the device is in a reset state, the internal phase clock is held in the Q1 state. Any processor mode that allows external execution will force the RE0/ALE pin as a low output and the RE1/OE and RE2/WR pins as high outputs.

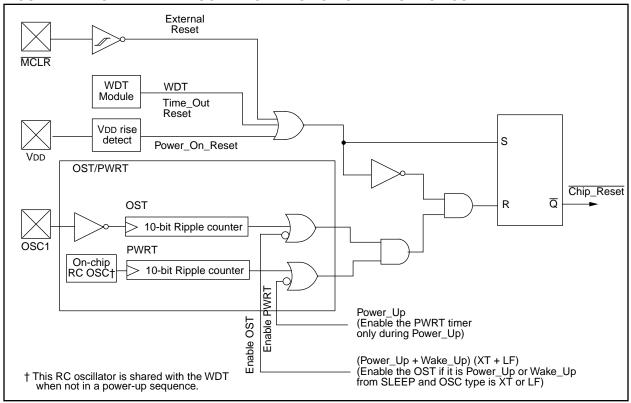

A simplified block diagram of the on-chip reset circuit is shown in Figure 4-1.

### 4.1 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT), and Oscillator Start-up</u> <u>Timer (OST)</u>

### 4.1.1 POWER-ON RESET (POR)

The Power-on Reset circuit holds the device in reset until VDD is above the trip point (in the range of 1.4V -2.3V). The PIC17C42 does not produce an internal reset when VDD declines. All other devices will produce an internal reset for both rising and falling VDD. To take advantage of the POR, just tie the MCLR/VPP pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD is required. See Electrical Specifications for details.

#### 4.1.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 96 ms time-out (nominal) on power-up. This occurs from rising edge of the POR signal and after the first rising edge of  $\overline{\text{MCLR}}$  (detected high). The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. In most cases the PWRT delay allows the VDD to rise to an acceptable level.

The power-up time delay will vary from chip to chip and to VDD and temperature. See DC parameters for details.

## FIGURE 4-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

© 1996 Microchip Technology Inc.

## 5.0 INTERRUPTS

The PIC17C4X devices have 11 sources of interrupt:

- External interrupt from the RA0/INT pin

- Change on RB7:RB0 pins

- TMR0 Overflow

- TMR1 Overflow

- TMR2 Overflow

- TMR3 Overflow

- USART Transmit buffer empty

- USART Receive buffer full

- Capture1

- Capture2

- T0CKI edge occurred

There are four registers used in the control and status of interrupts. These are:

- CPUSTA

- INTSTA

- PIE

- PIR

The CPUSTA register contains the GLINTD bit. This is the Global Interrupt Disable bit. When this bit is set, all interrupts are disabled. This bit is part of the controller core functionality and is described in the Memory Organization section. When an interrupt is responded to, the GLINTD bit is automatically set to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with the interrupt vector address. There are four interrupt vectors. Each vector address is for a specific interrupt source (except the peripheral interrupts which have the same vector address). These sources are:

- External interrupt from the RA0/INT pin

- TMR0 Overflow

- T0CKI edge occurred

- Any peripheral interrupt

When program execution vectors to one of these interrupt vector addresses (except for the peripheral interrupt address), the interrupt flag bit is automatically cleared. Vectoring to the peripheral interrupt vector address does not automatically clear the source of the interrupt. In the peripheral interrupt service routine, the source(s) of the interrupt can be determined by testing the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests.

All of the individual interrupt flag bits will be set regardless of the status of their corresponding mask bit or the GLINTD bit.

For external interrupt events, there will be an interrupt latency. For two cycle instructions, the latency could be one instruction cycle longer.

The "return from interrupt" instruction, RETFIE, can be used to mark the end of the interrupt service routine. When this instruction is executed, the stack is "POPed", and the GLINTD bit is cleared (to re-enable interrupts).

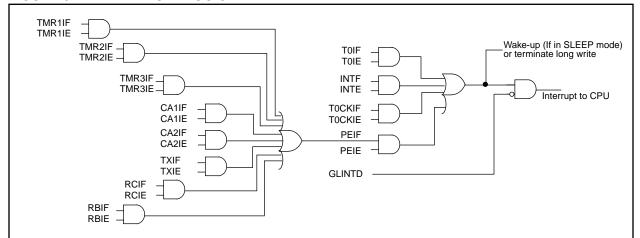

### FIGURE 5-1: INTERRUPT LOGIC

© 1996 Microchip Technology Inc.

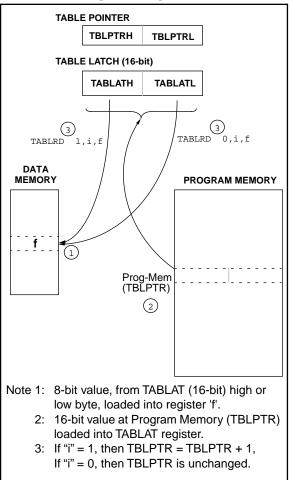

#### FIGURE 7-4: TABLRD INSTRUCTION OPERATION

## TABLE 9-9: PORTE FUNCTIONS

| Name    | Bit  | Buffer Type | Function                                                           |

|---------|------|-------------|--------------------------------------------------------------------|

| RE0/ALE | bit0 | TTL         | Input/Output or system bus Address Latch Enable (ALE) control pin. |

| RE1/OE  | bit1 | TTL         | Input/Output or system bus Output Enable (OE) control pin.         |

| RE2/WR  | bit2 | TTL         | Input/Output or system bus Write (WR) control pin.                 |

Legend: TTL = TTL input.

### TABLE 9-10: REGISTERS/BITS ASSOCIATED WITH PORTE

| Address     | Name  | Bit 7      | Bit 6                            | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|------------|----------------------------------|-------|-------|-------|--------|--------|---------|-------------------------------|-----------------------------------------|

| 15h, Bank 1 | PORTE | —          | —                                | —     | —     | _     | RE2/WR | RE1/OE | RE0/ALE | xxx                           | uuu                                     |

| 14h, Bank 1 | DDRE  | Data dired | ata direction register for PORTE |       |       |       |        |        |         | 111                           | 111                                     |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTE.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

## 11.0 TIMER0

The Timer0 module consists of a 16-bit timer/counter, TMR0. The high byte is TMR0H and the low byte is TMR0L. A software programmable 8-bit prescaler makes an effective 24-bit overflow timer. The clock source is also software programmable as either the internal instruction clock or the RA1/T0CKI pin. The control bits for this module are in register T0STA (Figure 11-1).

| R/W - 0        | R/W - 0                                                              | R/W - 0                                          | R/W - 0                                                            | R/W - 0                    | R/W - 0                  | R/W - 0     | U - 0     |                                                                                                      |

|----------------|----------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------|----------------------------|--------------------------|-------------|-----------|------------------------------------------------------------------------------------------------------|

| INTEDG<br>bit7 | TOSE                                                                 | TOCS                                             | PS3                                                                | PS2                        | PS1                      | PS0         | —<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented,<br>Read as '0'<br>-n = Value at POR reset |

| bit 7:         | <b>INTEDG</b> : R<br>This bit sele<br>1 = Rising e<br>0 = Falling e  | ects the ed<br>edge of RA                        | ge upon w<br>0/INT pin g                                           | hich the in<br>generates i | terrupt is d<br>nterrupt | etected     |           | -n = value al POR lesel                                                                              |

| bit 6:         |                                                                      | ects the ed<br>S = 0<br>edge of RA<br>edge of RA | ge upon w<br>1/T0CKI pi                                            | hich TMR(                  | nts TMR0 a               | and/or gene |           | CKIF interrupt<br>CKIF interrupt                                                                     |

| bit 5:         | <b>TOCS</b> : Time<br>This bit self<br>1 = Internal<br>0 = TOCKI     | ects the clo<br>instruction                      | ck source                                                          | for TMR0.                  |                          |             |           |                                                                                                      |

| bit 4-1:       | <b>PS3:PS0</b> : T<br>These bits                                     |                                                  |                                                                    |                            | R0.                      |             |           |                                                                                                      |

|                | PS3:PS0                                                              | Pre                                              | scale Valu                                                         | е                          |                          |             |           |                                                                                                      |

|                | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1xxx |                                                  | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 |                            |                          |             |           |                                                                                                      |

| bit 0:         | Unimplem                                                             | <b>ented</b> : Rea                               | id as '0'                                                          |                            |                          |             |           |                                                                                                      |

### FIGURE 11-1: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

#### © 1996 Microchip Technology Inc.

## 12.0 TIMER1, TIMER2, TIMER3, PWMS AND CAPTURES

The PIC17C4X has a wealth of timers and time-based functions to ease the implementation of control applications. These time-base functions include two PWM outputs and two Capture inputs.

Timer1 and Timer2 are two 8-bit incrementing timers, each with a period register (PR1 and PR2 respectively) and separate overflow interrupt flags. Timer1 and Timer2 can operate either as timers (increment on internal Fosc/4 clock) or as counters (increment on falling edge of external clock on pin RB4/TCLK12). They are also software configurable to operate as a single 16-bit timer. These timers are also used as the time-base for the PWM (pulse width modulation) module. Timer3 is a 16-bit timer/counter consisting of the TMR3H and TMR3L registers. This timer has four other associated registers. Two registers are used as a 16-bit period register or a 16-bit Capture1 register (PR3H/CA1H:PR3L/CA1L). The other two registers are strictly the Capture2 registers (CA2H:CA2L). Timer3 is the time-base for the two 16-bit captures.

TMR3 can be software configured to increment from the internal system clock or from an external signal on the RB5/TCLK3 pin.

Figure 12-1 and Figure 12-2 are the control registers for the operation of Timer1, Timer2, and Timer3, as well as PWM1, PWM2, Capture1, and Capture2.

## FIGURE 12-1: TCON1 REGISTER (ADDRESS: 16h, BANK 3)

| bit7     | I CA2ED0 CA1ED1 CA1ED0 T16 TMR3CS TMR2CS TMR1CS bit0                                                                                                                                                           | R = Readable bit<br>W = Writable bit<br>-n = Value at POR reset |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| bit 7-6: | <b>CA2ED1:CA2ED0</b> : Capture2 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge |                                                                 |

| bit 5-4: | <b>CA1ED1:CA1ED0</b> : Capture1 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge |                                                                 |

| bit 3:   | <b>T16</b> : Timer1:Timer2 Mode Select bit<br>1 = Timer1 and Timer2 form a 16-bit timer<br>0 = Timer1 and Timer2 are two 8-bit timers                                                                          |                                                                 |

| bit 2:   | <b>TMR3CS</b> : Timer3 Clock Source Select bit<br>1 = TMR3 increments off the falling edge of the RB5/TCLK3 pin<br>0 = TMR3 increments off the internal clock                                                  |                                                                 |

| bit 1:   | <b>TMR2CS</b> : Timer2 Clock Source Select bit<br>1 = TMR2 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR2 increments off the internal clock                                                 |                                                                 |

| bit 0:   | <b>TMR1CS</b> : Timer1 Clock Source Select bit<br>1 = TMR1 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR1 increments off the internal clock                                                 |                                                                 |

### 14.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLK-OUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation and SLEEP mode, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 14.1).

Under normal operation, the WDT must be cleared on a regular interval. This time is less the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

#### 14.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms, (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a postscaler with a division ratio of up to 1:256 can be assigned to the WDT. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

#### 14.3.2 CLEARING THE WDT AND POSTSCALER

The WDT and postscaler are cleared when:

- The device is in the reset state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the reset state.

#### 14.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT postscaler) it may take several seconds before a WDT time-out occurs.

The WDT and postscaler is the Power-up Timer during the Power-on Reset sequence.

#### 14.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the  $\overline{\text{TO}}$  bit is cleared (device is not reset). The CLRWDT instruction can be used to set the  $\overline{\text{TO}}$  bit. This allows the WDT to be a simple overflow timer. When in sleep, the WDT does not increment.

| DCF        | SNZ                                                          | Decreme                                                  | Decrement f, skip if not 0                                                              |                                                    |                                                                         |  |  |  |

|------------|--------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------|--|--|--|

| Synt       | tax:                                                         | [ <i>label</i> ] D                                       | CFSNZ                                                                                   | f,d                                                |                                                                         |  |  |  |

| Ope        | rands:                                                       | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                  | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$                       |                                                    |                                                                         |  |  |  |

| Ope        | ration:                                                      | .,                                                       | (f) $-1 \rightarrow$ (dest);<br>skip if not 0                                           |                                                    |                                                                         |  |  |  |

| Stat       | us Affected:                                                 | None                                                     |                                                                                         |                                                    |                                                                         |  |  |  |

| Enc        | oding:                                                       | 0010                                                     | 011d                                                                                    | ffff                                               | ffff                                                                    |  |  |  |

| Des        | cription:                                                    | WREG. If '<br>back in reg<br>If the resul<br>which is al | 'd' is 0 the<br>d' is 1 the<br>gister 'f'.<br>t is not 0, t<br>ready fetc<br>DP is exec | e result<br>result<br>he nex<br>hed, is<br>uted in | is placed in<br>is placed<br>t instruction,<br>discarded,<br>stead mak- |  |  |  |

| Wor        | ds:                                                          | 1                                                        |                                                                                         |                                                    |                                                                         |  |  |  |

| Cycl       | es:                                                          | 1(2)                                                     |                                                                                         |                                                    |                                                                         |  |  |  |

| QC         | ycle Activity:                                               |                                                          |                                                                                         |                                                    |                                                                         |  |  |  |

|            | Q1                                                           | Q2                                                       | Q3                                                                                      |                                                    | Q4                                                                      |  |  |  |

|            | Decode                                                       | Read<br>register 'f'                                     | Execu                                                                                   | ıte                                                | Write to destination                                                    |  |  |  |

| lf sk      | ip:                                                          |                                                          |                                                                                         |                                                    |                                                                         |  |  |  |

|            | Q1                                                           | Q2                                                       | Q3                                                                                      |                                                    | Q4                                                                      |  |  |  |

|            | Forced NOP                                                   | NOP                                                      | Execu                                                                                   | ute                                                | NOP                                                                     |  |  |  |

| <u>Exa</u> | <u>mple</u> :                                                | HERE<br>ZERO<br>NZERO                                    | DCFSNZ<br>:<br>:                                                                        | TEMP                                               | P, 1                                                                    |  |  |  |

|            | Before Instru<br>TEMP_V                                      |                                                          | ?                                                                                       |                                                    |                                                                         |  |  |  |

|            | After Instruct<br>TEMP_V<br>If TEMP_<br>PC<br>If TEMP_<br>PC | ALUE =<br>VALUE =<br>=                                   | 0;<br>Addre:<br>0;                                                                      | _VALU<br>ss (ze<br>ss (nz                          | RO)                                                                     |  |  |  |

| Syntax:<br>Operand | de.         | [ label ]                                           | 0010                                                                                                                                                                                                               |      |      |  |  |  |

|--------------------|-------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--|--|--|

| Operand            | 18.         | $0 \le k \le 81$                                    | ~                                                                                                                                                                                                                  | i.   |      |  |  |  |

|                    |             |                                                     | •                                                                                                                                                                                                                  |      |      |  |  |  |

| Operatio           | on:         | k → PC<1<br>k<12:8> -<br>PC<15:13                   | → PCLA                                                                                                                                                                                                             |      | ,    |  |  |  |

| Status A           | Affected:   | None                                                |                                                                                                                                                                                                                    |      |      |  |  |  |

| Encodin            | ig:         | 110k                                                | kkkk                                                                                                                                                                                                               | kkkk | kkkl |  |  |  |

| Description:       |             | The thirtee<br>loaded into<br>upper eigh<br>PCLATH. | anywhere within an 8K page boundary<br>The thirteen bit immediate value is<br>loaded into PC bits <12:0>. Then the<br>upper eight bits of PC are loaded into<br>PCLATH. GOTO is always a two-cycle<br>instruction. |      |      |  |  |  |

| Words:             |             | 1                                                   |                                                                                                                                                                                                                    |      |      |  |  |  |

| Cycles:            |             | 2                                                   |                                                                                                                                                                                                                    |      |      |  |  |  |

| Q Cycle            | Activity:   |                                                     |                                                                                                                                                                                                                    |      |      |  |  |  |

|                    | Q1          | Q2                                                  | Q3                                                                                                                                                                                                                 | 5    | Q4   |  |  |  |

| E                  | Decode      | Read literal<br>'k'<7:0>                            | Execu                                                                                                                                                                                                              | ute  | NOP  |  |  |  |

| For                | ced NOP     | NOP                                                 | Execu                                                                                                                                                                                                              | ute  | NOP  |  |  |  |

| Example            | <u>e</u> :  | GOTO THE                                            | RE                                                                                                                                                                                                                 |      |      |  |  |  |

| Afte               | er Instruct | tion                                                |                                                                                                                                                                                                                    |      |      |  |  |  |

|                    | PC =        | Address (TH                                         | HERE )                                                                                                                                                                                                             |      |      |  |  |  |

| INC          | F                               | Inc                 | cremer                                                                                                                                                    | nt f   |      |                       |  |  |

|--------------|---------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-----------------------|--|--|

| Synt         | tax:                            | [ <i>l</i> a        | abel]                                                                                                                                                     | INCF f | ,d   |                       |  |  |

| Ope          | rands:                          |                     | $0 \le f \le 255$<br>$d \in [0,1]$                                                                                                                        |        |      |                       |  |  |

| Ope          | ration:                         | (f)                 | + 1 $\rightarrow$                                                                                                                                         | (dest) |      |                       |  |  |

| Stat         | us Affected:                    | O\                  | /, C, D0                                                                                                                                                  | C, Z   |      |                       |  |  |

| Enco         | oding:                          | (                   | 0001                                                                                                                                                      | 010d   | ffff | ffff                  |  |  |

| Description: |                                 | me<br>WF            | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'. |        |      |                       |  |  |

| Wor          | ds:                             | 1                   |                                                                                                                                                           |        |      |                       |  |  |

| Cycl         | es:                             | 1                   |                                                                                                                                                           |        |      |                       |  |  |

| QC           | ycle Activity:                  |                     |                                                                                                                                                           |        |      |                       |  |  |

|              | Q1                              |                     | Q2                                                                                                                                                        | Q      | 3    | Q4                    |  |  |

|              | Decode                          |                     | tead<br>ister 'f'                                                                                                                                         | Exect  |      | Vrite to<br>stination |  |  |

| <u>Exa</u>   | mple:                           | IN                  | CF                                                                                                                                                        | CNT,   | 1    |                       |  |  |

|              | Before Instru                   | iction              | 1                                                                                                                                                         |        |      |                       |  |  |

|              | CNT                             | =                   | 0xFF                                                                                                                                                      |        |      |                       |  |  |

|              | Z<br>C                          | =                   | 0<br>?                                                                                                                                                    |        |      |                       |  |  |

|              | After Instruct<br>CNT<br>Z<br>C | tion<br>=<br>=<br>= | 0x00<br>1<br>1                                                                                                                                            |        |      |                       |  |  |

| INCFSZ                                               | Incremen                                                                                    | t f, skip if (                                                 | )                                                                                         |

|------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Syntax:                                              | [ label ]                                                                                   | INCFSZ f,                                                      | d                                                                                         |

| Operands:                                            | 0 ≤ f ≤ 255<br>d ∈ [0,1]                                                                    | 5                                                              |                                                                                           |

| Operation:                                           | (f) + 1 $\rightarrow$ (skip if resu                                                         |                                                                |                                                                                           |

| Status Affected:                                     | None                                                                                        |                                                                |                                                                                           |

| Encoding:                                            | 0001                                                                                        | 111d f:                                                        | fff ffff                                                                                  |

| Description:                                         | mented. If 'd<br>WREG. If 'd<br>back in regi<br>If the result<br>which is alr<br>and an NOF | I' is 1 the res<br>ister 'f'.<br>is 0, the nex<br>eady fetched | sult is placed in<br>ult is placed<br>t instruction,<br>, is discarded,<br>instead making |

| Words:                                               | 1                                                                                           |                                                                |                                                                                           |

| Cycles:                                              | 1(2)                                                                                        |                                                                |                                                                                           |

| Q Cycle Activity:                                    |                                                                                             |                                                                |                                                                                           |

| Q1                                                   | Q2                                                                                          | Q3                                                             | Q4                                                                                        |

| Decode                                               | Read<br>register 'f'                                                                        | Execute                                                        | Write to destination                                                                      |

| lf skip:                                             |                                                                                             |                                                                |                                                                                           |

| Q1                                                   | Q2                                                                                          | Q3                                                             | Q4                                                                                        |

| Forced NOP                                           | NOP                                                                                         | Execute                                                        | NOP                                                                                       |

| Example:                                             | NZERO                                                                                       | INCFSZ C<br>:<br>:                                             | 'NT, 1                                                                                    |

| Before Instr                                         |                                                                                             |                                                                |                                                                                           |

| PC                                                   |                                                                                             | S (HERE)                                                       |                                                                                           |

| After Instruc<br>CNT<br>If CNT<br>PC<br>If CNT<br>PC | = CNT + 7<br>= 0;<br>= Address<br>≠ 0;                                                      | 1<br>S(ZERO)<br>S(NZERO)                                       |                                                                                           |

| MOVLR                                                          | Move Literal to high nibble in BSR                                                                                                                                                                                                                                          |  |  |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                        | [ <i>label</i> ] MOVLR k                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Operands:                                                      | $0 \le k \le 15$                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Operation:                                                     | $k \rightarrow (BSR < 7:4>)$                                                                                                                                                                                                                                                |  |  |  |  |  |

| Status Affected:                                               | None                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Encoding:                                                      | 1011 101x kkkk uuuu                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Description:                                                   | The 4-bit literal 'k' is loaded into the<br>most significant 4-bits of the Bank<br>Select Register (BSR). Only the high<br>4-bits of the Bank Select Register<br>are affected. The lower half of the<br>BSR is unchanged. The assembler<br>will encode the "u" fields as 0. |  |  |  |  |  |

| Words:                                                         | 1                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Cycles:                                                        | 1                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Q Cycle Activity:                                              |                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Q1                                                             | Q2 Q3 Q4                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Decode                                                         | Read literal     Execute     Write       'k:u'     literal 'k' to     BSR<7:4>                                                                                                                                                                                              |  |  |  |  |  |

| Example:                                                       | MOVLR 5                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Before Instruction<br>BSR register = 0x22<br>After Instruction |                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| BSR regis                                                      |                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                                                | nstruction is not available in the C42 device.                                                                                                                                                                                                                              |  |  |  |  |  |

| MOVLW                 | Move Literal to WREG                           |  |  |  |  |  |

|-----------------------|------------------------------------------------|--|--|--|--|--|

| Syntax:               | [ <i>label</i> ] MOVLW k                       |  |  |  |  |  |

| Operands:             | $0 \le k \le 255$                              |  |  |  |  |  |

| Operation:            | $k \rightarrow (WREG)$                         |  |  |  |  |  |

| Status Affected:      | None                                           |  |  |  |  |  |

| Encoding:             | 1011 0000 kkkk kkkk                            |  |  |  |  |  |

| Description:          | The eight bit literal 'k' is loaded into WREG. |  |  |  |  |  |

| Words:                | 1                                              |  |  |  |  |  |

| Cycles:               | 1                                              |  |  |  |  |  |

| Q Cycle Activity:     |                                                |  |  |  |  |  |

| Q1                    | Q2 Q3 Q4                                       |  |  |  |  |  |

| Decode                | Read Execute Write to<br>literal 'k' WREG      |  |  |  |  |  |

| Example:              | MOVLW 0x5A                                     |  |  |  |  |  |

| After Instruc<br>WREG |                                                |  |  |  |  |  |

© 1996 Microchip Technology Inc.

## Applicable Devices 42 R42 42A 43 R43 44

| DC CHARA         | CTERI       | STICS                                                             | Operating to  | emperatu  | ire<br>-40°C  | C ≤ TA   | nless otherwise stated)<br>≤ +40°C<br>cribed in Section 17.1 |

|------------------|-------------|-------------------------------------------------------------------|---------------|-----------|---------------|----------|--------------------------------------------------------------|

| Parameter<br>No. | Sym         | Characteristic                                                    | Min           | Typ†      | Max           | Units    |                                                              |

|                  |             | Internal Program Memory<br>Programming Specs (Note 4)             |               |           |               |          |                                                              |

| D110<br>D111     | Vpp<br>Vddp | Voltage on MCLR/VPP pin<br>Supply voltage during<br>programming   | 12.75<br>4.75 | _<br>5.0  | 13.25<br>5.25 | V<br>V   | Note 5                                                       |

| D112<br>D113     | Ipp<br>Iddp | Current into MCLR/VPP pin<br>Supply current during<br>programming |               | 25 ‡<br>_ | 50 ‡<br>30 ‡  | mA<br>mA |                                                              |

| D114             |             | Programming pulse width                                           | 10            | 100       | 1000          | μs       | Terminated via internal/exter-<br>nal interrupt or a reset   |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

**Note:** When using the Table Write for internal programming, the device temperature must be less than 40°C.

## Applicable Devices 42 R42 42A 43 R43 44

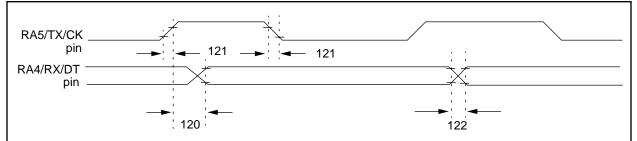

### FIGURE 17-9: USART MODULE: SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 17-9: SERIAL PORT SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                             | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|------------------------------------------------------------|-----|------|-----|-------|------------|

| 120              | TckH2dtV | SYNC XMIT (MASTER & SLAVE)<br>Clock high to data out valid | _   | _    | 65  | ns    |            |

| 121              | TckRF    | Clock out rise time and fall time (Master Mode)            | _   | 10   | 35  | ns    |            |

| 122              | TdtRF    | Data out rise time and fall time                           |     | 10   | 35  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

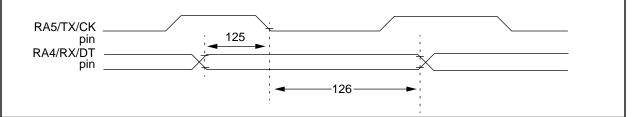

#### FIGURE 17-10: USART MODULE: SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 17-10: SERIAL PORT SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data hold before CK↓ (DT hold time) | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                   | 15  | —    |     | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## Applicable Devices 42 R42 42A 43 R43 44

## Applicable Devices 42 R42 42A 43 R43 44

## Applicable Devices 42 R42 42A 43 R43 44

## E.2 PIC16C5X Family of Devices