Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                |                                                                           |

| RAM Size                   | 454 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-25i-pq |

### **Table of Contents**

| 1.0 Overview                                                                |         |

|-----------------------------------------------------------------------------|---------|

| 2.0 PIC17C4X Device Varieties                                               |         |

| 3.0 Architectural Overview                                                  | <u></u> |

| 4.0 Reset                                                                   | 15      |

| 5.0 Interrupts                                                              | 21      |

| 6.0 Memory Organization                                                     | 29      |

| 7.0 Table Reads and Table Writes                                            | 43      |

| 8.0 Hardware Multiplier                                                     | 49      |

| 9.0 I/O Ports                                                               |         |

| 10.0 Overview of Timer Resources                                            | 65      |

| 11.0 Timer0                                                                 | 67      |

| 12.0 Timer1, Timer2, Timer3, PWMs and Captures                              |         |

| 13.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) Module |         |

| 14.0 Special Features of the CPU                                            |         |

| 15.0 Instruction Set Summary                                                | 107     |

| 16.0 Development Support                                                    | 143     |

| 17.0 PIC17C42 Electrical Characteristics                                    |         |

| 18.0 PIC17C42 DC and AC Characteristics                                     |         |

| 19.0 PIC17CR42/42A/43/R43/44 Electrical Characteristics                     |         |

| 20.0 PIC17CR42/42A/43/R43/44 DC and AC Characteristics                      |         |

| 21.0 Packaging Information                                                  |         |

| Appendix A: Modifications                                                   |         |

| Appendix B: Compatibility                                                   |         |

| Appendix C: What's New                                                      |         |

| Appendix D: What's Changed                                                  |         |

| Appendix E: PIC16/17 Microcontrollers                                       |         |

| Appendix F: Errata for PIC17C42 Silicon                                     |         |

| Index                                                                       |         |

| PIC17C4X Product Identification System                                      | 237     |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. For example, the legend below shows that some features of only the PIC17C43, PIC17C44 are described in this section.

Applicable Devices

42 R42 42A 43 R43 44

### To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error from the previous version of the PIC17C4X Data Sheet (Literature Number DS30412B), please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

To assist you in the use of this document, Appendix C contains a list of new information in this data sheet, while Appendix D contains information that has changed

### 1.0 OVERVIEW

This data sheet covers the PIC17C4X group of the PIC17CXX family of microcontrollers. The following devices are discussed in this data sheet:

- PIC17C42

- PIC17CR42

- PIC17C42A

- PIC17C43

- PIC17CR43

- PIC17C44

The PIC17CR42, PIC17C42A, PIC17C43, PIC17CR43, and PIC17C44 devices include architectural enhancements over the PIC17C42. These enhancements will be discussed throughout this data sheet.

The PIC17C4X devices are 40/44-Pin, EPROM/ROM-based members of the versatile PIC17CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC17CXX has enhanced core features, 16-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 16-bit wide instruction word with a separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 55 instructions (reduced instruction set) are available in the PIC17C42 and 58 instructions in all the other devices. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance. For mathematical intensive applications all devices, except the PIC17C42, have a single cycle 8 x 8 Hardware Multiplier.

PIC17CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC17C4X devices have up to 454 bytes of RAM and 33 I/O pins. In addition, the PIC17C4X adds several peripheral features useful in many high performance applications including:

- · Four timer/counters

- · Two capture inputs

- Two PWM outputs

- A Universal Synchronous Asynchronous Receiver Transmitter (USART)

These special features reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LF oscillator is for low frequency crystals and minimizes power consumption, XT is a standard crystal, and the EC is for external clock input. The SLEEP (power-down) mode offers additional

power saving. The user can wake-up the chip from SLEEP through several external and internal interrupts and device resets.

There are four configuration options for the device operational modes:

- Microprocessor

- Microcontroller

- · Extended microcontroller

- Protected microcontroller

The microprocessor and extended microcontroller modes allow up to 64K-words of external program memory.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software malfunction.

Table 1-1 lists the features of the PIC17C4X devices.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

The PIC17C4X fits perfectly in applications ranging from precise motor control and industrial process control to automotive, instrumentation, and telecom applications. Other applications that require extremely fast execution of complex software programs or the flexibility of programming the software code as one of the last steps of the manufacturing process would also be well suited. The EPROM technology makes customization of application programs (with unique security codes, combinations, model numbers, parameter storage, etc.) fast and convenient. Small footprint package options make the PIC17C4X ideal for applications with space limitations that require high performance. High speed execution, powerful peripheral features, flexible I/O, and low power consumption all at low cost make the PIC17C4X ideal for a wide range of embedded control applications.

### 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X and PIC16CXX families of microcontrollers will see the architectural enhancements that have been implemented. These enhancements allow the device to be more efficient in software and hardware requirements. Please refer to Appendix A for a detailed list of enhancements and modifications. Code written for PIC16C5X or PIC16CXX can be easily ported to PIC17CXX family of devices (Appendix B).

### 1.2 <u>Development Support</u>

The PIC17CXX family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a universal programmer, a "C" compiler, and fuzzy logic support tools.

### 6.2 <u>Data Memory Organization</u>

Data memory is partitioned into two areas. The first is the General Purpose Registers (GPR) area, while the second is the Special Function Registers (SFR) area. The SFRs control the operation of the device.

Portions of data memory are banked, this is for both areas. The GPR area is banked to allow greater than 232 bytes of general purpose RAM. SFRs are for the registers that control the peripheral functions. Banking requires the use of control bits for bank selection. These control bits are located in the Bank Select Register (BSR). If an access is made to a location outside this banked region, the BSR bits are ignored. Figure 6-5 shows the data memory map organization for the PIC17C42 and Figure 6-6 for all of the other PIC17C4X devices.

Instructions MOVPF and MOVFP provide the means to move values from the peripheral area ("P") to any location in the register file ("F"), and vice-versa. The definition of the "P" range is from 0h to 1Fh, while the "F" range is 0h to FFh. The "P" range has six more locations than peripheral registers (eight locations for the PIC17C42 device) which can be used as General Purpose Registers. This can be useful in some applications where variables need to be copied to other locations in the general purpose RAM (such as saving status information during an interrupt).

The entire data memory can be accessed either directly or indirectly through file select registers FSR0 and FSR1 (Section 6.4). Indirect addressing uses the appropriate control bits of the BSR for accesses into the banked areas of data memory. The BSR is explained in greater detail in Section 6.8.

#### 6.2.1 GENERAL PURPOSE REGISTER (GPR)

All devices have some amount of GPR area. The GPRs are 8-bits wide. When the GPR area is greater than 232, it must be banked to allow access to the additional memory space.

Only the PIC17C43 and PIC17C44 devices have banked memory in the GPR area. To facilitate switching between these banks, the MOVLR bank instruction has been added to the instruction set. GPRs are not initialized by a Power-on Reset and are unchanged on all other resets.

#### 6.2.2 SPECIAL FUNCTION REGISTERS (SFR)

The SFRs are used by the CPU and peripheral functions to control the operation of the device (Figure 6-5 and Figure 6-6). These registers are static RAM.

The SFRs can be classified into two sets, those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described here, while those related to a peripheral feature are described in the section for each peripheral feature.

The peripheral registers are in the banked portion of memory, while the core registers are in the unbanked region. To facilitate switching between the peripheral banks, the MOVLB bank instruction has been provided.

Peripheral Data in RBPU (PORTA<7>) Weak Pull-Up Match Signal\_ from other, port pins **RBIF** Port Input Latch Data Bus RD\_DDRB (Q2) RD\_PORTB (Q2) D  $\overline{\mathsf{OE}}$ WR\_DDRB (Q4) **~**\_CK D Port Q Data WR\_PORTB (Q4) PWM\_output PWM\_select Note: I/O pins have protection diodes to VDD and Vss.

FIGURE 9-5: **BLOCK DIAGRAM OF RB3 AND RB2 PORT PINS**

### 13.4 <u>USART Synchronous Slave Mode</u>

The synchronous slave mode differs from the master mode in the fact that the shift clock is supplied externally at the RA5/TX/CK pin (instead of being supplied internally in the master mode). This allows the device to transfer or receive data in the SLEEP mode. The slave mode is entered by clearing the CSRC (TXSTA<7>) bit.

### 13.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the sync master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to TXREG and then the SLEEP instruction executes, the following will occur. The first word will immediately transfer to the TSR and will transmit as the shift clock is supplied. The second word will remain in TXREG. TXIF will not be set. When the first word has been shifted out of TSR, TXREG will transfer the second word to the TSR and the TXIF flag will now be set. If TXIE is enabled, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, then the program will branch to interrupt vector (0020h).

Steps to follow when setting up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting the SYNC and SPEN bits and clearing the CSRC bit.

- 2. Clear the CREN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- If 9-bit transmission is desired, then set the TX9 bit.

- 5. Start transmission by loading data to TXREG.

- If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 7. Enable the transmission by setting TXEN.

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the reverse order.

Note:

To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

### 13.4.2 USART SYNCHRONOUS SLAVE RECEPTION

Operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode. Also, SREN is a don't care in slave mode.

If receive is enabled (CREN) prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR will transfer the data to RCREG (setting RCIF) and if the RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0020h).

Steps to follow when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting the SYNC and SPEN bits and clearing the CSRC bit.

- 2. If interrupts are desired, then set the RCIE bit.

- 3. If 9-bit reception is desired, then set the RX9 bit.

- 4. To enable reception, set the CREN bit.

- The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading RCREG.

- 8. If any error occurred, clear the error by clearing the CREN bit.

Note: To abort reception, either clear the SPEN bit, the SREN bit (when in single receive mode), or the CREN bit (when in continuous receive mode). This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

| CPFSLT                   |                                              | f with WREG                                          | i,                     | DAW                                                          | Decimal Adj                           | ust WREG Register                                                           |

|--------------------------|----------------------------------------------|------------------------------------------------------|------------------------|--------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------|

|                          | skip if f <                                  |                                                      |                        | Syntax:                                                      | [ <i>label</i> ] DAW                  | f,s                                                                         |

| Syntax:                  | [label] (                                    | CPFSLT f                                             |                        | Operands:                                                    | $0 \leq f \leq 255$                   |                                                                             |

| Operands:                | $0 \le f \le 25$                             | 5                                                    |                        |                                                              | s ∈ [0,1]                             |                                                                             |

| Operation:               | (f) – (WREG<br>skip if (f) <<br>(unsigned of |                                                      |                        | Operation:                                                   | •                                     | >>9] .OR. [DC = 1] then<br>0> + 6 $\rightarrow$ f<3:0>, s<3:0>;             |

| Status Affected:         | None                                         | . ,                                                  |                        |                                                              | WREG<3:0                              | $0> \to f<3:0>, s<3:0>;$                                                    |

| Encoding:                | 0011                                         | 0000 fff                                             | f ffff                 |                                                              | If [WREG<7:4>                         | >>9] .OR. [C = 1] then                                                      |

| Description:             | location 'f' t<br>performing                 | the contents of<br>to the contents<br>an unsigned su | of WREG by ubtraction. | Status Affected                                              | else<br>WREG<7:4                      | 4> + 6 → f<7:4>, s<7:4><br>4> → f<7:4>, s<7:4>                              |

|                          |                                              | en the fetched in                                    |                        | Encoding:                                                    | 0010 11                               | lls ffff ffff                                                               |

|                          | discarded a instead mation.                  | and an NOP is eath                                   | executed               | Description:                                                 | WREG resulting tion of two variations | ne eight bit value in<br>ng from the earlier addi-<br>ables (each in packed |

| Words:                   | 1                                            |                                                      |                        |                                                              | packed BCD re                         | nd produces a correct esult.                                                |

| Cycles:                  | 1 (2)                                        |                                                      |                        |                                                              |                                       | t is placed in Data                                                         |

| Q Cycle Activity:        |                                              |                                                      |                        |                                                              | memo<br>WRE                           | ory location 'f' and<br>G.                                                  |

| Q1<br>Decode             | Q2<br>Read                                   | Q3<br>Execute                                        | Q4<br>NOP              |                                                              |                                       | t is placed in Data                                                         |

| Decode                   | register 'f'                                 | Execute                                              | NOP                    |                                                              | memo                                  | ory location 'f'.                                                           |

| If skip:                 |                                              |                                                      |                        | Words:                                                       | 1                                     |                                                                             |

| Q1                       | Q2                                           | Q3                                                   | Q4                     | Cycles:                                                      | 1                                     |                                                                             |

| Forced NOP               | NOP                                          | Execute                                              | NOP                    | Q Cycle Activit                                              | =                                     |                                                                             |

| Example:  Before Instru  | NLESS<br>LESS                                | CPFSLT REG<br>:<br>:                                 |                        | Q1<br>Decode                                                 | Q2<br>Read<br>register 'f'            | Q3 Q4  Execute Write register 'f' and other                                 |

| PC                       |                                              | ddress (HERE)                                        |                        |                                                              |                                       | specified register                                                          |

| W                        | = ?                                          |                                                      |                        | Example1:                                                    | DAW REG1,                             | , ,                                                                         |

| After Instruct<br>If REG |                                              | REG;                                                 |                        | Example i:  Before Ins                                       |                                       | U                                                                           |

| PC<br>If REG<br>PC       | = Ac<br>≥ W                                  | ddress (LESS) REG; ddress (NLESS                     | )                      | WREG<br>REG1<br>C<br>DC                                      | $\Theta = 0xA5$                       |                                                                             |

|                          |                                              |                                                      |                        | After Instr<br>WREG<br>REG1<br>C<br>DC<br><u>Example 2</u> : | $\Theta = 0x05$                       |                                                                             |

|                          |                                              |                                                      |                        | Before Ins<br>WREG<br>REG1<br>C<br>DC                        | G = 0xCE                              |                                                                             |

After Instruction WREG =

REG1

DC

0x24

0x24

0

| RRNCF                         | Rotate Right f (no carry)                                                                                                                                       | SETF                                          | Set f                                                                                                                                |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                       | [ label ] RRNCF f,d                                                                                                                                             | Syntax:                                       | [ label ] SETF f,s                                                                                                                   |

| Operands:                     | $0 \le f \le 255$<br>$d \in [0,1]$                                                                                                                              | Operands:                                     | $0 \le f \le 255$<br>$s \in [0,1]$                                                                                                   |

| Operation:                    | $ f \rightarrow d; $ $ f<0> \rightarrow d<7> $                                                                                                                  | Operation:                                    | $\begin{array}{l} FFh \to f; \\ FFh \to d \end{array}$                                                                               |

| Status Affected:              | None                                                                                                                                                            | Status Affected:                              | None                                                                                                                                 |

| Encoding:                     | 0010 000d ffff ffff                                                                                                                                             | Encoding:                                     | 0010 101s ffff ffff                                                                                                                  |

| Description:                  | The contents of register 'f' are rotated one bit to the right. If 'd' is 0 the result is placed in WREG. If 'd' is 1 the result is placed back in register 'f'. | Description:                                  | If 's' is 0, both the data memory location 'f' and WREG are set to FFh. If 's' is 1 only the data memory location 'f' is set to FFh. |

|                               | register f                                                                                                                                                      | Words:                                        | 1                                                                                                                                    |

| <b>\</b> \\                   |                                                                                                                                                                 | Cycles:                                       | 1                                                                                                                                    |

| Words:                        | 1                                                                                                                                                               | Q Cycle Activity:                             |                                                                                                                                      |

| Cycles:                       | 1                                                                                                                                                               | Q1                                            | Q2 Q3 Q4                                                                                                                             |

| Q Cycle Activity:             | 02 02 04                                                                                                                                                        | Decode                                        | Read Execute Write                                                                                                                   |

| Q1<br>Decode                  | Q2     Q3     Q4       Read register 'f'     Execute write to destination                                                                                       |                                               | register 'f' register 'f' and other specified register                                                                               |

| Example 1:                    | RRNCF REG, 1                                                                                                                                                    |                                               |                                                                                                                                      |

| Before Instru<br>WREG<br>REG  | ction<br>= ?<br>= 1101 0111                                                                                                                                     | Example1:  Before Instru  REG  WREG           | SETF REG, 0  uction = 0xDA = 0x05                                                                                                    |

| After Instruct<br>WREG<br>REG | ion<br>= 0<br>= 1110 1011                                                                                                                                       | After Instruct<br>REG<br>WREG                 |                                                                                                                                      |

| Example 2:                    | RRNCF REG, 0                                                                                                                                                    | Example2:                                     | SETF REG, 1                                                                                                                          |

| Before Instru<br>WREG<br>REG  | ction = ? = 1101 0111                                                                                                                                           | Before Instru<br>REG<br>WREG<br>After Instruc | = 0xDA<br>= 0x05                                                                                                                     |

| After Instruct<br>WREG<br>REG | ion<br>= 1110 1011<br>= 1101 0111                                                                                                                               | REG<br>WREG                                   | = 0xFF<br>= 0x05                                                                                                                     |

**Applicable Devices** | 42 | R42 | 42A | 43 | R43 | 44 |

# TABLE 17-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC17C42-16                              | PIC17C42-25                              |

|-----|------------------------------------------|------------------------------------------|

| RC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 6 mA max.                           | IDD: 6 mA max.                           |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 4 MHz max.                         | Freq: 4 MHz max.                         |

| XT  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| EC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| LF  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 150 μA max. at 32 kHz (WDT enabled) | IDD: 150 μA max. at 32 kHz (WDT enabled) |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 2 MHz max.                         | Freq: 2 MHz max.                         |

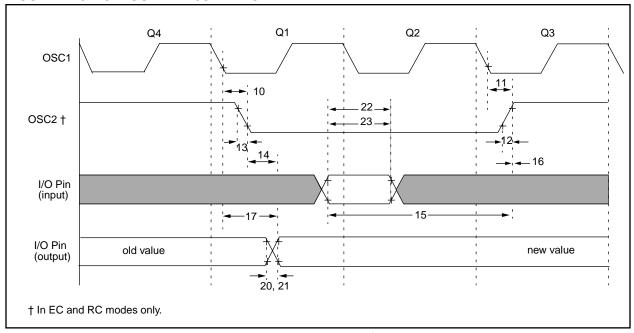

FIGURE 17-3: CLKOUT AND I/O TIMING

TABLE 17-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                      | Min            | Тур† | Max          | Units | Conditions |

|------------------|----------|-------------------------------------|----------------|------|--------------|-------|------------|

| 10               | TosH2ckL | OSC1↑ to CLKOUT↓                    | _              | 15 ‡ | 30 ‡         | ns    | Note 1     |

| 11               | TosH2ckH | OSC1↑ to CLKOUT↑                    | _              | 15‡  | 30 ‡         | ns    | Note 1     |

| 12               | TckR     | CLKOUT rise time                    | _              | 5‡   | 15 ‡         | ns    | Note 1     |

| 13               | TckF     | CLKOUT fall time                    | _              | 5‡   | 15 ‡         | ns    | Note 1     |

| 14               | TckH2ioV | CLKOUT↑ to Port out valid           | _              | _    | 0.5Tcy + 20‡ | ns    | Note 1     |

| 15               | TioV2ckH | Port in valid before CLKOUT↑        | 0.25Tcy + 25 ‡ | _    | _            | ns    | Note 1     |

| 16               | TckH2ioI | Port in hold after CLKOUT↑          | 0 ‡            | _    | _            | ns    | Note 1     |

| 17               | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid  | _              | _    | 100 ‡        | ns    |            |

| 20               | TioR     | Port output rise time               | _              | 10 ‡ | 35 ‡         | ns    |            |

| 21               | TioF     | Port output fall time               | _              | 10 ‡ | 35 ‡         | ns    |            |

| 22               | TinHL    | INT pin high or low time            | 25 *           | _    | _            | ns    |            |

| 23               | TrbHL    | RB7:RB0 change INT high or low time | 25 *           | _    | _            | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>†</sup> These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Measurements are taken in EC Mode where OSC2 output = 4 x Tosc = Tcy.

Applicable Devices 42 R42 42A 43 R43 44

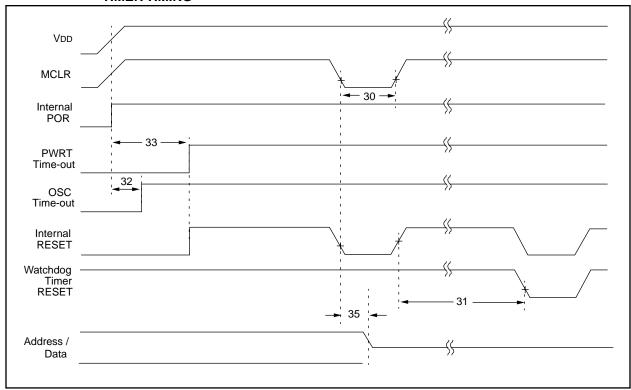

FIGURE 17-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

TABLE 17-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                  | Min   | Тур†        | Max   | Units | Conditions         |

|------------------|----------|-------------------------------------------------|-------|-------------|-------|-------|--------------------|

| 30               | TmcL     | MCLR Pulse Width (low)                          | 100 * | _           | _     | ns    |                    |

| 31               | Twdt     | Watchdog Timer Time-out Period (Prescale = 1)   | 5 *   | 12          | 25 *  | ms    |                    |

| 32               | Tost     | Oscillation Start-up Timer Period               |       | 1024 Tosc § |       | ms    | Tosc = OSC1 period |

| 33               | Tpwrt    | Power-up Timer Period                           | 40 *  | 96          | 200 * | ms    |                    |

| 35               | TmcL2adl | MCLR to System Interface bus (AD15:AD0) invalid | _     | _           | 100 * | ns    |                    |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>‡</sup> These parameters are for design guidance only and are not tested, nor characterized.

<sup>§</sup> This specification ensured by design.

**Applicable Devices** 42 R42 42A 43 R43 44

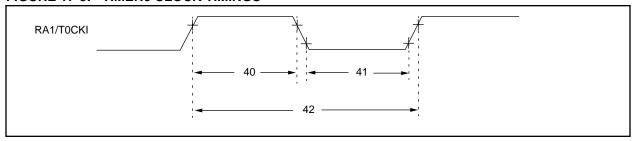

### FIGURE 17-5: TIMERO CLOCK TIMINGS

**TABLE 17-5: TIMERO CLOCK REQUIREMENTS**

| Parameter |      |                        |                |               |      |     |       |                    |

|-----------|------|------------------------|----------------|---------------|------|-----|-------|--------------------|

| No.       | Sym  | Characteristic         |                | Min           | Typ† | Max | Units | Conditions         |

| 40        | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5Tcy + 20 § | _    | _   | ns    |                    |

|           |      |                        | With Prescaler | 10*           |      | _   | ns    |                    |

| 41        | TtOL | T0CKI Low Pulse Width  | No Prescaler   | 0.5Tcy + 20 § | _    | _   | ns    |                    |

|           |      |                        | With Prescaler | 10*           | _    | _   | ns    |                    |

| 42        | Tt0P | T0CKI Period           | •              | Tcy + 40 §    | _    | _   | ns    | N = prescale value |

|           |      |                        |                | N             |      |     |       | (1, 2, 4,, 256)    |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- § This specification ensured by design.

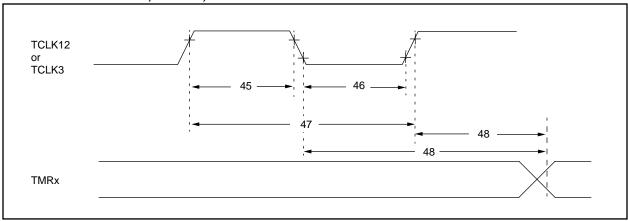

### FIGURE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK TIMINGS

TABLE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK REQUIREMENTS

| Parameter |           |                                                               |                 | Тур |          |       |                                 |

|-----------|-----------|---------------------------------------------------------------|-----------------|-----|----------|-------|---------------------------------|

| No.       | Sym       | Characteristic                                                | Min             | †   | Max      | Units | Conditions                      |

| 45        | Tt123H    | TCLK12 and TCLK3 high time                                    | 0.5 Tcy + 20 §  |     |          | ns    |                                 |

| 46        | Tt123L    | TCLK12 and TCLK3 low time                                     | 0.5 Tcy + 20 §  | _   | _        | ns    |                                 |

| 47        | Tt123P    | TCLK12 and TCLK3 input period                                 | TCY + 40 §<br>N |     | _        |       | N = prescale value (1, 2, 4, 8) |

| 48        | TckE2tmrl | Delay from selected External Clock Edge to<br>Timer increment | 2Tosc §         | _   | 6 Tosc § | _     |                                 |

- These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- § This specification ensured by design.

TABLE 19-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC17LCR42-08<br>PIC17LC42A-08<br>PIC17LC43-08<br>PIC17LCR43-08<br>PIC17LC44-08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PIC17CR42-16<br>PIC17C42A-16<br>PIC17C43-16<br>PIC17CR43-16<br>PIC17CR4-16                                    | PIC17CR42-25<br>PIC17C42A-25<br>PIC17C43-25<br>PIC17CR43-25<br>PIC17C44-25                                    | PIC17CR42-33<br>PIC17C42A-33<br>PIC17C43-33<br>PIC17CR43-33<br>PIC17C44-33 | JW Devices<br>(Ceramic Windowed<br>Devices)                                                                   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 2.5V to 6.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDD: 4.5V to 6.0V                                                                                             | VDD: 4.5V to 6.0V                                                                                             | VDD: 4.5V to 6.0V                                                          | VDD: 4.5V to 6.0V                                                                                             |

|     | IDD: 6 mA max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IDD: 6 mA max.                                                                                                | IDD: 6 mA max.                                                                                                | IDD: 6 mA max.                                                             | IDD: 6 mA max.                                                                                                |

|     | IPD: 5 μA max. at 5.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IPD: 5 μA max. at 5.5V                                                                                        | IPD: 5 μA max. at 5.5V                                                                                        | IPD: 5 μA max. at 5.5V                                                     | IPD: 5 µA max. at 5.5V                                                                                        |

|     | WDT disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | WDT disabled                                                                                                  | WDT disabled                                                                                                  | WDT disabled                                                               | WDT disabled                                                                                                  |

|     | Freq: 4 MHz max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Freq: 4 MHz max.                                                                                              | Freq: 4 MHz max.                                                                                              | Freq: 4 MHz max.                                                           | Freq: 4 MHz max.                                                                                              |

| X   | VDD: 2.5V to 6.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDD: 4.5V to 6.0V                                                                                             | VDD: 4.5V to 6.0V                                                                                             | VDD: 4.5V to 6.0V                                                          | VDD: 4.5V to 6.0V                                                                                             |

|     | IDD: 12 mA max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IDD: 24 mA max.                                                                                               | IDD: 38 mA max.                                                                                               | IDD: 38 mA max.                                                            | IDD: 38 mA max.                                                                                               |

|     | IPD: 5 μA max. at 5.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IPD: 5 μA max. at 5.5V                                                                                        | IPD: 5 μA max. at 5.5V                                                                                        | IPD: 5 μA max. at 5.5V                                                     | IPD: 5 µA max. at 5.5V                                                                                        |

|     | WDT disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | WDT disabled                                                                                                  | WDT disabled                                                                                                  | WDT disabled                                                               | WDT disabled                                                                                                  |

|     | Freq: 8 MHz max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Freq: 16 MHz max.                                                                                             | Freq: 25 MHz max.                                                                                             | Freq: 33 MHz max.                                                          | Freq: 33 MHz max.                                                                                             |

| EC  | EC Vpp: 2.5V to 6.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VDD: 4.5V to 6.0V                                                                                             | VDD: 4.5V to 6.0V                                                                                             | VDD: 4.5V to 6.0V                                                          | VDD: 4.5V to 6.0V                                                                                             |

|     | Ipp: 12 mA max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IDD: 24 mA max.                                                                                               | IDD: 38 mA max.                                                                                               | IDD: 38 mA max.                                                            | IDD: 38 mA max.                                                                                               |

|     | Ipp: 5 μA max. at 5.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IPD: 5 μA max. at 5.5V                                                                                        | IPD: 5 μA max. at 5.5V                                                                                        | IPD: 5 μA max. at 5.5V                                                     | IPD: 5 µA max. at 5.5V                                                                                        |

|     | WDT disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | WDT disabled                                                                                                  | WDT disabled                                                                                                  | WDT disabled                                                               | WDT disabled                                                                                                  |