# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

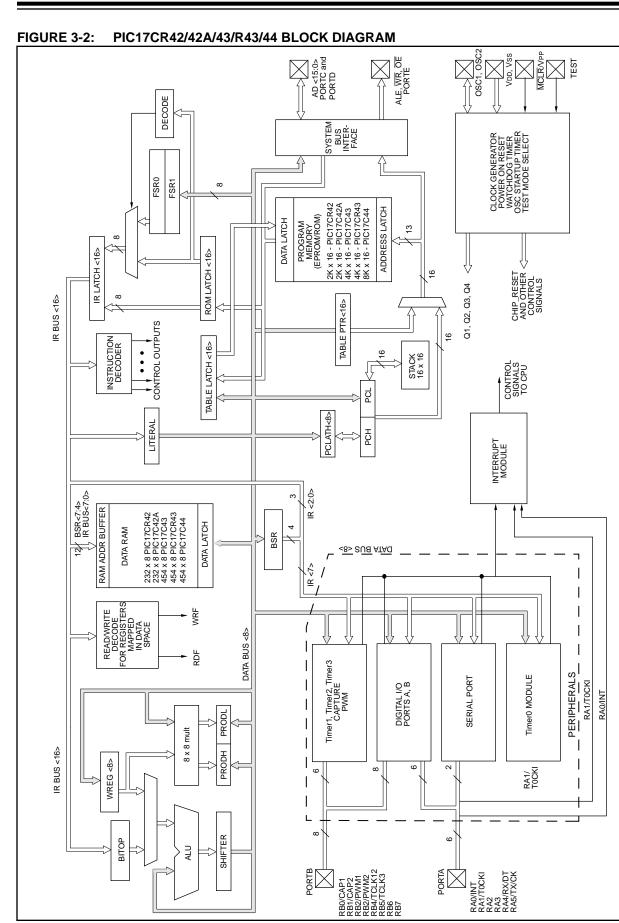

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 33MHz                                                                   |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 8KB (4K x 16)                                                           |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 454 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-33-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 3-1. |            |                      |                 |               |                |                                                                                                                                                                             |

|------------|------------|----------------------|-----------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name       | DIP<br>No. | PLCC<br>No.          | QFP<br>No.      | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                 |

|            |            |                      |                 |               |                | PORTD is a bi-directional I/O Port.                                                                                                                                         |

| RD0/AD8    | 40         | 43                   | 15              | I/O           | TTL            | This is also the upper byte of the 16-bit system bus in                                                                                                                     |

| RD1/AD9    | 39         | 42                   | 14              | I/O           | TTL            | microprocessor mode or extended microprocessor mode                                                                                                                         |

| RD2/AD10   | 38         | 41                   | 13              | I/O           | TTL            | or extended microcontroller mode. In multiplexed system                                                                                                                     |

| RD3/AD11   | 37         | 40                   | 12              | I/O           | TTL            | bus configuration these pins are address output as well as data input or output.                                                                                            |

| RD4/AD12   | 36         | 39                   | 11              | I/O           | TTL            |                                                                                                                                                                             |

| RD5/AD13   | 35         | 38                   | 10              | I/O           | TTL            |                                                                                                                                                                             |

| RD6/AD14   | 34         | 37                   | 9               | I/O           | TTL            |                                                                                                                                                                             |

| RD7/AD15   | 33         | 36                   | 8               | I/O           | TTL            |                                                                                                                                                                             |

|            |            |                      |                 |               |                | PORTE is a bi-directional I/O Port.                                                                                                                                         |

| RE0/ALE    | 30         | 32                   | 4               | I/O           | TTL            | In microprocessor mode or extended microcontroller<br>mode, it is the Address Latch Enable (ALE) output.<br>Address should be latched on the falling edge of ALE<br>output. |

| RE1/OE     | 29         | 31                   | 3               | I/O           | TTL            | In microprocessor or extended microcontroller mode, it is the Output Enable ( $\overline{OE}$ ) control output (active low).                                                |

| RE2/WR     | 28         | 30                   | 2               | I/O           | TTL            | In microprocessor or extended microcontroller mode, it is the Write Enable (WR) control output (active low).                                                                |

| TEST       | 27         | 29                   | 1               | I             | ST             | Test mode selection control input. Always tie to Vss for nor-<br>mal operation.                                                                                             |

| Vss        | 10,<br>31  | 11,<br>12,<br>33, 34 | 5, 6,<br>27, 28 | Р             |                | Ground reference for logic and I/O pins.                                                                                                                                    |

| Vdd        | 1          | 1, 44                | 16, 17          | Р             |                | Positive supply for logic and I/O pins.                                                                                                                                     |

| TABLE 3-1: | PINOUT DESCRIPTIONS |

|------------|---------------------|

|------------|---------------------|

Legend: I = Input only; O = Output only; I/O = Input/Output; P = Power; — = Not Used; TTL = TTL input; ST = Schmitt Trigger input. NOTES:

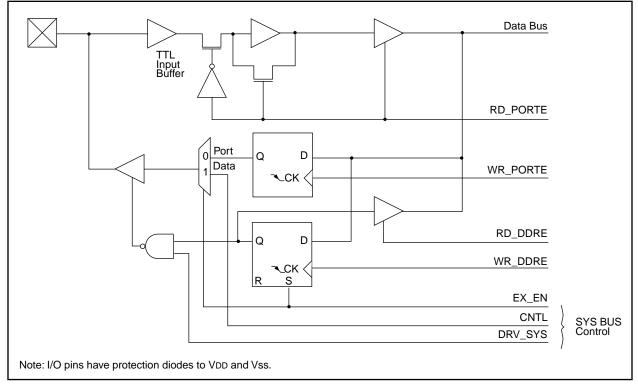

### 9.4.1 PORTE AND DDRE REGISTER

PORTE is a 3-bit bi-directional port. The corresponding data direction register is DDRE. A '1' in DDRE configures the corresponding port pin as an input. A '0' in the DDRE register configures the corresponding port pin as an output. Reading PORTE reads the status of the pins, whereas writing to it will write to the port latch. PORTE is multiplexed with the system bus. When operating as the system bus, PORTE contains the control signals for the address/data bus (AD15:AD0). These control signals are Address Latch Enable (ALE), Output Enable ( $\overline{OE}$ ), and Write ( $\overline{WR}$ ). The control signals  $\overline{OE}$  and  $\overline{WR}$  are active low signals. The timing for the system bus is shown in the Electrical Characteristics section.

Note: This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-4 shows the instruction sequence to initialize PORTE. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

### EXAMPLE 9-4: INITIALIZING PORTE

| MOVLB | 1     | ; | Select Bank 1            |

|-------|-------|---|--------------------------|

| CLRF  | PORTE | ; | Initialize PORTE data    |

|       |       | ; | latches before setting   |

|       |       | ; | the data direction       |

|       |       | ; | register                 |

| MOVLW | 0x03  | ; | Value used to initialize |

|       |       | ; | data direction           |

| MOVWF | DDRE  | ; | Set RE<1:0> as inputs    |

|       |       | ; | RE<2> as outputs         |

|       |       | ; | RE<7:3> are always       |

|       |       | ; | read as '0'              |

### FIGURE 9-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

NOTES:

# 12.0 TIMER1, TIMER2, TIMER3, PWMS AND CAPTURES

The PIC17C4X has a wealth of timers and time-based functions to ease the implementation of control applications. These time-base functions include two PWM outputs and two Capture inputs.

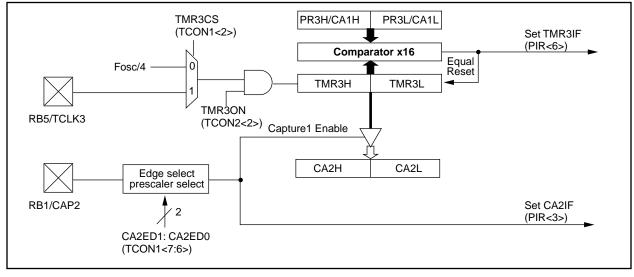

Timer1 and Timer2 are two 8-bit incrementing timers, each with a period register (PR1 and PR2 respectively) and separate overflow interrupt flags. Timer1 and Timer2 can operate either as timers (increment on internal Fosc/4 clock) or as counters (increment on falling edge of external clock on pin RB4/TCLK12). They are also software configurable to operate as a single 16-bit timer. These timers are also used as the time-base for the PWM (pulse width modulation) module. Timer3 is a 16-bit timer/counter consisting of the TMR3H and TMR3L registers. This timer has four other associated registers. Two registers are used as a 16-bit period register or a 16-bit Capture1 register (PR3H/CA1H:PR3L/CA1L). The other two registers are strictly the Capture2 registers (CA2H:CA2L). Timer3 is the time-base for the two 16-bit captures.

TMR3 can be software configured to increment from the internal system clock or from an external signal on the RB5/TCLK3 pin.

Figure 12-1 and Figure 12-2 are the control registers for the operation of Timer1, Timer2, and Timer3, as well as PWM1, PWM2, Capture1, and Capture2.

## FIGURE 12-1: TCON1 REGISTER (ADDRESS: 16h, BANK 3)

| bit7     | I CA2ED0 CA1ED1 CA1ED0 T16 TMR3CS TMR2CS TMR1CS bit0                                                                                                                                                           | R = Readable bit<br>W = Writable bit<br>-n = Value at POR reset |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| bit 7-6: | <b>CA2ED1:CA2ED0</b> : Capture2 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge |                                                                 |

| bit 5-4: | <b>CA1ED1:CA1ED0</b> : Capture1 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge |                                                                 |

| bit 3:   | <b>T16</b> : Timer1:Timer2 Mode Select bit<br>1 = Timer1 and Timer2 form a 16-bit timer<br>0 = Timer1 and Timer2 are two 8-bit timers                                                                          |                                                                 |

| bit 2:   | <b>TMR3CS</b> : Timer3 Clock Source Select bit<br>1 = TMR3 increments off the falling edge of the RB5/TCLK3 pin<br>0 = TMR3 increments off the internal clock                                                  |                                                                 |

| bit 1:   | <b>TMR2CS</b> : Timer2 Clock Source Select bit<br>1 = TMR2 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR2 increments off the internal clock                                                 |                                                                 |

| bit 0:   | <b>TMR1CS</b> : Timer1 Clock Source Select bit<br>1 = TMR1 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR1 increments off the internal clock                                                 |                                                                 |

### 12.2.1 ONE CAPTURE AND ONE PERIOD REGISTER MODE

In this mode registers PR3H/CA1H and PR3L/CA1L constitute a 16-bit period register. A block diagram is shown in Figure 12-7. The timer increments until it equals the period register and then resets to 0000h. TMR3 Interrupt Flag bit (TMR3IF) is set at this point. This interrupt can be disabled by clearing the TMR3 Interrupt Enable bit (TMR3IE). TMR3IF must be cleared in software.

This mode is selected if control bit CA1/PR3 is clear. In this mode, the Capture1 register, consisting of high byte (PR3H/CA1H) and low byte (PR3L/CA1L), is configured as the period control register for TMR3. Capture1 is disabled in this mode, and the corresponding Interrupt bit CA1IF is never set. TMR3 increments until it equals the value in the period register and then resets to 0000h.

Capture2 is active in this mode. The CA2ED1 and CA2ED0 bits determine the event on which capture will occur. The possible events are:

- · Capture on every falling edge

- Capture on every rising edge

- · Capture every 4th rising edge

- · Capture every 16th rising edge

When a capture takes place, an interrupt flag is latched into the CA2IF bit. This interrupt can be enabled by setting the corresponding mask bit CA2IE. The Peripheral Interrupt Enable bit (PEIE) must be set and the Global Interrupt Disable bit (GLINTD) must be cleared for the interrupt to be acknowledged. The CA2IF interrupt flag bit must be cleared in software.

When the capture prescale select is changed, the prescaler is not reset and an event may be generated. Therefore, the first capture after such a change will be ambiguous. However, it sets the time-base for the next capture. The prescaler is reset upon chip reset. Capture pin RB1/CAP2 is a multiplexed pin. When used as a port pin, Capture2 is not disabled. However, the user can simply disable the Capture2 interrupt by clearing CA2IE. If RB1/CAP2 is used as an output pin, the user can activate a capture by writing to the port pin. This may be useful during development phase to emulate a capture interrupt.

The input on capture pin RB1/CAP2 is synchronized internally to internal phase clocks. This imposes certain restrictions on the input waveform (see the Electrical Specification section for timing).

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the Timer3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The recommended sequence to read capture registers and capture overflow flag bits is shown in Example 12-1.

### EXAMPLE 12-1: SEQUENCE TO READ CAPTURE REGISTERS

| MOVLB 3              | ;Select Bank 3          |

|----------------------|-------------------------|

| MOVPF CA2L,LO_BYTE   | ;Read Capture2 low      |

|                      | ;byte, store in LO_BYTE |

| MOVPF CA2H, HI_BYTE  | ;Read Capture2 high     |

|                      | ;byte, store in HI_BYTE |

| MOVPF TCON2,STAT_VAL | ;Read TCON2 into file   |

|                      | ;STAT_VAL               |

### FIGURE 12-7: TIMER3 WITH ONE CAPTURE AND ONE PERIOD REGISTER BLOCK DIAGRAM

| BSF                   | Bit Set f                                                          |                                                                     |      |   |                     |  |  |  |

|-----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|------|---|---------------------|--|--|--|

| Syntax:               | [ <i>label</i> ] E                                                 | [ <i>label</i> ] BSF f,b                                            |      |   |                     |  |  |  |

| Operands:             | $\begin{array}{l} 0 \leq f \leq 25 \\ 0 \leq b \leq 7 \end{array}$ | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \end{array}$ |      |   |                     |  |  |  |

| Operation:            | Dperation: $1 \rightarrow (f < b >)$                               |                                                                     |      |   |                     |  |  |  |

| Status Affected: None |                                                                    |                                                                     |      |   |                     |  |  |  |

| Encoding:             | 1000                                                               | 0bbb                                                                | fff  | f | ffff                |  |  |  |

| Description:          | Bit 'b' in register 'f' is set.                                    |                                                                     |      |   |                     |  |  |  |

| Words:                | 1                                                                  |                                                                     |      |   |                     |  |  |  |

| Cycles:               | 1                                                                  | 1                                                                   |      |   |                     |  |  |  |

| Q Cycle Activity:     |                                                                    |                                                                     |      |   |                     |  |  |  |

| Q1                    | Q2                                                                 | Q3                                                                  | 3    |   | Q4                  |  |  |  |

| Decode                | Read<br>register 'f'                                               | Execu                                                               | ute  |   | Write<br>gister 'f' |  |  |  |

| Example:              | BSF                                                                | FLAG_RE                                                             | G, 7 |   |                     |  |  |  |

| After Instruct        | EG= 0x0A                                                           |                                                                     |      |   |                     |  |  |  |

| BTF        | SC                                                    | Bit Test, s                                                                 | Bit Test, skip if Clear                                                                                                                                                                                                                               |        |      |  |  |  |

|------------|-------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--|--|--|

| Synt       | tax:                                                  | [ <i>label</i> ] B                                                          | [label] BTFSC f,b                                                                                                                                                                                                                                     |        |      |  |  |  |

| Ope        | rands:                                                | $0 \le f \le 253$ $0 \le b \le 7$                                           | $0 \le f \le 255$ $0 \le b \le 7$                                                                                                                                                                                                                     |        |      |  |  |  |

| Ope        | ration:                                               | skip if (f <t< td=""><td>o&gt;) = 0</td><td></td><td></td></t<>             | o>) = 0                                                                                                                                                                                                                                               |        |      |  |  |  |

| Stat       | us Affected:                                          | None                                                                        |                                                                                                                                                                                                                                                       |        |      |  |  |  |

| Enc        | oding:                                                | 1001                                                                        | 1bbb                                                                                                                                                                                                                                                  | ffff   | ffff |  |  |  |

| Des        | cription:                                             | instruction<br>If bit 'b' is 0<br>fetched du<br>cution is di<br>cuted inste | If bit 'b' in register 'f' is 0 then the next instruction is skipped.<br>If bit 'b' is 0 then the next instruction fetched during the current instruction execution is discarded, and a NOP is executed instead, making this a two-cycle instruction. |        |      |  |  |  |

| Wor        | ds:                                                   | 1                                                                           | 1                                                                                                                                                                                                                                                     |        |      |  |  |  |

| Cycl       | les:                                                  | 1(2)                                                                        | 1(2)                                                                                                                                                                                                                                                  |        |      |  |  |  |

| QC         | ycle Activity:                                        |                                                                             |                                                                                                                                                                                                                                                       |        |      |  |  |  |

|            | Q1                                                    | Q2                                                                          | Q3                                                                                                                                                                                                                                                    |        | Q4   |  |  |  |

|            | Decode                                                | Read<br>register 'f'                                                        | Execu                                                                                                                                                                                                                                                 | ite    | NOP  |  |  |  |

| lf sk      | ip:                                                   |                                                                             |                                                                                                                                                                                                                                                       |        |      |  |  |  |

|            | Q1                                                    | Q2                                                                          | Q3                                                                                                                                                                                                                                                    |        | Q4   |  |  |  |

|            | Forced NOP                                            | NOP                                                                         | Execu                                                                                                                                                                                                                                                 | ite    | NOP  |  |  |  |

| <u>Exa</u> | mple:                                                 | FALSE                                                                       | BTFSC<br>:                                                                                                                                                                                                                                            | FLAG,1 |      |  |  |  |

|            | Before Instru<br>PC                                   |                                                                             | dress (HE                                                                                                                                                                                                                                             | RE)    |      |  |  |  |

|            | After Instructi<br>If FLAG<7<br>PC<br>If FLAG<7<br>PC | l> = 0;<br>= ac<br>l> = 1;                                                  | ldress (TR                                                                                                                                                                                                                                            |        |      |  |  |  |

| DECF              | Decreme                  | nt f               |                      | DECFSZ          | Decrement f,                                                      | skip if 0  |                 |

|-------------------|--------------------------|--------------------|----------------------|-----------------|-------------------------------------------------------------------|------------|-----------------|

| Syntax:           | [label]                  | DECF f,d           |                      | Syntax:         | [label] DEC                                                       | FSZ f,d    |                 |

| Operands:         | 0 ≤ f ≤ 258<br>d ∈ [0,1] | 5                  |                      | Operands:       | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |            |                 |

| Operation:        | (f) – 1 $\rightarrow$ (  | dest)              |                      | Operation:      | (f) – 1 $\rightarrow$ (dest                                       |            |                 |

| Status Affected:  | OV, C, DC                | ;, Z               |                      |                 | skip if result =                                                  | 0          |                 |

| Encoding:         | 0000                     | 011d ff            | ff ffff              | Status Affected | l: None                                                           |            |                 |

| Description:      | Decrement                | register 'f'. If ' | d' is 0 the          | Encoding:       | 0001 011                                                          | Ld fff     | f ffff          |

|                   |                          | ored in WREG       |                      | Description:    | The contents of mented. If 'd' is                                 | 0 the resu | It is placed in |

| Words:            | 1                        |                    |                      |                 | WREG. If 'd' is 1<br>back in register                             |            | t is placed     |

| Cycles:           | 1                        |                    |                      |                 | If the result is 0,                                               |            | instruction.    |

| Q Cycle Activity: |                          |                    |                      |                 | which is already                                                  | / fetched, | is discarded,   |

| Q1                | Q2                       | Q3                 | Q4                   |                 | and an NOP is e<br>ing it a two-cycle                             |            |                 |

| Decode            | Read<br>register 'f'     | Execute            | Write to destination | Words:          | 1                                                                 |            |                 |

| Example:          | DECF                     | CNT, 1             |                      | Cycles:         | 1(2)                                                              |            |                 |

| Before Instru     |                          | - ,                |                      | Q Cycle Activit | y:                                                                |            |                 |

| CNT               | = 0x01                   |                    |                      | Q1              | Q2                                                                | Q3         | Q4              |

| Z                 | = 0                      |                    |                      | Decode          |                                                                   | xecute     | Write to        |

| After Instruc     | tion                     |                    |                      |                 | register 'f'                                                      |            | destination     |

| CNT               | = 0x00                   |                    |                      | Example:        |                                                                   |            | CNT, 1          |

| Z                 | = 1                      |                    |                      |                 | GC<br>CONTINUE                                                    | OTO        | LOOP            |

|                   |                          |                    |                      | Defers inc      |                                                                   |            |                 |

|                   |                          |                    |                      | Before Ins      | liucion                                                           |            |                 |

| PC             | =   | Address (HERE)     |

|----------------|-----|--------------------|

| After Instruct | ion |                    |

| CNT            | =   | CNT - 1            |

| If CNT         | =   | 0;                 |

| PC             | =   | Address (CONTINUE) |

| If CNT         | ≠   | 0;                 |

| PC             | =   | Address (HERE+1)   |

| MOVPF                                                                                                                                                                                           | Move p to f                                                          |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                                                                                                                         | [ <i>label</i> ] MOVPF p,f                                           |  |  |  |  |  |  |

| Operands:                                                                                                                                                                                       | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq p \leq 31 \end{array}$ |  |  |  |  |  |  |

| Operation:                                                                                                                                                                                      | $(p) \rightarrow (f)$                                                |  |  |  |  |  |  |

| Status Affected: Z                                                                                                                                                                              |                                                                      |  |  |  |  |  |  |

| Encoding:                                                                                                                                                                                       | 010p pppp ffff ffff                                                  |  |  |  |  |  |  |

| Description: Move data from data memory location<br>'p' to data memory location 'f'. Location<br>'f' can be anywhere in the 256 byte data<br>space (00h to FFh) while 'p' can be 00h<br>to 1Fh. |                                                                      |  |  |  |  |  |  |

|                                                                                                                                                                                                 | Either 'p' or 'f' can be WREG (a useful special situation).          |  |  |  |  |  |  |

| MOVPF is particularly useful for transfer-<br>ring a peripheral register (e.g. the timer<br>or an I/O port) to a data memory loca-<br>tion. Both 'f' and 'p' can be indirectly<br>addressed.    |                                                                      |  |  |  |  |  |  |

| Words:                                                                                                                                                                                          | 1                                                                    |  |  |  |  |  |  |

| Cycles:                                                                                                                                                                                         | 1                                                                    |  |  |  |  |  |  |

| Q Cycle Activity:                                                                                                                                                                               |                                                                      |  |  |  |  |  |  |

| Q1                                                                                                                                                                                              | Q2 Q3 Q4                                                             |  |  |  |  |  |  |

| Decode                                                                                                                                                                                          | ReadExecuteWriteregister 'p'register 'f'                             |  |  |  |  |  |  |

| Example:                                                                                                                                                                                        | MOVPF REG1, REG2                                                     |  |  |  |  |  |  |

| Before Instru                                                                                                                                                                                   | iction                                                               |  |  |  |  |  |  |

| REG1<br>REG2                                                                                                                                                                                    | = 0x11<br>= 0x33                                                     |  |  |  |  |  |  |

| After Instruc<br>REG1<br>REG2                                                                                                                                                                   | ion<br>= 0x11<br>= 0x11                                              |  |  |  |  |  |  |

| MO\          | /WF                          | Ν               | Move WREG to f     |                               |     |   |                     |  |  |

|--------------|------------------------------|-----------------|--------------------|-------------------------------|-----|---|---------------------|--|--|

| Synt         | ax:                          | [ /             | label ]            | MOVWF                         | = f |   |                     |  |  |

| Ope          | rands:                       | 0               | ≤ f ≤ 25           | 5                             |     |   |                     |  |  |

| Ope          | ration:                      | (\              | VREG) ·            | $\rightarrow$ (f)             |     |   |                     |  |  |

| State        | us Affected:                 | N               | one                |                               |     |   |                     |  |  |

| Enco         | oding:                       |                 | 0000               | 0001                          | fff | f | ffff                |  |  |

| Description: |                              | Lo              |                    | from WR<br>can be a<br>space. |     | • |                     |  |  |

| Wor          | ds:                          | 1               |                    |                               |     |   |                     |  |  |

| Cycl         | es:                          | 1               |                    |                               |     |   |                     |  |  |

| QC           | ycle Activity:               |                 |                    |                               |     |   |                     |  |  |

|              | Q1                           |                 | Q2                 | Q3                            | 3   |   | Q4                  |  |  |

|              | Decode                       |                 | Read<br>gister 'f' | Execu                         | ute |   | Write<br>gister 'f' |  |  |

| <u>Exa</u>   | <u>mple</u> :                | M               | OVWF               | REG                           |     |   |                     |  |  |

|              | Before Instru<br>WREG<br>REG | uctio<br>=<br>= | n<br>0x4F<br>0xFF  |                               |     |   |                     |  |  |

|              | After Instruc<br>WREG<br>REG | tion<br>=<br>=  | 0x4F<br>0x4F       |                               |     |   |                     |  |  |

| NEGW         | V                            | Negate W                                                                           | Negate W                                                                                                                                                                                        |  |  |  |  |  |  |

|--------------|------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax       | <b>K</b> :                   | [ <i>label</i> ] NEGW f,s                                                          | ;                                                                                                                                                                                               |  |  |  |  |  |  |

| Opera        | nds:                         | 0 ≤ F ≤ 255<br>s ∈ [0,1]                                                           |                                                                                                                                                                                                 |  |  |  |  |  |  |

| Opera        | tion:                        | $\frac{\overline{WREG}}{\overline{WREG}} + 1 \to (f);$ $\overline{WREG} + 1 \to s$ |                                                                                                                                                                                                 |  |  |  |  |  |  |

| Status       | Affected:                    | OV, C, DC, Z                                                                       |                                                                                                                                                                                                 |  |  |  |  |  |  |

| Encod        | ling:                        | 0010 110s f                                                                        | fff ffff                                                                                                                                                                                        |  |  |  |  |  |  |

| Description: |                              | ment. If 's' is 0 the resul<br>WREG and data memo                                  | WREG is negated using two's comple-<br>ment. If 's' is 0 the result is placed in<br>WREG and data memory location 'f'. If<br>'s' is 1 the result is placed only in data<br>memory location 'f'. |  |  |  |  |  |  |

| Words        | :                            | 1                                                                                  | 1                                                                                                                                                                                               |  |  |  |  |  |  |

| Cycles       | 3:                           | 1                                                                                  |                                                                                                                                                                                                 |  |  |  |  |  |  |

| Q Cyc        | le Activity:                 |                                                                                    |                                                                                                                                                                                                 |  |  |  |  |  |  |

|              | Q1                           | Q2 Q3                                                                              | Q4                                                                                                                                                                                              |  |  |  |  |  |  |

|              | Decode                       | Read Execute<br>register 'f'                                                       | Write<br>register 'f'<br>and other<br>specified<br>register                                                                                                                                     |  |  |  |  |  |  |

| <u>Examp</u> | ole:                         | NEGW REG, 0                                                                        |                                                                                                                                                                                                 |  |  |  |  |  |  |

|              |                              | ction<br>= 0011 1010 [0x3A],<br>= 1010 1011 [0xAB]                                 |                                                                                                                                                                                                 |  |  |  |  |  |  |

| At           | fter Instruct<br>WREG<br>REG | ion<br>= 1100 0111 [0xC6]<br>= 1100 0111 [0xC6]                                    |                                                                                                                                                                                                 |  |  |  |  |  |  |

| NOF               | 2            | No Opera   | No Operation  |     |    |      |  |  |  |

|-------------------|--------------|------------|---------------|-----|----|------|--|--|--|

| Synt              | tax:         | [ label ]  | NOP           |     |    |      |  |  |  |

| Ope               | rands:       | None       |               |     |    |      |  |  |  |

| Ope               | ration:      | No opera   | tion          |     |    |      |  |  |  |

| Stat              | us Affected: | None       | None          |     |    |      |  |  |  |

| Encoding:         |              | 0000       | 0000          | 000 | 0  | 0000 |  |  |  |

| Des               | cription:    | No operati | No operation. |     |    |      |  |  |  |

| Wor               | ds:          | 1          | 1             |     |    |      |  |  |  |

| Cycl              | es:          | 1          |               |     |    |      |  |  |  |

| Q Cycle Activity: |              |            |               |     |    |      |  |  |  |

|                   | Q1           | Q2         | Q3            |     | Q4 |      |  |  |  |

|                   | Decode       | NOP        | Exect         | ute |    | NOP  |  |  |  |

|                   |              |            |               |     |    |      |  |  |  |

Example:

None.

| XORLW             | Exclusive OR Literal with                                                                       | XORWF                          | Exclusive OR WREG with f                                                                                                                                           |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                   | WREG                                                                                            | Syntax:                        | [label] XORWF f,d                                                                                                                                                  |  |  |  |  |

| Syntax:           | [ <i>label</i> ] XORLW k                                                                        | Operands:                      | $0 \le f \le 255$                                                                                                                                                  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                               |                                | d ∈ [0,1]                                                                                                                                                          |  |  |  |  |

| Operation:        | (WREG) .XOR. $k \rightarrow (WREG)$                                                             | Operation:                     | (WREG) .XOR. (f) $\rightarrow$ (dest)                                                                                                                              |  |  |  |  |

| Status Affected:  | Z                                                                                               | Status Affected:               | Z                                                                                                                                                                  |  |  |  |  |

| Encoding:         | 1011 0100 kkkk kkkk                                                                             | Encoding:                      | 0000 110d ffff ffff                                                                                                                                                |  |  |  |  |

| Description:      | The contents of WREG are XOR'ed<br>with the 8-bit literal 'k'. The result is<br>placed in WREG. | Description:                   | Exclusive OR the contents of WREG<br>with register 'f'. If 'd' is 0 the result is<br>stored in WREG. If 'd' is 1 the result is<br>stored back in the register 'f'. |  |  |  |  |

| Words:            | 1                                                                                               | Words:                         | 1                                                                                                                                                                  |  |  |  |  |

| Cycles:           | 1                                                                                               | Cycles:                        | 1                                                                                                                                                                  |  |  |  |  |

| Q Cycle Activity: |                                                                                                 | Q Cycle Activity:              |                                                                                                                                                                    |  |  |  |  |

| Q1                | Q2 Q3 Q4                                                                                        | Q Oycle Activity.<br>Q1        | Q2 Q3 Q4                                                                                                                                                           |  |  |  |  |

| Decode            | ReadExecuteWrite toliteral 'k'WREG                                                              | Decode                         | Read Execute Write to destination                                                                                                                                  |  |  |  |  |

| Example:          | XORLW 0xAF                                                                                      | L                              |                                                                                                                                                                    |  |  |  |  |

| Before Instruc    | ction                                                                                           | Example:                       | XORWF REG, 1                                                                                                                                                       |  |  |  |  |

| After Instructi   | = 0xB5<br>on<br>= 0x1A                                                                          | Before Instru<br>REG<br>WREG   | ction<br>= 0xAF<br>= 0xB5                                                                                                                                          |  |  |  |  |

|                   |                                                                                                 | After Instructi<br>REG<br>WREG | ion<br>= 0x1A<br>= 0xB5                                                                                                                                            |  |  |  |  |

Applicable Devices 42 R42 42A 43 R43 44

# 17.0 PIC17C42 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                              | 55 to +125°C                      |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Storage temperature                                                                                         |                                   |

| Voltage on VDD with respect to Vss                                                                          |                                   |

| Voltage on MCLR with respect to Vss (Note 2)                                                                | 0.6V to +14V                      |

| Voltage on RA2 and RA3 with respect to Vss                                                                  | 0.6V to +12V                      |

| Voltage on all other pins with respect to Vss                                                               |                                   |

| Total power dissipation (Note 1)                                                                            | 1.0W                              |

| Maximum current out of Vss pin(s) - Total                                                                   | 250 mA                            |

| Maximum current into VDD pin(s) - Total                                                                     | 200 mA                            |

| Input clamp current, liк (Vi < 0 or Vi > VDD)                                                               |                                   |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                              | ±20 mA                            |

| Maximum output current sunk by any I/O pin (except RA2 and RA3)                                             | 35 mA                             |

| Maximum output current sunk by RA2 or RA3 pins                                                              | 60 mA                             |

| Maximum output current sourced by any I/O pin                                                               | 20 mA                             |

| Maximum current sunk by PORTA and PORTB (combined)                                                          | 150 mA                            |

| Maximum current sourced by PORTA and PORTB (combined)                                                       | 100 mA                            |

| Maximum current sunk by PORTC, PORTD and PORTE (combined)                                                   | 150 mA                            |

| Maximum current sourced by PORTC, PORTD and PORTE (combined)                                                | 100 mA                            |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-V | OH) X IOH} + $\Sigma$ (VOL X IOL) |

**Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# Applicable Devices 42 R42 42A 43 R43 44

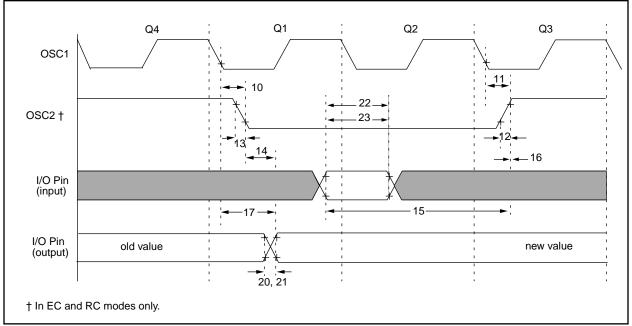

### FIGURE 17-3: CLKOUT AND I/O TIMING

### TABLE 17-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                 | Min            | Тур† | Max          | Units | Conditions |

|------------------|----------|------------------------------------------------|----------------|------|--------------|-------|------------|

| 10               | TosH2ckL | OSC1↑ to CLKOUT↓                               |                | 15 ‡ | 30 ‡         | ns    | Note 1     |

| 11               | TosH2ckH | OSC1↑ to CLKOUT↑                               | —              | 15‡  | 30 ‡         | ns    | Note 1     |

| 12               | TckR     | CLKOUT rise time                               | —              | 5‡   | 15 ‡         | ns    | Note 1     |

| 13               | TckF     | CLKOUT fall time                               | —              | 5‡   | 15 ‡         | ns    | Note 1     |

| 14               | TckH2ioV | CLKOUT <sup>↑</sup> to Port out valid          | —              | —    | 0.5Tcy + 20‡ | ns    | Note 1     |

| 15               | TioV2ckH | Port in valid before CLKOUT                    | 0.25Tcy + 25 ‡ | —    | —            | ns    | Note 1     |

| 16               | TckH2iol | Port in hold after CLKOUT                      | 0 ‡            | —    | —            | ns    | Note 1     |

| 17               | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid | —              | —    | 100 ‡        | ns    |            |

| 20               | TioR     | Port output rise time                          | —              | 10 ‡ | 35 ‡         | ns    |            |

| 21               | TioF     | Port output fall time                          | —              | 10 ‡ | 35 ‡         | ns    |            |

| 22               | TinHL    | INT pin high or low time                       | 25 *           | _    | —            | ns    |            |

| 23               | TrbHL    | RB7:RB0 change INT high or low time            | 25 *           | —    | —            | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Measurements are taken in EC Mode where OSC2 output = 4 x Tosc = Tcy.

### Applicable Devices 42 R42 42A 43 R43 44

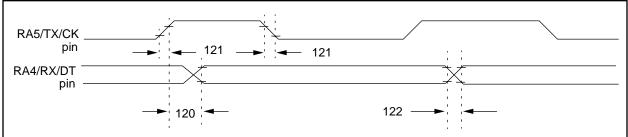

### FIGURE 19-9: USART MODULE: SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### **TABLE 19-9:** SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param | C. m                                                                                                                   | Characteristic                    |                          | Min    | Trent | Max | Unito | Conditions |  |

|-------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|--------|-------|-----|-------|------------|--|

| No.   | Sym                                                                                                                    | Characteristic                    |                          | IVIIII | Тур†  | Max | Units | Conditions |  |

| 120   | TckH2dtV                                                                                                               | SYNC XMIT (MASTER &               |                          |        |       |     |       |            |  |

|       |                                                                                                                        | SLAVE)                            | PIC17CR42/42A/43/R43/44  | —      | —     | 50  | ns    |            |  |

|       |                                                                                                                        | Clock high to data out valid      | PIC17LCR42/42A/43/R43/44 | —      | —     | 75  | ns    |            |  |

| 121   | TckRF                                                                                                                  | Clock out rise time and fall time | PIC17CR42/42A/43/R43/44  | —      | —     | 25  | ns    |            |  |

|       |                                                                                                                        | (Master Mode)                     | PIC17LCR42/42A/43/R43/44 | —      | —     | 40  | ns    |            |  |

| 122   | TdtRF                                                                                                                  | Data out rise time and fall time  | PIC17CR42/42A/43/R43/44  | —      | —     | 25  | ns    |            |  |

|       |                                                                                                                        |                                   | PIC17LCR42/42A/43/R43/44 | —      | —     | 40  | ns    |            |  |

| †     | Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not |                                   |                          |        |       |     |       |            |  |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

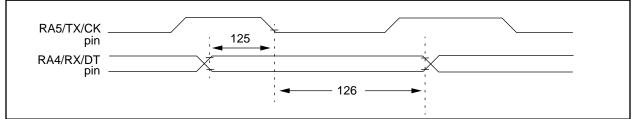

### FIGURE 19-10: USART MODULE: SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### **TABLE 19-10: SYNCHRONOUS RECEIVE REQUIREMENTS**

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data hold before CK↓ (DT hold time) | 15  |      | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                   | 15  | _    | _   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

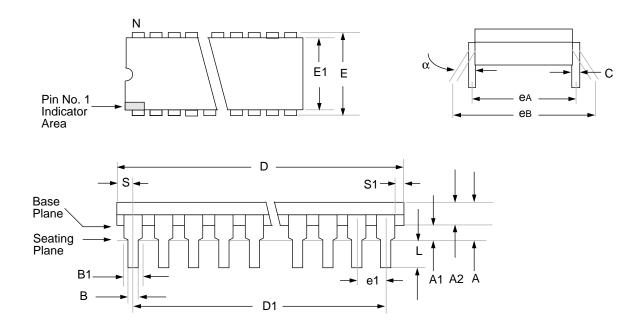

# 21.2 <u>40-Lead Plastic Dual In-line (600 mil)</u>

| Package Group: Plastic Dual In-Line (PLA) |             |        |           |        |       |           |  |  |

|-------------------------------------------|-------------|--------|-----------|--------|-------|-----------|--|--|

|                                           | Millimeters |        |           | Inches |       |           |  |  |

| Symbol                                    | Min         | Мах    | Notes     | Min    | Max   | Notes     |  |  |

| α                                         | 0°          | 10°    |           | 0°     | 10°   |           |  |  |

| Α                                         | _           | 5.080  |           | _      | 0.200 |           |  |  |

| A1                                        | 0.381       | _      |           | 0.015  | _     |           |  |  |

| A2                                        | 3.175       | 4.064  |           | 0.125  | 0.160 |           |  |  |

| В                                         | 0.355       | 0.559  |           | 0.014  | 0.022 |           |  |  |

| B1                                        | 1.270       | 1.778  | Typical   | 0.050  | 0.070 | Typical   |  |  |

| С                                         | 0.203       | 0.381  | Typical   | 0.008  | 0.015 | Typical   |  |  |

| D                                         | 51.181      | 52.197 |           | 2.015  | 2.055 |           |  |  |

| D1                                        | 48.260      | 48.260 | Reference | 1.900  | 1.900 | Reference |  |  |

| E                                         | 15.240      | 15.875 |           | 0.600  | 0.625 |           |  |  |

| E1                                        | 13.462      | 13.970 |           | 0.530  | 0.550 |           |  |  |

| e1                                        | 2.489       | 2.591  | Typical   | 0.098  | 0.102 | Typical   |  |  |

| eA                                        | 15.240      | 15.240 | Reference | 0.600  | 0.600 | Reference |  |  |

| eB                                        | 15.240      | 17.272 |           | 0.600  | 0.680 |           |  |  |

| L                                         | 2.921       | 3.683  |           | 0.115  | 0.145 |           |  |  |

| N                                         | 40          | 40     |           | 40     | 40    |           |  |  |

| S                                         | 1.270       | _      |           | 0.050  | _     |           |  |  |

| S1                                        | 0.508       | -      |           | 0.020  | _     |           |  |  |

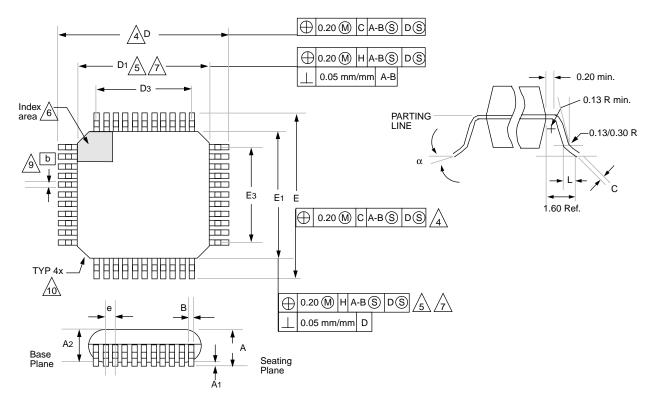

| Package Group: Plastic MQFP |        |             |           |          |            |           |     |       |  |

|-----------------------------|--------|-------------|-----------|----------|------------|-----------|-----|-------|--|

|                             |        | Millimeters |           |          | Inches     |           |     |       |  |

| Symbol                      | Min    | Max Notes   |           | Max Note |            | Min       | Мах | Notes |  |

| α                           | 0°     | <b>7</b> °  |           | 0°       | <b>7</b> ° |           |     |       |  |

| А                           | 2.000  | 2.350       |           | 0.078    | 0.093      |           |     |       |  |

| A1                          | 0.050  | 0.250       |           | 0.002    | 0.010      |           |     |       |  |

| A2                          | 1.950  | 2.100       |           | 0.768    | 0.083      |           |     |       |  |

| b                           | 0.300  | 0.450       | Typical   | 0.011    | 0.018      | Typical   |     |       |  |

| С                           | 0.150  | 0.180       |           | 0.006    | 0.007      |           |     |       |  |

| D                           | 12.950 | 13.450      |           | 0.510    | 0.530      |           |     |       |  |

| D1                          | 9.900  | 10.100      |           | 0.390    | 0.398      |           |     |       |  |

| D3                          | 8.000  | 8.000       | Reference | 0.315    | 0.315      | Reference |     |       |  |

| E                           | 12.950 | 13.450      |           | 0.510    | 0.530      |           |     |       |  |

| E1                          | 9.900  | 10.100      |           | 0.390    | 0.398      |           |     |       |  |

| E3                          | 8.000  | 8.000       | Reference | 0.315    | 0.315      | Reference |     |       |  |

| е                           | 0.800  | 0.800       |           | 0.031    | 0.032      |           |     |       |  |

| L                           | 0.730  | 1.030       |           | 0.028    | 0.041      |           |     |       |  |

| Ν                           | 44     | 44          |           | 44       | 44         |           |     |       |  |

| CP                          | 0.102  | _           |           | 0.004    | _          |           |     |       |  |

PIC16C7X Family of Devices

E.5

| Clock Memory Peripherals Features Features Peripherals Features Features Clock Memory Peripherals Features Feat | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ | ГМR0 — — — 4 4 13 3.0-6.0 Yes — 18-pin DIP, SOIC | TMR0           4         4         13         3.0-6.0         Yes         18-pin DIP, SOIC;           20-pin SSOP         20-pin SSOP         20-pin SSOP         20-pin SSOP         20-pin SSOP | TMR0,         1         SPI/I <sup>2</sup> C         -         5         8         22         2.5-6.0         Yes         28-pin SDIP, SOIC, SSOP           TMR1, TMR2         -         5         8         22         2.5-6.0         Yes         28-pin SDIP, SOIC, SSOP | TMR0, 2 SPI/I <sup>2</sup> C, - 5 11 22 3.0-6.0 Yes - 28-pin SDIP, SOIC<br>TMR1, TMR2 USART | TMR0, 2 SPI/I <sup>2</sup> C, 5 11 22 2.5-6.0 Yes Yes 28-pin SDIP, SOIC<br>TMR1, TMR2 USART | TMR0,         2         SPI/I <sup>2</sup> C,         Yes         8         12         33         3.0-6.0         Yes         40-pin DIP;           TMR1, TMR2         USART         12         33         3.0-6.0         Yes         44-pin PLCC, MQFP | TMR0,         2         SPI/I <sup>2</sup> C,         Yes         8         12         33         2.5-6.0         Yes         40-pin DIP;           TMR1, TMR2         USART         12         33         2.5-6.0         Yes         44-pin PLCC, MQFP, TQFP | All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|