Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 33MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                |                                                                           |

| RAM Size                   | 454 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-33e-pq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 PIC17C4X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC17C4X Product Selection System section at the end of this data sheet. When placing orders, please use the "PIC17C4X Product Identification System" at the back of this data sheet to specify the correct part number.

For the PIC17C4X family of devices, there are four device "types" as indicated in the device number:

- C, as in PIC17C42. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC17LC42. These devices have EPROM type memory, operate over an extended voltage range, and reduced frequency range.

- 3. **CR**, as in PIC17**CR**42. These devices have ROM type memory and operate over the standard voltage range.

- 4. LCR, as in PIC17LCR42. These devices have ROM type memory, operate over an extended voltage range, and reduced frequency range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes. Microchip's PRO MATE<sup>TM</sup> programmer supports programming of the PIC17C4X. Third party programmers also are available; refer to the *Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers expecting frequent code changes and updates.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

ROM devices do not allow serialization information in the program memory space.

For information on submitting ROM code, please contact your regional sales office.

#### 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

For information on submitting ROM code, please contact your regional sales office.

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC17C4X can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC17C4X uses a modified Harvard architecture. This architecture has the program and data accessed from separate memories. So the device has a program memory bus and a data memory bus. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory (accesses over the same bus). Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. PIC17C4X opcodes are 16-bits wide, enabling single word instructions. The full 16-bit wide program memory bus fetches a 16-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions. Consequently, all instructions execute in a single cycle (121 ns @ 33 MHz), except for program branches and two special instructions that transfer data between program and data memory.

The PIC17C4X can address up to 64K x 16 of program memory space.

The **PIC17C42** and **PIC17C42A** integrate 2K x 16 of EPROM program memory on-chip, while the **PIC17CR42** has 2K x 16 of ROM program memory on-chip.

The **PIC17C43** integrates 4K x 16 of EPROM program memory, while the **PIC17CR43** has 4K x 16 of ROM program memory.

The **PIC17C44** integrates 8K x 16 EPROM program memory.

Program execution can be internal only (microcontroller or protected microcontroller mode), external only (microprocessor mode) or both (extended microcontroller mode). Extended microcontroller mode does not allow code protection.

The PIC17CXX can directly or indirectly address its register files or data memory. All special function registers, including the Program Counter (PC) and Working Register (WREG), are mapped in the data memory. The PIC17CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC17CXX simple yet efficient. In addition, the learning curve is reduced significantly.

One of the PIC17CXX family architectural enhancements from the PIC16CXX family allows two file registers to be used in some two operand instructions. This allows data to be moved directly between two registers without going through the WREG register. This increases performance and decreases program memory usage. The PIC17CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift, and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature.

The WREG register is an 8-bit working register used for ALU operations.

All PIC17C4X devices (except the PIC17C42) have an 8 x 8 hardware multiplier. This multiplier generates a 16-bit result in a single cycle.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

Although the ALU does not perform signed arithmetic, the Overflow bit (OV) can be used to implement signed math. Signed arithmetic is comprised of a magnitude and a sign bit. The overflow bit indicates if the magnitude overflows and causes the sign bit to change state. Signed math can have greater than 7-bit values (magnitude), if more than one byte is used. The use of the overflow bit only operates on bit6 (MSb of magnitude) and bit7 (sign bit) of the value in the ALU. That is, the overflow bit is not useful if trying to implement signed math where the magnitude, for example, is 11-bits. If the signed math values are greater than 7-bits (15-, 24or 31-bit), the algorithm must ensure that the low order bytes ignore the overflow status bit.

Care should be taken when adding and subtracting signed numbers to ensure that the correct operation is executed. Example 3-1 shows an item that must be taken into account when doing signed arithmetic on an ALU which operates as an unsigned machine.

#### EXAMPLE 3-1: SIGNED MATH

| Hex Value    | Signed Value<br>Math | Unsigned Value<br>Math      |

|--------------|----------------------|-----------------------------|

| FFh          | -127                 | 255                         |

| <u>+ 01h</u> | <u>+ 1</u>           | <u>+ 1</u>                  |

| = ?          | = -126 (FEh)         | = 0 (00h);<br>Carry bit = 1 |

|              |                      | curry pro - r               |

Signed math requires the result in REG to be FEh (-126). This would be accomplished by subtracting one as opposed to adding one.

Simplified block diagrams are shown in Figure 3-1 and Figure 3-2. The descriptions of the device pins are listed in Table 3-1.

© 1996 Microchip Technology Inc.

#### 4.1.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (1024Tosc) delay after  $\overline{\text{MCLR}}$  is detected high or a wake-up from SLEEP event occurs.

The OST time-out is invoked only for XT and LF oscillator modes on a Power-on Reset or a Wake-up from SLEEP.

The OST counts the oscillator pulses on the OSC1/CLKIN pin. The counter only starts incrementing after the amplitude of the signal reaches the oscillator input thresholds. This delay allows the crystal oscillator or resonator to stabilize before the device exits reset. The length of time-out is a function of the crystal/resonator frequency.

#### 4.1.4 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First the internal POR signal goes high when the POR trip point is reached. If MCLR is high, then both the OST and PWRT timers start. In general the PWRT time-out is longer, except with low frequency crystals/resonators. The total time-out also varies based on oscillator configuration. Table 4-1 shows the times that are associated with the oscillator configuration. Figure 4-2 and Figure 4-3 display these time-out sequences.

If the device voltage is not within electrical specification at the end of a time-out, the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be held low until the voltage is within the device specification. The use of an external RC delay is sufficient for many of these applications.

# TABLE 4-1:TIME-OUT IN VARIOUSSITUATIONS

| Oscillator<br>Configuration | Power-up                            | Wake up<br>from<br>SLEEP | MCLR<br>Reset |

|-----------------------------|-------------------------------------|--------------------------|---------------|

| XT, LF                      | Greater of:<br>96 ms or<br>1024Tosc | 1024Tosc                 | —             |

| EC, RC                      | Greater of:<br>96 ms or<br>1024Tosc |                          | —             |

The time-out sequence begins from the first rising edge of  $\overline{\text{MCLR}}$ .

Table 4-3 shows the reset conditions for some special registers, while Table 4-4 shows the initialization conditions for all the registers. The shaded registers (in Table 4-4) are for all devices except the PIC17C42. In the PIC17C42, the PRODH and PRODL registers are general purpose RAM.

# TABLE 4-2:STATUS BITS AND THEIR<br/>SIGNIFICANCE

| TO | PD | Event                                                                              |

|----|----|------------------------------------------------------------------------------------|

| 1  | 1  | Power-on Reset, MCLR Reset during normal operation, or CLRWDT instruction executed |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP                            |

| 0  | 1  | WDT Reset during normal operation                                                  |

| 0  | 0  | WDT Reset during SLEEP                                                             |

In Figure 4-2, Figure 4-3 and Figure 4-4, TPWRT > TOST, as would be the case in higher frequency crystals. For lower frequency crystals, (i.e., 32 kHz) TOST would be greater.

#### TABLE 4-3: RESET CONDITION FOR THE PROGRAM COUNTER AND THE CPUSTA REGISTER

| Event                             |                                    | PCH:PCL               | CPUSTA                              | OST Active |       |         |

|-----------------------------------|------------------------------------|-----------------------|-------------------------------------|------------|-------|---------|

| Power-on Reset                    | wer-on Reset                       |                       | 11 11                               | Yes        |       |         |

| MCLR Reset during normal ope      | ration                             | 0000h                 | 11 11                               | No         |       |         |

| MCLR Reset during SLEEP           |                                    | 0000h                 | 11 10                               | Yes (2)    |       |         |

| WDT Reset during normal operation | ation                              | 0000h                 | 11 01                               | No         |       |         |

| WDT Reset during SLEEP (3)        |                                    | 0000h                 | 11 00                               | Yes (2)    |       |         |

| Interrupt wake-up from SLEEP      | t wake-up from SLEEP GLINTD is set |                       | pt wake-up from SLEEP GLINTD is set |            | 11 10 | Yes (2) |

|                                   | GLINTD is clear                    | PC + 1 <sup>(1)</sup> | 10 10                               | Yes (2)    |       |         |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0'.

Note 1: On wake-up, this instruction is executed. The instruction at the appropriate interrupt vector is fetched and then executed.

2: The OST is only active when the Oscillator is configured for XT or LF modes.

3: The Program Counter = 0, that is the device branches to the reset vector. This is different from the mid-range devices.

| Register  | Address | Power-on Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEF<br>through interrupt |

|-----------|---------|----------------|-------------------------|-----------------------------------------|

| Bank 2    |         | -              |                         | ·                                       |

| TMR1      | 10h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| TMR2      | 11h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| TMR3L     | 12h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| TMR3H     | 13h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR1       | 14h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR2       | 15h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR3/CA1L  | 16h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| PR3/CA1H  | 17h     | XXXX XXXX      | uuuu uuuu               | սսսս սսսս                               |

| Bank 3    |         |                |                         |                                         |

| PW1DCL    | 10h     | xx             | uu                      | uu                                      |

| PW2DCL    | 11h     | xx             | uu                      | uu                                      |

| PW1DCH    | 12h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| PW2DCH    | 13h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| CA2L      | 14h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| CA2H      | 15h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| TCON1     | 16h     | 0000 0000      | 0000 0000               | uuuu uuuu                               |

| TCON2     | 17h     | 0000 0000      | 0000 0000               | uuuu uuuu                               |

| Unbanked  |         |                |                         |                                         |

| PRODL (5) | 18h     | XXXX XXXX      | นนนน นนนน               | นนนน นนนน                               |

| PRODH (5) | 19h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

#### TABLE 4-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (Cont.'d)

Legend: u = unchanged, x = unknown, - = unimplemented read as '0', q = value depends on condition. Note 1: One or more bits in INTSTA, PIR will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

3: See Table 4-3 for reset value of specific condition.

4: Only applies to the PIC17C42.

5: Does not apply to the PIC17C42.

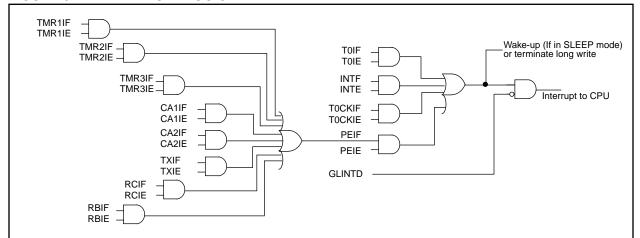

### 5.0 INTERRUPTS

The PIC17C4X devices have 11 sources of interrupt:

- External interrupt from the RA0/INT pin

- Change on RB7:RB0 pins

- TMR0 Overflow

- TMR1 Overflow

- TMR2 Overflow

- TMR3 Overflow

- USART Transmit buffer empty

- USART Receive buffer full

- Capture1

- Capture2

- T0CKI edge occurred

There are four registers used in the control and status of interrupts. These are:

- CPUSTA

- INTSTA

- PIE

- PIR

The CPUSTA register contains the GLINTD bit. This is the Global Interrupt Disable bit. When this bit is set, all interrupts are disabled. This bit is part of the controller core functionality and is described in the Memory Organization section. When an interrupt is responded to, the GLINTD bit is automatically set to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with the interrupt vector address. There are four interrupt vectors. Each vector address is for a specific interrupt source (except the peripheral interrupts which have the same vector address). These sources are:

- External interrupt from the RA0/INT pin

- TMR0 Overflow

- T0CKI edge occurred

- Any peripheral interrupt

When program execution vectors to one of these interrupt vector addresses (except for the peripheral interrupt address), the interrupt flag bit is automatically cleared. Vectoring to the peripheral interrupt vector address does not automatically clear the source of the interrupt. In the peripheral interrupt service routine, the source(s) of the interrupt can be determined by testing the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests.

All of the individual interrupt flag bits will be set regardless of the status of their corresponding mask bit or the GLINTD bit.

For external interrupt events, there will be an interrupt latency. For two cycle instructions, the latency could be one instruction cycle longer.

The "return from interrupt" instruction, RETFIE, can be used to mark the end of the interrupt service routine. When this instruction is executed, the stack is "POPed", and the GLINTD bit is cleared (to re-enable interrupts).

#### FIGURE 5-1: INTERRUPT LOGIC

© 1996 Microchip Technology Inc.

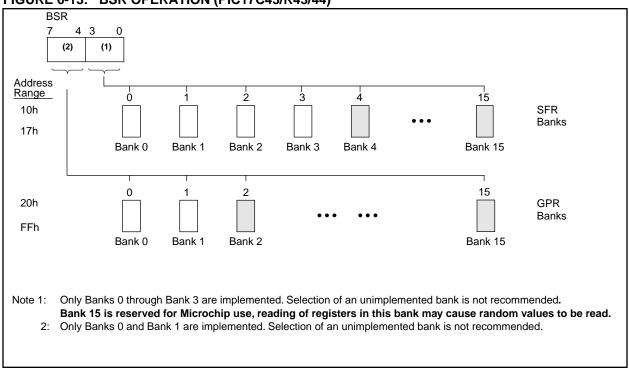

#### 6.8 Bank Select Register (BSR)

The BSR is used to switch between banks in the data memory area (Figure 6-13). In the PIC17C42, PIC17CR42, and PIC17C42A only the lower nibble is implemented. While in the PIC17C43, PIC17CR43, and PIC17C44 devices, the entire byte is implemented. The lower nibble is used to select the peripheral register bank. The upper nibble is used to select the general purpose memory bank.

All the Special Function Registers (SFRs) are mapped into the data memory space. In order to accommodate the large number of registers, a banking scheme has been used. A segment of the SFRs, from address 10h to address 17h, is banked. The lower nibble of the bank select register (BSR) selects the currently active "peripheral bank." Effort has been made to group the peripheral registers of related functionality in one bank. However, it will still be necessary to switch from bank to bank in order to address all peripherals related to a single task. To assist this, a MOVLB bank instruction is in the instruction set. For the PIC17C43, PIC17CR43, and PIC17C44 devices, the need for a large general purpose memory space dictated a general purpose RAM banking scheme. The upper nibble of the BSR selects the currently active general purpose RAM bank. To assist this, a MOVLR bank instruction has been provided in the instruction set.

If the currently selected bank is not implemented (such as Bank 13), any read will read all '0's. Any write is completed to the bit bucket and the ALU status bits will be set/cleared as appropriate.

**Note:** Registers in Bank 15 in the Special Function Register area, are reserved for Microchip use. Reading of registers in this bank may cause random values to be read.

#### FIGURE 6-13: BSR OPERATION (PIC17C43/R43/44)

Example 9-1 shows the instruction sequence to initialize PORTB. The Bank Select Register (BSR) must be selected to Bank 0 for the port to be initialized.

#### EXAMPLE 9-1: INITIALIZING PORTB

| MOVLB | 0     | ; | Select Bank 0                |

|-------|-------|---|------------------------------|

| CLRF  | PORTB | ; | Initialize PORTB by clearing |

|       |       | ; | output data latches          |

| MOVLW | 0xCF  | ; | Value used to initialize     |

|       |       | ; | data direction               |

| MOVWF | DDRB  | ; | Set RB<3:0> as inputs        |

|       |       | ; | RB<5:4> as outputs           |

|       |       | ; | RB<7:6> as inputs            |

|       |       |   |                              |

| Name       | Bit  | Buffer Type | Function                                                                                                                                 |

|------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/CAP1   | bit0 | ST          | Input/Output or the RB0/CAP1 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB1/CAP2   | bit1 | ST          | Input/Output or the RB1/CAP2 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB2/PWM1   | bit2 | ST          | Input/Output or the RB2/PWM1 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB3/PWM2   | bit3 | ST          | Input/Output or the RB3/PWM2 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB4/TCLK12 | bit4 | ST          | Input/Output or the external clock input to Timer1 and Timer2. Software pro-<br>grammable weak pull-up and interrupt on change features. |

| RB5/TCLK3  | bit5 | ST          | Input/Output or the external clock input to Timer3. Software programmable weak pull-up and interrupt on change features.                 |

| RB6        | bit6 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

| RB7        | bit7 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

#### TABLE 9-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger input.

#### TABLE 9-4: REGISTERS/BITS ASSOCIATED WITH PORTB

| Address       | Name   | Bit 7      | Bit 6         | Bit 5        | Bit 4  | Bit 3   | Bit 2  | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets<br>(Note1) |

|---------------|--------|------------|---------------|--------------|--------|---------|--------|-----------|---------|-------------------------------|--------------------------------------------|

| 12h, Bank 0   | PORTB  | PORTB d    | ata latch     |              |        |         |        |           |         | xxxx xxxx                     | uuuu uuuu                                  |

| 11h, Bank 0   | DDRB   | Data dired | ction registe | er for PORTE | 5      |         |        |           |         | 1111 1111                     | 1111 1111                                  |

| 10h, Bank 0   | PORTA  | RBPU       | _             | RA5          | RA4    | RA3     | RA2    | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                                  |

| 06h, Unbanked | CPUSTA | _          | _             | STKAV        | GLINTD | TO      | PD     | _         | _       | 11 11                         | 11 qq                                      |

| 07h, Unbanked | INTSTA | PEIF       | <b>T0CKIF</b> | T0IF         | INTF   | PEIE    | T0CKIE | T0IE      | INTE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF        | TMR2IF       | TMR1IF | CA2IF   | CA1IF  | TXIF      | RCIF    | 0000 0010                     | 0000 0010                                  |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE        | TMR2IE       | TMR1IE | CA2IE   | CA1IE  | TXIE      | RCIE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0        | CA1ED1       | CA1ED0 | T16     | TMR3CS | TMR2CS    | TMR1CS  | 0000 0000                     | 0000 0000                                  |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF        | PWM2ON       | PWM10N | CA1/PR3 | TMR3ON | TMR2ON    | TMR10N  | 0000 0000                     | 0000 0000                                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = Value depends on condition.

Shaded cells are not used by PORTB.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

### FIGURE 13-2: RCSTA REGISTER (ADDRESS: 13h, BANK 0)

| SPEN   | N.W0         R/W - 0         R/W - 0         U - 0         R - 0         R - 0         R - x           RX9         SREN         CREN         —         FERR         OERR         RX9D         R = Readable bit                                                                                                                                             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit7   | bit 0<br>W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)                                                                                                                                                                                                                                                                                      |

| bit 7: | <b>SPEN</b> : Serial Port Enable bit<br>1 = Configures RA5/RX/DT and RA4/TX/CK pins as serial port pins<br>0 = Serial port disabled                                                                                                                                                                                                                        |

| bit 6: | <b>RX9</b> : 9-bit Receive Enable bit<br>1 = Selects 9-bit reception<br>0 = Selects 8-bit reception                                                                                                                                                                                                                                                        |

| bit 5: | SREN: Single Receive Enable bit         This bit enables the reception of a single byte. After receiving the byte, this bit is automatically cleared.         Synchronous mode:         1 = Enable reception         0 = Disable reception         Note: This bit is ignored in synchronous slave reception.         Asynchronous mode:         Don't care |

| bit 4: | CREN: Continuous Receive Enable bit<br>This bit enables the continuous reception of serial data.<br><u>Asynchronous mode:</u><br>1 = Enable reception<br>0 = Disables reception<br><u>Synchronous mode:</u><br>1 = Enables continuous reception until CREN is cleared (CREN overrides SREN)<br>0 = Disables continuous reception                           |

| bit 3: | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                 |

| bit 2: | FERR: Framing Error bit<br>1 = Framing error (Updated by reading RCREG)<br>0 = No framing error                                                                                                                                                                                                                                                            |

| bit 1: | OERR: Overrun Error bit<br>1 = Overrun (Cleared by clearing CREN)<br>0 = No overrun error                                                                                                                                                                                                                                                                  |

| bit 0: | <b>RX9D</b> : 9th bit of receive data (can be the software calculated parity bit)                                                                                                                                                                                                                                                                          |

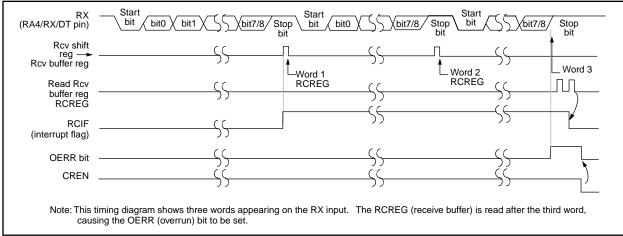

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

#### FIGURE 13-8: ASYNCHRONOUS RECEPTION

| <b>TABLE 13-6</b> : | <b>REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION</b> |

|---------------------|---------------------------------------------------------|

|                     |                                                         |

| Address     | Name  | Bit 7     | Bit 6     | Bit 5    | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|-----------|-----------|----------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR   | RBIF      | TMR3IF    | TMR2IF   | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA | SPEN      | RX9       | SREN     | CREN   | _     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0 | RCREG | RX7       | RX6       | RX5      | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE   | RBIE      | TMR3IE    | TMR2IE   | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA | CSRC      | TX9       | TXEN     | SYNC   | _     | —     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 | SPBRG | Baud rate | generator | register |        |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous reception. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

| Address                                        | Name  | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|--------|--------|--------|-------|-----------|-----------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1                                    | PIR   | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF     | TXIF      | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9    | SREN   | CREN   | _     | FERR      | OERR      | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0                                    | RCREG | RX7   | RX6    | RX5    | RX4    | RX3   | RX2       | RX1       | RX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1                                    | PIE   | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE     | TXIE      | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9    | TXEN   | SYNC   |       | —         | TRMT      | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |        |        |        |       | xxxx xxxx | uuuu uuuu |       |                               |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous master reception.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

# PIC17C4X

| ANDWF                                                  | AND WRE                                                  | EG with                     | f                    |                       |  |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------|-----------------------------|----------------------|-----------------------|--|--|--|--|

| Syntax:                                                | [ <i>label</i> ] A                                       | NDWF                        | f,d                  |                       |  |  |  |  |

| Operands:                                              | $0 \le f \le 255$ $d \in [0,1]$                          | 5                           |                      |                       |  |  |  |  |

| Operation:                                             | (WREG) .                                                 | AND. (f)                    | $\rightarrow$ (dest) | )                     |  |  |  |  |

| Status Affected:                                       | Z                                                        |                             |                      |                       |  |  |  |  |

| Encoding:                                              | 0000                                                     | 101d                        | ffff                 | ffff                  |  |  |  |  |

| Description:                                           | The conten<br>register 'f'.<br>in WREG. I<br>back in reg | lf 'd' is 0<br>f 'd' is 1 t | the result           | is stored             |  |  |  |  |

| Words:                                                 | 1                                                        | 1                           |                      |                       |  |  |  |  |

| Cycles:                                                | 1                                                        |                             |                      |                       |  |  |  |  |

| Q Cycle Activity:                                      |                                                          |                             |                      |                       |  |  |  |  |

| Q1                                                     | Q2                                                       | Q3                          | 3                    | Q4                    |  |  |  |  |

| Decode                                                 | Read<br>register 'f'                                     | Execu                       |                      | Vrite to<br>stination |  |  |  |  |

| Example:                                               | ANDWF                                                    | REG, 1                      |                      |                       |  |  |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG | = 0x17<br>= 0xC2                                         |                             |                      |                       |  |  |  |  |

| BCF            |            |                                  |                                   |       |     |                     |  |  |  |  |

|----------------|------------|----------------------------------|-----------------------------------|-------|-----|---------------------|--|--|--|--|

| Syntax:        |            | [label] E                        | [ <i>label</i> ] BCF f,b          |       |     |                     |  |  |  |  |

| Operand        | s:         | $0 \le f \le 25$ $0 \le b \le 7$ | $0 \le f \le 255$ $0 \le b \le 7$ |       |     |                     |  |  |  |  |

| Operatio       | n:         | $0 \rightarrow (f < b >$         | -)                                |       |     |                     |  |  |  |  |

| Status A       | ffected:   | None                             |                                   |       |     |                     |  |  |  |  |

| Encoding       | g:         | 1000                             | 1bbb                              | fff   | f   | ffff                |  |  |  |  |

| Descripti      | ion:       | Bit 'b' in re                    | gister 'f' is                     | clear | ed. |                     |  |  |  |  |

| Words:         |            | 1                                | 1                                 |       |     |                     |  |  |  |  |

| Cycles:        |            | 1                                |                                   |       |     |                     |  |  |  |  |

| Q Cycle        | Activity:  |                                  |                                   |       |     |                     |  |  |  |  |

|                | Q1         | Q2                               | Q3                                |       |     | Q4                  |  |  |  |  |

| D              | ecode      | Read<br>register 'f'             | Execu                             | ute   |     | Write<br>gister 'f' |  |  |  |  |

| <u>Example</u> | :          | BCF                              | FLAG_R                            | EG,   | 7   |                     |  |  |  |  |

|                | r Instruct | EG = 0xC7                        |                                   |       |     |                     |  |  |  |  |

|                |            | 20 - 0,47                        |                                   |       |     |                     |  |  |  |  |

# PIC17C4X

| TABLRD            | Table R     | ead      |           |

|-------------------|-------------|----------|-----------|

| Example1:         | TABLRD      | 1, 1,    | REG ;     |

| Before Instruc    | ction       |          |           |

| REG               |             | =        | 0x53      |

| TBLATH            |             | =        | 0xAA      |

| TBLATL            |             | =        | 0x55      |

| TBLPTR            |             | =        |           |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

| After Instruction | on (table v | write co | mpletion) |

| REG               |             | =        | 0xAA      |

| TBLATH            |             | =        | 0x12      |

| TBLATL            |             | =        | 0x34      |

| TBLPTR            |             |          | 0xA357    |

| MEMORY            | (TBLPTR)    | =        | 0x5678    |

| Example2:         | TABLRD      | 0, 0,    | REG ;     |

| Before Instruc    | ction       |          |           |

| REG               |             | =        | 0x53      |

| TBLATH            |             | =        | 0xAA      |

| TBLATL            |             | =        | 0x55      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

| After Instruction | on (table v | write co | mpletion) |

| REG               |             | =        | 0x55      |

| TBLATH            |             | =        | 0x12      |

| TBLATL            |             | =        | 0x34      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

|                   |             |          |           |

|                   |             |          |           |

|                   |             |          |           |

|                   |             |          |           |

|                   |             |          |           |

| TABLWT                                       | Table Write                                                                                                                                      |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                      | [label] TABLWT t,i,f                                                                                                                             |

| Operands:                                    | 0 ≤ f ≤ 255<br>i ∈ [0,1]<br>t ∈ [0,1]                                                                                                            |

| Operation:                                   | $f \in [0, 1]$<br>If $f = 0$ ,                                                                                                                   |

| e per au e m                                 | $f \rightarrow TBLATL;$                                                                                                                          |

|                                              | If t = 1,<br>f $\rightarrow$ TBLATH;                                                                                                             |

|                                              | TBLAT $\rightarrow$ Prog Mem (TBLPTF                                                                                                             |

|                                              | If i = 1,<br>TBLPTR + 1 $\rightarrow$ TBLPTR                                                                                                     |

| Status Affected:                             | None                                                                                                                                             |

| Encoding:                                    | 1010 11ti ffff ffff                                                                                                                              |

| Description:                                 | 1. Load value in 'f' into 16-bit table                                                                                                           |

|                                              | latch (TBLAT)<br>If t = 0: load into low byte;                                                                                                   |

|                                              | If t = 1: load into high byte                                                                                                                    |

|                                              | 2. The contents of TBLAT is written to the program memory location                                                                               |

|                                              | pointed to by TBLPTR                                                                                                                             |

|                                              | If TBLPTR points to external<br>program memory location, then                                                                                    |

|                                              | the instruction takes two-cycle                                                                                                                  |

|                                              | If TBLPTR points to an internal                                                                                                                  |

|                                              | EPROM location, then the<br>instruction is terminated when                                                                                       |

|                                              | an interrupt is received.                                                                                                                        |

|                                              | LR/VPP pin must be at the programmir<br>for successful programming of intern                                                                     |

| If MCLR                                      | /VPP = VDD                                                                                                                                       |

|                                              | gramming sequence of internal memore<br>executed, but will not be successf                                                                       |

| (althoug                                     | h the internal memory location may b                                                                                                             |

| disturbe                                     | -7                                                                                                                                               |

|                                              | <ol> <li>The TBLPTR can be automati-<br/>cally incremented</li> </ol>                                                                            |

|                                              |                                                                                                                                                  |

|                                              | If i = 0; TBLPTR is not                                                                                                                          |

|                                              | incremented                                                                                                                                      |

| Words:                                       |                                                                                                                                                  |

|                                              | incremented<br>If i = 1; TBLPTR is incremented                                                                                                   |

| Cycles:                                      | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip                                                            |

| Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1 | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip<br>EPROM program memory)<br>Q2 Q3 Q4                       |

| Cycles:<br>Q Cycle Activity:                 | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip<br>EPROM program memory)<br>Q2 Q3 Q4<br>Read Execute Write |

| Cycles:<br>Q Cycle Activity:<br>Q1           | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip<br>EPROM program memory)<br>Q2 Q3 Q4                       |

# TABLE 17-1:CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS<br/>AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| OSC | PIC17C42-16                              | PIC17C42-25                              |

|-----|------------------------------------------|------------------------------------------|

| RC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 6 mA max.                           | IDD: 6 mA max.                           |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 4 MHz max.                         | Freq: 4 MHz max.                         |

| XT  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| EC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| LF  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 150 μA max. at 32 kHz (WDT enabled) | IDD: 150 μA max. at 32 kHz (WDT enabled) |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 2 MHz max.                         | Freq: 2 MHz max.                         |

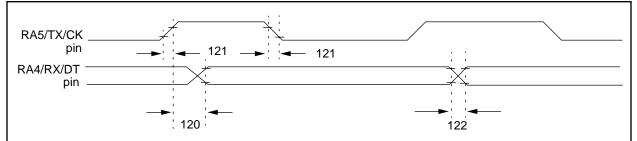

#### FIGURE 17-9: USART MODULE: SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 17-9: SERIAL PORT SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                             | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|------------------------------------------------------------|-----|------|-----|-------|------------|

| 120              | TckH2dtV | SYNC XMIT (MASTER & SLAVE)<br>Clock high to data out valid |     | _    | 65  | ns    |            |

| 121              | TckRF    | Clock out rise time and fall time (Master Mode)            | _   | 10   | 35  | ns    |            |

| 122              | TdtRF    | Data out rise time and fall time                           |     | 10   | 35  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

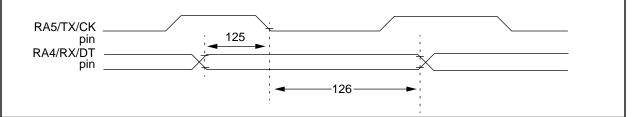

#### FIGURE 17-10: USART MODULE: SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 17-10: SERIAL PORT SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data hold before CK↓ (DT hold time) | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                   | 15  | —    | _   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

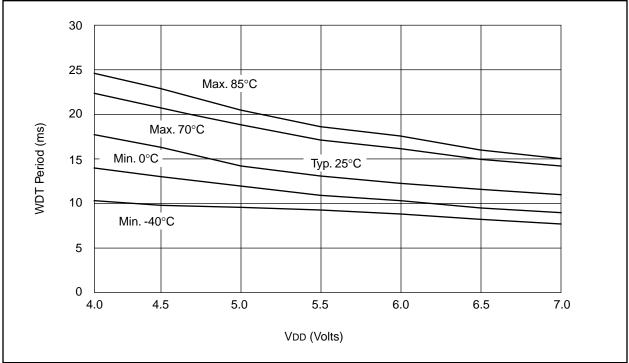

### FIGURE 18-13: WDT TIMER TIME-OUT PERIOD vs. VDD

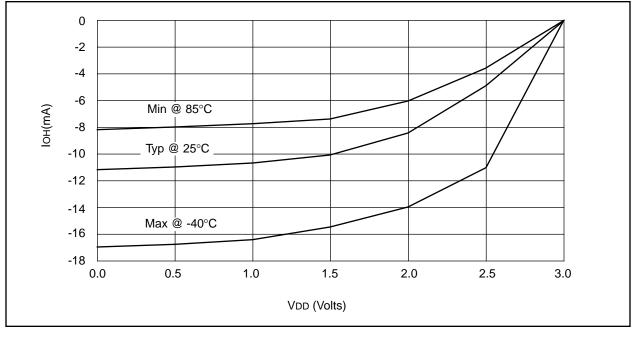

FIGURE 18-14: IOH vs. VOH, VDD = 3V

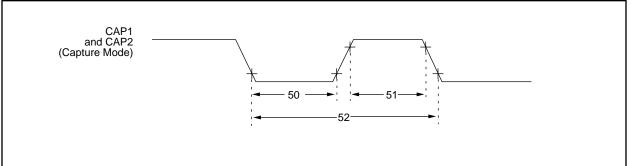

#### FIGURE 19-7: CAPTURE TIMINGS

#### TABLE 19-7: CAPTURE REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                        | Min                | Тур† | Max | Units | Conditions                      |

|------------------|------|---------------------------------------|--------------------|------|-----|-------|---------------------------------|

| 50               | TccL | Capture1 and Capture2 input low time  | 10 *               | —    | —   | ns    |                                 |

| 51               | TccH | Capture1 and Capture2 input high time | 10 *               | —    |     | ns    |                                 |

| 52               | TccP | Capture1 and Capture2 input period    | <u>2Tcy</u> §<br>N | _    | _   | ns    | N = prescale value<br>(4 or 16) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

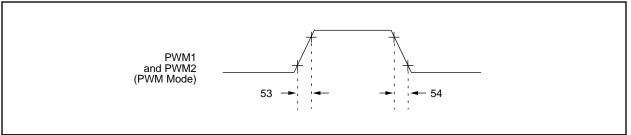

#### FIGURE 19-8: PWM TIMINGS

#### TABLE 19-8: PWM REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                           | Min | Тур† | Max   | Units | Conditions |

|------------------|------|------------------------------------------|-----|------|-------|-------|------------|

| 53               | TccR | PWM1 and PWM2 output rise time           |     | 10 * | 35 *§ | ns    |            |

| 54               | TccF | PWM1 and PWM2 output fall time           |     | 10 * | 35 *§ | ns    |            |

| * The            |      | motors are observatorized but not tested |     |      |       |       |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

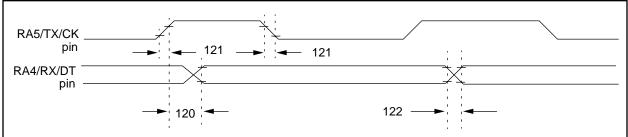

#### FIGURE 19-9: USART MODULE: SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 19-9: SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param | Course                                                                                                                 | Characteristic                    |                          | Min  | Truck | Max | Unite | Conditions |  |

|-------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|------|-------|-----|-------|------------|--|

| No.   | Sym                                                                                                                    | Characteristic                    |                          | wiin | Тур†  | Max | Units | Conditions |  |

| 120   | TckH2dtV                                                                                                               | SYNC XMIT (MASTER &               |                          |      |       |     |       |            |  |

|       |                                                                                                                        | SLAVE)                            | PIC17CR42/42A/43/R43/44  | —    | -     | 50  | ns    |            |  |

|       |                                                                                                                        | Clock high to data out valid      | PIC17LCR42/42A/43/R43/44 | 1 —  | -     | 75  | ns    |            |  |

| 121   | TckRF                                                                                                                  | Clock out rise time and fall time | PIC17CR42/42A/43/R43/44  | —    | —     | 25  | ns    |            |  |

|       |                                                                                                                        | (Master Mode)                     | PIC17LCR42/42A/43/R43/44 | —    | —     | 40  | ns    |            |  |

| 122   | TdtRF                                                                                                                  | Data out rise time and fall time  | PIC17CR42/42A/43/R43/44  | —    | —     | 25  | ns    |            |  |

|       |                                                                                                                        |                                   | PIC17LCR42/42A/43/R43/44 | —    | —     | 40  | ns    |            |  |

| +     | Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not |                                   |                          |      |       |     |       |            |  |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

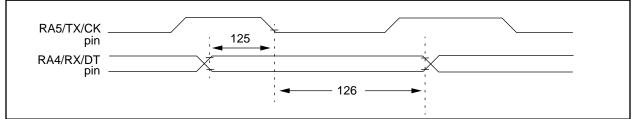

#### FIGURE 19-10: USART MODULE: SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### **TABLE 19-10: SYNCHRONOUS RECEIVE REQUIREMENTS**

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data hold before CK↓ (DT hold time) | 15  |      | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                   | 15  | _    | _   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

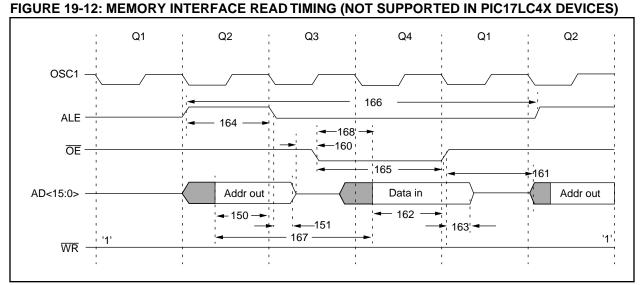

# TABLE 19-12: MEMORY INTERFACE READ REQUIREMENTS (NOT SUPPORTED IN PIC17LC4X DEVICES)

| Parameter<br>No. | Sym      | Characteristic                                            | Min           | Тур†      | Max          | Units | Conditions |

|------------------|----------|-----------------------------------------------------------|---------------|-----------|--------------|-------|------------|

| 150              | TadV2alL | AD15:AD0 (address) valid to ALE↓<br>(address setup time)  | 0.25Tcy - 10  | _         | _            | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)           | 5*            |           | _            | ns    |            |

| 160              | TadZ2oeL | AD15:AD0 hi-impedance to $\overline{\text{OE}}\downarrow$ | 0*            | _         | —            | ns    |            |

| 161              | ToeH2adD | OE↑ to AD15:AD0 driven                                    | 0.25Tcy - 15  | _         | _            | ns    |            |

| 162              | TadV2oeH | Data in valid before OE↑<br>(data setup time)             | 35            | _         | _            | ns    |            |

| 163              | ToeH2adI | OE <sup>↑</sup> to data in invalid (data hold time)       | 0             | _         | _            | ns    |            |

| 164              | TalH     | ALE pulse width                                           | —             | 0.25Tcy § | —            | ns    |            |

| 165              | ToeL     | OE pulse width                                            | 0.5Tcy - 35 § | _         | _            | ns    |            |

| 166              | TalH2alH | ALE↑ to ALE↑(cycle time)                                  | —             | TCY §     | _            | ns    |            |

| 167              | Tacc     | Address access time                                       | _             | _         | 0.75Tcy - 30 | ns    |            |

| 168              | Тое      | Output enable access time<br>(OE low to Data Valid)       | _             | _         | 0.5Tcy - 45  | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

\*

# PIC17C4X

| Delay From External Clock Edge       | 68  |

|--------------------------------------|-----|

| Development Support                  |     |

| Development Tools                    |     |

| Device Drawings                      |     |

| 44-Lead Plastic Surface Mount (MQFP  |     |

| 10x10 mm Body 1.6/0.15 mm Lead Form) | 209 |

| DIGIT BORROW                         | 9   |

| Digit Carry (DC)                     | 9   |

| Duty Cycle                           | 75  |

|                                      |     |

# Ε

| Electrical Characteristics                 |

|--------------------------------------------|

| PIC17C42                                   |

| Absolute Maximum Ratings147                |

| Capture Timing159                          |

| CLKOUT and I/O Timing 156                  |

| DC Characteristics149                      |

| External Clock Timing155                   |

| Memory Interface Read Timing 162           |

| Memory Interface Write Timing              |

| PWM Timing159                              |

| RESET, Watchdog Timer, Oscillator Start-up |

| Timer and Power-up Timer157                |

| Timer0 Clock Timings158                    |

| Timer1, Timer2 and Timer3 Clock Timing 158 |

| USART Module, Synchronous Receive160       |

| USART Module, Synchronous Transmission 160 |

| PIC17C43/44                                |

| Absolute Maximum Ratings175                |

| Capture Timing188                          |

| CLKOUT and I/O Timing 185                  |

| DC Characteristics177                      |

| External Clock Timing184                   |

| Memory Interface Read Timing 191           |

| Memory Interface Write Timing              |

| Parameter Measurement Information183       |

| RESET, Watchdog Timer, Oscillator Start-up |

| Timer and Power-up Timer Timing            |

| Timer0 Clock Timing187                     |

| Timer1, Timer2 and Timer3 Clock Timing 187 |

| Timing Parameter Symbology182              |

| USART Module Synchronous Receive           |

| Timing189                                  |

| USART Module Synchronous Transmission      |

| Timing189                                  |

| EPROM Memory Access Time Order Suffix      |

| Extended Microcontroller                   |

| Extended Microcontroller Mode              |

| External Memory Interface                  |

| External Program Memory Waveforms          |

# F

| Family of Devices | 6   |

|-------------------|-----|

| PIC14000          |     |

| PIC16C5X          |     |

| PIC16CXXX         | 215 |

| PIC16C6X          | 216 |

| PIC16C7X          | 217 |

| PIC16C8X          | 218 |

| PIC16C9XX         |     |

| PIC17CXX          |     |

| FERR              |     |

| FOSC0             |     |

| FOSC1                                                         |          |

|---------------------------------------------------------------|----------|

| FS0                                                           | 36       |

| FS1                                                           | 36       |

| FS2                                                           | 36       |

| FS3                                                           | 36       |

| FSR0                                                          | 34, 40   |

| FSR1                                                          |          |

| Fuzzy Logic Dev. System ( <i>fuzzy</i> TECH <sup>®</sup> -MP) | 143, 145 |

## G

| General Format for Instructions 108                   |

|-------------------------------------------------------|

| General Purpose RAM                                   |

| General Purpose RAM Bank 42                           |

| General Purpose Register (GPR) 32                     |

| GLINTD 25, 37, 78, 105                                |

| GOTO                                                  |

| GPR (General Purpose Register) 32                     |

| Graphs                                                |

| ЮН vs. VOH, VDD = 3V 170, 200                         |

| ЮН vs. VOH, VDD = 5V 171, 201                         |

| IOL vs. VOL, VDD = 3V 171, 201                        |

| IOL vs. VOL, VDD = 5V 172, 202                        |

| Maximum IDD vs. Frequency                             |

| (External Clock 125°C to -40°C) 167, 197              |

| Maximum IPD vs. VDD Watchdog Disabled 168, 198        |

| Maximum IPD vs. VDD Watchdog Enabled 169, 199         |

| RC Oscillator Frequency vs.                           |

| VDD (Cext = 100 pF) 164, 194                          |

| RC Oscillator Frequency vs.                           |

| VDD (Cext = 22 pF) 164, 194                           |

| RC Oscillator Frequency vs.                           |

| VDD (Cext = 300 pF)                                   |

| Transconductance of LF Oscillator vs.VDD 166, 196     |

| Transconductance of XT Oscillator vs. VDD 166, 196    |

| Typical IDD vs. Frequency                             |

| (External Clock 25°C)                                 |

| Typical IPD vs. VDD Watchdog Disabled 25°C . 168, 198 |

| Typical IPD vs. VDD Watchdog Enabled 25°C 169, 199    |

| Typical RC Oscillator vs. Temperature                 |

| VTH (Input Threshold Voltage) of I/O Pins vs.         |

| VDD                                                   |

| VTH (Input Threshold Voltage) of OSC1 Input           |

| (In XT, HS, and LP Modes) vs. VDD 173, 203            |

| VTH, VIL of MCLR, TOCKI and OSC1                      |

| (In RC Mode) vs. VDD                                  |

| WDT Timer Time-Out Period vs. VDD 170, 200            |

### Н

| Hardware Multiplier | <br>49 |

|---------------------|--------|

| i la aware manipher | <br>-0 |

## L

| I/O Ports                      |        |

|--------------------------------|--------|

| Bi-directional                 | 64     |

| I/O Ports                      | 53     |

| Programming Considerations     | 64     |

| Read-Modify-Write Instructions | 64     |

| Successive Operations          | 64     |

| INCF                           | 123    |

| INCFSNZ                        | 124    |

| INCFSZ                         | 123    |

| INDF0                          | 34, 40 |

| INDF1                          | 34, 40 |

|                                |        |

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoq® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.