Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 33MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 454 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-33i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

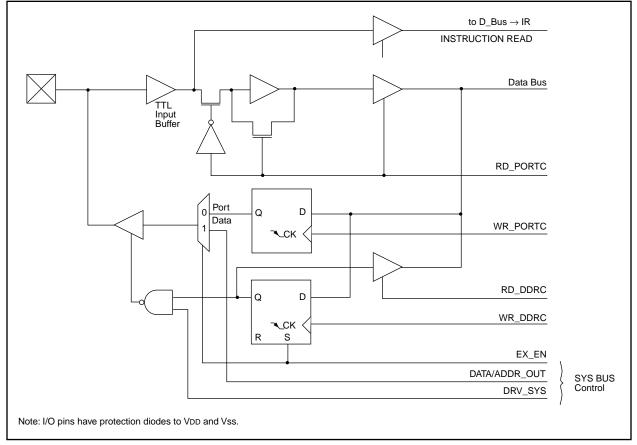

#### 9.3 PORTC and DDRC Registers

PORTC is an 8-bit bi-directional port. The corresponding data direction register is DDRC. A '1' in DDRC configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTC reads the status of the pins, whereas writing to it will write to the port latch. PORTC is multiplexed with the system bus. When operating as the system bus, PORTC is the low order byte of the address/data bus (AD7:AD0). The timing for the system bus is shown in the Electrical Characteristics section.

**Note:** This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-2 shows the instruction sequence to initialize PORTC. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-2: INITIALIZING PORTC

| 1     | ;             | Select Bank 1                                        |

|-------|---------------|------------------------------------------------------|

| PORTC | ;             | Initialize PORTC data                                |

|       | ;             | latches before setting                               |

|       | ;             | the data direction                                   |

|       | ;             | register                                             |

| 0xCF  | ;             | Value used to initialize                             |

|       | ;             | data direction                                       |

| DDRC  | ;             | Set RC<3:0> as inputs                                |

|       | ;             | RC<5:4> as outputs                                   |

|       | ;             | RC<7:6> as inputs                                    |

|       | PORTC<br>0xCF | PORTC ;<br>;<br>;<br>;<br>;<br>0xCF ;<br>DDRC ;<br>; |

#### FIGURE 9-6: BLOCK DIAGRAM OF RC<7:0> PORT PINS

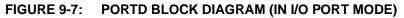

#### 9.4 PORTD and DDRD Registers

PORTD is an 8-bit bi-directional port. The corresponding data direction register is DDRD. A '1' in DDRD configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTD reads the status of the pins, whereas writing to it will write to the port latch. PORTD is multiplexed with the system bus. When operating as the system bus, PORTD is the high order byte of the address/data bus (AD15:AD8). The timing for the system bus is shown in the Electrical Characteristics section.

Note: This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-3 shows the instruction sequence to initialize PORTD. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-3: INITIALIZING PORTD

| MOVLB | 1     | ; | Select Bank 1            |

|-------|-------|---|--------------------------|

| CLRF  | PORTD | ; | Initialize PORTD data    |

|       |       | ; | latches before setting   |

|       |       | ; | the data direction       |

|       |       | ; | register                 |

| MOVLW | 0xCF  | ; | Value used to initialize |

|       |       | ; | data direction           |

| MOVWF | DDRD  | ; | Set RD<3:0> as inputs    |

|       |       | ; | RD<5:4> as outputs       |

|       |       | ; | RD<7:6> as inputs        |

|       |       |   |                          |

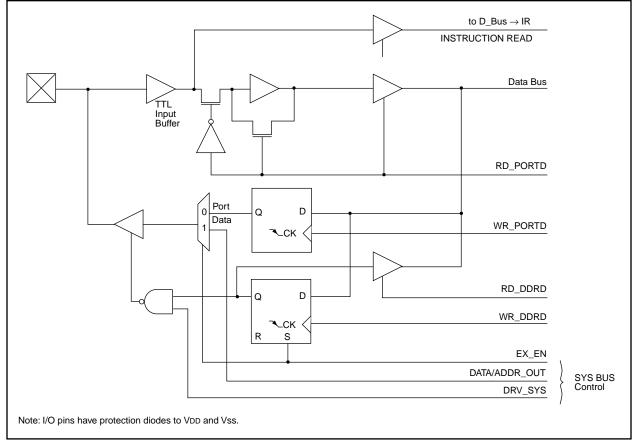

#### 11.3 Read/Write Consideration for TMR0

Although TMR0 is a 16-bit timer/counter, only 8-bits at a time can be read or written during a single instruction cycle. Care must be taken during any read or write.

#### 11.3.1 READING 16-BIT VALUE

The problem in reading the entire 16-bit value is that after reading the low (or high) byte, its value may change from FFh to 00h.

Example 11-1 shows a 16-bit read. To ensure a proper read, interrupts must be disabled during this routine.

#### EXAMPLE 11-1: 16-BIT READ

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

|--------|--------|-------|-----------------|

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| MOVFP  | TMPLO, | WREG  | ;tmplo -> wreg  |

| CPFSLT | TMR0L  |       | ;tmr0l < wreg?  |

| RETURN |        |       | ;no then return |

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| RETURN |        |       | ;return         |

#### 11.3.2 WRITING A 16-BIT VALUE TO TMR0

Since writing to either TMR0L or TMR0H will effectively inhibit increment of that half of the TMR0 in the next cycle (following write), but not inhibit increment of the other half, the user must write to TMR0L first and TMR0H next in two consecutive instructions, as shown in Example 11-2. The interrupt must be disabled. Any write to either TMR0L or TMR0H clears the prescaler.

#### EXAMPLE 11-2: 16-BIT WRITE

BSF CPUSTA, GLINTD ; Disable interrupt MOVFP RAM\_L, TMROL ; MOVFP RAM\_H, TMROH ; BCF CPUSTA, GLINTD ; Done, enable interrupt

#### 11.4 Prescaler Assignments

Timer0 has an 8-bit prescaler. The prescaler assignment is fully under software control; i.e., it can be changed "on the fly" during program execution. When changing the prescaler assignment, clearing the prescaler is recommended before changing assignment. The value of the prescaler is "unknown," and assigning a value that is less then the present value makes it difficult to take this unknown time into account.

#### FIGURE 11-4: TMR0 TIMING: WRITE HIGH OR LOW BYTE

### FIGURE 13-2: RCSTA REGISTER (ADDRESS: 13h, BANK 0)

| SPEN   | N.W0         R/W - 0         R/W - 0         U - 0         R - 0         R - 0         R - x           RX9         SREN         CREN         —         FERR         OERR         RX9D         R = Readable bit                                                                                                                                             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit7   | bit 0<br>W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)                                                                                                                                                                                                                                                                                      |

| bit 7: | <b>SPEN</b> : Serial Port Enable bit<br>1 = Configures RA5/RX/DT and RA4/TX/CK pins as serial port pins<br>0 = Serial port disabled                                                                                                                                                                                                                        |

| bit 6: | <b>RX9</b> : 9-bit Receive Enable bit<br>1 = Selects 9-bit reception<br>0 = Selects 8-bit reception                                                                                                                                                                                                                                                        |

| bit 5: | SREN: Single Receive Enable bit         This bit enables the reception of a single byte. After receiving the byte, this bit is automatically cleared.         Synchronous mode:         1 = Enable reception         0 = Disable reception         Note: This bit is ignored in synchronous slave reception.         Asynchronous mode:         Don't care |

| bit 4: | CREN: Continuous Receive Enable bit<br>This bit enables the continuous reception of serial data.<br><u>Asynchronous mode:</u><br>1 = Enable reception<br>0 = Disables reception<br><u>Synchronous mode:</u><br>1 = Enables continuous reception until CREN is cleared (CREN overrides SREN)<br>0 = Disables continuous reception                           |

| bit 3: | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                 |

| bit 2: | FERR: Framing Error bit<br>1 = Framing error (Updated by reading RCREG)<br>0 = No framing error                                                                                                                                                                                                                                                            |

| bit 1: | OERR: Overrun Error bit<br>1 = Overrun (Cleared by clearing CREN)<br>0 = No overrun error                                                                                                                                                                                                                                                                  |

| bit 0: | <b>RX9D</b> : 9th bit of receive data (can be the software calculated parity bit)                                                                                                                                                                                                                                                                          |

#### TABLE 13-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address     | Name                                      | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------------------------------------------|-------|--------|--------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR                                       | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA                                     | SPEN  | RX9    | SREN   | CREN   | —     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 16h, Bank 0 | TXREG                                     | TX7   | TX6    | TX5    | TX4    | TX3   | TX2   | TX1   | TX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE                                       | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA                                     | CSRC  | TX9    | TXEN   | SYNC   | —     |       | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 | Bank 0 SPBRG Baud rate generator register |       |        |        |        |       |       |       |       |                               | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous master transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

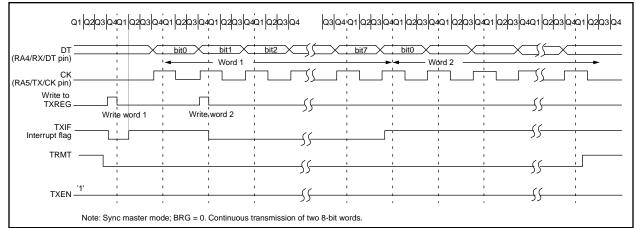

#### FIGURE 13-9: SYNCHRONOUS TRANSMISSION

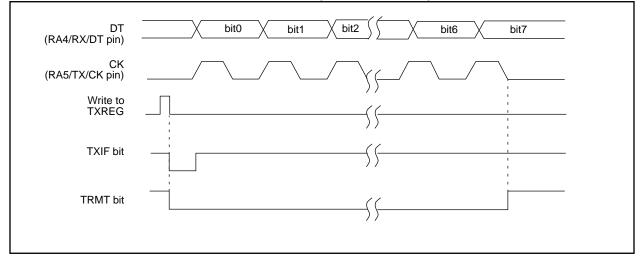

#### FIGURE 13-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

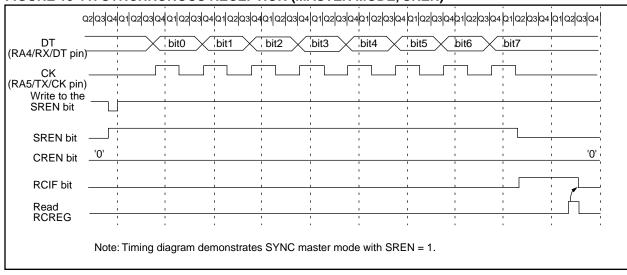

#### 13.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either the SREN (RCSTA<5>) bit or the CREN (RCSTA<4>) bit. Data is sampled on the RA4/RX/DT pin on the falling edge of the clock. If SREN is set, then only a single word is received. If CREN is set, the reception is continuous until CREN is reset. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to RCREG (if it is empty). If the transfer is complete, the interrupt bit RCIF (PIR<0>) is set. The actual interrupt can be enabled/disabled by setting/clearing the RCIE (PIE<0>) bit. RCIF is a read only bit which is RESET by the hardware. In this case it is reset when RCREG has been read and is empty. RCREG is a double buffered register; i.e., it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR. On the clocking of the last bit of the third byte, if RCREG is still full, then the overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. RCREG can be read twice to retrieve the two bytes in the FIFO. The OERR bit has to be cleared in software. This is done by clearing the CREN bit. If OERR bit is set, transfers from RSR to RCREG are inhibited, so it is essential to clear OERR bit if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register will allow the RX9D and FERR bits to be loaded with values for the next received data: therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old FERR and RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. See Section 13.1 for details.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- 6. The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- 7. Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading RCREG.

- 9. If any error occurred, clear the error by clearing CREN.

Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

#### FIGURE 13-11: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

| Address     | Name                                          | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-----------------------------------------------|-------|--------|--------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR                                           | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA                                         | SPEN  | RX9    | SREN   | CREN   |       | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 16h, Bank 0 | TXREG                                         | TX7   | TX6    | TX5    | TX4    | TX3   | TX2   | TX1   | TX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE                                           | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA                                         | CSRC  | TX9    | TXEN   | SYNC   |       | _     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 | 7h, Bank 0 SPBRG Baud rate generator register |       |        |        |        |       |       |       |       |                               | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous slave transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

#### TABLE 13-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address     | Name  | Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank1  | PIR   | RBIF      | TMR3IF    | TMR2IF    | TMR1IF    | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank0  | RCSTA | SPEN      | RX9       | SREN      | CREN      | _     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank0  | RCREG | RX7       | RX6       | RX5       | RX4       | RX3   | RX2   | RX1   | RX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank1  | PIE   | RBIE      | TMR3IE    | TMR2IE    | TMR1IE    | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA | CSRC      | TX9       | TXEN      | SYNC      | _     | -     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank0  | SPBRG | Baud rate | generator | xxxx xxxx | uuuu uuuu |       |       |       |       |                               |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous slave reception.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

| BSF                                                                         | Bit Set f                                                           |                          |        |    |                     |  |  |  |  |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------|--------|----|---------------------|--|--|--|--|

| Syntax:                                                                     | [ <i>label</i> ] E                                                  | [ <i>label</i> ] BSF f,b |        |    |                     |  |  |  |  |

| Operands:                                                                   | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \end{array}$ |                          |        |    |                     |  |  |  |  |

| Operation:                                                                  | $1 \rightarrow (f < b >$                                            | -)                       |        |    |                     |  |  |  |  |

| Status Affected:                                                            | None                                                                |                          |        |    |                     |  |  |  |  |

| Encoding:                                                                   | 1000                                                                | 0bbb                     | fff    | f  | ffff                |  |  |  |  |

| Description:                                                                | Bit 'b' in re                                                       | gister 'f' is            | s set. |    |                     |  |  |  |  |

| Words:                                                                      | 1                                                                   |                          |        |    |                     |  |  |  |  |

| Cycles:                                                                     | 1                                                                   |                          |        |    |                     |  |  |  |  |

| Q Cycle Activity:                                                           |                                                                     |                          |        |    |                     |  |  |  |  |

| Q1                                                                          | Q2                                                                  | Q3                       | 3      | Q4 |                     |  |  |  |  |

| Decode                                                                      | Read<br>register 'f'                                                | Execu                    | ute    |    | Write<br>gister 'f' |  |  |  |  |

| Example:                                                                    | BSF                                                                 | FLAG_RE                  | G, 7   |    |                     |  |  |  |  |

| Before Instruction<br>FLAG_REG= 0x0A<br>After Instruction<br>FLAG_REG= 0x8A |                                                                     |                          |        |    |                     |  |  |  |  |

| BTF        | SC                                                    | Bit Test, s                                                     | Bit Test, skip if Clear                                                                                                                                                                                                                                                 |        |      |  |  |  |  |  |

|------------|-------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--|--|--|--|--|

| Synt       | tax:                                                  | [ <i>label</i> ] B                                              | [label] BTFSC f,b                                                                                                                                                                                                                                                       |        |      |  |  |  |  |  |

| Ope        | rands:                                                | $0 \le f \le 253$ $0 \le b \le 7$                               | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                     |        |      |  |  |  |  |  |

| Ope        | ration:                                               | skip if (f <t< td=""><td>o&gt;) = 0</td><td></td><td></td></t<> | o>) = 0                                                                                                                                                                                                                                                                 |        |      |  |  |  |  |  |

| Stat       | us Affected:                                          | None                                                            |                                                                                                                                                                                                                                                                         |        |      |  |  |  |  |  |

| Enc        | oding:                                                | 1001                                                            | 1bbb                                                                                                                                                                                                                                                                    | ffff   | ffff |  |  |  |  |  |

| Des        | cription:                                             | instruction<br>If bit 'b' is 0<br>fetched dui<br>cution is dia  | If bit 'b' in register 'f' is 0 then the next<br>instruction is skipped.<br>If bit 'b' is 0 then the next instruction<br>fetched during the current instruction exe-<br>cution is discarded, and a NOP is exe-<br>cuted instead, making this a two-cycle<br>instruction |        |      |  |  |  |  |  |

| Wor        | ds:                                                   | 1                                                               |                                                                                                                                                                                                                                                                         |        |      |  |  |  |  |  |

| Cycl       | les:                                                  | 1(2)                                                            |                                                                                                                                                                                                                                                                         |        |      |  |  |  |  |  |

| QC         | ycle Activity:                                        |                                                                 |                                                                                                                                                                                                                                                                         |        |      |  |  |  |  |  |

|            | Q1                                                    | Q2                                                              | Q3                                                                                                                                                                                                                                                                      |        | Q4   |  |  |  |  |  |

|            | Decode                                                | Read<br>register 'f'                                            | Execu                                                                                                                                                                                                                                                                   | ite    | NOP  |  |  |  |  |  |

| lf sk      | ip:                                                   |                                                                 |                                                                                                                                                                                                                                                                         |        |      |  |  |  |  |  |

|            | Q1                                                    | Q2                                                              | Q3                                                                                                                                                                                                                                                                      |        | Q4   |  |  |  |  |  |

|            | Forced NOP                                            | NOP                                                             | Execu                                                                                                                                                                                                                                                                   | ite    | NOP  |  |  |  |  |  |

| <u>Exa</u> | mple:                                                 | FALSE                                                           | BTFSC<br>:                                                                                                                                                                                                                                                              | FLAG,1 |      |  |  |  |  |  |

|            | RE)                                                   |                                                                 |                                                                                                                                                                                                                                                                         |        |      |  |  |  |  |  |

|            | After Instructi<br>If FLAG<7<br>PC<br>If FLAG<7<br>PC | l> = 0;<br>= ac<br>l> = 1;                                      | ldress (TR                                                                                                                                                                                                                                                              |        |      |  |  |  |  |  |

| DECF              | Decreme                  | nt f               |                      | DECFSZ          | Decrement f,                                                      | skip if 0                                                                              |               |  |  |

|-------------------|--------------------------|--------------------|----------------------|-----------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------|--|--|

| Syntax:           | [label]                  | DECF f,d           |                      | Syntax:         | [label] DEC                                                       | [ <i>label</i> ] DECFSZ f,d                                                            |               |  |  |

| Operands:         | 0 ≤ f ≤ 258<br>d ∈ [0,1] | 5                  |                      | Operands:       | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |                                                                                        |               |  |  |

| Operation:        | (f) – 1 $\rightarrow$ (  | dest)              |                      | Operation:      | (f) – 1 $\rightarrow$ (dest                                       |                                                                                        |               |  |  |

| Status Affected:  | OV, C, DC                | ;, Z               |                      |                 | skip if result =                                                  | 0                                                                                      |               |  |  |

| Encoding:         | 0000                     | 011d ff            | ff ffff              | Status Affected | l: None                                                           |                                                                                        |               |  |  |

| Description:      | Decrement                | register 'f'. If ' | d' is 0 the          | Encoding:       | 0001 011                                                          | Ld fff                                                                                 | f ffff        |  |  |

|                   |                          | ored in WREG       |                      | Description:    | mented. If 'd' is                                                 | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed ir |               |  |  |

| Words:            | 1                        |                    |                      |                 | WREG. If 'd' is 1<br>back in register                             |                                                                                        | t is placed   |  |  |

| Cycles:           | 1                        |                    |                      |                 | If the result is 0,                                               |                                                                                        | instruction.  |  |  |

| Q Cycle Activity: |                          |                    |                      |                 | which is already                                                  | / fetched,                                                                             | is discarded, |  |  |

| Q1                | Q2                       | Q3                 | Q4                   |                 | and an NOP is e<br>ing it a two-cycle                             |                                                                                        |               |  |  |

| Decode            | Read<br>register 'f'     | Execute            | Write to destination | Words:          | 1                                                                 |                                                                                        |               |  |  |

| Example:          | DECF                     | CNT, 1             |                      | Cycles:         | 1(2)                                                              |                                                                                        |               |  |  |

| Before Instru     |                          | - ,                |                      | Q Cycle Activit | y:                                                                |                                                                                        |               |  |  |

| CNT               | = 0x01                   |                    |                      | Q1              | Q2                                                                | Q3                                                                                     | Q4            |  |  |

| Z                 | = 0                      |                    |                      | Decode          |                                                                   | xecute                                                                                 | Write to      |  |  |

| After Instruc     | tion                     |                    |                      |                 | register 'f'                                                      |                                                                                        | destination   |  |  |

| CNT               | = 0x00                   |                    |                      | Example:        |                                                                   |                                                                                        | CNT, 1        |  |  |

| Z                 | = 1                      |                    |                      |                 | GC<br>CONTINUE                                                    | OTO                                                                                    | LOOP          |  |  |

|                   |                          |                    |                      | Defers inc      |                                                                   |                                                                                        |               |  |  |

|                   |                          |                    |                      | Before Ins      | liucion                                                           |                                                                                        |               |  |  |

| PC             | =   | Address (HERE)     |

|----------------|-----|--------------------|

| After Instruct | ion |                    |

| CNT            | =   | CNT - 1            |

| If CNT         | =   | 0;                 |

| PC             | =   | Address (CONTINUE) |

| If CNT         | ≠   | 0;                 |

| PC             | =   | Address (HERE+1)   |

| INFSNZ                                               | Incremer                                                                              | Increment f, skip if not 0                                                                                                                                                                                                                                                                                                    |        |                       |  |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------|--|--|--|

| Syntax:                                              | [ <i>label</i> ] II                                                                   | [ <i>label</i> ] INFSNZ f,d                                                                                                                                                                                                                                                                                                   |        |                       |  |  |  |

| Operands:                                            | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                                               | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                             |        |                       |  |  |  |

| Operation:                                           | (f) + 1 $\rightarrow$                                                                 | (f) + 1 $\rightarrow$ (dest), skip if not 0                                                                                                                                                                                                                                                                                   |        |                       |  |  |  |

| Status Affected:                                     | None                                                                                  |                                                                                                                                                                                                                                                                                                                               |        |                       |  |  |  |

| Encoding:                                            | 0010                                                                                  | 010d                                                                                                                                                                                                                                                                                                                          | ffff   | ffff                  |  |  |  |

| Description:                                         | mented. If<br>WREG. If '<br>back in reg<br>If the result<br>which is all<br>and an NO | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'.<br>If the result is not 0, the next instruction,<br>which is already fetched, is discarded,<br>and an NOP is executed instead making<br>it a two-cycle instruction. |        |                       |  |  |  |

| Words:                                               | 1                                                                                     |                                                                                                                                                                                                                                                                                                                               |        |                       |  |  |  |

| Cycles:                                              | 1(2)                                                                                  |                                                                                                                                                                                                                                                                                                                               |        |                       |  |  |  |

| Q Cycle Activity:                                    |                                                                                       |                                                                                                                                                                                                                                                                                                                               |        |                       |  |  |  |

| Q1                                                   | Q2                                                                                    | Q                                                                                                                                                                                                                                                                                                                             | 3      | Q4                    |  |  |  |

| Decode                                               | Read<br>register 'f'                                                                  | Exect                                                                                                                                                                                                                                                                                                                         |        | Vrite to<br>stination |  |  |  |

| lf skip:                                             |                                                                                       |                                                                                                                                                                                                                                                                                                                               |        |                       |  |  |  |

| Q1                                                   | Q2                                                                                    | Q                                                                                                                                                                                                                                                                                                                             | 3      | Q4                    |  |  |  |

| Forced NOP                                           | NOP                                                                                   | Exect                                                                                                                                                                                                                                                                                                                         | ute    | NOP                   |  |  |  |

| Example:                                             | HERE<br>ZERO<br>NZERO                                                                 | INFSNZ                                                                                                                                                                                                                                                                                                                        | REG, 1 |                       |  |  |  |

| Before Instru<br>REG                                 | uction<br>= REG                                                                       |                                                                                                                                                                                                                                                                                                                               |        |                       |  |  |  |

| After Instruc<br>REG<br>If REG<br>PC<br>If REG<br>PC | = REG +<br>= 1;<br>= Addres<br>= 0;                                                   | 1<br>s (zero<br>s (nzero                                                                                                                                                                                                                                                                                                      |        |                       |  |  |  |

| Current      |                        | [ lahal]            |                                                                                                    |                   |                  |  |

|--------------|------------------------|---------------------|----------------------------------------------------------------------------------------------------|-------------------|------------------|--|

| Synt         | ax:                    | [ label ]           | IORLW                                                                                              | К                 |                  |  |

| Ope          | rands:                 | $0 \le k \le 25$    | 55                                                                                                 |                   |                  |  |

| Ope          | ration:                | (WREG)              | .OR. (k)                                                                                           | $\rightarrow$ (WR | EG)              |  |

| State        | us Affected:           | Z                   |                                                                                                    |                   |                  |  |

| Enco         | oding:                 | 1011                | 0011                                                                                               | kkkk              | kkkk             |  |

| Description: |                        | the eight b         | The contents of WREG are OR'ed with<br>the eight bit literal 'k'. The result is<br>placed in WREG. |                   |                  |  |

| Words:       |                        | 1                   |                                                                                                    |                   |                  |  |

| Cycl         | es:                    | 1                   |                                                                                                    |                   |                  |  |

| QC           | ycle Activity:         |                     |                                                                                                    |                   |                  |  |

|              | Q1                     | Q2                  | Q                                                                                                  | 3                 | Q4               |  |

|              | Decode                 | Read<br>literal 'k' | Exect                                                                                              | ute               | Write to<br>WREG |  |

| Example:     |                        | IORLW               | 0x35                                                                                               |                   |                  |  |

|              | Before Instru<br>WREG  | iction<br>= 0x9A    |                                                                                                    |                   |                  |  |

|              | After Instruct<br>WREG | tion<br>= 0xBF      |                                                                                                    |                   |                  |  |

| RLNCF              | Rotate Left f (no carry)                                                                                                                             |          |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Syntax:            | [label] RLNCF f,d                                                                                                                                    |          |

| Operands:          | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$                                                                                    |          |

| Operation:         | $f < n > \rightarrow d < n+1 >;$<br>$f < 7 > \rightarrow d < 0 >$                                                                                    |          |

| Status Affected:   | None                                                                                                                                                 |          |

| Encoding:          | 0010 001d ffff                                                                                                                                       | ffff     |

| Description:       | The contents of register 'f' are re<br>one bit to the left. If 'd' is 0 the re<br>placed in WREG. If 'd' is 1 the re<br>stored back in register 'f'. | esult is |

| Words:             | 1                                                                                                                                                    |          |

| Cycles:            | 1                                                                                                                                                    |          |

| Q Cycle Activity:  |                                                                                                                                                      |          |

| Q1                 | Q2 Q3 Q                                                                                                                                              | 4        |

| Decode             | ReadExecuteWritregister 'f'destir                                                                                                                    |          |

| Example:           | RLNCF REG, 1                                                                                                                                         |          |

| Before Instru      | uction                                                                                                                                               |          |

| C<br>REG           | = 0<br>= 1110 1011                                                                                                                                   |          |

| After Instruc<br>C | tion                                                                                                                                                 |          |

| RRCF                             | Rotate Right f through Carry                                                                                                                                                                       |  |  |  |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                          | [ <i>label</i> ] RRCF f,d                                                                                                                                                                          |  |  |  |  |

| Operands:                        | $0 \le f \le 255$<br>$d \in [0,1]$                                                                                                                                                                 |  |  |  |  |

| Operation:                       |                                                                                                                                                                                                    |  |  |  |  |

| Status Affected                  | С                                                                                                                                                                                                  |  |  |  |  |

| Encoding:                        | 0001 100d ffff ffff                                                                                                                                                                                |  |  |  |  |

| Description:                     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>WREG. If 'd' is 1 the result is placed<br>back in register 'f'. |  |  |  |  |

| Words:                           | 1                                                                                                                                                                                                  |  |  |  |  |

| Cycles:                          | 1                                                                                                                                                                                                  |  |  |  |  |

| Q Cycle Activit                  | :                                                                                                                                                                                                  |  |  |  |  |

| Q1                               | Q2 Q3 Q4                                                                                                                                                                                           |  |  |  |  |

| Decode                           | Read         Execute         Write to           register 'f'         destination                                                                                                                   |  |  |  |  |

| Example:                         | RRCF REG1,0                                                                                                                                                                                        |  |  |  |  |

| Before Ins                       | uction                                                                                                                                                                                             |  |  |  |  |

| REG1<br>C                        | = 1110 0110<br>= 0                                                                                                                                                                                 |  |  |  |  |

| After Instr<br>REG1<br>WREC<br>C | ction<br>= 1110 0110<br>= 0111 0011<br>= 0                                                                                                                                                         |  |  |  |  |

| TABLRD            | Table R     | ead      |           |

|-------------------|-------------|----------|-----------|

| Example1:         | TABLRD      | 1, 1,    | REG ;     |

| Before Instruc    | ction       |          |           |

| REG               |             | =        | 0x53      |

| TBLATH            |             | =        | 0xAA      |

| TBLATL            |             | =        | 0x55      |

| TBLPTR            |             | =        |           |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

| After Instruction | on (table v | write co | mpletion) |

| REG               |             | =        | 0xAA      |

| TBLATH            |             | =        | 0x12      |

| TBLATL            |             | =        | 0x34      |

| TBLPTR            |             |          | 0xA357    |

| MEMORY            | (TBLPTR)    | =        | 0x5678    |

| Example2:         | TABLRD      | 0, 0,    | REG ;     |

| Before Instruc    | ction       |          |           |

| REG               |             | =        | 0x53      |

| TBLATH            |             | =        | 0xAA      |

| TBLATL            |             | =        | 0x55      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

| After Instruction | on (table v | write co | mpletion) |

| REG               |             | =        | 0x55      |

| TBLATH            |             | =        | 0x12      |

| TBLATL            |             | =        | 0x34      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

|                   |             |          |           |

|                   |             |          |           |

|                   |             |          |           |

|                   |             |          |           |

|                   |             |          |           |

| TABLWT                                       | Table Write                                                                                                                                      |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                      | [label] TABLWT t,i,f                                                                                                                             |

| Operands:                                    | 0 ≤ f ≤ 255<br>i ∈ [0,1]<br>t ∈ [0,1]                                                                                                            |

| Operation:                                   | $f \in [0, 1]$<br>If $f = 0$ ,                                                                                                                   |

| e per au e m                                 | $f \rightarrow TBLATL;$                                                                                                                          |

|                                              | If t = 1,<br>f $\rightarrow$ TBLATH;                                                                                                             |

|                                              | TBLAT $\rightarrow$ Prog Mem (TBLPTF                                                                                                             |

|                                              | If i = 1,<br>TBLPTR + 1 $\rightarrow$ TBLPTR                                                                                                     |

| Status Affected:                             | None                                                                                                                                             |

| Encoding:                                    | 1010 11ti ffff ffff                                                                                                                              |

| Description:                                 | 1. Load value in 'f' into 16-bit table                                                                                                           |

|                                              | latch (TBLAT)<br>If t = 0: load into low byte;                                                                                                   |

|                                              | If t = 1: load into high byte                                                                                                                    |

|                                              | 2. The contents of TBLAT is written to the program memory location                                                                               |

|                                              | pointed to by TBLPTR                                                                                                                             |

|                                              | If TBLPTR points to external<br>program memory location, then                                                                                    |

|                                              | the instruction takes two-cycle                                                                                                                  |

|                                              | If TBLPTR points to an internal                                                                                                                  |

|                                              | EPROM location, then the<br>instruction is terminated when                                                                                       |

|                                              | an interrupt is received.                                                                                                                        |

|                                              | LR/VPP pin must be at the programmir<br>for successful programming of intern                                                                     |

| If MCLR                                      | /VPP = VDD                                                                                                                                       |

|                                              | gramming sequence of internal memore<br>executed, but will not be successf                                                                       |

| (althoug                                     | h the internal memory location may b                                                                                                             |

| disturbe                                     | -7                                                                                                                                               |

|                                              | <ol> <li>The TBLPTR can be automati-<br/>cally incremented</li> </ol>                                                                            |

|                                              |                                                                                                                                                  |

|                                              | If i = 0; TBLPTR is not                                                                                                                          |

|                                              | incremented                                                                                                                                      |

| Words:                                       |                                                                                                                                                  |

|                                              | incremented<br>If i = 1; TBLPTR is incremented                                                                                                   |

| Cycles:                                      | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip                                                            |

| Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1 | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip<br>EPROM program memory)<br>Q2 Q3 Q4                       |

| Cycles:<br>Q Cycle Activity:                 | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip<br>EPROM program memory)<br>Q2 Q3 Q4<br>Read Execute Write |

| Cycles:<br>Q Cycle Activity:<br>Q1           | incremented<br>If i = 1; TBLPTR is incremented<br>1<br>2 (many if write is to on-chip<br>EPROM program memory)<br>Q2 Q3 Q4                       |

## TABLE 17-1:CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS<br/>AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| OSC | PIC17C42-16                              | PIC17C42-25                              |

|-----|------------------------------------------|------------------------------------------|

| RC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 6 mA max.                           | IDD: 6 mA max.                           |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 4 MHz max.                         | Freq: 4 MHz max.                         |

| XT  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| EC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| LF  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 150 μA max. at 32 kHz (WDT enabled) | IDD: 150 μA max. at 32 kHz (WDT enabled) |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 2 MHz max.                         | Freq: 2 MHz max.                         |

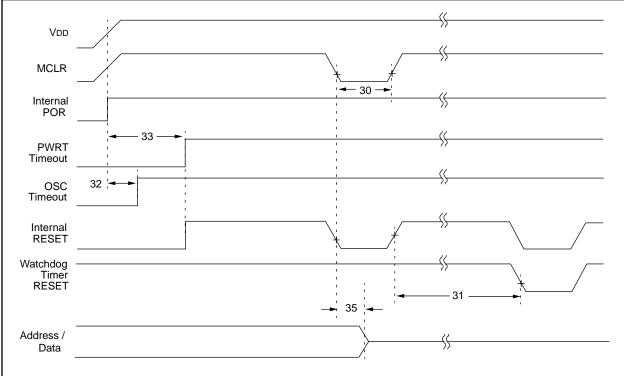

## TABLE 19-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                   |                              | Min   | Тур†      | Max   | Units | Conditions         |

|------------------|----------|--------------------------------------------------|------------------------------|-------|-----------|-------|-------|--------------------|

| 30               | TmcL     | MCLR Pulse Width (low)                           |                              | 100 * | _         | _     | ns    | VDD = 5V           |

| 31               | Twdt     | Watchdog Timer Time-out Period<br>(Prescale = 1) |                              | 5 *   | 12        | 25 *  | ms    | VDD = 5V           |

| 32               | Tost     | Oscillation Start-up Timer Period                |                              | _     | 1024Tosc§ | _     | ms    | Tosc = OSC1 period |

| 33               | Tpwrt    | Power-up Timer Period                            |                              | 40 *  | 96        | 200 * | ms    | VDD = 5V           |

| 35               | TmcL2adl | MCLR to System Inter-<br>face bus (AD15:AD0>)    | PIC17CR42/42A/<br>43/R43/44  | —     | _         | 100 * | ns    |                    |

|                  |          | invalid                                          | PIC17LCR42/<br>42A/43/R43/44 | —     | _         | 120 * | ns    |                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

§ This specification ensured by design.

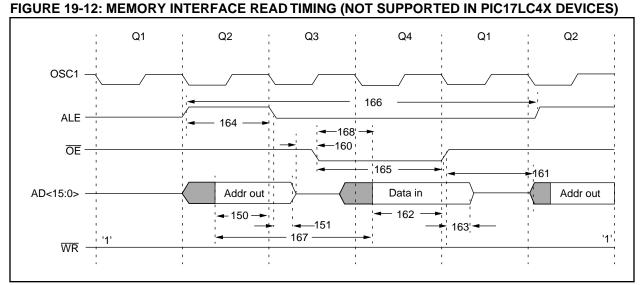

## TABLE 19-12: MEMORY INTERFACE READ REQUIREMENTS (NOT SUPPORTED IN PIC17LC4X DEVICES)

| Parameter<br>No. | Sym      | Characteristic                                            | Min           | Тур†      | Max          | Units | Conditions |

|------------------|----------|-----------------------------------------------------------|---------------|-----------|--------------|-------|------------|

| 150              | TadV2alL | AD15:AD0 (address) valid to ALE↓<br>(address setup time)  | 0.25Tcy - 10  | _         | _            | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)           | 5*            |           | _            | ns    |            |

| 160              | TadZ2oeL | AD15:AD0 hi-impedance to $\overline{\text{OE}}\downarrow$ | 0*            | _         | —            | ns    |            |

| 161              | ToeH2adD | OE↑ to AD15:AD0 driven                                    | 0.25Tcy - 15  | _         | _            | ns    |            |

| 162              | TadV2oeH | Data in valid before OE↑<br>(data setup time)             | 35            | _         | _            | ns    |            |

| 163              | ToeH2adI | OE <sup>↑</sup> to data in invalid (data hold time)       | 0             | _         | _            | ns    |            |

| 164              | TalH     | ALE pulse width                                           | —             | 0.25Tcy § | —            | ns    |            |

| 165              | ToeL     | OE pulse width                                            | 0.5Tcy - 35 § | _         | _            | ns    |            |

| 166              | TalH2alH | ALE↑ to ALE↑(cycle time)                                  | —             | TCY §     | _            | ns    |            |

| 167              | Tacc     | Address access time                                       | _             | _         | 0.75Tcy - 30 | ns    |            |

| 168              | Тое      | Output enable access time<br>(OE low to Data Valid)       | _             | _         | 0.5Tcy - 45  | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

\*

NOTES:

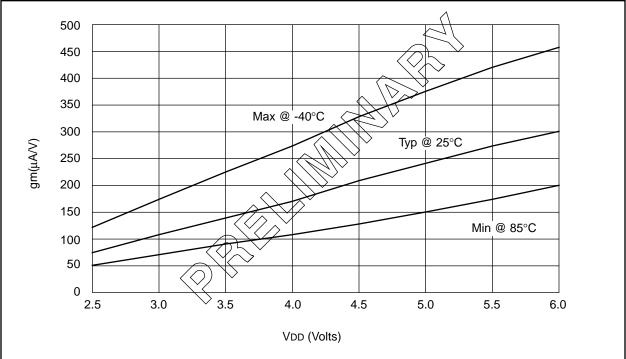

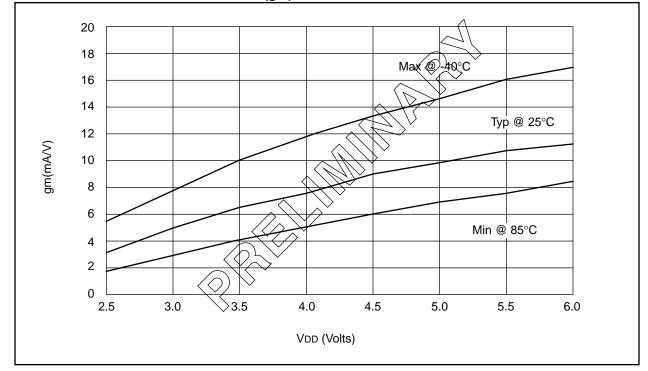

FIGURE 20-6: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

#### 21.6 Package Marking Information 40-Lead PDIP/CERDIP Example PIC17C43-25I/P L006 AABBCDE 9441CCA MICROCHIP MICROCHIP $\bigcirc$ 40 Lead CERDIP Windowed Example XXXXXXXXXXXX PIC17C44 XXXXXXXXXXXX /JW XXXXXXXXXXXX L184 AABBCDE 9444CCT 44-Lead PLCC Example $\mathcal{M}$ $\mathcal{M}$ MICROCHIP MICROCHIP PIC17C42 XXXXXXXXXX ○ <sub>XXXXXXXXX</sub> Ο -16I/L XXXXXXXXXX L013 AABBCDE 9445CCN 44-Lead MQFP Example $\mathcal{M}$ $\mathbf{w}$ XXXXXXXXXX PIC17C44 -25/PT XXXXXXXXXX XXXXXXXXXXX L247 AABBCDE 9450CAT $\cap$ $\cap$ 44-Lead TQFP Example \$ $\mathcal{Q}$ PIC17C44 XXXXXXXXXXX -25/TQ XXXXXXXXXX XXXXXXXXXXX L247 AABBCDE 9450CAT $\cap$ $\cap$ Microchip part number information Legend: MM...M XX...X Customer specific information\* AA Year code (last 2 digits of calendar year) BΒ Week code (week of January 1 is week '01') С Facility code of the plant at which wafer is manufactured C = Chandler, Arizona, U.S.A., S = Tempe, Arizona, U.S.A. D Mask revision number Е Assembly code of the plant or country of origin in which part was assembled Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information. Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond

code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

### **APPENDIX C: WHAT'S NEW**

The structure of the document has been made consistent with other data sheets. This ensures that important topics are covered across all PIC16/17 families. Here is an overview of new features.

Added the following devices:

PIC17CR42

PIC17C42A

PIC17CR43

A 33 MHz option is now available.

### APPENDIX D: WHAT'S CHANGED

To make software more portable across the different PIC16/17 families, the name of several registers and control bits have been changed. This allows control bits that have the same function, to have the same name (regardless of processor family). Care must still be taken, since they may not be at the same special function register address. The following shows the register and bit names that have been changed:

| Old Name | New Name |

|----------|----------|

| TX8/9    | TX9      |

| RC8/9    | RX9      |

| RCD8     | RX9D     |

| TXD8     | TX9D     |