#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

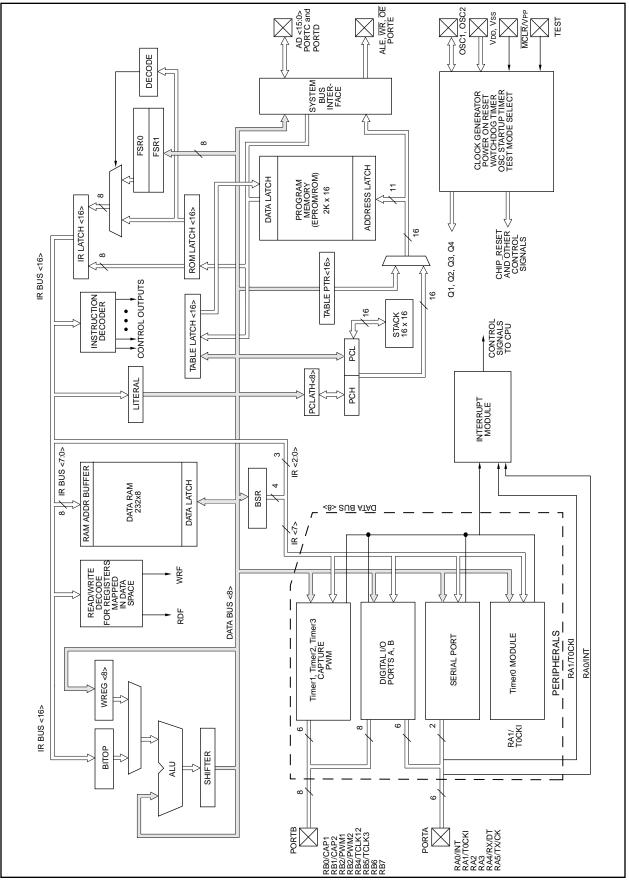

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | PIC                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 33MHz                                                                 |

| Connectivity               | UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 33                                                                    |

| Program Memory Size        | 8KB (4K x 16)                                                         |

| Program Memory Type        | EPROM, UV                                                             |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 454 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                             |

| Data Converters            | -                                                                     |

| Oscillator Type            | External                                                              |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                       |

| Mounting Type              | Through Hole                                                          |

| Package / Case             | 40-CDIP (0.600", 15.24mm) Window                                      |

| Supplier Device Package    | 40-Cerdip                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43-jw |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

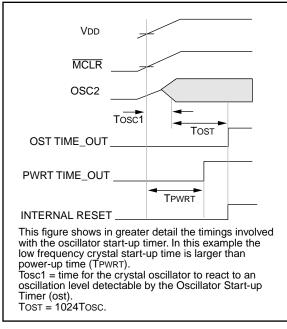

#### 4.1.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (1024Tosc) delay after  $\overline{\text{MCLR}}$  is detected high or a wake-up from SLEEP event occurs.

The OST time-out is invoked only for XT and LF oscillator modes on a Power-on Reset or a Wake-up from SLEEP.

The OST counts the oscillator pulses on the OSC1/CLKIN pin. The counter only starts incrementing after the amplitude of the signal reaches the oscillator input thresholds. This delay allows the crystal oscillator or resonator to stabilize before the device exits reset. The length of time-out is a function of the crystal/resonator frequency.

#### 4.1.4 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First the internal POR signal goes high when the POR trip point is reached. If MCLR is high, then both the OST and PWRT timers start. In general the PWRT time-out is longer, except with low frequency crystals/resonators. The total time-out also varies based on oscillator configuration. Table 4-1 shows the times that are associated with the oscillator configuration. Figure 4-2 and Figure 4-3 display these time-out sequences.

If the device voltage is not within electrical specification at the end of a time-out, the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be held low until the voltage is within the device specification. The use of an external RC delay is sufficient for many of these applications.

## TABLE 4-1:TIME-OUT IN VARIOUSSITUATIONS

| Oscillator<br>Configuration | Power-up                            | Wake up<br>from<br>SLEEP | MCLR<br>Reset |

|-----------------------------|-------------------------------------|--------------------------|---------------|

| XT, LF                      | Greater of:<br>96 ms or<br>1024Tosc | 1024Tosc                 | —             |

| EC, RC                      | Greater of:<br>96 ms or<br>1024Tosc |                          | —             |

The time-out sequence begins from the first rising edge of  $\overline{\text{MCLR}}$ .

Table 4-3 shows the reset conditions for some special registers, while Table 4-4 shows the initialization conditions for all the registers. The shaded registers (in Table 4-4) are for all devices except the PIC17C42. In the PIC17C42, the PRODH and PRODL registers are general purpose RAM.

## TABLE 4-2:STATUS BITS AND THEIR<br/>SIGNIFICANCE

| TO | PD | Event                                                                              |

|----|----|------------------------------------------------------------------------------------|

| 1  | 1  | Power-on Reset, MCLR Reset during normal operation, or CLRWDT instruction executed |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP                            |

| 0  | 1  | WDT Reset during normal operation                                                  |

| 0  | 0  | WDT Reset during SLEEP                                                             |

In Figure 4-2, Figure 4-3 and Figure 4-4, TPWRT > TOST, as would be the case in higher frequency crystals. For lower frequency crystals, (i.e., 32 kHz) TOST would be greater.

#### TABLE 4-3: RESET CONDITION FOR THE PROGRAM COUNTER AND THE CPUSTA REGISTER

| Event                                      |                 | PCH:PCL               | CPUSTA | OST Active |

|--------------------------------------------|-----------------|-----------------------|--------|------------|

| Power-on Reset                             |                 | 0000h                 | 11 11  | Yes        |

| MCLR Reset during normal ope               | ration          | 0000h                 | 11 11  | No         |

| MCLR Reset during SLEEP                    |                 | 0000h                 | 11 10  | Yes (2)    |

| WDT Reset during normal operation          | ation           | 0000h                 | 11 01  | No         |

| WDT Reset during SLEEP (3)                 |                 | 0000h                 | 11 00  | Yes (2)    |

| Interrupt wake-up from SLEEP GLINTD is set |                 | PC + 1                | 11 10  | Yes (2)    |

|                                            | GLINTD is clear | PC + 1 <sup>(1)</sup> | 10 10  | Yes (2)    |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0'.

Note 1: On wake-up, this instruction is executed. The instruction at the appropriate interrupt vector is fetched and then executed.

2: The OST is only active when the Oscillator is configured for XT or LF modes.

3: The Program Counter = 0, that is the device branches to the reset vector. This is different from the mid-range devices.

#### FIGURE 4-5: OSCILLATOR START-UPTIME

#### FIGURE 4-6: USING ON-CHIP POR

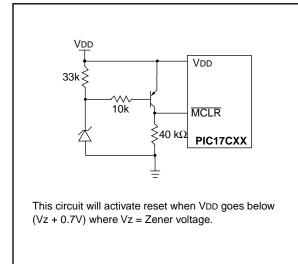

#### FIGURE 4-7: BROWN-OUT PROTECTION CIRCUIT 1

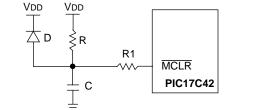

## FIGURE 4-8: PIC17C42 EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: An external Power-on Reset circuit is required only if VDD power-up time is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R < 40 k $\Omega$  is recommended to ensure that the voltage drop across R does not exceed 0.2V (max. leakage current spec. on the  $\overline{MCLR}/VPP$  pin is 5  $\mu$ A). A larger voltage drop will degrade VIH level on the  $\overline{MCLR}/VPP$  pin.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or (Electrical Overstress) EOS.

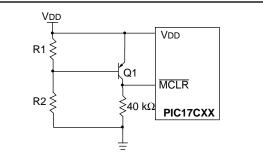

FIGURE 4-9: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

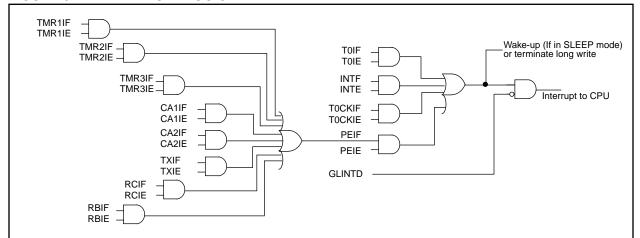

## 5.0 INTERRUPTS

The PIC17C4X devices have 11 sources of interrupt:

- External interrupt from the RA0/INT pin

- Change on RB7:RB0 pins

- TMR0 Overflow

- TMR1 Overflow

- TMR2 Overflow

- TMR3 Overflow

- USART Transmit buffer empty

- USART Receive buffer full

- Capture1

- Capture2

- T0CKI edge occurred

There are four registers used in the control and status of interrupts. These are:

- CPUSTA

- INTSTA

- PIE

- PIR

The CPUSTA register contains the GLINTD bit. This is the Global Interrupt Disable bit. When this bit is set, all interrupts are disabled. This bit is part of the controller core functionality and is described in the Memory Organization section. When an interrupt is responded to, the GLINTD bit is automatically set to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with the interrupt vector address. There are four interrupt vectors. Each vector address is for a specific interrupt source (except the peripheral interrupts which have the same vector address). These sources are:

- External interrupt from the RA0/INT pin

- TMR0 Overflow

- T0CKI edge occurred

- Any peripheral interrupt

When program execution vectors to one of these interrupt vector addresses (except for the peripheral interrupt address), the interrupt flag bit is automatically cleared. Vectoring to the peripheral interrupt vector address does not automatically clear the source of the interrupt. In the peripheral interrupt service routine, the source(s) of the interrupt can be determined by testing the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests.

All of the individual interrupt flag bits will be set regardless of the status of their corresponding mask bit or the GLINTD bit.

For external interrupt events, there will be an interrupt latency. For two cycle instructions, the latency could be one instruction cycle longer.

The "return from interrupt" instruction, RETFIE, can be used to mark the end of the interrupt service routine. When this instruction is executed, the stack is "POPed", and the GLINTD bit is cleared (to re-enable interrupts).

#### FIGURE 5-1: INTERRUPT LOGIC

© 1996 Microchip Technology Inc.

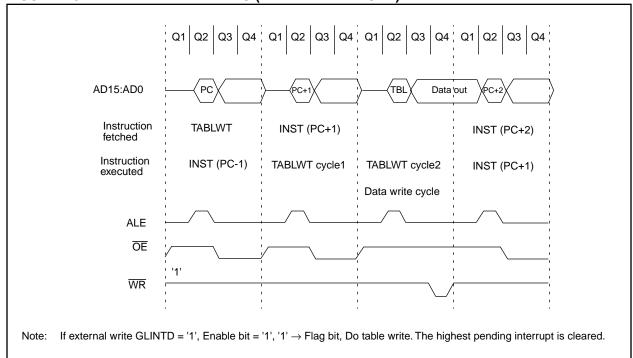

#### 7.2 <u>Table Writes to External Memory</u>

Table writes to external memory are always two-cycle instructions. The second cycle writes the data to the external memory location. The sequence of events for an external memory write are the same for an internal write.

| Note: | If an interrupt is pending or occurs during the TABLWT, the two cycle table write |

|-------|-----------------------------------------------------------------------------------|

|       | completes. The RA0/INT, TMR0, or T0CKI                                            |

|       | interrupt flag is automatically cleared or                                        |

|       | the pending peripheral interrupt is                                               |

|       | acknowledged.                                                                     |

7.2.2 TABLE WRITE CODE

The "i" operand of the TABLWT instruction can specify that the value in the 16-bit TBLPTR register is automatically incremented for the next write. In Example 7-1, the TBLPTR register is not automatically incremented.

#### EXAMPLE 7-1: TABLE WRITE

| CLRWDT |                 | ; | Clear WDT      |

|--------|-----------------|---|----------------|

| MOVLW  | HIGH (TBL_ADDR) | ; | Load the Table |

| MOVWF  | TBLPTRH         | ; | address        |

| MOVLW  | LOW (TBL_ADDR)  | ; |                |

| MOVWF  | TBLPTRL         | ; |                |

| MOVLW  | HIGH (DATA)     | ; | Load HI byte   |

| TLWT   | 1, WREG         | ; | in TABLATCH    |

| MOVLW  | LOW (DATA)      | ; | Load LO byte   |

| TABLWT | 0,0,WREG        | ; | in TABLATCH    |

|        |                 | ; | and write to   |

|        |                 | ; | program memory |

|        |                 | ; | (Ext. SRAM)    |

|        |                 |   |                |

#### FIGURE 7-5: TABLWT WRITE TIMING (EXTERNAL MEMORY)

NOTES:

#### 13.2 USART Asynchronous Mode

In this mode, the USART uses standard nonreturn-to-zero (NRZ) format (one start bit, eight or nine data bits, and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock x64 of the bit shift rate. Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

The asynchronous mode is selected by clearing the SYNC bit (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

#### 13.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 13-3. The heart of the transmitter is the transmit shift register (TSR). The shift register obtains its data from the read/write transmit buffer (TXREG). TXREG is loaded with data in software. The TSR is not loaded until the stop bit has been transmitted from the previous load. As soon as the stop bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one TCY at the end of the current BRG cycle), the TXREG is empty and an interrupt bit, TXIF (PIR<1>) is set. This interrupt can be enabled or disabled by the TXIE bit (PIE<1>). TXIF will be set regardless of TXIE and cannot be reset in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of the TXREG, the TRMT (TXSTA<1>) bit shows the status of the TSR. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty.

| Note: | The TSR is not mapped in data memory, |

|-------|---------------------------------------|

|       | so it is not available to the user.   |

Transmission enabled setting is by the TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 13-5). The transmission can also be started by first loading TXREG and then setting TXEN. Normally when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to TSR resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 13-6). Clearing TXEN during a transmission will cause the transmission to be aborted. This will reset the transmitter and the RA5/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty).

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. Load data to the TXREG register.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 7. Enable the transmission by setting TXEN (starts transmission).

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the opposite order.

Note: To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

#### 14.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLK-OUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation and SLEEP mode, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 14.1).

Under normal operation, the WDT must be cleared on a regular interval. This time is less the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

#### 14.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms, (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a postscaler with a division ratio of up to 1:256 can be assigned to the WDT. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

#### 14.3.2 CLEARING THE WDT AND POSTSCALER

The WDT and postscaler are cleared when:

- The device is in the reset state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the reset state.

#### 14.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT postscaler) it may take several seconds before a WDT time-out occurs.

The WDT and postscaler is the Power-up Timer during the Power-on Reset sequence.

#### 14.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the  $\overline{\text{TO}}$  bit is cleared (device is not reset). The CLRWDT instruction can be used to set the  $\overline{\text{TO}}$  bit. This allows the WDT to be a simple overflow timer. When in sleep, the WDT does not increment.

#### 14.4 Power-down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction. This clears the Watchdog Timer and postscaler (if enabled). The  $\overrightarrow{PD}$  bit is cleared and the  $\overrightarrow{TO}$  bit is set (in the CPUSTA register). In SLEEP mode, the oscillator driver is turned off. The I/O ports maintain their status (driving high, low, or hi-impedance).

The  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level (VIHMC). A WDT time-out RESET does not drive the  $\overline{\text{MCLR}}/\text{VPP}$  pin low.

#### 14.4.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- A POR reset

- External reset input on MCLR/VPP pin

- WDT Reset (if WDT was enabled)

- Interrupt from RA0/INT pin, RB port change, T0CKI interrupt, or some Peripheral Interrupts

The following peripheral interrupts can wake-up from SLEEP:

- · Capture1 interrupt

- Capture2 interrupt

- · USART synchronous slave transmit interrupt

- · USART synchronous slave receive interrupt

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

Any reset event will cause a device reset. Any interrupt event is considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the CPUSTA register can be used to determine the cause of device reset. The

$\overline{PD}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{TO}$  bit is cleared if WDT time-out occurred (and caused wake-up).

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GLINTD bit. If the GLINTD bit is set (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GLINTD bit is clear (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt vector address. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

Note: If the global interrupts are disabled (GLINTD is set), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from sleep. The TO bit is set, and the PD bit is cleared.

The WDT is cleared when the device wake from SLEEP, regardless of the source of wake-up.

14.4.1.1 WAKE-UP DELAY

When the oscillator type is configured in XT or LF mode, the Oscillator Start-up Timer (OST) is activated on wake-up. The OST will keep the device in reset for 1024Tosc. This needs to be taken into account when considering the interrupt response time when coming out of SLEEP.

#### FIGURE 14-9: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                              | Q1   Q2   Q3   Q4                                                                                     | Q1   Q2   Q3   Q4                                  | Q1   Q2      | Q3   Q4      | Q1   Q2       | Q3  Q4                 | Q1   Q2   Q3   Q4                            |

|------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|--------------|---------------|------------------------|----------------------------------------------|

| OSC1                         |                                                                                                       |                                                    |              |              |               | $\frown \frown \frown$ |                                              |

| CLKOUT(4)                    |                                                                                                       | /                                                  |              | Tost(2)      | \/<br>\/      |                        |                                              |

| INT                          |                                                                                                       |                                                    |              |              | I<br>I        |                        |                                              |

| (RA0/INT pin)                | ı ı                                                                                                   |                                                    | : (          |              | 1             |                        | <u>1                                    </u> |

| INTF flag                    |                                                                                                       |                                                    | <u>`</u>     |              | I             |                        | Interrupt Latency (2)                        |

| GLINTD bit                   | 1<br>11                                                                                               |                                                    | · ·          |              | I             |                        | ·                                            |

|                              | i i                                                                                                   |                                                    | Processor    |              | 1             |                        | 1 I                                          |

| INSTRUCTION                  | FLOW                                                                                                  |                                                    | in SLEEP     |              | 1<br>1        |                        | I I<br>I I                                   |

| PC                           | C PC                                                                                                  | PC+1                                               |              | +2           | × 0004        | h                      | × <u>0005h</u>                               |

| Instruction (<br>fetched     | Inst (PC) = SLEEP                                                                                     | Inst (PC+1)                                        |              |              | Inst (PC      | +2)                    |                                              |

| Instruction {                | Inst (PC-1)                                                                                           | SLEEP                                              |              |              | Inst (PC      | +1)                    | Dummy Cycle                                  |

| 2: Tost = 102<br>3: When GLI | scillator mode assume<br>4Tosc (drawing not to s<br>NTD = 0 processor jum<br>s not available in these | scale). This delay will<br>ps to interrupt routing | e after wake | -up. If GLIN | ITD = 1, exec | ution will             | continue in line.                            |

| INFSNZ                                               | Incremer                                                                                                            | Increment f, skip if not 0                                                            |                                                                            |                                                |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------|--|--|

| Syntax:                                              | [ <i>label</i> ] II                                                                                                 | NFSNZ                                                                                 | f,d                                                                        |                                                |  |  |

| Operands:                                            | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                                                                             | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$                     |                                                                            |                                                |  |  |

| Operation:                                           | (f) + 1 $\rightarrow$                                                                                               | (f) + 1 $\rightarrow$ (dest), skip if not 0                                           |                                                                            |                                                |  |  |

| Status Affected:                                     | None                                                                                                                |                                                                                       |                                                                            |                                                |  |  |

| Encoding:                                            | 0010                                                                                                                | 010d                                                                                  | ffff                                                                       | ffff                                           |  |  |

| Description:                                         | The conter<br>mented. If<br>WREG. If '<br>back in reg<br>If the result<br>which is all<br>and an NO<br>it a two-cyc | 'd' is 0 the<br>d' is 1 the<br>jister 'f'.<br>t is not 0,<br>ready feto<br>P is exect | e result is p<br>result is p<br>the next in<br>ched, is dis<br>uted instea | placed in<br>blaced<br>istruction,<br>scarded, |  |  |

| Words:                                               | 1                                                                                                                   |                                                                                       |                                                                            |                                                |  |  |

| Cycles:                                              | 1(2)                                                                                                                |                                                                                       |                                                                            |                                                |  |  |

| Q Cycle Activity:                                    |                                                                                                                     |                                                                                       |                                                                            |                                                |  |  |

| Q1                                                   | Q2                                                                                                                  | Q                                                                                     | 3                                                                          | Q4                                             |  |  |

| Decode                                               | Read<br>register 'f'                                                                                                | Exect                                                                                 |                                                                            | Vrite to<br>stination                          |  |  |

| lf skip:                                             |                                                                                                                     |                                                                                       |                                                                            |                                                |  |  |

| Q1                                                   | Q2                                                                                                                  | Q                                                                                     | 3                                                                          | Q4                                             |  |  |

| Forced NOP                                           | NOP                                                                                                                 | Exect                                                                                 | ute                                                                        | NOP                                            |  |  |

| Example:                                             | HERE<br>ZERO<br>NZERO                                                                                               | INFSNZ                                                                                | REG, 1                                                                     |                                                |  |  |

| Before Instru<br>REG                                 | uction<br>= REG                                                                                                     |                                                                                       |                                                                            |                                                |  |  |

| After Instruc<br>REG<br>If REG<br>PC<br>If REG<br>PC | = REG +<br>= 1;<br>= Addres<br>= 0;                                                                                 | 1<br>s (zero<br>s (nzero                                                              |                                                                            |                                                |  |  |

| Current      |                        | [ lahal]                                |               |                   |                  |

|--------------|------------------------|-----------------------------------------|---------------|-------------------|------------------|

| Synt         | ax:                    | [ label ]                               | IORLW         | К                 |                  |

| Ope          | rands:                 | $0 \le k \le 25$                        | 55            |                   |                  |

| Ope          | ration:                | (WREG)                                  | .OR. (k)      | $\rightarrow$ (WR | EG)              |

| State        | us Affected:           | Z                                       |               |                   |                  |

| Encoding:    |                        | 1011                                    | 0011          | kkkk              | kkkk             |

| Description: |                        | The conte<br>the eight b<br>placed in \ | it literal 'k |                   |                  |

| Words:       |                        | 1                                       |               |                   |                  |

| Cycl         | es:                    | 1                                       |               |                   |                  |

| QC           | ycle Activity:         |                                         |               |                   |                  |

|              | Q1                     | Q2                                      | Q             | 3                 | Q4               |

|              | Decode                 | Read<br>literal 'k'                     | Exect         | ute               | Write to<br>WREG |

| <u>Exa</u>   | <u>mple</u> :          | IORLW                                   | 0x35          |                   |                  |

|              | Before Instru<br>WREG  | iction<br>= 0x9A                        |               |                   |                  |

|              | After Instruct<br>WREG | tion<br>= 0xBF                          |               |                   |                  |

| MOVFP                        | Move f to                 | р                                 |                                                                         | MOVLB                    | Move Lite                             | eral to low i       | nibble in BSR                 |

|------------------------------|---------------------------|-----------------------------------|-------------------------------------------------------------------------|--------------------------|---------------------------------------|---------------------|-------------------------------|

| Syntax:                      | [ <i>label</i> ] N        | IOVFP f,p                         |                                                                         | Syntax:                  | [ label ]                             | MOVLB k             |                               |

| Operands:                    | 0 ≤ f ≤ 255               | 5                                 |                                                                         | Operands:                | $0 \le k \le 15$                      | 5                   |                               |

|                              | $0 \le p \le 31$          |                                   |                                                                         | Operation:               | k  ightarrow (BSR                     | (<3:0>)             |                               |

| Operation:                   | $(f) \to (p)$             |                                   |                                                                         | Status Affected:         | None                                  |                     |                               |

| Status Affected:             | None                      |                                   |                                                                         | Encoding:                | 1011                                  | 1000 ui             | uuu kkkk                      |

| Encoding:                    | 011p                      | pppp ff                           | ff ffff                                                                 | Description:             | The four bi                           | t literal 'k' is lo | baded in the                  |

| Description:                 | to data mer<br>can be any | mory location '<br>where in the 2 | nory location 'f'<br>p'. Location 'f'<br>56 word data<br>'p' can be 00h |                          | low 4-bits of are affected is unchang | of the Bank Se      |                               |

|                              |                           | 'f' can be WR                     | EG (a useful                                                            | Words:                   | 1                                     |                     |                               |

|                              | •                         | ecial situation).                 |                                                                         | Cycles:                  | 1                                     |                     |                               |

|                              |                           |                                   | on to a periph-                                                         | Q Cycle Activity:        |                                       |                     |                               |

|                              |                           |                                   | transmit buffer                                                         | Q1                       | Q2                                    | Q3                  | Q4                            |

|                              | indirectly a              | ort). Both 'f' an<br>ddressed.    | d p can be                                                              | Decode                   | Read                                  | Execute             | Write literal                 |

| Words:                       | 1                         |                                   |                                                                         |                          | literal 'u:k'                         |                     | 'k' to<br>BSR<3:0>            |

| Cycles:                      | 1                         |                                   |                                                                         | Example:                 | MOVLB                                 | 0x5                 |                               |

| Q Cycle Activity             | :                         |                                   |                                                                         | Before Instru            | uction                                |                     |                               |

| Q1                           | Q2                        | Q3                                | Q4                                                                      | BSR reg                  | ister = 0x                            | :22                 |                               |

| Decode                       | Read<br>register 'f'      | Execute                           | Write<br>register 'p'                                                   | After Instruc<br>BSR reg |                                       | :25                 |                               |

| Example:                     | MOVFP I                   | REG1, REG2                        |                                                                         | Note: For th             | ne PIC17C42                           | 2, only the lo      | ow four bits of               |

| Before Insti<br>REG1<br>REG2 |                           | 33,<br>11                         |                                                                         |                          | BSR registe<br>ed. The uppe           |                     | sically imple-<br>ead as '0'. |

| After Instru<br>REG1         |                           | 33,                               |                                                                         |                          |                                       |                     |                               |

REG2

0x33

=

| MULLW                                                     | Multiply I                                                                                                                         | _iteral with V                                                                                                                                                                            | VREG                                                                                      | MULWF                                         | Multiply V                                                                                                                  | VREG with                                                                                                                                                                                                         | f                                                                                                              |  |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| Syntax:                                                   | [ label ]                                                                                                                          | MULLW k                                                                                                                                                                                   |                                                                                           | Syntax:                                       | [ label ]                                                                                                                   | MULWF f                                                                                                                                                                                                           |                                                                                                                |  |

| Operands:                                                 | $0 \le k \le 25$                                                                                                                   | 5                                                                                                                                                                                         |                                                                                           | Operands:                                     | $0 \le f \le 25$                                                                                                            | $0 \le f \le 255$                                                                                                                                                                                                 |                                                                                                                |  |

| Operation:                                                | (k x WRE                                                                                                                           | G) $\rightarrow$ PRODI                                                                                                                                                                    | H:PRODL                                                                                   | Operation:                                    | (WREG x                                                                                                                     | (WREG x f) $\rightarrow$ PRODH:PROD                                                                                                                                                                               |                                                                                                                |  |

| Status Affected:                                          | None                                                                                                                               |                                                                                                                                                                                           |                                                                                           | Status Affected                               | : None                                                                                                                      |                                                                                                                                                                                                                   |                                                                                                                |  |

| Encoding:                                                 | 1011                                                                                                                               | 1100 kk                                                                                                                                                                                   | kk kkkk                                                                                   | Encoding:                                     | 0011                                                                                                                        | 0100 ff                                                                                                                                                                                                           | Ef ffff                                                                                                        |  |

| Description:                                              | out betwee<br>and the 8-b<br>result is pla<br>register pai<br>high byte.<br>WREG is u<br>None of the<br>Note that n<br>is possible | ed multiplicatio<br>n the contents<br>bit literal 'k'. The<br>aced in PRODH<br>ir. PRODH con<br>unchanged.<br>e status flags a<br>either overflow<br>in this operatio<br>ssible but not o | of WREG<br>e 16-bit<br>H:PRODL<br>tains the<br>are affected.<br>y nor carry<br>on. A zero | Description:                                  | out betwee<br>and the reg<br>16-bit resul<br>PRODH:PF<br>PRODH co<br>Both WREC<br>None of the<br>Note that n<br>is possible | d multiplication<br>n the contents<br>jister file locat<br>t is stored in t<br>RODL register<br>ntains the hig<br>G and 'f' are un<br>e status flags a<br>either overflow<br>in this operations<br>ssible but not | s of WREG<br>ion 'f'. The<br>he<br>pair.<br>h byte.<br>nchanged.<br>are affected.<br>v nor carry<br>on. A zero |  |

| Words:                                                    | 1                                                                                                                                  |                                                                                                                                                                                           |                                                                                           | Words:                                        | 1                                                                                                                           |                                                                                                                                                                                                                   |                                                                                                                |  |

| Cycles:                                                   | 1                                                                                                                                  |                                                                                                                                                                                           |                                                                                           | Cycles:                                       | 1                                                                                                                           |                                                                                                                                                                                                                   |                                                                                                                |  |

| Q Cycle Activity:                                         |                                                                                                                                    |                                                                                                                                                                                           |                                                                                           | Q Cycle Activity                              | :                                                                                                                           |                                                                                                                                                                                                                   |                                                                                                                |  |

| Q1                                                        | Q2                                                                                                                                 | Q3                                                                                                                                                                                        | Q4                                                                                        | Q1                                            | Q2                                                                                                                          | Q3                                                                                                                                                                                                                | Q4                                                                                                             |  |

| Decode                                                    | Read<br>literal 'k'                                                                                                                | Execute                                                                                                                                                                                   | Write<br>registers<br>PRODH:<br>PRODL                                                     | Decode                                        | Read<br>register 'f'                                                                                                        | Execute                                                                                                                                                                                                           | Write<br>registers<br>PRODH:<br>PRODL                                                                          |  |

| Example:                                                  | MULLW                                                                                                                              | 0xC4                                                                                                                                                                                      |                                                                                           | Example:                                      | MULWF                                                                                                                       | REG                                                                                                                                                                                                               | 1                                                                                                              |  |

| Before Instru<br>WREG<br>PRODH<br>PRODL<br>After Instruct | = 0><br>= ?<br>= ?                                                                                                                 | κE2                                                                                                                                                                                       |                                                                                           | Before Inst<br>WREG<br>REG<br>PRODI<br>PRODI  | = 0x<br>= 0x<br>H = ?                                                                                                       | (C4<br>(B5                                                                                                                                                                                                        |                                                                                                                |  |

| WREG<br>PRODH<br>PRODL                                    | = 0><br>= 0><br>= 0>                                                                                                               | (C4<br>(AD<br>(08<br>is not avail                                                                                                                                                         | able in the                                                                               | After Instru<br>WREG<br>REG<br>PRODI<br>PRODI | $\begin{array}{rcl} = & 0 \\ = & 0 \\ + & = & 0 \end{array}$                                                                | xC4<br>xB5<br>x8A<br>x94                                                                                                                                                                                          |                                                                                                                |  |

| PIC17                                                     | C42 device                                                                                                                         |                                                                                                                                                                                           |                                                                                           |                                               | instruction<br>17C42 device                                                                                                 |                                                                                                                                                                                                                   | lable in th                                                                                                    |  |

## Applicable Devices 42 R42 42A 43 R43 44

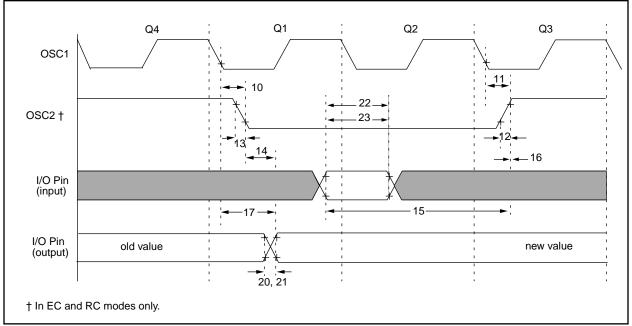

#### FIGURE 17-3: CLKOUT AND I/O TIMING

### TABLE 17-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                 | Min            | Тур† | Max          | Units | Conditions |

|------------------|----------|------------------------------------------------|----------------|------|--------------|-------|------------|

| 10               | TosH2ckL | OSC1↑ to CLKOUT↓                               |                | 15 ‡ | 30 ‡         | ns    | Note 1     |

| 11               | TosH2ckH | OSC1↑ to CLKOUT↑                               | —              | 15‡  | 30 ‡         | ns    | Note 1     |

| 12               | TckR     | CLKOUT rise time                               | —              | 5‡   | 15 ‡         | ns    | Note 1     |

| 13               | TckF     | CLKOUT fall time                               | —              | 5‡   | 15 ‡         | ns    | Note 1     |

| 14               | TckH2ioV | CLKOUT <sup>↑</sup> to Port out valid          | —              | —    | 0.5Tcy + 20‡ | ns    | Note 1     |

| 15               | TioV2ckH | Port in valid before CLKOUT                    | 0.25Tcy + 25 ‡ | —    | —            | ns    | Note 1     |

| 16               | TckH2iol | Port in hold after CLKOUT                      | 0 ‡            | —    | —            | ns    | Note 1     |

| 17               | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid | —              | —    | 100 ‡        | ns    |            |

| 20               | TioR     | Port output rise time                          | —              | 10 ‡ | 35 ‡         | ns    |            |

| 21               | TioF     | Port output fall time                          | —              | 10 ‡ | 35 ‡         | ns    |            |

| 22               | TinHL    | INT pin high or low time                       | 25 *           | _    | —            | ns    |            |

| 23               | TrbHL    | RB7:RB0 change INT high or low time            | 25 *           | —    | —            | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Measurements are taken in EC Mode where OSC2 output = 4 x Tosc = Tcy.

## Applicable Devices 42 R42 42A 43 R43 44

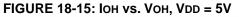

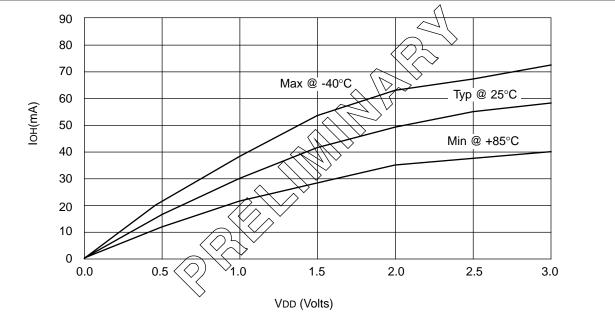

FIGURE 18-16: IOL vs. VOL, VDD = 3V

## Applicable Devices 42 R42 42A 43 R43 44

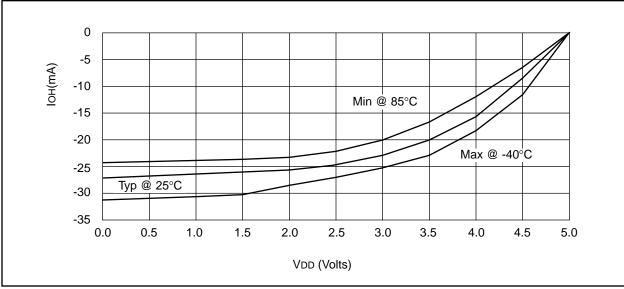

## TABLE 19-11: MEMORY INTERFACE WRITE REQUIREMENTS (NOT SUPPORTED IN PIC17LC4X DEVICES)

| Parameter<br>No. | Sym      | Characteristic                                                 | Min          | Тур†      | Мах | Units | Conditions |

|------------------|----------|----------------------------------------------------------------|--------------|-----------|-----|-------|------------|

| 150              | TadV2alL | AD<15:0> (address) valid to ALE↓<br>(address setup time)       | 0.25Tcy - 10 |           | _   | ns    |            |

| 151              | TalL2adI | ALE↓ to address out invalid<br>(address hold time)             | 0            | _         | —   | ns    |            |

| 152              | TadV2wrL | Data out valid to $\overline{WR} \downarrow$ (data setup time) | 0.25Tcy - 40 | _         | _   | ns    |            |

| 153              | TwrH2adl | WR↑ to data out invalid<br>(data hold time)                    | _            | 0.25Tcy § | _   | ns    |            |

| 154              | TwrL     | WR pulse width                                                 | —            | 0.25Tcy § | —   | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

## Applicable Devices 42 R42 42A 43 R43 44

### FIGURE 20-17: IOL vs. VOL, VDD = 5V

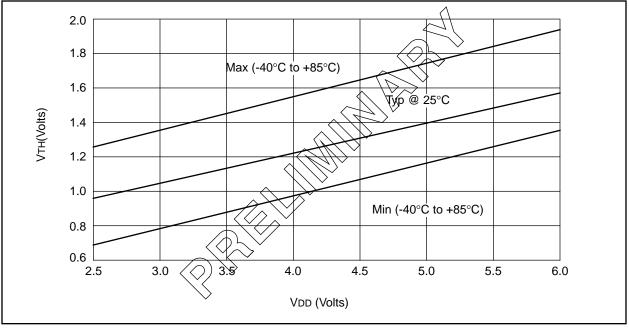

#### FIGURE 20-18: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS (TTL) VS. VDD

NOTES:

#### 21.6 **Package Marking Information** 40-Lead PDIP/CERDIP Example PIC17C43-25I/P L006 AABBCDE 9441CCA MICROCHIP MICROCHIP $\bigcirc$ 40 Lead CERDIP Windowed Example XXXXXXXXXXXX PIC17C44 XXXXXXXXXXXX /JW XXXXXXXXXXXX L184 AABBCDE 9444CCT 44-Lead PLCC Example $\mathcal{M}$ $\mathcal{M}$ MICROCHIP MICROCHIP PIC17C42 XXXXXXXXXX ○ <sub>XXXXXXXXX</sub> Ο -16I/L XXXXXXXXXX L013 AABBCDE 9445CCN 44-Lead MQFP Example $\mathcal{M}$ $\mathbf{w}$ XXXXXXXXXX PIC17C44 -25/PT XXXXXXXXXX XXXXXXXXXXX L247 AABBCDE 9450CAT $\cap$ $\cap$ 44-Lead TQFP Example \$ $\mathcal{Q}$ PIC17C44 XXXXXXXXXX -25/TQ XXXXXXXXXX XXXXXXXXXXX L247 AABBCDE 9450CAT $\cap$ $\cap$ Microchip part number information Legend: MM...M XX...X Customer specific information\* AA Year code (last 2 digits of calendar year) BΒ Week code (week of January 1 is week '01') С Facility code of the plant at which wafer is manufactured C = Chandler, Arizona, U.S.A., S = Tempe, Arizona, U.S.A. D Mask revision number Е Assembly code of the plant or country of origin in which part was assembled Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information. Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond

code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

## **APPENDIX C: WHAT'S NEW**

The structure of the document has been made consistent with other data sheets. This ensures that important topics are covered across all PIC16/17 families. Here is an overview of new features.

Added the following devices:

PIC17CR42

PIC17C42A

PIC17CR43

A 33 MHz option is now available.

## APPENDIX D: WHAT'S CHANGED

To make software more portable across the different PIC16/17 families, the name of several registers and control bits have been changed. This allows control bits that have the same function, to have the same name (regardless of processor family). Care must still be taken, since they may not be at the same special function register address. The following shows the register and bit names that have been changed:

| Old Name | New Name |  |  |

|----------|----------|--|--|

| TX8/9    | TX9      |  |  |

| RC8/9    | RX9      |  |  |

| RCD8     | RX9D     |  |  |

| TXD8     | TX9D     |  |  |

Instruction DECFSNZ corrected to DCFSNZ

Instruction INCFSNZ corrected to INFSNZ

Enhanced discussion on PWM to include equation for determining bits of PWM resolution.

Section 13.2.2 and 13.3.2 have had the description of updating the FERR and RX9 bits enhanced.

The location of configuration bit PM2 was changed (Figure 6-1 and Figure 14-1).

Enhanced description of the operation of the INTSTA register.

Added note to discussion of interrupt operation.

Tightened electrical spec D110.

Corrected steps for setting up USART Asynchronous Reception.

NOTES: