Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 16MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 454 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43t-16e-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

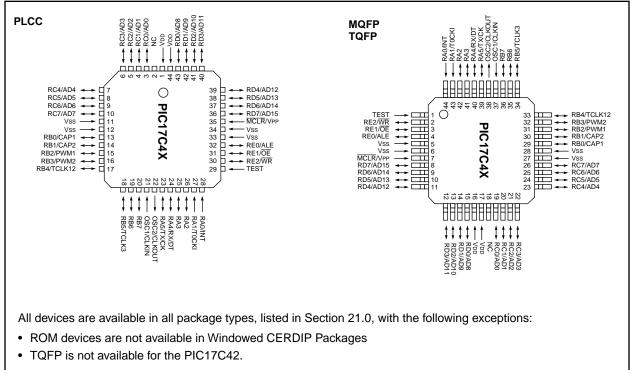

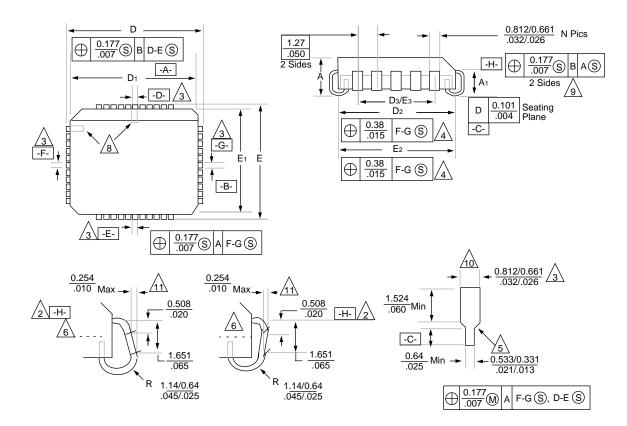

### Pin Diagrams Cont.'d

### 5.1 Interrupt Status Register (INTSTA)

The Interrupt Status/Control register (INTSTA) records the individual interrupt requests in flag bits, and contains the individual interrupt enable bits (not for the peripherals).

The PEIF bit is a read only, bit wise OR of all the peripheral flag bits in the PIR register (Figure 5-4).

Note: T0IF, INTF, T0CKIF, or PEIF will be set by the specified condition, even if the corresponding interrupt enable bit is clear (interrupt disabled) or the GLINTD bit is set (all interrupts disabled).

Care should be taken when clearing any of the INTSTA register enable bits when interrupts are enabled (GLINTD is clear). If any of the INTSTA flag bits (T0IF, INTF, T0CKIF, or PEIF) are set in the same instruction cycle as the corresponding interrupt enable bit is cleared, the device will vector to the reset address (0x00).

When disabling any of the INTSTA enable bits, the GLINTD bit should be set (disabled).

### FIGURE 5-2: INTSTA REGISTER (ADDRESS: 07h, UNBANKED)

| bit $W = V$                                                                                                                                                                                                                                                                                                                | eadable bit<br>/ritable bit<br>/alue at POR reset |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| bit 7: <b>PEIF</b> : Peripheral Interrupt Flag bit<br>This bit is the OR of all peripheral interrupt flag bits AND'ed with their corres<br>1 = A peripheral interrupt is pending                                                                                                                                           | /alue at POR reset                                |

| bit 7: <b>PEIF</b> : Peripheral Interrupt Flag bit<br>This bit is the OR of all peripheral interrupt flag bits AND'ed with their corres<br>1 = A peripheral interrupt is pending                                                                                                                                           |                                                   |

|                                                                                                                                                                                                                                                                                                                            | ponding enable bits.                              |

| <ul> <li>bit 6: TOCKIF: External Interrupt on TOCKI Pin Flag bit</li> <li>This bit is cleared by hardware, when the interrupt logic forces program exercised</li> <li>1 = The software specified edge occurred on the RA1/T0CKI pin</li> <li>0 = The software specified edge did not occur on the RA1/T0CKI pin</li> </ul> | cution to vector (18h).                           |

| bit 5: <b>T0IF</b> : TMR0 Overflow Interrupt Flag bit<br>This bit is cleared by hardware, when the interrupt logic forces program exer<br>1 = TMR0 overflowed<br>0 = TMR0 did not overflow                                                                                                                                 | cution to vector (10h).                           |

| <ul> <li>bit 4: INTF: External Interrupt on INT Pin Flag bit</li> <li>This bit is cleared by hardware, when the interrupt logic forces program exercise</li> <li>1 = The software specified edge occurred on the RA0/INT pin</li> <li>0 = The software specified edge did not occur on the RA0/INT pin</li> </ul>          | cution to vector (08h).                           |

| <ul> <li>bit 3: PEIE: Peripheral Interrupt Enable bit</li> <li>This bit enables all peripheral interrupts that have their corresponding enabl</li> <li>1 = Enable peripheral interrupts</li> <li>0 = Disable peripheral interrupts</li> </ul>                                                                              | e bits set.                                       |

| bit 2: <b>TOCKIE</b> : External Interrupt on TOCKI Pin Enable bit<br>1 = Enable software specified edge interrupt on the RA1/TOCKI pin<br>0 = Disable interrupt on the RA1/TOCKI pin                                                                                                                                       |                                                   |

| bit 1: <b>T0IE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enable TMR0 overflow interrupt<br>0 = Disable TMR0 overflow interrupt                                                                                                                                                                                       |                                                   |

| bit 0: <b>INTE</b> : External Interrupt on RA0/INT Pin Enable bit<br>1 = Enable software specified edge interrupt on the RA0/INT pin<br>0 = Disable software specified edge interrupt on the RA0/INT pin                                                                                                                   |                                                   |

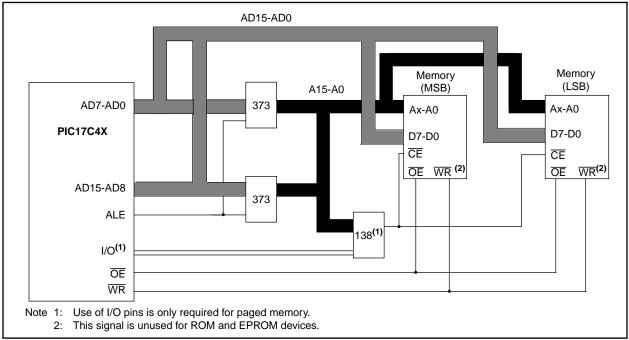

### 6.1.2 EXTERNAL MEMORY INTERFACE

When either microprocessor or extended microcontroller mode is selected, PORTC, PORTD and PORTE are configured as the system bus. PORTC and PORTD are the multiplexed address/data bus and PORTE is for the control signals. External components are needed to demultiplex the address and data. This can be done as shown in Figure 6-4. The waveforms of address and data are shown in Figure 6-3. For complete timings, please refer to the electrical specification section.

### FIGURE 6-3: EXTERNAL PROGRAM MEMORY ACCESS WAVEFORMS

| :      | Q1   Q2   Q3   Q4   | Q1   Q2   Q3   Q4   Q1 |  |  |  |  |  |  |  |

|--------|---------------------|------------------------|--|--|--|--|--|--|--|

| AD     | X                   |                        |  |  |  |  |  |  |  |

| <15:0> | Address out Data in | Address out Data out   |  |  |  |  |  |  |  |

| ALE    |                     |                        |  |  |  |  |  |  |  |

| OE     | '4'                 | · · · ·                |  |  |  |  |  |  |  |

| WR     | '1'                 | <u> </u>               |  |  |  |  |  |  |  |

|        | Read cycle          | Write cycle            |  |  |  |  |  |  |  |

|        |                     | , white cycle          |  |  |  |  |  |  |  |

The system bus requires that there is no bus conflict (minimal leakage), so the output value (address) will be capacitively held at the desired value.

As the speed of the processor increases, external EPROM memory with faster access time must be used. Table 6-2 lists external memory speed requirements for a given PIC17C4X device frequency.

In extended microcontroller mode, when the device is executing out of internal memory, the control signals will continue to be active. That is, they indicate the action that is occurring in the internal memory. The external memory access is ignored.

This following selection is for use with Microchip EPROMs. For interfacing to other manufacturers memory, please refer to the electrical specifications of the desired PIC17C4X device, as well as the desired memory device to ensure compatibility.

| TABLE 6-2: | EPROM MEMORY ACCESS  |

|------------|----------------------|

|            | TIME ORDERING SUFFIX |

| PIC17C4X                | Instruction         | EPRON    | OM Suffix            |  |  |

|-------------------------|---------------------|----------|----------------------|--|--|

| Oscillator<br>Frequency | Cycle<br>Time (Tcy) | PIC17C42 | PIC17C43<br>PIC17C44 |  |  |

| 8 MHz                   | 500 ns              | -25      | -25                  |  |  |

| 16 MHz                  | 250 ns              | -12      | -15                  |  |  |

| 20 MHz                  | 200 ns              | -90      | -10                  |  |  |

| 25 MHz                  | 160 ns              | N.A.     | -70                  |  |  |

| 33 MHz                  | 121 ns              | N.A.     | (1)                  |  |  |

Note 1: The access times for this requires the use of fast SRAMS.

**Note:** The external memory interface is not supported for the LC devices.

FIGURE 6-4: TYPICAL EXTERNAL PROGRAM MEMORY CONNECTION DIAGRAM

© 1996 Microchip Technology Inc.

| Address            | Name                                                                                                                                           | Bit 7     | Bit 6         | Bit 5          | Bit 4        | Bit 3          | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|----------------|--------------|----------------|--------|--------|--------|-------------------------------|-------------------------------------|

| Bank 2             | Bank 2                                                                                                                                         |           |               |                |              |                |        |        |        |                               |                                     |

| 10h                | TMR1                                                                                                                                           | Timer1    |               |                |              |                |        |        |        | xxxx xxxx                     | uuuu uuuu                           |

| 11h                | TMR2                                                                                                                                           | Timer2    |               |                |              |                |        |        |        | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | TMR3L                                                                                                                                          | TMR3 reg  | ister; low b  | yte            |              |                |        |        |        | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | TMR3H                                                                                                                                          | TMR3 reg  | ister; high l | oyte           |              |                |        |        |        | xxxx xxxx                     | uuuu uuuu                           |

| 14h                | PR1                                                                                                                                            | Timer1 pe | eriod registe | er             |              |                |        |        |        | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | PR2                                                                                                                                            | Timer2 pe | eriod registe | er             |              |                |        |        |        | xxxx xxxx                     | uuuu uuuu                           |

| 16h                | PR3L/CA1L                                                                                                                                      | Timer3 pe | eriod registe | er, low byte/c | apture1 regi | ster; low by   | te     |        |        | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | PR3H/CA1H                                                                                                                                      | Timer3 pe | eriod registe | er, high byte/ | capture1 reg | jister; high b | oyte   |        |        | xxxx xxxx                     | uuuu uuuu                           |

| Bank 3             |                                                                                                                                                |           |               |                |              |                |        |        |        |                               |                                     |

| 10h                | PW1DCL                                                                                                                                         | DC1       | DC0           | —              | —            | —              | —      | _      | —      | xx                            | uu                                  |

| 11h                | PW2DCL                                                                                                                                         | DC1       | DC0           | TM2PW2         | _            | —              | —      | _      | _      | xx0                           | uu0                                 |

| 12h                | PW1DCH                                                                                                                                         | DC9       | DC8           | DC7            | DC6          | DC5            | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | PW2DCH                                                                                                                                         | DC9       | DC8           | DC7            | DC6          | DC5            | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                           |

| 14h                | CA2L                                                                                                                                           | Capture2  | low byte      |                |              |                |        |        |        | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | CA2H                                                                                                                                           | Capture2  | high byte     |                |              |                |        |        |        | xxxx xxxx                     | uuuu uuuu                           |

| 16h                | TCON1                                                                                                                                          | CA2ED1    | CA2ED0        | CA1ED1         | CA1ED0       | T16            | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                           |

| 17h                | TCON2                                                                                                                                          | CA2OVF    | CA10VF        | PWM2ON         | PWM10N       | CA1/PR3        | TMR3ON | TMR2ON | TMR10N | 0000 0000                     | 0000 0000                           |

| Unbanke            | ed                                                                                                                                             |           |               |                |              |                |        |        |        |                               |                                     |

| 18h <sup>(5)</sup> | PRODL                                                                                                                                          | Low Byte  | of 16-bit Pr  | oduct (8 x 8   | Hardware M   | lultiply)      |        |        |        | XXXX XXXX                     | uuuu uuuu                           |

| 19h <sup>(5)</sup> | PRODH                                                                                                                                          | High Byte | of 16-bit P   | roduct (8 x 8  | B Hardware N | /lultiply)     |        |        |        | xxxx xxxx                     | uuuu uuuu                           |

| Legend:            | egend: x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. |           |               |                |              |                |        |        |        |                               |                                     |

#### **TABLE 6-3**: SPECIAL FUNCTION REGISTERS (Cont.'d)

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated from or transferred to the upper byte of the program counter. The TO and PD status bits in CPUSTA are not affected by a MCLR reset. Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset. The following values are for both TBLPTRL and TBLPTRH:

2:

3: 4:

All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000) except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu) The PRODL and PRODH registers are not implemented on the PIC17C42.

5:

### 6.2.2.3 TMR0 STATUS/CONTROL REGISTER (T0STA)

This register contains various control bits. Bit7 (INTEDG) is used to control the edge upon which a signal on the RA0/INT pin will set the RB0/INT interrupt flag. The other bits configure the Timer0 prescaler and clock source. (Figure 11-1).

### FIGURE 6-9: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

| R/W - 0        | R/W - 0                                                                                                                                                      | R/W - 0                                          | R/W - 0                                                            | R/W - 0                    | R/W - 0                  | R/W - 0     | U - 0 |                                                                                                       |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------|----------------------------|--------------------------|-------------|-------|-------------------------------------------------------------------------------------------------------|--|

| INTEDG<br>bit7 | TOSE                                                                                                                                                         | TOCS                                             | PS3                                                                | PS2                        | PS1                      | PS0         | bit0  | R = Readable bit<br>W = Writable bit<br>U = Unimplemented,<br>reads as '0'<br>-n = Value at POR reset |  |

| bit 7:         | INTEDG: R<br>This bit sele<br>1 = Rising e<br>0 = Falling e                                                                                                  | ects the ed<br>edge of RA                        | ge upon w<br>0/INT pin g                                           | hich the in<br>generates i | terrupt is d<br>nterrupt | etected.    |       |                                                                                                       |  |

| bit 6:         |                                                                                                                                                              | ects the ed<br>S = 0<br>edge of RA<br>edge of RA | ge upon w<br>1/T0CKI pi                                            | hich TMRC                  | nts TMR0 a               | and/or gene |       | CKIF interrupt<br>CKIF interrupt                                                                      |  |

| bit 5:         | <b>TOCS</b> : Timer0 Clock Source Select bit<br>This bit selects the clock source for Timer0.<br>1 = Internal instruction clock cycle (TcY)<br>0 = T0CKI pin |                                                  |                                                                    |                            |                          |             |       |                                                                                                       |  |

| bit 4-1:       | PS3:PS0: 7<br>These bits                                                                                                                                     |                                                  |                                                                    |                            | ner0.                    |             |       |                                                                                                       |  |

|                | PS3:PS0                                                                                                                                                      | Pre                                              | scale Valu                                                         | е                          |                          |             |       |                                                                                                       |  |

|                | 0000<br>001<br>0010<br>010<br>0100<br>0101<br>0110<br>0111<br>1xxx                                                                                           |                                                  | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 |                            |                          |             |       |                                                                                                       |  |

| bit 0:         | Unimplem                                                                                                                                                     | <b>ented</b> : Rea                               | id as '0'                                                          |                            |                          |             |       |                                                                                                       |  |

Example 8-4 shows the sequence to do an 16 x 16 signed multiply. Equation 8-2 shows the algorithm that used. The 32-bit result is stored in four registers RES3:RES0. To account for the sign bits of the arguments, each argument pairs most significant bit (MSb) is tested and the appropriate subtractions are done.

| EQUATION 8-2: | 16 x 16 SIGNED |

|---------------|----------------|

|               | MULTIPLICATION |

|               | ALGORITHM      |

RES3:RES0

- = ARG1H:ARG1L \* ARG2H:ARG2L

- - (-1 \* ARG1H<7> \* ARG2H:ARG2L \* 2<sup>16</sup>)

## EXAMPLE 8-4: 16 x 16 SIGNED MULTIPLY

|     | ROUTINE  |             |   |                  |  |  |  |  |  |  |

|-----|----------|-------------|---|------------------|--|--|--|--|--|--|

|     | MOVFP    | ARG1L, WREG |   |                  |  |  |  |  |  |  |

|     | MULWF    | ARG2L       | ; | ARG1L * ARG2L -> |  |  |  |  |  |  |

|     |          |             |   | PRODH:PRODL      |  |  |  |  |  |  |

|     | MOVPF    | PRODH, RES1 |   |                  |  |  |  |  |  |  |

|     |          | PRODL, RESO |   |                  |  |  |  |  |  |  |

| ;   |          | - ,         |   |                  |  |  |  |  |  |  |

|     | MOVFP    | ARG1H, WREG |   |                  |  |  |  |  |  |  |

|     |          |             |   | ARG1H * ARG2H -> |  |  |  |  |  |  |

|     | 110201   | into bii    | ; |                  |  |  |  |  |  |  |

|     | MOVPF    | PRODH, RES3 |   | TRODUCTRODE      |  |  |  |  |  |  |

|     |          | PRODL, RES2 |   |                  |  |  |  |  |  |  |

| ;   | 110 11 1 | TRODE, REDZ | ' |                  |  |  |  |  |  |  |

| '   | MOVFP    | ARG1L, WREG |   |                  |  |  |  |  |  |  |

|     |          |             |   | ARG1L * ARG2H -> |  |  |  |  |  |  |

|     | HOLMI    | 111(0211    | ; |                  |  |  |  |  |  |  |

|     | MOVFP    | PRODL, WREG |   | TRODITITRODE     |  |  |  |  |  |  |

|     |          |             |   | Add cross        |  |  |  |  |  |  |

|     |          |             |   |                  |  |  |  |  |  |  |

|     |          |             | ; | products         |  |  |  |  |  |  |

|     |          |             |   |                  |  |  |  |  |  |  |

|     |          | WREG, F     | ; |                  |  |  |  |  |  |  |

|     | ADDWFC   | RES3, F     | ; |                  |  |  |  |  |  |  |

| ;   | NOTED    |             |   |                  |  |  |  |  |  |  |

|     |          | ARG1H, WREG | ' | 100111 + 10001   |  |  |  |  |  |  |

|     | MULWF    | ARG2L       |   | ARG1H * ARG2L -> |  |  |  |  |  |  |

|     |          |             | , | PRODH:PRODL      |  |  |  |  |  |  |

|     | MOMED    |             |   |                  |  |  |  |  |  |  |

|     |          | PRODL, WREG |   | Add among        |  |  |  |  |  |  |

|     | ADDWF    | RES1, F     |   |                  |  |  |  |  |  |  |

|     |          | PRODH, WREG |   | products         |  |  |  |  |  |  |

|     |          |             | ; |                  |  |  |  |  |  |  |

|     | CLRF     | WREG, F     | ; |                  |  |  |  |  |  |  |

|     | ADDWFC   | RES3, F     | ; |                  |  |  |  |  |  |  |

| ;   |          |             |   |                  |  |  |  |  |  |  |

|     |          | ARG2H, 7    | ' | ARG2H:ARG2L neg? |  |  |  |  |  |  |

|     |          |             |   | no, check ARG1   |  |  |  |  |  |  |

|     | MOVFP    | ARG1L, WREG |   |                  |  |  |  |  |  |  |

|     |          | RES2        | ; |                  |  |  |  |  |  |  |

|     | MOVFP    | ARG1H, WREG | ; |                  |  |  |  |  |  |  |

|     | SUBWFB   | RES3        |   |                  |  |  |  |  |  |  |

| ;   |          |             |   |                  |  |  |  |  |  |  |

| SIC | GN_ARG1  |             |   |                  |  |  |  |  |  |  |

|     |          |             |   | ARG1H:ARG1L neg? |  |  |  |  |  |  |

|     | GOTO     | CONT_CODE   |   | no, done         |  |  |  |  |  |  |

|     |          | ARG2L, WREG |   |                  |  |  |  |  |  |  |

|     | SUBWF    | RES2        | ; |                  |  |  |  |  |  |  |

|     | MOVFP    | ARG2H, WREG | ; |                  |  |  |  |  |  |  |

|     | SUBWFB   | RES3        |   |                  |  |  |  |  |  |  |

| ;   |          |             |   |                  |  |  |  |  |  |  |

| COI | NT_CODE  |             |   |                  |  |  |  |  |  |  |

|     | :        |             |   |                  |  |  |  |  |  |  |

### 12.0 TIMER1, TIMER2, TIMER3, PWMS AND CAPTURES

The PIC17C4X has a wealth of timers and time-based functions to ease the implementation of control applications. These time-base functions include two PWM outputs and two Capture inputs.

Timer1 and Timer2 are two 8-bit incrementing timers, each with a period register (PR1 and PR2 respectively) and separate overflow interrupt flags. Timer1 and Timer2 can operate either as timers (increment on internal Fosc/4 clock) or as counters (increment on falling edge of external clock on pin RB4/TCLK12). They are also software configurable to operate as a single 16-bit timer. These timers are also used as the time-base for the PWM (pulse width modulation) module. Timer3 is a 16-bit timer/counter consisting of the TMR3H and TMR3L registers. This timer has four other associated registers. Two registers are used as a 16-bit period register or a 16-bit Capture1 register (PR3H/CA1H:PR3L/CA1L). The other two registers are strictly the Capture2 registers (CA2H:CA2L). Timer3 is the time-base for the two 16-bit captures.

TMR3 can be software configured to increment from the internal system clock or from an external signal on the RB5/TCLK3 pin.

Figure 12-1 and Figure 12-2 are the control registers for the operation of Timer1, Timer2, and Timer3, as well as PWM1, PWM2, Capture1, and Capture2.

### FIGURE 12-1: TCON1 REGISTER (ADDRESS: 16h, BANK 3)

| bit7     | I CA2ED0 CA1ED1 CA1ED0 T16 TMR3CS TMR2CS TMR1CS bit0                                                                                                                                                           | R = Readable bit<br>W = Writable bit<br>-n = Value at POR reset |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| bit 7-6: | <b>CA2ED1:CA2ED0</b> : Capture2 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge |                                                                 |

| bit 5-4: | <b>CA1ED1:CA1ED0</b> : Capture1 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge |                                                                 |

| bit 3:   | <b>T16</b> : Timer1:Timer2 Mode Select bit<br>1 = Timer1 and Timer2 form a 16-bit timer<br>0 = Timer1 and Timer2 are two 8-bit timers                                                                          |                                                                 |

| bit 2:   | <b>TMR3CS</b> : Timer3 Clock Source Select bit<br>1 = TMR3 increments off the falling edge of the RB5/TCLK3 pin<br>0 = TMR3 increments off the internal clock                                                  |                                                                 |

| bit 1:   | <b>TMR2CS</b> : Timer2 Clock Source Select bit<br>1 = TMR2 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR2 increments off the internal clock                                                 |                                                                 |

| bit 0:   | <b>TMR1CS</b> : Timer1 Clock Source Select bit<br>1 = TMR1 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR1 increments off the internal clock                                                 |                                                                 |

### FIGURE 13-2: RCSTA REGISTER (ADDRESS: 13h, BANK 0)

| SPEN   | N.W0         R/W - 0         R/W - 0         U - 0         R - 0         R - 0         R - x           RX9         SREN         CREN         —         FERR         OERR         RX9D         R = Readable bit                                                                                                                                             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit7   | bit 0<br>W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)                                                                                                                                                                                                                                                                                      |

| bit 7: | <b>SPEN</b> : Serial Port Enable bit<br>1 = Configures RA5/RX/DT and RA4/TX/CK pins as serial port pins<br>0 = Serial port disabled                                                                                                                                                                                                                        |

| bit 6: | <b>RX9</b> : 9-bit Receive Enable bit<br>1 = Selects 9-bit reception<br>0 = Selects 8-bit reception                                                                                                                                                                                                                                                        |

| bit 5: | SREN: Single Receive Enable bit         This bit enables the reception of a single byte. After receiving the byte, this bit is automatically cleared.         Synchronous mode:         1 = Enable reception         0 = Disable reception         Note: This bit is ignored in synchronous slave reception.         Asynchronous mode:         Don't care |

| bit 4: | CREN: Continuous Receive Enable bit<br>This bit enables the continuous reception of serial data.<br><u>Asynchronous mode:</u><br>1 = Enable reception<br>0 = Disables reception<br><u>Synchronous mode:</u><br>1 = Enables continuous reception until CREN is cleared (CREN overrides SREN)<br>0 = Disables continuous reception                           |

| bit 3: | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                 |

| bit 2: | FERR: Framing Error bit<br>1 = Framing error (Updated by reading RCREG)<br>0 = No framing error                                                                                                                                                                                                                                                            |

| bit 1: | OERR: Overrun Error bit<br>1 = Overrun (Cleared by clearing CREN)<br>0 = No overrun error                                                                                                                                                                                                                                                                  |

| bit 0: | <b>RX9D</b> : 9th bit of receive data (can be the software calculated parity bit)                                                                                                                                                                                                                                                                          |

| CPFSEQ                                                                                                            | Compare f with WREG,<br>skip if f = WREG                                                                                                                                                                                                                           |          | CPF        | SGT    | -                                             | Compare f with WREG,<br>skip if f > WREG                                               |                                                                                          |               |  |  |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|--------|-----------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------|--|--|

| Syntax:                                                                                                           | [label] CPFSEQ f                                                                                                                                                                                                                                                   |          |            | Syn    | tax:                                          | [label]                                                                                | [label] CPFSGT f                                                                         |               |  |  |

| Operands:                                                                                                         | $0 \le f \le 255$                                                                                                                                                                                                                                                  | 5        |            | Ope    | rands:                                        | $0 \le f \le 255$                                                                      | 5                                                                                        |               |  |  |

| Operation:                                                                                                        | (f) – (WREG),<br>skip if (f) = (WREG)<br>(unsigned comparison)                                                                                                                                                                                                     |          |            | Ope    | ration:                                       | skip if (f) >                                                                          | (f) – (WREG),<br>skip if (f) > (WREG)<br>(unsigned comparison)                           |               |  |  |

| Status Affected:                                                                                                  | None                                                                                                                                                                                                                                                               |          |            | Stat   | us Affected:                                  | None                                                                                   |                                                                                          |               |  |  |

| Encoding:                                                                                                         | 0011                                                                                                                                                                                                                                                               | 0001 fff | f ffff     | Enc    | oding:                                        | 0011                                                                                   | 0010 ff:                                                                                 | ff ffff       |  |  |

| Description:                                                                                                      | Compares the contents of data memory<br>location 'f' to the contents of WREG by<br>performing an unsigned subtraction.<br>If 'f' = WREG then the fetched instruc-<br>tion is discarded and an NOP is exe-<br>cuted instead making this a two-cycle<br>instruction. |          |            |        | cription:                                     | location 'f' t<br>by performi<br>If the conte<br>WREG the<br>discarded a<br>instead ma | o the contents<br>ng an unsigne<br>nts of 'f' > the<br>n the fetched in<br>and an NOP is | nstruction is |  |  |

| Words:                                                                                                            | 1                                                                                                                                                                                                                                                                  |          |            | 14/0 - | de .                                          | tion.<br>1                                                                             |                                                                                          |               |  |  |

| Cycles:                                                                                                           | 1 (2)                                                                                                                                                                                                                                                              |          |            | Wor    |                                               | -                                                                                      |                                                                                          |               |  |  |

| Q Cycle Activity:                                                                                                 |                                                                                                                                                                                                                                                                    |          |            | Cyc    |                                               | 1 (2)                                                                                  |                                                                                          |               |  |  |

| Q1                                                                                                                | Q2                                                                                                                                                                                                                                                                 | Q3       | Q4         | QC     | ycle Activity:<br>Q1                          | Q2                                                                                     | Q3                                                                                       | Q4            |  |  |

| Decode                                                                                                            | Read<br>register 'f'                                                                                                                                                                                                                                               | Execute  | NOP        |        | Decode                                        | Read                                                                                   | Execute                                                                                  | NOP           |  |  |

| If skip:                                                                                                          |                                                                                                                                                                                                                                                                    |          |            | lf sk  | in:                                           | register 'f'                                                                           |                                                                                          |               |  |  |

| Q1                                                                                                                | Q2                                                                                                                                                                                                                                                                 | Q3       | Q4         |        | Q1                                            | Q2                                                                                     | Q3                                                                                       | Q4            |  |  |

| Forced NOP                                                                                                        | NOP                                                                                                                                                                                                                                                                | Execute  | NOP        |        | Forced NOP                                    | NOP                                                                                    | Execute                                                                                  | NOP           |  |  |

| Example: HERE CPFSEQ REG<br>NEQUAL :<br>EQUAL :                                                                   |                                                                                                                                                                                                                                                                    |          | <u>Exa</u> | mple:  | HERE<br>NGREATER<br>GREATER                   | CPFSGT RE<br>:<br>:                                                                    | G                                                                                        |               |  |  |

| Before Instru<br>PC Addre                                                                                         | Before Instruction                                                                                                                                                                                                                                                 |          |            |        | Before Instru                                 | -                                                                                      | ·                                                                                        |               |  |  |

| WREG<br>REG                                                                                                       | ess = HE<br>= ?<br>= ?                                                                                                                                                                                                                                             | RE       |            |        | PC<br>WREG                                    |                                                                                        | dress (HERE)                                                                             |               |  |  |

| REG = ?<br>After Instruction<br>If REG = WREG;<br>PC = Address (EQUAL)<br>If REG ≠ WREG;<br>PC = Address (NEQUAL) |                                                                                                                                                                                                                                                                    |          |            |        | After Instruc<br>If REG<br>PC<br>If REG<br>PC | > Wi<br>= Ad<br>≤ Wi                                                                   | REG;<br>Idress (GREAT<br>REG;<br>Idress (NGREZ                                           |               |  |  |

## PIC17C4X

| DECF              | Decreme                  | nt f               |                      | DECFSZ          | Decrement f, s                                                    | skip if 0       |          |

|-------------------|--------------------------|--------------------|----------------------|-----------------|-------------------------------------------------------------------|-----------------|----------|

| Syntax:           | [label]                  | DECF f,d           |                      | Syntax:         | [label] DECF                                                      | SZ f,d          |          |

| Operands:         | 0 ≤ f ≤ 255<br>d ∈ [0,1] | 5                  |                      | Operands:       | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |                 |          |

| Operation:        | $(f) - 1 \rightarrow ($  | (dest)             |                      | Operation:      | (f) – 1 $\rightarrow$ (dest)                                      | );              |          |

| Status Affected:  | OV, C, DC                | ;, Z               |                      |                 | skip if result = 0                                                | 0               |          |

| Encoding:         | 0000                     | 011d ff            | ff ffff              | Status Affected | : None                                                            |                 |          |

| Description:      | Decrement                | register 'f'. If ' | d' is 0 the          | Encoding:       | 0001 0110                                                         | d ffff          | ffff     |

|                   |                          | ored in WREG       |                      | Description:    | The contents of r<br>mented. If 'd' is 0                          | the result is p | laced in |

| Words:            | 1                        |                    |                      |                 | WREG. If 'd' is 1<br>back in register 'f                          | •               | laced    |

| Cycles:           | 1                        |                    |                      |                 | If the result is 0, 1                                             |                 | iction.  |

| Q Cycle Activity: |                          |                    |                      |                 | which is already                                                  | fetched, is dis | carded,  |

| Q1                | Q2                       | Q3                 | Q4                   |                 | and an NOP is ex<br>ing it a two-cycle                            |                 | ad mak-  |

| Decode            | Read<br>register 'f'     | Execute            | Write to destination | Words:          | 1                                                                 |                 |          |

| Example:          | DECF                     | CNT, 1             |                      | Cycles:         | 1(2)                                                              |                 |          |

| Before Instru     |                          | - ,                |                      | Q Cycle Activit | y:                                                                |                 |          |

| CNT               | = 0x01                   |                    |                      | Q1              | Q2                                                                | Q3              | Q4       |

| Z                 | = 0                      |                    |                      | Decode          |                                                                   |                 | rite to  |

| After Instruc     | tion                     |                    |                      |                 | register 'f'                                                      | des             | tination |

| CNT               | = 0x00                   |                    |                      | Example:        |                                                                   | CFSZ CNT,       |          |

| Z                 | = 1                      |                    |                      |                 | GO1<br>CONTINUE                                                   | TO LOOP         | 2        |

|                   |                          |                    |                      | Defers inc      |                                                                   |                 |          |

|                   |                          |                    |                      | Before Ins      | liucuon                                                           |                 |          |

| PC             | =   | Address (HERE)     |

|----------------|-----|--------------------|

| After Instruct | ion |                    |

| CNT            | =   | CNT - 1            |

| If CNT         | =   | 0;                 |

| PC             | =   | Address (CONTINUE) |

| If CNT         | ≠   | 0;                 |

| PC             | =   | Address (HERE+1)   |

# PIC17C4X

| TLWT              | Table Late                      | ch Write                           |                     | TSTFSZ                    | Test f, sk            | ip if 0                        |             |   |  |

|-------------------|---------------------------------|------------------------------------|---------------------|---------------------------|-----------------------|--------------------------------|-------------|---|--|

| Syntax:           | [label] T                       | LWT t,f                            |                     | Syntax:                   | [ label ]             | TSTFSZ f                       |             |   |  |

| Operands:         | 0 ≤ f ≤ 255                     | $0 \le f \le 255$                  |                     |                           |                       | Operands:                      | 0 ≤ f ≤ 25  | 5 |  |

|                   | t ∈ [0,1]                       |                                    |                     | Operation:                | skip if f =           | 0                              |             |   |  |

| Operation:        | If $t = 0$ ,                    |                                    |                     | Status Affected:          | None                  |                                |             |   |  |

|                   | $f \rightarrow TB$<br>If t = 1, | LAIL;                              |                     | Encoding:                 | 0011                  | 0011 fff                       | f ffff      |   |  |

|                   | $f \rightarrow TB$              | LATH                               |                     | Description:              | If 'f' = 0, the       | e next instructio              | on, fetched |   |  |

| Status Affected:  | None                            |                                    |                     | ·                         |                       | current instructi              |             |   |  |

| Encoding:         | 1010                            | 01tx ff:                           | ff ffff             |                           |                       | d and an NOP<br>a two-cycle in |             |   |  |

| Description:      | Data from fi                    | ile register 'f' i                 | s written into      | Words:                    | 1                     | ·                              |             |   |  |

| ·                 |                                 | able latch (TBI                    |                     | Cycles:                   | 1 (2)                 |                                |             |   |  |

|                   | -                               | byte is writte                     |                     | Q Cycle Activity:         | ( )                   |                                |             |   |  |

|                   |                                 | byte is written<br>tion is used in |                     | Q1                        | Q2                    | Q3                             | Q4          |   |  |

|                   |                                 |                                    | lata from data      | Decode                    | Read                  | Execute                        | NOP         |   |  |

|                   | memory to                       | program mem                        | iory.               |                           | register 'f'          |                                |             |   |  |

| Words:            | 1                               |                                    |                     | If skip:                  | 00                    | 02                             | 04          |   |  |

| Cycles:           | 1                               |                                    |                     | Q1<br>Forced NOP          | Q2<br>NOP             | Q3<br>Execute                  | Q4<br>NOP   |   |  |

| Q Cycle Activity: |                                 |                                    |                     |                           |                       |                                | NOI         |   |  |

| Q1                | Q2                              | Q3                                 | Q4                  | Example:                  | HERE<br>NZERO         | TSTFSZ CNT<br>:                |             |   |  |

| Decode            | Read<br>register 'f'            | Execute                            | Write<br>register   |                           | ZERO :                | -                              |             |   |  |

|                   | regioner 1                      |                                    | TBLATH or<br>TBLATL | Before Instru<br>PC = Ado | lction<br>dress(HERE) |                                |             |   |  |

| Example:          | TLWT t                          | :, RAM                             |                     | After Instruct            | tion                  |                                |             |   |  |

| Before Instru     |                                 |                                    |                     | If CNT                    |                       | .00,                           |             |   |  |

| t                 | = 0                             |                                    |                     | PC<br>If CNT              |                       | dress (ZERO)<br>00,            |             |   |  |

| RAM<br>TBLAT      | = 0xB7<br>= 0x0000              | (TBLATH =                          | 0×00)               | PC                        | = Ac                  | dress (NZERO                   | )           |   |  |

| IDEAI             | - 000000                        | (TBLATL =                          |                     |                           |                       |                                |             |   |  |

| After Instruct    | tion                            |                                    |                     |                           |                       |                                |             |   |  |

| RAM               | = 0xB7                          |                                    |                     |                           |                       |                                |             |   |  |

| TBLAT             | = 0x00B7                        | (TBLATH =<br>(TBLATL =             | ,                   |                           |                       |                                |             |   |  |

| Before Instru     |                                 |                                    |                     |                           |                       |                                |             |   |  |

| t<br>RAM          | = 1<br>= 0xB7                   |                                    |                     |                           |                       |                                |             |   |  |

| TBLAT             | = 0x0000                        | (TBLATH =<br>(TBLATL =             | ,                   |                           |                       |                                |             |   |  |

| After Instruct    | tion                            |                                    |                     |                           |                       |                                |             |   |  |

| RAM               | = 0xB7                          |                                    |                     |                           |                       |                                |             |   |  |

| TBLAT             | = 0xB700                        | ``                                 | ,                   |                           |                       |                                |             |   |  |

|                   |                                 | (TBLATL =                          | UXUU)               |                           |                       |                                |             |   |  |

MPASM allow full symbolic debugging from the Microchip Universal Emulator System (PICMASTER).

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

### 16.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

### 16.12 C Compiler (MPLAB-C)

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of micro-controllers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display (PICMASTER emulator software versions 1.13 and later).

### 16.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

### 16.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

### 16.15 <u>SEEVAL® Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 16.16 <u>TrueGauge<sup>®</sup> Intelligent Battery</u> <u>Management</u>

The TrueGauge development tool supports system development with the MTA11200B TrueGauge Intelligent Battery Management IC. System design verification can be accomplished before hardware prototypes are built. User interface is graphically-oriented and measured data can be saved in a file for exporting to Microsoft Excel.

### 16.17 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters. NOTES:

### Applicable Devices 42 R42 42A 43 R43 44

#### 19.2 **DC CHARACTERISTICS:**

### PIC17LC42A/43/LC44 (Commercial, Industrial) PIC17LCR42/43 (Commercial, Industrial)

| DC CHARA         | CTERIS | STICS                                                            | Standard<br>Operating |      | •    |       | s (unless otherwise stated)<br>$\leq TA \leq +85^{\circ}C$ for industrial and<br>$\leq TA \leq +70^{\circ}C$ for commercial |

|------------------|--------|------------------------------------------------------------------|-----------------------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------|

| Parameter<br>No. | Sym    | Characteristic                                                   | Min                   | Тур† | Мах  | Units | Conditions                                                                                                                  |

| D001             | Vdd    | Supply Voltage                                                   | 2.5                   | _    | 6.0  | V     |                                                                                                                             |

| D002             | Vdr    | RAM Data Retention<br>Voltage (Note 1)                           | 1.5 *                 | -    | Ι    | V     | Device in SLEEP mode                                                                                                        |

| D003             | VPOR   | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | _                     | Vss  | _    | V     | See section on Power-on Reset for details                                                                                   |

| D004             | SVDD   | VDD rise rate to<br>ensure internal<br>Power-on Reset signal     | 0.060 *               | _    | Ι    | mV/ms | See section on Power-on Reset for details                                                                                   |

| D010             | IDD    | Supply Current                                                   | -                     | 3    | 6    | mA    | Fosc = 4 MHz (Note 4)                                                                                                       |

| D011             |        | (Note 2)                                                         | -                     | 6    | 12 * | mA    | Fosc = 8 MHz                                                                                                                |

| D014             |        |                                                                  | -                     | 95   | 150  | μA    | Fosc = 32 kHz,                                                                                                              |

|                  |        |                                                                  |                       |      |      |       | WDT disabled (EC osc configuration)                                                                                         |

| D020             | IPD    | Power-down                                                       | -                     | 10   | 40   | μA    | VDD = 5.5V, WDT enabled                                                                                                     |

| D021             |        | Current (Note 3)                                                 | -                     | < 1  | 5    | μA    | VDD = 5.5V, WDT disabled                                                                                                    |

These parameters are characterized but not tested.

+ Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1=external square wave, from rail to rail; all I/O pins tristated, pulled to VDD or VSS, TOCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

Current consumed from the oscillator and I/O's driving external capacitive or resistive loads needs to be considered.

For the RC oscillator, the current through the external pull-up resistor (R) can be estimated as: VbD / (2 • R). For capacitive loads, the current can be estimated (for an individual I/O pin) as (CL • VDD) • f

CL = Total capacitive load on the I/O pin; f = average frequency the I/O pin switches.

The capacitive currents are most significant when the device is configured for external execution (includes extended microcontroller mode).

- 3: The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IR = VDD/2Rext (mA) with Rext in kOhm.

Standard Operating Conditions (unloss otherwise stated)

### Applicable Devices 42 R42 42A 43 R43 44

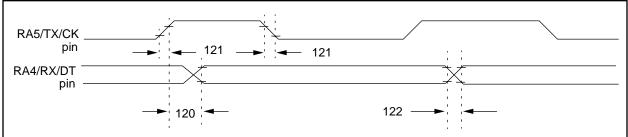

### FIGURE 19-9: USART MODULE: SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 19-9: SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param | C. m       | Characteristic                    |                                    | Min     | Trent  | Max    | Unito   | Conditions  |

|-------|------------|-----------------------------------|------------------------------------|---------|--------|--------|---------|-------------|

| No.   | Sym        | Characteristic                    |                                    | IVIIII  | Тур†   | Max    | Units   | Conditions  |

| 120   | TckH2dtV   | SYNC XMIT (MASTER &               |                                    |         |        |        |         |             |

|       |            | SLAVE)                            | PIC17CR42/42A/43/R43/44            | —       | —      | 50     | ns      |             |

|       |            | Clock high to data out valid      | PIC17LCR42/42A/43/R43/44           | —       | —      | 75     | ns      |             |

| 121   | TckRF      | Clock out rise time and fall time | PIC17CR42/42A/43/R43/44            | —       | —      | 25     | ns      |             |

|       |            | (Master Mode)                     | PIC17LCR42/42A/43/R43/44           | —       | —      | 40     | ns      |             |

| 122   | TdtRF      | Data out rise time and fall time  | PIC17CR42/42A/43/R43/44            | —       | —      | 25     | ns      |             |

|       |            |                                   | PIC17LCR42/42A/43/R43/44           | —       | —      | 40     | ns      |             |

| †     | Data in "T | yp" column is at 5V, 25°C unless  | otherwise stated. These parameters | are for | design | guidan | ce only | and are not |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

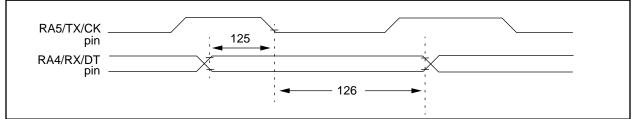

### FIGURE 19-10: USART MODULE: SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### **TABLE 19-10: SYNCHRONOUS RECEIVE REQUIREMENTS**

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data hold before CK↓ (DT hold time) | 15  |      | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                   | 15  | _    | _   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 21.3 44-Lead Plastic Leaded Chip Carrier (Square)

|        | Package Group: Plastic Leaded Chip Carrier (PLCC) |             |           |       |        |           |

|--------|---------------------------------------------------|-------------|-----------|-------|--------|-----------|

|        |                                                   | Millimeters |           |       | Inches |           |

| Symbol | Min                                               | Max         | Notes     | Min   | Max    | Notes     |

| А      | 4.191                                             | 4.572       |           | 0.165 | 0.180  |           |