Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 454 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43t-25i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register  | Address | Power-on Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEF<br>through interrupt |

|-----------|---------|----------------|-------------------------|-----------------------------------------|

| Bank 2    |         | -              |                         | ·                                       |

| TMR1      | 10h     | XXXX XXXX      | սսսս սսսս               | uuuu uuuu                               |

| TMR2      | 11h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| TMR3L     | 12h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| TMR3H     | 13h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR1       | 14h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR2       | 15h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR3/CA1L  | 16h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| PR3/CA1H  | 17h     | XXXX XXXX      | uuuu uuuu               | սսսս սսսս                               |

| Bank 3    |         |                |                         |                                         |

| PW1DCL    | 10h     | xx             | uu                      | uu                                      |

| PW2DCL    | 11h     | xx             | uu                      | uu                                      |

| PW1DCH    | 12h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| PW2DCH    | 13h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| CA2L      | 14h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| CA2H      | 15h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| TCON1     | 16h     | 0000 0000      | 0000 0000               | uuuu uuuu                               |

| TCON2     | 17h     | 0000 0000      | 0000 0000               | uuuu uuuu                               |

| Unbanked  |         |                |                         |                                         |

| PRODL (5) | 18h     | XXXX XXXX      | นนนน นนนน               | นนนน นนนน                               |

| PRODH (5) | 19h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

## TABLE 4-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (Cont.'d)

Legend: u = unchanged, x = unknown, - = unimplemented read as '0', q = value depends on condition. Note 1: One or more bits in INTSTA, PIR will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

3: See Table 4-3 for reset value of specific condition.

4: Only applies to the PIC17C42.

5: Does not apply to the PIC17C42.

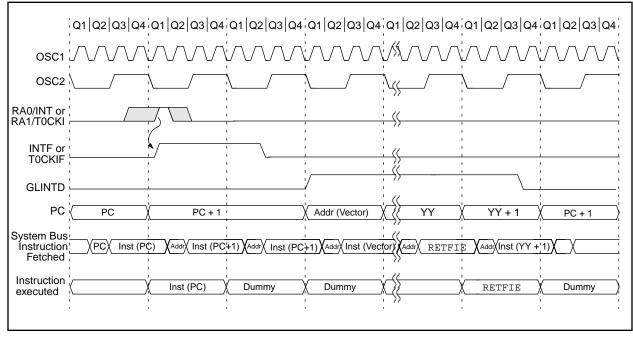

# 5.5 RA0/INT Interrupt

The external interrupt on the RA0/INT pin is edge triggered. Either the rising edge, if INTEDG bit (T0STA<7>) is set, or the falling edge, if INTEDG bit is clear. When a valid edge appears on the RA0/INT pin, the INTF bit (INTSTA<4>) is set. This interrupt can be disabled by clearing the INTE control bit (INTSTA<0>). The INT interrupt can wake the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

# 5.6 TMR0 Interrupt

An overflow (FFFFh  $\rightarrow$  0000h) in TMR0 will set the T0IF (INTSTA<5>) bit. The interrupt can be enabled/ disabled by setting/clearing the T0IE control bit (INTSTA<1>). For operation of the Timer0 module, see Section 11.0.

# 5.7 TOCKI Interrupt

The external interrupt on the RA1/T0CKI pin is edge triggered. Either the rising edge, if the T0SE bit (T0STA<6>) is set, or the falling edge, if the T0SE bit is clear. When a valid edge appears on the RA1/T0CKI pin, the T0CKIF bit (INTSTA<6>) is set. This interrupt can be disabled by clearing the T0CKIE control bit (INTSTA<2>). The T0CKI interrupt can wake up the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

# 5.8 Peripheral Interrupt

The peripheral interrupt flag indicates that at least one of the peripheral interrupts occurred (PEIF is set). The PEIF bit is a read only bit, and is a bit wise OR of all the flag bits in the PIR register AND'ed with the corresponding enable bits in the PIE register. Some of the peripheral interrupts can wake the processor from SLEEP. See Section 14.4 for details on SLEEP operation.

# FIGURE 5-5: INT PIN / TOCKI PIN INTERRUPT TIMING

#### 6.4.1 INDIRECT ADDRESSING REGISTERS

The PIC17C4X has four registers for indirect addressing. These registers are:

- INDF0 and FSR0

- INDF1 and FSR1

Registers INDF0 and INDF1 are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data. The FSR is an 8-bit register and allows addressing anywhere in the 256-byte data memory address range. For banked memory, the bank of memory accessed is specified by the value in the BSR.

If file INDF0 (or INDF1) itself is read indirectly via an FSR, all '0's are read (Zero bit is set). Similarly, if INDF0 (or INDF1) is written to indirectly, the operation will be equivalent to a NOP, and the status bits are not affected.

#### 6.4.2 INDIRECT ADDRESSING OPERATION

The indirect addressing capability has been enhanced over that of the PIC16CXX family. There are two control bits associated with each FSR register. These two bits configure the FSR register to:

- Auto-decrement the value (address) in the FSR after an indirect access

- Auto-increment the value (address) in the FSR after an indirect access

- No change to the value (address) in the FSR after an indirect access

These control bits are located in the ALUSTA register. The FSR1 register is controlled by the FS3:FS2 bits and FSR0 is controlled by the FS1:FS0 bits.

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the ALUSTA register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

If the FSR register contains a value of 0h, an indirect read will read 0h (Zero bit is set) while an indirect write will be equivalent to a NOP (status bits are not affected).

Indirect addressing allows single cycle data transfers within the entire data space. This is possible with the use of the MOVPF and MOVFP instructions, where either 'p' or 'f' is specified as INDF0 (or INDF1).

If the source or destination of the indirect address is in banked memory, the location accessed will be determined by the value in the BSR. A simple program to clear RAM from 20h - FFh is shown in Example 6-1.

## EXAMPLE 6-1: INDIRECT ADDRESSING

|    | MOVLW  | 0x20        | ;           |           |

|----|--------|-------------|-------------|-----------|

|    | MOVWF  | FSR0        | ; FSR0 = 20 | h         |

|    | BCF    | ALUSTA, FS1 | ; Increment | FSR       |

|    | BSF    | ALUSTA, FSO | ; after acc | ess       |

|    | BCF    | ALUSTA, C   | ; C = 0     |           |

|    | MOVLW  | END_RAM + 1 | ;           |           |

| LP | CLRF   | INDF0       | ; Addr(FSR) | = 0       |

|    | CPFSEQ | FSR0        | ; FSRO = EN | ID_RAM+1? |

|    | GOTO   | LP          | ; NO, clear | next      |

|    | :      |             | ; YES, All  | RAM is    |

|    | :      |             | ; cleared   |           |

|    |        |             |             |           |

#### 6.5 <u>Table Pointer (TBLPTRL and</u> <u>TBLPTRH)</u>

File registers TBLPTRL and TBLPTRH form a 16-bit pointer to address the 64K program memory space. The table pointer is used by instructions TABLWT and TABLRD.

The TABLRD and the TABLWT instructions allow transfer of data between program and data space. The table pointer serves as the 16-bit address of the data word within the program memory. For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 7.0.

### 6.6 <u>Table Latch (TBLATH, TBLATL)</u>

The table latch (TBLAT) is a 16-bit register, with TBLATH and TBLATL referring to the high and low bytes of the register. It is not mapped into data or program memory. The table latch is used as a temporary holding latch during data transfer between program and data memory (see descriptions of instructions TABLRD, TABLWT, TLRD and TLWT). For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 7.0.

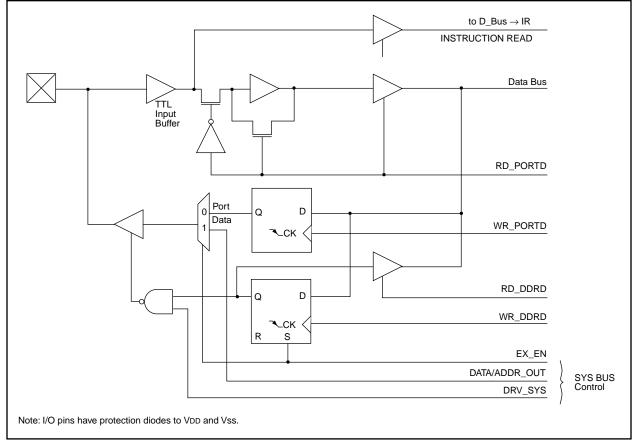

# 9.4 PORTD and DDRD Registers

PORTD is an 8-bit bi-directional port. The corresponding data direction register is DDRD. A '1' in DDRD configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTD reads the status of the pins, whereas writing to it will write to the port latch. PORTD is multiplexed with the system bus. When operating as the system bus, PORTD is the high order byte of the address/data bus (AD15:AD8). The timing for the system bus is shown in the Electrical Characteristics section.

Note: This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-3 shows the instruction sequence to initialize PORTD. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

### EXAMPLE 9-3: INITIALIZING PORTD

| MOVLB | 1     | ; | Select Bank 1            |

|-------|-------|---|--------------------------|

| CLRF  | PORTD | ; | Initialize PORTD data    |

|       |       | ; | latches before setting   |

|       |       | ; | the data direction       |

|       |       | ; | register                 |

| MOVLW | 0xCF  | ; | Value used to initialize |

|       |       | ; | data direction           |

| MOVWF | DDRD  | ; | Set RD<3:0> as inputs    |

|       |       | ; | RD<5:4> as outputs       |

|       |       | ; | RD<7:6> as inputs        |

|       |       |   |                          |

# FIGURE 12-2: TCON2 REGISTER (ADDRESS: 17h, BANK 3)

| R - 0  | R - 0 R/W - 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | F CA10VF PWM20N PWM10N CA1/PR3 TMR30N TMR20N TMR10N R = Readable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit7   | bit0 W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | -n = Value at POR reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 7: | <ul> <li>CA2OVF: Capture2 Overflow Status bit</li> <li>This bit indicates that the capture value had not been read from the capture register pair (CA2H:CA2L)</li> <li>before the next capture event occurred. The capture register retains the oldest unread capture value (last capture before overflow). Subsequent capture events will not update the capture register with the Timer3 value until the capture register has been read (both bytes).</li> <li>1 = Overflow occurred on Capture2 register</li> <li>0 = No overflow occurred on Capture2 register</li> </ul> |

| bit 6: | <b>CA1OVF</b> : Capture1 Overflow Status bit<br>This bit indicates that the capture value had not been read from the capture register pair<br>(PR3H/CA2H:PR3L/CA2L) before the next capture event occurred. The capture register retains the old-<br>est unread capture value (last capture before overflow). Subsequent capture events will not update the<br>capture register with the TMR3 value until the capture register has been read (both bytes).<br>1 = Overflow occurred on Capture1 register<br>0 = No overflow occurred on Capture1 register                     |

| bit 5: | <b>PWM2ON</b> : PWM2 On bit<br>1 = PWM2 is enabled (The RB3/PWM2 pin ignores the state of the DDRB<3> bit)<br>0 = PWM2 is disabled (The RB3/PWM2 pin uses the state of the DDRB<3> bit for data direction)                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4: | <b>PWM1ON</b> : PWM1 On bit<br>1 = PWM1 is enabled (The RB2/PWM1 pin ignores the state of the DDRB<2> bit)<br>0 = PWM1 is disabled (The RB2/PWM1 pin uses the state of the DDRB<2> bit for data direction)                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3: | <b>CA1/PR3</b> : CA1/PR3 Register Mode Select bit<br>1 = Enables Capture1 (PR3H/CA1H:PR3L/CA1L is the Capture1 register. Timer3 runs without<br>a period register)<br>0 = Enables the Period register (PR3H/CA1H:PR3L/CA1L is the Period register for Timer3)                                                                                                                                                                                                                                                                                                                 |

| bit 2: | TMR3ON: Timer3 On bit<br>1 = Starts Timer3<br>0 = Stops Timer3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 1: | <b>TMR2ON</b> : Timer2 On bit<br>This bit controls the incrementing of the Timer2 register. When Timer2:Timer1 form the 16-bit timer (T16<br>is set), TMR2ON must be set. This allows the MSB of the timer to increment.<br>1 = Starts Timer2 (Must be enabled if the T16 bit (TCON1<3>) is set)<br>0 = Stops Timer2                                                                                                                                                                                                                                                          |

| bit 0: | TMR1ON: Timer1 On bit<br><u>When T16 is set (in 16-bit Timer Mode)</u><br>1 = Starts 16-bit Timer2:Timer1<br>0 = Stops 16-bit Timer2:Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | <u>When T16 is clear (in 8-bit Timer Mode)</u><br>1 = Starts 8-bit Timer1<br>0 = Stops 8-bit Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

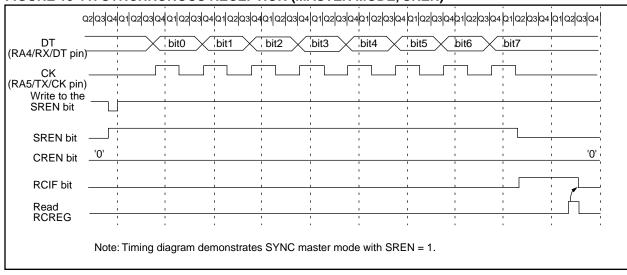

## 13.3 USART Synchronous Master Mode

In Master Synchronous mode, the data is transmitted in a half-duplex manner; i.e. transmission and reception do not occur at the same time: when transmitting data, the reception is inhibited and vice versa. The synchronous mode is entered by setting the SYNC (TXSTA<4>) bit. In addition, the SPEN (RCSTA<7>) bit is set in order to configure the RA5 and RA4 I/O ports to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting the CSRC (TXSTA<7>) bit.

#### 13.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 13-3. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer TXREG. TXREG is loaded with data in software. The TSR is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one TCY at the end of the current BRG cycle), TXREG is empty and the TXIF (PIR<1>) bit is set. This interrupt can be enabled/disabled by setting/clearing the TXIE bit (PIE<1>). TXIF will be set regardless of the state of bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of TXREG, TRMT (TXSTA<1>) shows the status of the TSR. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting the TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the RA5/TX/CK pin. Data out is stable around the falling edge of the synchronous clock (Figure 13-10). The transmission can also be started by first loading TXREG and then setting TXEN. This is advantageous when slow baud rates are selected, since BRG is kept in RESET when the TXEN, CREN, and SREN bits are clear. Setting the TXEN bit will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to the TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The RA4/RX/DT and RA5/TX/CK pins will revert to hi-impedance. If either CREN or SREN are set during a transmission, the transmission is aborted and the

RA4/RX/DT pin reverts to a hi-impedance state (for a reception). The RA5/TX/CK pin will remain an output if the CSRC bit is set (internal clock). The transmitter logic is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear the TXEN bit. If the SREN bit is set (to interrupt an ongoing transmission and receive a single word), then after the single word is received, SREN will be cleared and the serial port will revert back to transmitting, since the TXEN bit is still set. The DT line will immediately switch from hi-impedance receive mode to transmit and start driving. To avoid this, TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty). If the TSR was empty and TXREG was written before writing the "new" TX9D, the "present" value of TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (see Baud Rate Generator Section for details).

- 2. Enable the synchronous master serial port by setting the SYNC, SPEN, and CSRC bits.

- 3. Ensure that the CREN and SREN bits are clear (these bits override transmission when set).

- 4. If interrupts are desired, then set the TXIE bit (the GLINTD bit must be clear and the PEIE bit must be set).

- 5. If 9-bit transmission is desired, then set the TX9 bit.

- 6. Start transmission by loading data to the TXREG register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 8. Enable the transmission by setting TXEN.

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the reverse order.

Note: To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

#### 13.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either the SREN (RCSTA<5>) bit or the CREN (RCSTA<4>) bit. Data is sampled on the RA4/RX/DT pin on the falling edge of the clock. If SREN is set, then only a single word is received. If CREN is set, the reception is continuous until CREN is reset. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to RCREG (if it is empty). If the transfer is complete, the interrupt bit RCIF (PIR<0>) is set. The actual interrupt can be enabled/disabled by setting/clearing the RCIE (PIE<0>) bit. RCIF is a read only bit which is RESET by the hardware. In this case it is reset when RCREG has been read and is empty. RCREG is a double buffered register; i.e., it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR. On the clocking of the last bit of the third byte, if RCREG is still full, then the overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. RCREG can be read twice to retrieve the two bytes in the FIFO. The OERR bit has to be cleared in software. This is done by clearing the CREN bit. If OERR bit is set, transfers from RSR to RCREG are inhibited, so it is essential to clear OERR bit if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register will allow the RX9D and FERR bits to be loaded with values for the next received data: therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old FERR and RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. See Section 13.1 for details.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- 6. The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- 7. Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading RCREG.

- 9. If any error occurred, clear the error by clearing CREN.

Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

# FIGURE 13-11: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

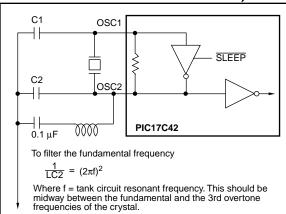

#### FIGURE 14-3: CRYSTAL OPERATION, OVERTONE CRYSTALS (XT OSC CONFIGURATION)

# TABLE 14-2: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Oscillator<br>Type | Resonator<br>Frequency         | Capacitor Range<br>C1 = C2               |

|--------------------|--------------------------------|------------------------------------------|

| LF                 | 455 kHz<br>2.0 MHz             | 15 - 68 pF<br>10 - 33 pF                 |

| ХТ                 | 4.0 MHz<br>8.0 MHz<br>16.0 MHz | 22 - 68 pF<br>33 - 100 pF<br>33 - 100 pF |

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### **Resonators Used:**

| 455 kHz                                           | Panasonic EFO-A455K04B | ± 0.3% |  |  |

|---------------------------------------------------|------------------------|--------|--|--|

| 2.0 MHz                                           | ± 0.5%                 |        |  |  |

| 4.0 MHz                                           | ± 0.5%                 |        |  |  |

| 8.0 MHz                                           | ± 0.5%                 |        |  |  |

| 16.0 MHz Murata Erie CSA16.00MX ± 0.5%            |                        |        |  |  |

| Resonators used did not have built-in capacitors. |                        |        |  |  |

# TABLE 14-3:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR

| Osc<br>Type | Freq                  | C1               | C2             |

|-------------|-----------------------|------------------|----------------|

| LF          | 32 kHz <sup>(1)</sup> | 100-150 pF       | 100-150 pF     |

|             | 1 MHz                 | 10-33 pF         | 10-33 pF       |

|             | 2 MHz                 | 10-33 pF         | 10-33 pF       |

| XT          | 2 MHz                 | 47-100 pF        | 47-100 pF      |

|             | 4 MHz                 | 15-68 pF         | 15-68 pF       |

|             | 8 MHz <sup>(2)</sup>  | 15-47 pF         | 15-47 pF       |

|             | 16 MHz                | TBD              | TBD            |

|             | 25 MHz                | 15-47 pF         | 15-47 pF       |

|             | 32 MHz <sup>(3)</sup> | <sub>0</sub> (3) | <sub>(3)</sub> |

Higher capacitance increases the stability of the oscillator but also increases the start-up time and the oscillator current. These values are for design guidance only. Rs may be required in XT mode to avoid overdriving the crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values for external components.

- Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

- 2: Rs of 330Ω is required for a capacitor combination of 15/15 pF.

- 3: Only the capacitance of the board was present.

#### **Crystals Used:**

| 32.768 kHz | Epson C-001R32.768K-A | ± 20 PPM     |

|------------|-----------------------|--------------|

| 1.0 MHz    | ECS-10-13-1           | $\pm$ 50 PPM |

| 2.0 MHz    | ECS-20-20-1           | $\pm$ 50 PPM |

| 4.0 MHz    | ECS-40-20-1           | ± 50 PPM     |

| 8.0 MHz    | ECS ECS-80-S-4        | ± 50 PPM     |

|            | ECS-80-18-1           |              |

| 16.0 MHz   | ECS-160-20-1          | TBD          |

| 25 MHz     | CTS CTS25M            | $\pm$ 50 PPM |

| 32 MHz     | CRYSTEK HF-2          | $\pm$ 50 PPM |

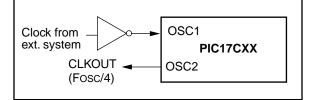

#### 14.2.3 EXTERNAL CLOCK OSCILLATOR

In the EC oscillator mode, the OSC1 input can be driven by CMOS drivers. In this mode, the OSC1/CLKIN pin is hi-impedance and the OSC2/CLK-OUT pin is the CLKOUT output (4 Tosc).

### FIGURE 14-4: EXTERNAL CLOCK INPUT OPERATION (EC OSC CONFIGURATION)

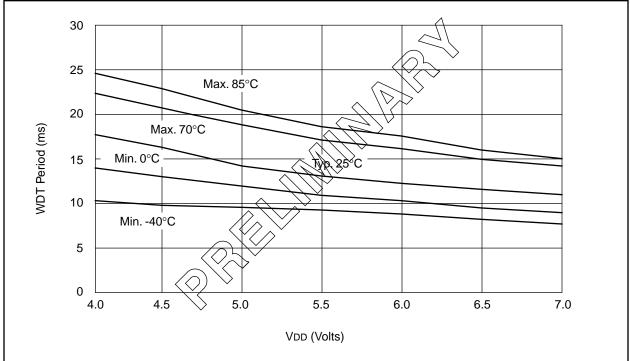

## 14.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLK-OUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation and SLEEP mode, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 14.1).

Under normal operation, the WDT must be cleared on a regular interval. This time is less the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

#### 14.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms, (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a postscaler with a division ratio of up to 1:256 can be assigned to the WDT. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

#### 14.3.2 CLEARING THE WDT AND POSTSCALER

The WDT and postscaler are cleared when:

- The device is in the reset state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the reset state.

#### 14.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT postscaler) it may take several seconds before a WDT time-out occurs.

The WDT and postscaler is the Power-up Timer during the Power-on Reset sequence.

#### 14.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the  $\overline{\text{TO}}$  bit is cleared (device is not reset). The CLRWDT instruction can be used to set the  $\overline{\text{TO}}$  bit. This allows the WDT to be a simple overflow timer. When in sleep, the WDT does not increment.

Table 15-2 lists the instructions recognized by the MPASM assembler.

| Note 1: | Any unused opcode is Reserved. Use of |

|---------|---------------------------------------|

|         | any reserved opcode may cause unex-   |

|         | pected operation.                     |

**Note 2:** The shaded instructions are not available in the PIC17C42

All instruction examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

To represent a binary number:

0000 0100b

where b signifies a binary string.

### FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

### 15.1 <u>Special Function Registers as</u> <u>Source/Destination</u>

The PIC17C4X's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 15.1.1 ALUSTA AS DESTINATION

If an instruction writes to ALUSTA, the Z, C, DC and OV bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF ALUSTA will clear register ALUSTA, and then set the Z bit leaving 0000 0100b in the register.

#### 15.1.2 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $\text{PCH} \rightarrow \text{PCLATH}; \text{PCL} \rightarrow \text{dest}$                    |

|--------------------|-----------------------------------------------------------------------------------------------|

| Write PCL:         | PCLATH $\rightarrow$ PCH;<br>8-bit destination value $\rightarrow$ PCL                        |

| Read-Modify-Write: | $PCL \rightarrow ALU$ operand<br>$PCLATH \rightarrow PCH$ ;<br>8-bit result $\rightarrow PCL$ |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 15.1.3 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write). The user should keep this in mind when operating on special function registers, such as ports.

| BSF                                                                         | Bit Set f                                                          |                                   |        |   |                     |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------|--------|---|---------------------|

| Syntax:                                                                     | [ <i>label</i> ] E                                                 | [ <i>label</i> ] BSF f,b          |        |   |                     |

| Operands:                                                                   | $\begin{array}{l} 0 \leq f \leq 25 \\ 0 \leq b \leq 7 \end{array}$ | $0 \le f \le 255$ $0 \le b \le 7$ |        |   |                     |

| Operation:                                                                  | $1 \rightarrow (f < b >$                                           | -)                                |        |   |                     |

| Status Affected:                                                            | None                                                               |                                   |        |   |                     |

| Encoding:                                                                   | 1000                                                               | 0bbb                              | fff    | f | ffff                |

| Description:                                                                | Bit 'b' in re                                                      | gister 'f' is                     | s set. |   |                     |

| Words:                                                                      | 1                                                                  |                                   |        |   |                     |

| Cycles:                                                                     | 1                                                                  |                                   |        |   |                     |

| Q Cycle Activity:                                                           |                                                                    |                                   |        |   |                     |

| Q1                                                                          | Q2                                                                 | Q3                                |        |   | Q4                  |

| Decode                                                                      | Read<br>register 'f'                                               | Execu                             | ute    |   | Write<br>gister 'f' |

| Example:                                                                    | BSF                                                                | FLAG_RE                           | G, 7   |   |                     |

| Before Instruction<br>FLAG_REG= 0x0A<br>After Instruction<br>FLAG_REG= 0x8A |                                                                    |                                   |        |   |                     |

| BTF        | SC                                                    | Bit Test, s                                                                                                   | skip if Cle                                              | ear                                                 |                                |

|------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|--------------------------------|

| Synt       | tax:                                                  | [ <i>label</i> ] B                                                                                            | TFSC f,I                                                 | b                                                   |                                |

| Ope        | rands:                                                | $0 \le f \le 253$ $0 \le b \le 7$                                                                             | 5                                                        |                                                     |                                |

| Ope        | ration:                                               | skip if (f <t< td=""><td>o&gt;) = 0</td><td></td><td></td></t<>                                               | o>) = 0                                                  |                                                     |                                |

| Stat       | us Affected:                                          | None                                                                                                          |                                                          |                                                     |                                |

| Enc        | oding:                                                | 1001                                                                                                          | 1bbb                                                     | ffff                                                | ffff                           |

| Des        | cription:                                             | If bit 'b' in<br>instruction<br>If bit 'b' is 0<br>fetched du<br>cution is dia<br>cuted inste<br>instruction. | is skipped.<br>then the n<br>ring the cur<br>scarded, ar | ext instruction<br>rent instruction<br>rend a NOP i | ction<br>Iction exe-<br>s exe- |

| Wor        | ds:                                                   | 1                                                                                                             |                                                          |                                                     |                                |

| Cycl       | les:                                                  | 1(2)                                                                                                          |                                                          |                                                     |                                |

| QC         | ycle Activity:                                        |                                                                                                               |                                                          |                                                     |                                |

|            | Q1                                                    | Q2                                                                                                            | Q3                                                       |                                                     | Q4                             |

|            | Decode                                                | Read<br>register 'f'                                                                                          | Execu                                                    | ite                                                 | NOP                            |

| lf sk      | ip:                                                   |                                                                                                               |                                                          |                                                     |                                |

|            | Q1                                                    | Q2                                                                                                            | Q3                                                       |                                                     | Q4                             |

|            | Forced NOP                                            | NOP                                                                                                           | Execu                                                    | ite                                                 | NOP                            |

| <u>Exa</u> | mple:                                                 | FALSE                                                                                                         | BTFSC<br>:                                               | FLAG,1                                              |                                |

|            | Before Instru<br>PC                                   |                                                                                                               | dress (HE                                                | RE)                                                 |                                |

|            | After Instructi<br>If FLAG<7<br>PC<br>If FLAG<7<br>PC | l> = 0;<br>= ac<br>l> = 1;                                                                                    | ldress (TR                                               |                                                     |                                |

| CALL                                | Subroutir                                                  | ne Call                                                                                            |                                                                              | CLF        | RF                                       | Clear f                                                                       |                    |          |                       |

|-------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------|------------------------------------------|-------------------------------------------------------------------------------|--------------------|----------|-----------------------|

| Syntax:                             | [label] (                                                  | CALL k                                                                                             |                                                                              | Syn        | tax:                                     | [ <i>label</i> ] CL                                                           | RF f,s             |          |                       |

| Operands:                           | $0 \le k \le 40$                                           | 95                                                                                                 |                                                                              | Ope        | erands:                                  | $0 \le f \le 25$                                                              | 5                  |          |                       |

| Operation:                          | k<12:8> –                                                  | TOS, $k \rightarrow PC$<br>$\rightarrow PCLATH < 4$<br>$\Rightarrow \rightarrow PCLATH$            | :0>;                                                                         |            | eration:                                 | $00h \rightarrow f, s$<br>$00h \rightarrow de$                                |                    |          |                       |

| Status Affecte                      |                                                            |                                                                                                    | 1<7.02                                                                       | Stat       | tus Affected:                            | None                                                                          |                    |          |                       |

|                                     |                                                            |                                                                                                    |                                                                              | ר Enc      | oding:                                   | 0010                                                                          | 100s               | ffff     | ffff                  |

| Encoding:<br>Description:           | return addr<br>the stack. T<br>PC bits<12<br>bits of the F | kkkk kkl<br>call within 8K<br>ess (PC+1) is<br>he 13-bit value<br>:0>. Then the p<br>PC are copied | page. First,<br>pushed onto<br>is loaded into<br>upper-eight<br>into PCLATH. |            | scription:                               | Clears the<br>ister(s).<br>s = 0: Data<br>WREG are<br>s = 1: Data<br>cleared. | memory<br>cleared. | location |                       |

|                                     |                                                            | wo-cycle instru                                                                                    |                                                                              | Woi        | rds:                                     | 1                                                                             |                    |          |                       |

|                                     | See LCALL<br>space.                                        | for calls outsid                                                                                   | le 8K memory                                                                 | Сус        | les:                                     | 1                                                                             |                    |          |                       |

| Words:                              | 1                                                          |                                                                                                    |                                                                              | QC         | cycle Activity:                          |                                                                               |                    |          |                       |

| Cycles:                             | 2                                                          |                                                                                                    |                                                                              |            | Q1                                       | Q2                                                                            | Q                  |          | Q4                    |

| Q Cycle Activ                       | ity:                                                       |                                                                                                    |                                                                              |            | Decode                                   | Read<br>register 'f'                                                          | Exec               |          | Write<br>register 'f' |

| Q1                                  | Q2                                                         | Q3                                                                                                 | Q4                                                                           |            |                                          |                                                                               |                    |          | and other             |

| Decode                              | e Read literal<br>'k'<7:0>                                 | Execute                                                                                            | NOP                                                                          |            |                                          |                                                                               |                    |          | specified<br>register |

| Forced N                            | OP NOP                                                     | Execute                                                                                            | NOP                                                                          | <u>Exa</u> | mple:                                    | CLRF                                                                          | FLAC               | G_REG    |                       |

| <u>Example</u> :<br>Before In<br>PC |                                                            | CALL THE                                                                                           | RE                                                                           |            | Before Instru<br>FLAG_R<br>After Instruc | EG = 0                                                                        | κ5Α                |          |                       |

| After Inst<br>PC                    |                                                            | ERE)                                                                                               |                                                                              |            | FLAG_R                                   | EG = 0>                                                                       | (00                |          |                       |

PC = Address(THERE) TOS = Address(HERE + 1)

| CLRWDT            | Clear Wa                                                                                                                             | tchdog      | Timer   |                                          |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|------------------------------------------|

| Syntax:           | [ label ]                                                                                                                            | CLRWD       | Г       |                                          |

| Operands:         | None                                                                                                                                 |             |         |                                          |

| Operation:        | $\begin{array}{c} 00h \rightarrow Wh \\ 0 \rightarrow WDT \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |             | ller,   |                                          |

| Status Affected:  | TO, PD                                                                                                                               |             |         |                                          |

| Encoding:         | 0000                                                                                                                                 | 0000        | 0000    | 0100                                     |

| Description:      |                                                                                                                                      | o resets t  | he pres | e watchdog<br>caler of the<br>5 are set. |

| Words:            | 1                                                                                                                                    |             |         |                                          |

| Cycles:           | 1                                                                                                                                    |             |         |                                          |

| Q Cycle Activity: |                                                                                                                                      |             |         |                                          |

|                   |                                                                                                                                      |             |         |                                          |

| Q1                | Q2                                                                                                                                   | Q3          |         | Q4                                       |

| Q1<br>Decode      | Q2<br>Read<br>register<br>ALUSTA                                                                                                     | Q3<br>Execu |         | Q4<br>NOP                                |

|                   | Read<br>register                                                                                                                     |             |         |                                          |

| Decode            | Read<br>register<br>ALUSTA<br>CLRWDT                                                                                                 |             |         |                                          |

| COMF                           | Complem                                                  | ent f                      |           |                     |

|--------------------------------|----------------------------------------------------------|----------------------------|-----------|---------------------|

| Syntax:                        | [label]                                                  | COMF                       | f,d       |                     |

| Operands:                      | 0 ≤ f ≤ 255<br>d ∈ [0,1]                                 | 5                          |           |                     |

| Operation:                     | $(\overline{f}) \rightarrow (d$                          | est)                       |           |                     |

| Status Affected:               | Z                                                        |                            |           |                     |

| Encoding:                      | 0001                                                     | 001d                       | ffff      | ffff                |

| Description:                   | The conten<br>mented. If '<br>WREG. If 'c<br>back in reg | d' is 0 the<br>d' is 1 the | result is | stored in           |

| Words:                         | 1                                                        |                            |           |                     |

| Cycles:                        | 1                                                        |                            |           |                     |

| Q Cycle Activity:              |                                                          |                            |           |                     |

| Q1                             | Q2                                                       | Q3                         |           | Q4                  |

| Decode                         | Read<br>register 'f'                                     | Execu                      |           | Write<br>gister 'f' |

| Example:                       | COMF                                                     | REG                        | 1,0       |                     |

| Before Instru<br>REG1          | ction<br>= 0x13                                          |                            |           |                     |

| After Instruct<br>REG1<br>WREG | = 0x13                                                   |                            |           |                     |

| IORWF                    | Inclusive            |                                                   | with f               | LCALL          | Long Cal                                  | I                                            |                               |

|--------------------------|----------------------|---------------------------------------------------|----------------------|----------------|-------------------------------------------|----------------------------------------------|-------------------------------|

| Syntax:                  | [ label ]            | ORWF f,d                                          |                      | Syntax:        | [ label ]                                 | LCALL k                                      |                               |

| Operands:                | $0 \le f \le 255$    | 5                                                 |                      | Operands:      | $0 \le k \le 25$                          | 5                                            |                               |

|                          | d ∈ [0,1]            |                                                   |                      | Operation:     | PC + 1 $\rightarrow$                      | TOS;                                         |                               |

| Operation:               | (WREG) .             | $OR.\left(f ight) ightarrow\left(de ight)$        | est)                 |                | $k \rightarrow PCL$ ,                     | (PCLATH) -                                   | $\rightarrow$ PCH             |

| Status Affected:         | Z                    |                                                   |                      | Status Affecte | d: None                                   |                                              |                               |

| Encoding:                | 0000                 | 100d ff:                                          | ff ffff              | Encoding:      | 1011                                      | 0111 kk                                      | kk kkkk                       |

| Description:             | 'd' is 0 the r       | R WREG with<br>esult is placed<br>esult is placed | 0                    | Description:   | tine call to<br>gram mem<br>First, the re | anywhere with<br>ory space.<br>eturn address | · · ·                         |

| Words:                   | 1                    |                                                   |                      |                | •                                         | to the stack. A<br>ress is then lo           |                               |

| Cycles:                  | 1                    |                                                   |                      |                |                                           | ounter. The lo                               |                               |

| Q Cycle Activity:        |                      |                                                   |                      |                |                                           |                                              | s embedded in                 |

| Q1                       | Q2                   | Q3                                                | Q4                   |                |                                           | om PC high h                                 | er 8-bits of PC olding latch, |

| Decode                   | Read<br>register 'f' | Execute                                           | Write to destination |                | PCLATH.                                   | Ū                                            | 0                             |

|                          | 0                    |                                                   | uestination          | Words:         | 1                                         |                                              |                               |

| Example:                 |                      | ESULT, O                                          |                      | Cycles:        | 2                                         |                                              |                               |

| Before Instru<br>RESULT  |                      |                                                   |                      | Q Cycle Activi | ty:                                       |                                              |                               |

| WREG                     | = 0x13<br>= 0x91     |                                                   |                      | Q1             | Q2                                        | Q3                                           | Q4                            |

| After Instruct<br>RESULT |                      |                                                   |                      | Decode         | Read<br>literal 'k'                       | Execute                                      | Write<br>register PCL         |

| WREG                     | = 0x13<br>= 0x93     |                                                   |                      | Forced NC      | DP NOP                                    | Execute                                      | NOP                           |

|                          |                      |                                                   |                      | Example:       | MOVPF W                                   | IGH(SUBROU<br>REG, PCLAT<br>OW(SUBROUT       | Н                             |

**Before Instruction**

| SUBROUTINE        | = | 16-bit Address |

|-------------------|---|----------------|

| PC                | = | ?              |

| After Instruction |   |                |

| PC = Address (S | UBROUTINE) |

|-----------------|------------|

|-----------------|------------|

# Applicable Devices 42 R42 42A 43 R43 44

# FIGURE 18-17: IOL vs. VOL, VDD = 5V

# Applicable Devices 42 R42 42A 43 R43 44

# 19.5 <u>Timing Diagrams and Specifications</u>

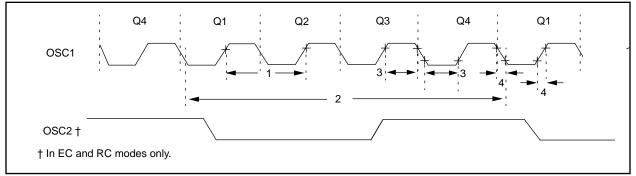

# FIGURE 19-2: EXTERNAL CLOCK TIMING

# TABLE 19-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                     | Min   | Тур†   | Max   | Units | Conditions                                        |

|--------------|-------|------------------------------------|-------|--------|-------|-------|---------------------------------------------------|

|              | Fosc  | External CLKIN Frequency           | DC    | _      | 8     | MHz   | EC osc mode - 08 devices (8 MHz devices)          |

|              |       | (Note 1)                           | DC    | _      | 16    | MHz   | - 16 devices (16 MHz devices)                     |

|              |       | (                                  | DC    | _      | 25    | MHz   | - 25 devices (25 MHz devices)                     |

|              |       |                                    | DC    | —      | 33    | MHz   | - 33 devices (33 MHz devices)                     |

|              |       | Oscillator Frequency               | DC    | _      | 4     | MHz   | RC osc mode                                       |

|              |       | (Note 1)                           | 1     | _      | 8     | MHz   | XT osc mode - 08 devices (8 MHz devices)          |

|              |       |                                    | 1     | _      | 16    | MHz   | - 16 devices (16 MHz devices)                     |

|              |       |                                    | 1     | _      | 25    | MHz   | - 25 devices (25 MHz devices)                     |

|              |       |                                    | 1     | _      | 33    | MHz   | - 33 devices (33 MHz devices)                     |

|              |       |                                    | DC    | —      | 2     | MHz   | LF osc mode                                       |

| 1            | Tosc  | External CLKIN Period              | 125   | _      | —     | ns    | EC osc mode - 08 devices (8 MHz devices)          |

|              |       | (Note 1)                           | 62.5  | _      | —     | ns    | - 16 devices (16 MHz devices)                     |

|              |       |                                    | 40    | _      | —     | ns    | - 25 devices (25 MHz devices)                     |

|              |       |                                    | 30.3  | —      | —     | ns    | - 33 devices (33 MHz devices)                     |

|              |       | Oscillator Period                  | 250   | _      | —     | ns    | RC osc mode                                       |

|              |       | (Note 1)                           | 125   | _      | 1,000 | ns    | XT osc mode - 08 devices (8 MHz devices)          |

|              |       |                                    | 62.5  | _      | 1,000 | ns    | - 16 devices (16 MHz devices)                     |

|              |       |                                    | 40    | —      | 1,000 | ns    | <ul> <li>- 25 devices (25 MHz devices)</li> </ul> |

|              |       |                                    | 30.3  | —      | 1,000 | ns    | - 33 devices (33 MHz devices)                     |

|              |       |                                    | 500   | —      | —     | ns    | LF osc mode                                       |

| 2            | Тсү   | Instruction Cycle Time<br>(Note 1) | 121.2 | 4/Fosc | DC    | ns    |                                                   |

| 3            | TosL, | Clock in (OSC1)                    | 10 ±  | _      | _     | ns    | EC oscillator                                     |

|              | TosH  | high or low time                   | · '   |        |       |       |                                                   |

| 4            | TosR, | Clock in (OSC1)                    | _     | _      | 5‡    | ns    | EC oscillator                                     |

|              | TosF  | rise or fall time                  |       |        |       |       |                                                   |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

# Applicable Devices 42 R42 42A 43 R43 44

# FIGURE 20-13: WDT TIMER TIME-OUT PERIOD vs. VDD

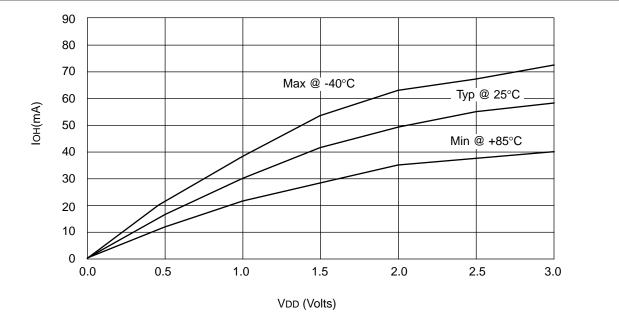

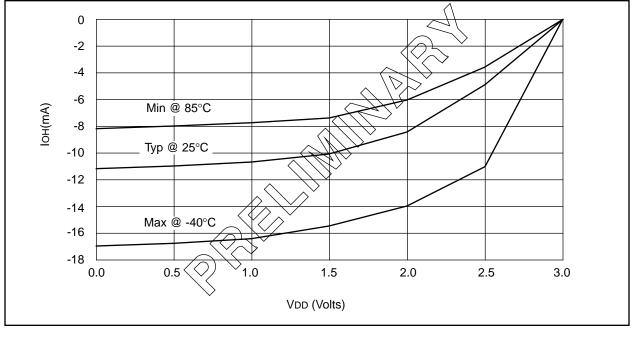

FIGURE 20-14: IOH vs. VOH, VDD = 3V

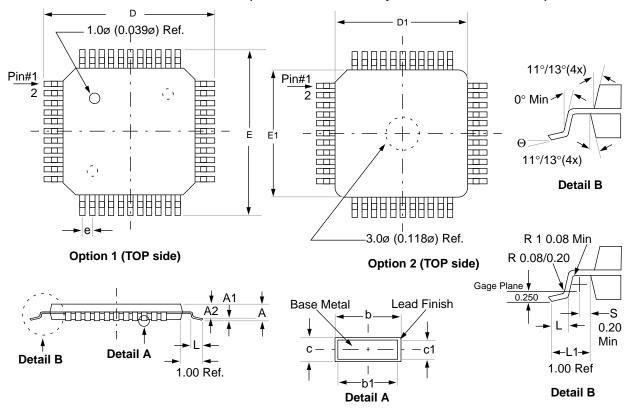

| 21.5 | 44-Lead Plastic Surface Mount ( | TOFP 10x10 mm Body | v 1.0/0.10 mm Lead Form) |

|------|---------------------------------|--------------------|--------------------------|

| 21.0 |                                 |                    |                          |

| Package Group: Plastic TQFP |       |             |       |       |            |       |

|-----------------------------|-------|-------------|-------|-------|------------|-------|

|                             |       | Millimeters |       |       | Inches     |       |

| Symbol                      | Min   | Max         | Notes | Min   | Max        | Notes |

| A                           | 1.00  | 1.20        |       | 0.039 | 0.047      |       |

| A1                          | 0.05  | 0.15        |       | 0.002 | 0.006      |       |

| A2                          | 0.95  | 1.05        |       | 0.037 | 0.041      |       |

| D                           | 11.75 | 12.25       |       | 0.463 | 0.482      |       |

| D1                          | 9.90  | 10.10       |       | 0.390 | 0.398      |       |

| E                           | 11.75 | 12.25       |       | 0.463 | 0.482      |       |

| E1                          | 9.90  | 10.10       |       | 0.390 | 0.398      |       |

| L                           | 0.45  | 0.75        |       | 0.018 | 0.030      |       |

| е                           | 0.80  | BSC         |       | 0.031 | BSC        |       |

| b                           | 0.30  | 0.45        |       | 0.012 | 0.018      |       |

| b1                          | 0.30  | 0.40        |       | 0.012 | 0.016      |       |

| С                           | 0.09  | 0.20        |       | 0.004 | 0.008      |       |

| c1                          | 0.09  | 0.16        |       | 0.004 | 0.006      |       |

| Ν                           | 44    | 44          |       | 44    | 44         |       |

| Θ                           | 0°    | 7°          |       | 0°    | <b>7</b> ° |       |

Note 1: Dimensions D1 and E1 do not include mold protrusion. Allowable mold protrusion is 0.25m/m (0.010") per side. D1 and E1 dimensions including mold mismatch.

2: Dimension "b" does not include Dambar protrusion, allowable Dambar protrusion shall be 0.08m/m (0.003")max.

3: This outline conforms to JEDEC MS-026.

# E.4 PIC16C6X Family of Devices