Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 454 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c43t-25i-pq |

|                            |                                                                            |

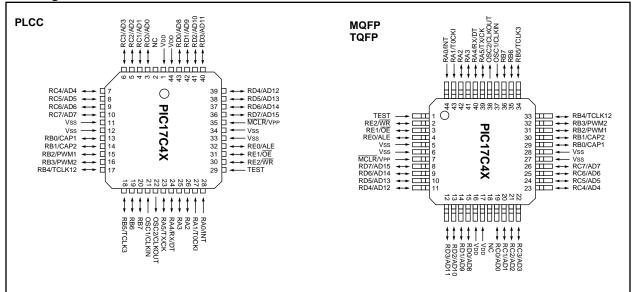

#### Pin Diagrams Cont.'d

All devices are available in all package types, listed in Section 21.0, with the following exceptions:

- ROM devices are not available in Windowed CERDIP Packages

- TQFP is not available for the PIC17C42.

NOTES:

FIGURE 3-1: PIC17C42 BLOCK DIAGRAM ALE, WR, OF OSC1, OSC2, OSC2, OSC3, AD <15:0> PORTC and PORTD DECODE SYSTEM BUS INTER-FACE FSR0 FSR1 ADDRESS LATCH PROGRAM MEMORY (EPROM/ROM) 2K x 16 DATA LATCH IR LATCH <16> ROM LATCH <16> 16 Q1, Q2, Q3, Q4 IR BUS <16> TABLE PTR<16> CONTROL OUTPUTS 16 INSTRUCTION DECODER TABLE LATCH <16> STACK 16 x 16 CONTROL SIGNALS TO CPU РС PCLATH<8> LITERAL PC H INTERRUPT MODULE IR BUS <7:0> IR <2:0> RAM ADDR BUFFER DATA RAM 232x8 DATA LATCH 4 BSR <8> SUB ATAD IR <7> READ/WRITE DECODE FOR REGISTERS MAPPED IN DATA SPACE WRF DATA BUS <8> RDF PERIPHERALS - \_\_\_RA1/T0CKI Timer0 MODULE SERIAL PORT DIGITAL I/O PORTS A, B RA0/INT WREG <8> IR BUS <16> 9 ∞ RA1/ TOCKI 9 BITOP SHIFTER ALU PORTA RA0/INT RA1/TOCKI RA2 RA3 RA4/RX/DT RA5/TX/CK

#### 5.1 <u>Interrupt Status Register (INTSTA)</u>

The Interrupt Status/Control register (INTSTA) records the individual interrupt requests in flag bits, and contains the individual interrupt enable bits (not for the peripherals).

The PEIF bit is a read only, bit wise OR of all the peripheral flag bits in the PIR register (Figure 5-4).

Note: TOIF, INTF, TOCKIF, or PEIF will be set by the specified condition, even if the corresponding interrupt enable bit is clear (interrupt disabled) or the GLINTD bit is set (all interrupts disabled).

Care should be taken when clearing any of the INTSTA register enable bits when interrupts are enabled (GLINTD is clear). If any of the INTSTA flag bits (T0IF, INTF, T0CKIF, or PEIF) are set in the same instruction cycle as the corresponding interrupt enable bit is cleared, the device will vector to the reset address (0x00).

When disabling any of the INTSTA enable bits, the GLINTD bit should be set (disabled).

#### FIGURE 5-2: INTSTA REGISTER (ADDRESS: 07h, UNBANKED)

| R - 0  | R/W - 0                                                                                                                                                                                                                                                                         | R/W - 0                | R/W - 0                 | R/W - 0                  | R/W - 0                                | R/W - 0                 | R/W - 0     |                               |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|--------------------------|----------------------------------------|-------------------------|-------------|-------------------------------|--|

| PEIF   | TOCKIF                                                                                                                                                                                                                                                                          | TOIF                   | INTF                    | PEIE                     | T0CKIE                                 | TOIE                    | INTE        | R = Readable bit              |  |

| bit7   | 1001111                                                                                                                                                                                                                                                                         |                        |                         |                          | 1001112                                | . 0.12                  | bit0        | W = Writable bit              |  |

| DIL    |                                                                                                                                                                                                                                                                                 |                        |                         |                          |                                        |                         | DILU        | - n = Value at POR reset      |  |

| bit 7: |                                                                                                                                                                                                                                                                                 |                        |                         |                          |                                        |                         |             |                               |  |

| bit 6: | This bit is 1 = The so                                                                                                                                                                                                                                                          | cleared l<br>oftware s | by hardwa<br>pecified e | ire, when t<br>dge occur | red on the                             | pt logic for<br>RA1/T0C |             | am execution to vector (18h). |  |

| bit 5: | TOIF: TMF This bit is $1 = TMR0$ $0 = TMR0$                                                                                                                                                                                                                                     | cleared l<br>overflow  | by hardwa<br>ed         |                          |                                        | pt logic foi            | rces progra | am execution to vector (10h). |  |

| bit 4: | INTF: External Interrupt on INT Pin Flag bit This bit is cleared by hardware, when the interrupt logic forces program execution to vector (08h).  1 = The software specified edge occurred on the RA0/INT pin  0 = The software specified edge did not occur on the RA0/INT pin |                        |                         |                          |                                        |                         |             |                               |  |

| bit 3: |                                                                                                                                                                                                                                                                                 |                        |                         |                          |                                        |                         |             |                               |  |

| bit 2: |                                                                                                                                                                                                                                                                                 | e softwar              | e specifie              | d edge int               | Pin Enable<br>errupt on t<br>(I pin    |                         | 0CKI pin    |                               |  |

| bit 1: | <b>T0IE</b> : TMF<br>1 = Enable<br>0 = Disable                                                                                                                                                                                                                                  | e TMR0 o               | overflow in             | terrupt                  | bit                                    |                         |             |                               |  |

| bit 0: | 1 = Enable                                                                                                                                                                                                                                                                      | e softwar              | e specifie              | d edge int               | in Enable<br>errupt on t<br>terrupt on | he RA0/IN               |             |                               |  |

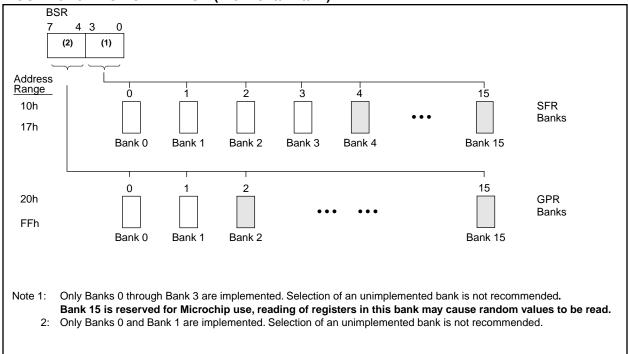

#### 6.8 Bank Select Register (BSR)

The BSR is used to switch between banks in the data memory area (Figure 6-13). In the PIC17C42, PIC17CR42, and PIC17C42A only the lower nibble is implemented. While in the PIC17C43, PIC17CR43, and PIC17C44 devices, the entire byte is implemented. The lower nibble is used to select the peripheral register bank. The upper nibble is used to select the general purpose memory bank.

All the Special Function Registers (SFRs) are mapped into the data memory space. In order to accommodate the large number of registers, a banking scheme has been used. A segment of the SFRs, from address 10h to address 17h, is banked. The lower nibble of the bank select register (BSR) selects the currently active "peripheral bank." Effort has been made to group the peripheral registers of related functionality in one bank. However, it will still be necessary to switch from bank to bank in order to address all peripherals related to a single task. To assist this, a MOVLB bank instruction is in the instruction set.

For the PIC17C43, PIC17CR43, and PIC17C44 devices, the need for a large general purpose memory space dictated a general purpose RAM banking scheme. The upper nibble of the BSR selects the currently active general purpose RAM bank. To assist this, a MOVLR bank instruction has been provided in the instruction set.

If the currently selected bank is not implemented (such as Bank 13), any read will read all '0's. Any write is completed to the bit bucket and the ALU status bits will be set/cleared as appropriate.

Note:

Registers in Bank 15 in the Special Function Register area, are reserved for Microchip use. Reading of registers in this bank may cause random values to be read.

#### FIGURE 6-13: BSR OPERATION (PIC17C43/R43/44)

#### 7.1 <u>Table Writes to Internal Memory</u>

A table write operation to internal memory causes a long write operation. The long write is necessary for programming the internal EPROM. Instruction execution is halted while in a long write cycle. The long write will be terminated by any enabled interrupt. To ensure that the EPROM location has been well programmed, a minimum programming time is required (see specification #D114). Having only one interrupt enabled to terminate the long write ensures that no unintentional interrupts will prematurely terminate the long write.

The sequence of events for programming an internal program memory location should be:

- Disable all interrupt sources, except the source to terminate EPROM program write.

- 2. Raise MCLR/VPP pin to the programming voltage.

- 3. Clear the WDT.

- 4. Do the table write. The interrupt will terminate the long write.

- 5. Verify the memory location (table read).

Note: Programming requirements must be met. See timing specification in electrical specifications for the desired device. Violating these specifications (including temperature) may result in EPROM locations that are not fully programmed and may lose their state over time.

#### 7.1.1 TERMINATING LONG WRITES

An interrupt source or reset are the only events that terminate a long write operation. Terminating the long write from an interrupt source requires that the interrupt enable and flag bits are set. The GLINTD bit only enables the vectoring to the interrupt address.

If the TOCKI, RAO/INT, or TMR0 interrupt source is used to terminate the long write; the interrupt flag, of the highest priority enabled interrupt, will terminate the long write and automatically be cleared.

- Note 1: If an interrupt is pending, the TABLWT is aborted (an NOP is executed). The highest priority pending interrupt, from the TOCKI, RAO/INT, or TMR0 sources that is enabled, has its flag cleared.

- Note 2: If the interrupt is not being used for the program write timing, the interrupt should be disabled. This will ensure that the interrupt is not lost, nor will it terminate the long write prematurely.

If a peripheral interrupt source is used to terminate the long write, the interrupt enable and flag bits must be set. The interrupt flag will not be automatically cleared upon the vectoring to the interrupt vector address.

If the GLINTD bit is cleared prior to the long write, when the long write is terminated, the program will branch to the interrupt vector.

If the GLINTD bit is set prior to the long write, when the long write is terminated, the program will not vector to the interrupt address.

TABLE 7-1: INTERRUPT - TABLE WRITE INTERACTION

| Interrupt<br>Source     | GLINTD | Enable<br>Bit | Flag<br>Bit | Action                                                                                                        |

|-------------------------|--------|---------------|-------------|---------------------------------------------------------------------------------------------------------------|

| RA0/INT, TMR0,<br>T0CKI | 0      | 1             | 1           | Terminate long table write (to internal program memory), branch to interrupt vector (branch clears flag bit). |

|                         | 0      | 1             | 0           | None                                                                                                          |

|                         | 1      | 0             | x           | None                                                                                                          |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is automatically cleared).                     |

| Peripheral              | 0      | 1             | 1           | Terminate table write, branch to interrupt vector.                                                            |

|                         | 0      | 1             | 0           | None                                                                                                          |

|                         | 1      | 0             | x           | None                                                                                                          |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is set).                                       |

Example 8-3 shows the sequence to do a 16  $\times$  16 unsigned multiply. Equation 8-1 shows the algorithm that is used. The 32-bit result is stored in 4 registers RES3:RES0.

# EQUATION 8-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

RES3:RES0 = ARG1H:ARG1L\*ARG2L

=  $(ARG1H * ARG2H * 2^{16}) + (ARG1H * ARG2L * 2^{8}) +$

(ARG1L \* ARG2H \* 2<sup>8</sup>) +

(ARG1L \* ARG2L)

#### **EXAMPLE 8-3: 16 x 16 MULTIPLY ROUTINE**

```

ARG1L, WREG

MOVFP

ARG2L ; ARG1L * ARG2L ->

{\tt MULWF}

; PRODH:PRODL

MOVPF

PRODH, RES1 ;

MOVPF

PRODL, RESO ;

MOVFP

ARG1H, WREG

ARG2H ; ARG1H * ARG2H ->

MULWF

PRODH: PRODL

PRODH, RES3 ;

MOVPF

PRODL, RES2 ;

MOVPF

MOVFP

ARG1L, WREG

ARG2H ; ARG1L * ARG2H ->

MULWF

; PRODH:PRODL

MOVFP

PRODL, WREG;

ADDWF

RES1, F ; Add cross

PRODH, WREG; products

MOVFP

ADDWFC

RES2, F

CLRF

WREG, F

;

RES3, F

ADDWFC

ARG1H, WREG;

MOVFP

MULWF

ARG2L ; ARG1H * ARG2L ->

; PRODH:PRODL

MOVFP

PRODL, WREG;

RES1, F ; Add cross

ADDWF

MOVFP

PRODH, WREG; products

ADDWFC

RES2, F ;

WREG, F

CLRF

;

ADDWFC

RES3, F

```

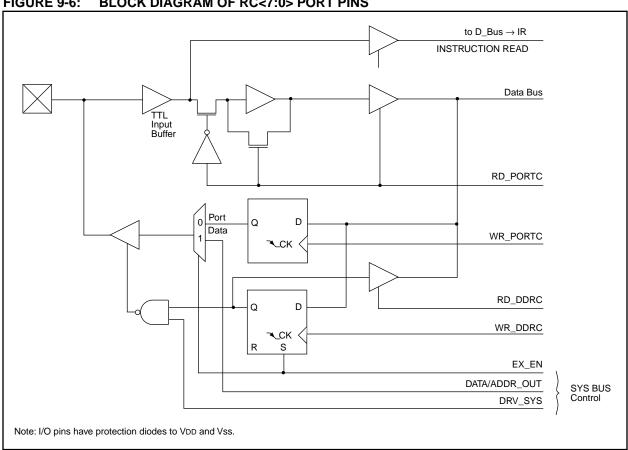

#### 9.3 **PORTC and DDRC Registers**

PORTC is an 8-bit bi-directional port. The corresponding data direction register is DDRC. A '1' in DDRC configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTC reads the status of the pins, whereas writing to it will write to the port latch. PORTC is multiplexed with the system bus. When operating as the system bus, PORTC is the low order byte of the address/data bus (AD7:AD0). The timing for the system bus is shown in the Electrical Characteristics section.

Note: This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a gen-

eral purpose I/O.

Example 9-2 shows the instruction sequence to initialize PORTC. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### **EXAMPLE 9-2: INITIALIZING PORTC**

MOVIB 1 ; Select Bank 1 CLRF PORTC ; Initialize PORTC data latches before setting the data direction register MOVLW 0xCF Value used to initialize data direction MOVWF DDRC Set RC<3:0> as inputs

RC<5:4> as outputs

RC<7:6> as inputs

FIGURE 9-6: **BLOCK DIAGRAM OF RC<7:0> PORT PINS**

#### 12.1.3.1 PWM PERIODS

The period of the PWM1 output is determined by Timer1 and its period register (PR1). The period of the PWM2 output can be software configured to use either Timer1 or Timer2 as the time-base. When TM2PW2 bit (PW2DCL<5>) is clear, the time-base is determined by TMR1 and PR1. When TM2PW2 is set, the time-base is determined by Timer2 and PR2.

Running two different PWM outputs on two different timers allows different PWM periods. Running both PWMs from Timer1 allows the best use of resources by freeing Timer2 to operate as an 8-bit timer. Timer1 and Timer2 can not be used as a 16-bit timer if either PWM is being used.

The PWM periods can be calculated as follows:

The duty cycle of PWMx is determined by the 10-bit value DCx<9:0>. The upper 8-bits are from register PWxDCH and the lower 2-bits are from PWxDCL<7:6> (PWxDCH:PWxDCL<7:6>). Table 12-3 shows the maximum PWM frequency (FPWM) given the value in the period register.

The number of bits of resolution that the PWM can achieve depends on the operation frequency of the device as well as the PWM frequency (FPWM).

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)}$$

bits

The PWMx duty cycle is as follows:

PWMx Duty Cycle = (DCx) x Tosc

where DCx represents the 10-bit value from PWxDCH:PWxDCL.

If DCx = 0, then the duty cycle is zero. If PRx = PWxDCH, then the PWM output will be low for one to four Q-clock (depending on the state of the PWxDCL<7:6> bits). For a Duty Cycle to be 100%, the PWxDCH value must be greater then the PRx value.

The duty cycle registers for both PWM outputs are double buffered. When the user writes to these registers, they are stored in master latches. When TMR1 (or TMR2) overflows and a new PWM period begins, the master latch values are transferred to the slave latches and the PWMx pin is forced high.

Note:

For PW1DCH, PW1DCL, PW2DCH and PW2DCL registers, a write operation writes to the "master latches" while a read operation reads the "slave latches". As a result, the user may not read back what was just written to the duty cycle registers.

The user should also avoid any "read-modify-write" operations on the duty cycle registers, such as: ADDWF PW1DCH. This may cause duty cycle outputs that are unpredictable.

TABLE 12-3: PWM FREQUENCY vs. RESOLUTION AT 25 MHz

| PWM                    | Frequency (kHz) |       |         |       |       |  |  |  |

|------------------------|-----------------|-------|---------|-------|-------|--|--|--|

| Frequency              | 24.4            | 48.8  | 65.104  | 97.66 | 390.6 |  |  |  |

| PRx Value              | 0xFF            | 0x7F  | 0x5F    | 0x3F  | 0x0F  |  |  |  |

| High<br>Resolution     | 10-bit          | 9-bit | 8.5-bit | 8-bit | 6-bit |  |  |  |

| Standard<br>Resolution | 8-bit           | 7-bit | 6.5-bit | 6-bit | 4-bit |  |  |  |

#### 12.1.3.2 PWM INTERRUPTS

The PWM module makes use of TMR1 or TMR2 interrupts. A timer interrupt is generated when TMR1 or TMR2 equals its period register and is cleared to zero. This interrupt also marks the beginning of a PWM cycle. The user can write new duty cycle values before the timer roll-over. The TMR1 interrupt is latched into the TMR1IF bit and the TMR2 interrupt is latched into the TMR2IF bit. These flags must be cleared in software.

#### 12.1.3.3 EXTERNAL CLOCK SOURCE

The PWMs will operate regardless of the clock source of the timer. The use of an external clock has ramifications that must be understood. Because the external TCLK12 input is synchronized internally (sampled once per instruction cycle), the time TCLK12 changes to the time the timer increments will vary by as much as TCY (one instruction cycle). This will cause jitter in the duty cycle as well as the period of the PWM output.

This jitter will be  $\pm TCY$ , unless the external clock is synchronized with the processor clock. Use of one of the PWM outputs as the clock source to the TCLKx input, will supply a synchronized clock.

In general, when using an external clock source for PWM, its frequency should be much less than the device frequency (Fosc).

#### 13.4 <u>USART Synchronous Slave Mode</u>

The synchronous slave mode differs from the master mode in the fact that the shift clock is supplied externally at the RA5/TX/CK pin (instead of being supplied internally in the master mode). This allows the device to transfer or receive data in the SLEEP mode. The slave mode is entered by clearing the CSRC (TXSTA<7>) bit.

### 13.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the sync master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to TXREG and then the SLEEP instruction executes, the following will occur. The first word will immediately transfer to the TSR and will transmit as the shift clock is supplied. The second word will remain in TXREG. TXIF will not be set. When the first word has been shifted out of TSR, TXREG will transfer the second word to the TSR and the TXIF flag will now be set. If TXIE is enabled, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, then the program will branch to interrupt vector (0020h).

Steps to follow when setting up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting the SYNC and SPEN bits and clearing the CSRC bit.

- 2. Clear the CREN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- If 9-bit transmission is desired, then set the TX9 bit.

- 5. Start transmission by loading data to TXREG.

- If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 7. Enable the transmission by setting TXEN.

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the reverse order.

Note:

To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

### 13.4.2 USART SYNCHRONOUS SLAVE RECEPTION

Operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode. Also, SREN is a don't care in slave mode.

If receive is enabled (CREN) prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR will transfer the data to RCREG (setting RCIF) and if the RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0020h).

Steps to follow when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting the SYNC and SPEN bits and clearing the CSRC bit.

- 2. If interrupts are desired, then set the RCIE bit.

- 3. If 9-bit reception is desired, then set the RX9 bit.

- 4. To enable reception, set the CREN bit.

- The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading RCREG.

- 8. If any error occurred, clear the error by clearing the CREN bit.

Note: To abort reception, either clear the SPEN bit, the SREN bit (when in single receive mode), or the CREN bit (when in continuous receive mode). This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

| MOVLR             | Move Literal to high nibble in BSR                                                                                                                                                                                                                        |       |      |      |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                 | MOVLR | k    |      |  |  |  |  |

| Operands:         | $0 \le k \le 15$                                                                                                                                                                                                                                          |       |      |      |  |  |  |  |

| Operation:        | $k \rightarrow (BSR < 7:4>)$                                                                                                                                                                                                                              |       |      |      |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                      |       |      |      |  |  |  |  |

| Encoding:         | 1011                                                                                                                                                                                                                                                      | 101x  | kkkk | uuuu |  |  |  |  |

| Description:      | The 4-bit literal 'k' is loaded into the most significant 4-bits of the Bank Select Register (BSR). Only the high 4-bits of the Bank Select Register are affected. The lower half of the BSR is unchanged. The assembler will encode the "u" fields as 0. |       |      |      |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                         |       |      |      |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                         |       |      |      |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                           |       |      |      |  |  |  |  |

|     | Q1     | Q2                    | Q3      | Q4                                  |

|-----|--------|-----------------------|---------|-------------------------------------|

|     | Decode | Read literal<br>'k:u' | Execute | Write<br>literal 'k' to<br>BSR<7:4> |

| Exa | mple:  | MOVLR 5               |         |                                     |

Before Instruction

BSR register = 0x22

After Instruction

BSR register = 0x52

**Note:** This instruction is not available in the PIC17C42 device.

| MO\   | /LW            | Move Lit            | Move Literal to WREG |          |      |                  |  |  |  |

|-------|----------------|---------------------|----------------------|----------|------|------------------|--|--|--|

| Synt  | ax:            | [ label ]           | MOVLW                | / k      |      |                  |  |  |  |

| Ope   | rands:         | $0 \le k \le 25$    | $0 \le k \le 255$    |          |      |                  |  |  |  |

| Ope   | ration:        | $k \to (WR$         | EG)                  |          |      |                  |  |  |  |

| State | us Affected:   | None                |                      |          |      |                  |  |  |  |

| Enco  | oding:         | 1011                | 0000                 | kkk      | ck   | kkkk             |  |  |  |

| Des   | cription:      | The eight WREG.     | oit literal '        | k' is lo | adeo | d into           |  |  |  |

| Wor   | ds:            | 1                   | 1                    |          |      |                  |  |  |  |

| Cycl  | es:            | 1                   |                      |          |      |                  |  |  |  |

| Q C   | ycle Activity: |                     |                      |          |      |                  |  |  |  |

|       | Q1             | Q2                  | Q                    | 3        |      | Q4               |  |  |  |

|       | Decode         | Read<br>literal 'k' | Exec                 | ute      |      | /rite to<br>VREG |  |  |  |

Example: MOVLW 0x5A

After Instruction WREG = 0x5A

**Applicable Devices** | 42 | R42 | 42A | 43 | R43 | 44 |

# TABLE 17-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC17C42-16                              | PIC17C42-25                              |

|-----|------------------------------------------|------------------------------------------|

| RC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 6 mA max.                           | IDD: 6 mA max.                           |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 4 MHz max.                         | Freq: 4 MHz max.                         |

| XT  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| EC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| LF  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 150 μA max. at 32 kHz (WDT enabled) | IDD: 150 μA max. at 32 kHz (WDT enabled) |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 2 MHz max.                         | Freq: 2 MHz max.                         |

Applicable Devices 42 R42 42A 43 R43 44

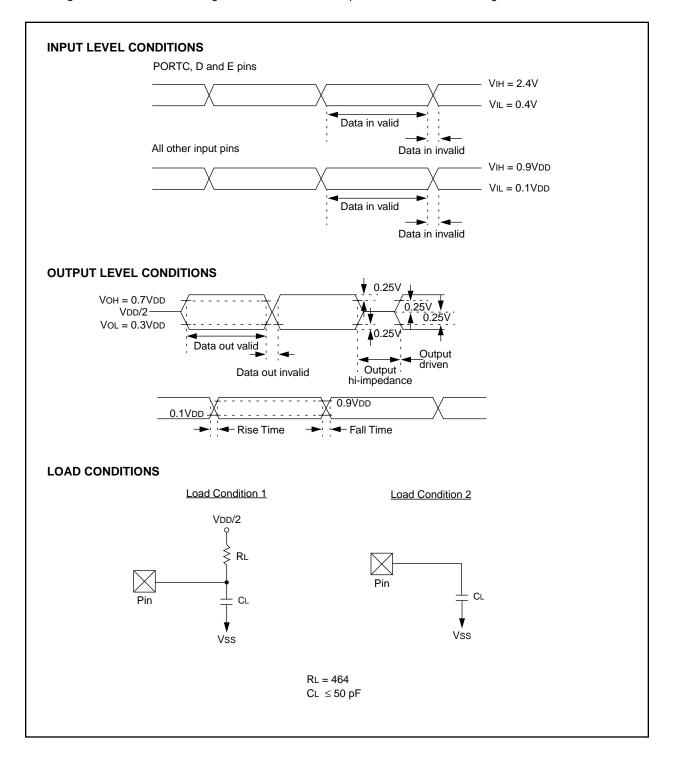

#### FIGURE 17-1: PARAMETER MEASUREMENT INFORMATION

All timings are measure between high and low measurement points as indicated in the figures below.

Applicable Devices 42 R42 42A 43 R43 44

19.2 DC CHARACTERISTICS: PIC17LC42A/43/LC44 (Commercial, Industrial) PIC17LCR42/43 (Commercial, Industrial)

| DC CHARACTERISTICS   |      |                                                              | <b>Standard</b> Operating | •            | _                |                | s (unless otherwise stated)  ≤ TA ≤ +85°C for industrial and ≤ TA ≤ +70°C for commercial |

|----------------------|------|--------------------------------------------------------------|---------------------------|--------------|------------------|----------------|------------------------------------------------------------------------------------------|

| Parameter No.        | Sym  | Characteristic                                               | Min                       | Тур†         | Max              | Units          | Conditions                                                                               |

| D001                 | VDD  | Supply Voltage                                               | 2.5                       | _            | 6.0              | V              |                                                                                          |

| D002                 | VDR  | RAM Data Retention<br>Voltage (Note 1)                       | 1.5 *                     | _            | _                | V              | Device in SLEEP mode                                                                     |

| D003                 | VPOR | VDD start voltage to ensure internal Power-on Reset signal   | _                         | Vss          | _                | V              | See section on Power-on Reset for details                                                |

| D004                 | SVDD | VDD rise rate to<br>ensure internal<br>Power-on Reset signal | 0.060 *                   | -            | -                | mV/ms          | See section on Power-on Reset for details                                                |

| D010<br>D011<br>D014 | IDD  | Supply Current (Note 2)                                      | _<br>_<br>_               | 3<br>6<br>95 | 6<br>12 *<br>150 | mA<br>mA<br>μA | Fosc = 4 MHz (Note 4) Fosc = 8 MHz Fosc = 32 kHz, WDT disabled (EC osc configuration)    |

| D020<br>D021         | IPD  | Power-down<br>Current (Note 3)                               | _<br>_                    | 10<br>< 1    | 40<br>5          | μΑ<br>μΑ       | VDD = 5.5V, WDT enabled<br>VDD = 5.5V, WDT disabled                                      |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1=external square wave, from rail to rail; all I/O pins tristated, pulled to VDD or Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

Current consumed from the oscillator and I/O's driving external capacitive or resistive loads needs to be considered.

For the RC oscillator, the current through the external pull-up resistor (R) can be estimated as: VDD / (2 • R). For capacitive loads, the current can be estimated (for an individual I/O pin) as (CL • VDD) • f

CL = Total capacitive load on the I/O pin; f = average frequency the I/O pin switches.

The capacitive currents are most significant when the device is configured for external execution (includes extended microcontroller mode).

- 3: The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IR = VDD/2Rext (mA) with Rext in kOhm.

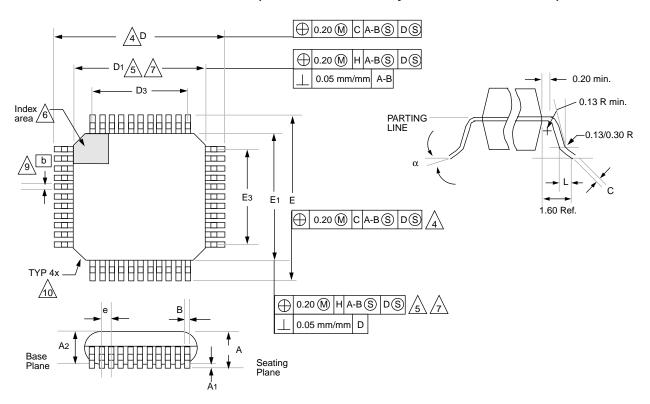

#### 21.4 44-Lead Plastic Surface Mount (MQFP 10x10 mm Body 1.6/0.15 mm Lead Form)

| Package Group: Plastic MQFP |        |             |           |       |       |           |  |  |  |

|-----------------------------|--------|-------------|-----------|-------|-------|-----------|--|--|--|

|                             |        | Millimeters |           |       |       |           |  |  |  |

| Symbol                      | Min    | Max         | Notes     | Min   | Max   | Notes     |  |  |  |

| α                           | 0°     | 7°          |           | 0°    | 7°    |           |  |  |  |

| Α                           | 2.000  | 2.350       |           | 0.078 | 0.093 |           |  |  |  |

| A1                          | 0.050  | 0.250       |           | 0.002 | 0.010 |           |  |  |  |

| A2                          | 1.950  | 2.100       |           | 0.768 | 0.083 |           |  |  |  |

| b                           | 0.300  | 0.450       | Typical   | 0.011 | 0.018 | Typical   |  |  |  |

| С                           | 0.150  | 0.180       |           | 0.006 | 0.007 |           |  |  |  |

| D                           | 12.950 | 13.450      |           | 0.510 | 0.530 |           |  |  |  |

| D1                          | 9.900  | 10.100      |           | 0.390 | 0.398 |           |  |  |  |

| D3                          | 8.000  | 8.000       | Reference | 0.315 | 0.315 | Reference |  |  |  |

| E                           | 12.950 | 13.450      |           | 0.510 | 0.530 |           |  |  |  |

| E1                          | 9.900  | 10.100      |           | 0.390 | 0.398 |           |  |  |  |

| E3                          | 8.000  | 8.000       | Reference | 0.315 | 0.315 | Reference |  |  |  |

| е                           | 0.800  | 0.800       |           | 0.031 | 0.032 |           |  |  |  |

| L                           | 0.730  | 1.030       |           | 0.028 | 0.041 |           |  |  |  |

| N                           | 44     | 44          |           | 44    | 44    |           |  |  |  |

| СР                          | 0.102  | _           |           | 0.004 | _     |           |  |  |  |

| Delay From External Clock Edge68           | FOSC199                                                |

|--------------------------------------------|--------------------------------------------------------|

| Development Support143                     | FS0                                                    |

| Development Tools143                       | FS1                                                    |

| Device Drawings                            | FS2                                                    |

| 44-Lead Plastic Surface Mount (MQFP        | FS3                                                    |

| 10x10 mm Body 1.6/0.15 mm Lead Form)209    | FSR0                                                   |

| DIGIT BORROW9                              | FSR1 34, 40                                            |

| Digit Carry (DC)9                          | Fuzzy Logic Dev. System (fuzzyTECH®-MP) 143, 145       |

| Duty Cycle75                               |                                                        |

|                                            | G                                                      |

| E                                          |                                                        |

| Floatrical Characteristics                 | General Format for Instructions                        |

| Electrical Characteristics                 | General Purpose RAM                                    |

| PIC17C42                                   | General Purpose RAM Bank                               |

| Absolute Maximum Ratings147                | General Purpose Register (GPR)                         |

| Capture Timing                             | GLINTD 25, 37, 78, 105                                 |

| CLKOUT and I/O Timing156                   | GOTO                                                   |

| DC Characteristics                         | GPR (General Purpose Register)                         |

| External Clock Timing                      | Graphs                                                 |

| Memory Interface Read Timing162            | IOH vs. VOH, VDD = 3V                                  |

| Memory Interface Write Timing161           | IOH vs. VOH, VDD = 5V                                  |

| PWM Timing159                              | IOL vs. VOL, VDD = 3V                                  |

| RESET, Watchdog Timer, Oscillator Start-up | IOL vs. VOL, VDD = 5V                                  |

| Timer and Power-up Timer157                | Maximum IDD vs. Frequency                              |

| Timer0 Clock Timings158                    | (External Clock 125°C to -40°C) 167, 197               |

| Timer1, Timer2 and Timer3 Clock Timing 158 | Maximum IPD vs. VDD Watchdog Disabled 168, 198         |

| USART Module, Synchronous Receive 160      | Maximum IPD vs. VDD Watchdog Enabled 169, 199          |

| USART Module, Synchronous Transmission 160 | RC Oscillator Frequency vs.                            |

| PIC17C43/44                                | VDD (Cext = 100 pF)                                    |

| Absolute Maximum Ratings175                | RC Oscillator Frequency vs.                            |

| Capture Timing188                          | VDD (Cext = 22 pF)                                     |

| CLKOUT and I/O Timing185                   | RC Oscillator Frequency vs.                            |

| DC Characteristics177                      | VDD (Cext = 300 pF)                                    |

| External Clock Timing184                   | Transconductance of LF Oscillator vs.VDD 166, 196      |

| Memory Interface Read Timing191            | Transconductance of XT Oscillator vs. VDD 166, 196     |

| Memory Interface Write Timing190           | Typical IDD vs. Frequency                              |

| Parameter Measurement Information183       | (External Clock 25°C) 167, 197                         |

| RESET, Watchdog Timer, Oscillator Start-up | Typical IPD vs. VDD Watchdog Disabled 25°C . 168, 198  |

| Timer and Power-up Timer Timing186         | Typical IPD vs. VDD Watchdog Enabled 25°C 169, 199     |

| Timer0 Clock Timing187                     | Typical RC Oscillator vs. Temperature 163, 193         |

| Timer1, Timer2 and Timer3 Clock Timing 187 | VTH (Input Threshold Voltage) of I/O Pins vs.          |

| Timing Parameter Symbology182              | VDD 172, 202                                           |

| USART Module Synchronous Receive           | VTH (Input Threshold Voltage) of OSC1 Input            |

| Timing189                                  | (In XT, HS, <u>and L</u> P Modes) vs. VDD 173, 203     |

| USART Module Synchronous Transmission      | VTH, VIL of $\overline{MCLR}$ , T0CKI and OSC1         |

| Timing189                                  | (In RC Mode) vs. VDD 173, 203                          |

| EPROM Memory Access Time Order Suffix31    | WDT Timer Time-Out Period vs. VDD 170, 200             |

| Extended Microcontroller29                 |                                                        |

| Extended Microcontroller Mode31            | Н                                                      |

| External Memory Interface31                | П                                                      |

| External Program Memory Waveforms31        | Hardware Multiplier49                                  |

| F                                          |                                                        |

| •                                          | I                                                      |

| Family of Devices6                         | I/O Ports                                              |

| PIC14000213                                | Bi-directional64                                       |

| PIC16C5X214                                |                                                        |

| PIC16CXXX215                               | I/O Ports                                              |

| PIC16C6X216                                | Programming Considerations                             |

| PIC16C7X217                                | Read-Modify-Write Instructions64 Successive Operations |

| PIC16C8X218                                | INCF                                                   |

| PIC16C9XX219                               | INCF                                                   |

| PIC17CXX220                                | INCFSIZ                                                |

| FERR                                       | INDF0                                                  |

| FOSC099                                    | INDF1                                                  |

|                                            | 34, 40                                                 |

| MP-C C Compiler145                             | PORTD                                 | 19, 34, 60 |

|------------------------------------------------|---------------------------------------|------------|

| MPSIM Software Simulator143, 145               | PORTE                                 | 19, 34, 62 |

| MULLW129                                       | Power-down Mode                       | 105        |

| Multiply Examples                              | Power-on Reset (POR)                  | 15, 99     |

| 16 x 16 Routine50                              | Power-up Timer (PWRT)                 | 15, 99     |

| 16 x 16 Signed Routine51                       | PR1                                   | 20, 35     |

| 8 x 8 Routine49                                | PR2                                   | 20, 35     |

| 8 x 8 Signed Routine49                         | PR3/CA1H                              | 20         |

| MULWF129                                       | PR3/CA1L                              | 20         |

|                                                | PR3H/CA1H                             | 35         |

| A.I.                                           | PR3L/CA1L                             | 35         |

| N                                              | Prescaler Assignments                 | 69         |

|                                                | PRO MATE® Universal Programmer        | 143        |

| NEGW130                                        | PRODH                                 |            |

| NOP130                                         | PRODL                                 |            |

|                                                | Program Counter (PC)                  | 41         |

| 0                                              | Program Memory                        |            |

| O .                                            | External Access Waveforms             | 31         |

| OERR84                                         | External Connection Diagram           |            |

| Opcode Field Descriptions                      | Map                                   |            |

| ·                                              | Modes                                 | 20         |

| OSC Selection                                  | Extended Microcontroller              | 20         |

| Oscillator                                     | Microcontroller                       |            |

| Configuration                                  | Microprocessor                        |            |

| Crystal                                        | Protected Microcontroller             | 29         |

| External Clock101                              |                                       |            |

| External Crystal Circuit102                    | Operation                             |            |

| External Parallel Resonant Crystal Circuit 102 | Organization                          | 29         |

| External Series Resonant Crystal Circuit102    | Transfers from Data Memory            |            |

| RC102                                          | Protected Microcontroller             |            |

| RC Frequencies165, 195                         | PS0                                   | ,          |

| Oscillator Start-up Time (Figure)18            | PS1                                   | ,          |

| Oscillator Start-up Timer (OST)15, 99          | PS2                                   | ,          |

| OST15, 99                                      | PS3                                   | 38, 67     |

| OV9, 36                                        | PUSH                                  | 27, 39     |

| Overflow (OV)9                                 | PW1DCH                                | 20, 35     |

|                                                | PW1DCL                                | 20, 35     |

| <b>D</b>                                       | PW2DCH                                | 20, 35     |

| P                                              | PW2DCL                                | 20, 35     |

|                                                | PWM                                   | 71, 75     |

| Package Marking Information210                 | Duty Cycle                            | 76         |

| Packaging Information205                       | External Clock Source                 |            |

| Parameter Measurement Information154           | Frequency vs. Resolution              |            |

| PC (Program Counter)41                         | Interrupts                            |            |

| PCH41                                          | Max Resolution/Frequency for External |            |

| PCL34, 41, 108                                 | Clock Input                           | 77         |

| PCLATH34, 41                                   | Output                                |            |

| PD                                             | Periods                               |            |

| PEIE                                           | PWM1                                  |            |

| PEIF22                                         | PWM1ON                                |            |

| Peripheral Bank42                              | PWM2                                  |            |

| Peripheral Interrupt Enable                    | PWM2ON                                |            |

| Peripheral Interrupt Request (PIR)24           | PWRT                                  | •          |

| PICDEM-1 Low-Cost PIC16/17 Demo Board143, 144  | FVKI                                  | 15, 99     |

| PICDEM-2 Low-Cost PIC16CXX Demo Board 143, 144 |                                       |            |

| PICDEM-3 Low-Cost PIC16C9XXX Demo Board144     | R                                     |            |

| PICMASTER® RT In-Circuit Emulator              |                                       |            |

| PICSTART® Low-Cost Development System143       | RA1/T0CKI pin                         | 67         |

|                                                | RBIE                                  |            |

| PIE                                            | RBIF                                  |            |

| Pin Compatible Devices                         | RBPU                                  |            |

| PIR                                            | RC Oscillator                         |            |

| PM0                                            |                                       |            |

| PM199, 106                                     | RC Oscillator Frequencies             |            |

| POP27, 39                                      | RCIE                                  |            |

| POR15, 99                                      | RCIF                                  |            |

| PORTA                                          | RCREG 19, 34                          |            |

| PORTB                                          | RCSTA 19                              |            |

| PORTC19, 34, 58                                | Reading 16-bit Value                  | 69         |

| Receive Status and Control Register83     | SWAPF                           | 137    |

|-------------------------------------------|---------------------------------|--------|

| Register File Map33                       | SYNC                            | 83     |

| Registers                                 | Synchronous Master Mode         | 93     |

| ALUSTA27, 36                              | Synchronous Master Reception    | 95     |

| BRG86                                     | Synchronous Master Transmission | 93     |

| BSR27                                     | Synchronous Slave Mode          | 97     |

| CPUSTA37                                  | •                               |        |

| File Map                                  | <b>-</b>                        |        |

| FSR040                                    | Т                               |        |

| FSR140                                    |                                 |        |

| INDF040                                   | T0CKI Pin                       |        |

| INDF140                                   | TOCKIE                          |        |

| INTSTA                                    | T0CKIF                          |        |

| PIE                                       | T0CS                            | 38, 67 |

| PIR                                       | T0IE                            | 22     |

| RCSTA84                                   | T0IF                            | 22     |

| Special Function Table34                  | T0SE                            | 38, 67 |

| TOSTA                                     | T0STA                           | 34, 38 |

| TCON1                                     | T16                             | 71     |

| TCON2                                     | Table Latch                     | 40     |

|                                           | Table Pointer                   | 40     |

| TMR181                                    | Table Read                      |        |

| TMR281                                    | Example                         | 48     |

| TMR381                                    | Section                         |        |

| TXSTA83                                   | Table Reads Section             |        |

| WREG27                                    |                                 |        |

| Reset                                     | TABLRD Operation                |        |

| Section15                                 | Timing                          |        |

| Status Bits and Their Significance        | TLRD                            |        |

| Time-Out in Various Situations            | TLRD Operation                  | 44     |

| Time-Out Sequence                         | Table Write                     |        |

| RETFIE                                    | Code                            | 46     |

|                                           | Interaction                     | 45     |

| RETLW                                     | Section                         |        |

| RETURN                                    | TABLWT Operation                |        |

| RLCF                                      | Terminating Long Writes         |        |

| RLNCF                                     | Timing                          |        |

| RRCF                                      | TLWT Operation                  |        |

| RRNCF                                     | To External Memory              |        |

| RX Pin Sampling Scheme91                  |                                 |        |

| RX984                                     | To Internal Memory              |        |

| RX9D84                                    | TABLRD                          |        |

|                                           | TABLWT                          |        |

|                                           | TBLATH                          |        |

| S                                         | TBLATL                          | 40     |

|                                           | TBLPTRH                         | 34, 40 |

| Sampling91                                | TBLPTRL                         | 34, 40 |

| Saving STATUS and WREG in RAM27           | TCLK12                          | 71     |

| SETF                                      | TCLK3                           | 71     |

| SFR                                       | TCON1                           |        |

| SFR (Special Function Registers)          | TCON2                           | ,      |

| SFR As Source/Destination                 | Terminating Long Writes         | •      |

| Signed Math 9                             | Time-Out Sequence               |        |

| <u> </u>                                  | Timer Resources                 |        |

| SLEEP                                     |                                 |        |

| Software Simulator (MPSIM)145             | Timer0                          | b/     |

| SPBRG                                     | Timer1                          | _      |

| Special Features of the CPU               | 16-bit Mode                     |        |

| Special Function Registers29, 32, 34, 108 | Clock Source Select             |        |

| SPEN                                      | On bit                          | 72     |

| SREN84                                    | Section                         | 71, 73 |

| Stack                                     | Timer2                          |        |

| Operation                                 | 16-bit Mode                     | 74     |

| Pointer                                   | Clock Source Select             |        |

| Stack                                     | On bit                          |        |

| STKAL 39                                  | Section                         |        |

| STKAV                                     | Timer3                          | 1, 1   |

| SUBLW                                     | Clock Source Select             | 7/     |

|                                           |                                 |        |

| SUBWF                                     | On bit                          |        |

| SUBWFB 136                                | Section                         | 71. 77 |

| Figure 6-12:  | Program Counter using The CALL and        | Figure 14-3:   | Crystal Operation, Overtone Crystals       |

|---------------|-------------------------------------------|----------------|--------------------------------------------|

| Ciaura 6 12.  | GOTO Instructions                         | Figure 14 4    | (XT OSC Configuration)                     |

| Figure 6-13:  | BSR Operation (PIC17C43/R43/44)           | Figure 14-4:   | External Clock Input Operation             |

| Figure 7-1:   | TLWT Instruction Operation                | Ciauro 14 E    | (EC OSC Configuration)                     |

| Figure 7-2:   | TABLWT Instruction Operation              | Figure 14-5:   | External Parallel Resonant Crystal         |

| Figure 7-3:   | TLRD Instruction Operation                | F: 44 C        | Oscillator Circuit                         |

| Figure 7-4:   | TABLED Instruction Operation              | Figure 14-6:   | External Series Resonant Crystal           |

| Figure 7-5:   | TABLWT Write Timing                       | F: 44.7        | Oscillator Circuit                         |

|               | (External Memory)46                       | Figure 14-7:   | RC Oscillator Mode                         |

| Figure 7-6:   | Consecutive TABLWT Write Timing           | Figure 14-8:   | Watchdog Timer Block Diagram 104           |

|               | (External Memory)47                       | Figure 14-9:   | Wake-up From Sleep Through Interrupt 105   |

| Figure 7-7:   | TABLRD Timing48                           | Figure 15-1:   | General Format for Instructions 108        |

| Figure 7-8:   | TABLRD Timing (Consecutive TABLRD         | Figure 15-2:   | Q Cycle Activity 109                       |

|               | Instructions)48                           | Figure 17-1:   | Parameter Measurement Information 154      |

| Figure 9-1:   | RA0 and RA1 Block Diagram53               | Figure 17-2:   | External Clock Timing 155                  |

| Figure 9-2:   | RA2 and RA3 Block Diagram54               | Figure 17-3:   | CLKOUT and I/O Timing 156                  |

| Figure 9-3:   | RA4 and RA5 Block Diagram54               | Figure 17-4:   | Reset, Watchdog Timer,                     |

| Figure 9-4:   | Block Diagram of RB<7:4> and RB<1:0>      | •              | Oscillator Start-Up Timer and              |

| · ·           | Port Pins55                               |                | Power-Up Timer Timing 157                  |

| Figure 9-5:   | Block Diagram of RB3 and RB2 Port Pins56  | Figure 17-5:   | Timer0 Clock Timings 158                   |

| Figure 9-6:   | Block Diagram of RC<7:0> Port Pins58      | Figure 17-6:   | Timer1, Timer2, And Timer3 Clock           |

| Figure 9-7:   | PORTD Block Diagram                       | 94.0 0.        | Timings                                    |

| riguic o 7.   | (in I/O Port Mode)60                      | Figure 17-7:   | Capture Timings 159                        |

| Figure 0.9:   |                                           | Figure 17-8:   | PWM Timings                                |

| Figure 9-8:   | PORTE Block Diagram (in I/O Bort Mode) 62 | Figure 17-9:   | USART Module: Synchronous                  |

| Figure 0.0.   | (in I/O Port Mode)                        | rigule 17-9.   | •                                          |

| Figure 9-9:   | Successive I/O Operation                  | F' 47 40       | Transmission (Master/Slave) Timing 160     |

| Figure 11-1:  | TOSTA Register (Address: 05h,             | Figure 17-10:  | USART Module: Synchronous Receive          |

| =             | Unbanked)                                 |                | (Master/Slave) Timing                      |

| Figure 11-2:  | Timer0 Module Block Diagram68             | Figure 17-11:  | Memory Interface Write Timing 161          |

| Figure 11-3:  | TMR0 Timing with External Clock           | Figure 17-12:  | Memory Interface Read Timing 162           |

|               | (Increment on Falling Edge)68             | Figure 18-1:   | Typical RC Oscillator Frequency            |

| Figure 11-4:  | TMR0 Timing: Write High or Low Byte 69    |                | vs. Temperature 163                        |

| Figure 11-5:  | TMR0 Read/Write in Timer Mode70           | Figure 18-2:   | Typical RC Oscillator Frequency            |

| Figure 12-1:  | TCON1 Register (Address: 16h, Bank 3)71   |                | vs. VDD                                    |

| Figure 12-2:  | TCON2 Register (Address: 17h, Bank 3)72   | Figure 18-3:   | Typical RC Oscillator Frequency            |

| Figure 12-3:  | Timer1 and Timer2 in Two 8-bit            | •              | vs. VDD                                    |

| · ·           | Timer/Counter Mode73                      | Figure 18-4:   | Typical RC Oscillator Frequency            |

| Figure 12-4:  | TMR1 and TMR2 in 16-bit Timer/Counter     | · ·            | vs. VDD                                    |

| Ü             | Mode74                                    | Figure 18-5:   | Transconductance (gm) of LF Oscillator     |

| Figure 12-5:  | Simplified PWM Block Diagram75            |                | vs. VDD                                    |

| Figure 12-6:  | PWM Output75                              | Figure 18-6:   | Transconductance (gm) of XT Oscillator     |

| Figure 12-7:  | Timer3 with One Capture and One           | 94.0 .0 0.     | vs. VDD                                    |

| riguic 12 7.  | Period Register Block Diagram78           | Figure 18-7:   | Typical IDD vs. Frequency (External        |

| Figure 12-8:  | Timer3 with Two Capture Registers         | riguic 10-7.   | Clock 25°C)                                |

| rigule 12-0.  | Block Diagram79                           | Figure 18-8:   | Maximum IDD vs. Frequency (External        |

| Figure 12 0:  |                                           | rigule 10-0.   |                                            |

| Figure 12-9:  | TMR1, TMR2, and TMR3 Operation in         | F: 40 0:       | Clock 125°C to -40°C)                      |

| Fig. 40.40    | External Clock Mode80                     | Figure 18-9:   | Typical IPD vs. VDD Watchdog               |

| Figure 12-10: | TMR1, TMR2, and TMR3 Operation in         | E: 10.10       | Disabled 25°C                              |

| =             | Timer Mode81                              | Figure 18-10:  | Maximum IPD vs. VDD Watchdog               |

| Figure 13-1:  | TXSTA Register (Address: 15h, Bank 0) 83  |                | Disabled                                   |

| Figure 13-2:  | RCSTA Register (Address: 13h, Bank 0) 84  | Figure 18-11:  | Typical IPD vs. VDD Watchdog               |

| Figure 13-3:  | USART Transmit85                          |                | Enabled 25°C 169                           |

| Figure 13-4:  | USART Receive85                           | Figure 18-12:  | Maximum IPD vs. VDD Watchdog               |

| Figure 13-5:  | Asynchronous Master Transmission90        |                | Enabled 169                                |

| Figure 13-6:  | Asynchronous Master Transmission          |                | WDT Timer Time-Out Period vs. VDD 170      |

|               | (Back to Back)90                          | Figure 18-14:  | IOH vs. VOH, VDD = 3V                      |

| Figure 13-7:  | RX Pin Sampling Scheme91                  | Figure 18-15:  | IOH vs. VOH, VDD = 5V                      |

| Figure 13-8:  | Asynchronous Reception92                  | Figure 18-16:  | IOL vs. VOL, VDD = 3V                      |

| Figure 13-9:  | Synchronous Transmission94                | Figure 18-17:  | IOL vs. VOL, VDD = 5V                      |

| Figure 13-10: | Synchronous Transmission                  |                | VTH (Input Threshold Voltage) of           |

| -             | (Through TXEN)94                          | -              | I/O Pins (TTL) vs. VDD 172                 |

| Figure 13-11: | Synchronous Reception (Master Mode,       | Figure 18-19:  | VTH, VIL of I/O Pins (Schmitt Trigger) vs. |

| 3             | SREN)95                                   | 3.12.12.101    | VDD                                        |

| Figure 14-1:  | Configuration Word99                      | Figure 18-20:  | VTH (Input Threshold Voltage) of OSC1      |

| Figure 14-2:  | Crystal or Ceramic Resonator Operation    |                | Input (In XT and LF Modes) vs. VDD 173     |

| 9 1 7 2.      | (XT or LF OSC Configuration)100           | Figure 19-1:   | Parameter Measurement Information 183      |

|               | (AT 51 E1 500 Configuration) 100          | 1 1gul 6 13-1. | i didinotoi wodouroment inioimation 100    |

#### Note the following details of the code protection feature on PICmicro® MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- · Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELO© code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.